ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к способам и устройству для генерирования результатов проверки циклически избыточным кодом для множества кодовых блоков.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

Система беспроводной связи обычно включает в себя множество базовых станций и множество мобильных станций, в то время как единственная базовая станция осуществляет связь с набором мобильных станций. Передача от базовой станции к мобильной станции известна как нисходящая связь. Подобным образом, передача от мобильной станции к базовой станции известна как восходящая связь. И базовые станции, и мобильные станции могут использовать множество антенн для передачи и приема радиочастотных сигналов. Радиоволновой сигнал может относиться либо к сигналам с мультиплексированием с ортогональным частотным разделением каналов (OFDM), либо к сигналам множественного доступа с кодовым разделением каналов (CDMA). Мобильная станция может быть устройством PDA (персональный цифровой ассистент), дорожным, либо карманным устройством.

В системах с длительным циклом развития (LTE) в Проекте партнерства в области систем связи третьего поколения (3GPP), когда транспортный блок является большим, транспортный блок сегментируется на множество кодовых блоков, так что может быть сгенерировано множество кодированных пакетов, что выигрышно вследствие преимуществ, таких как предоставление возможности параллельной обработки или реализация конвейерной обработки данных и гибкий компромисс между потребляемой мощностью и сложностью аппаратного обеспечения.

В современной конструкции высокоскоростного совместно используемого канала передачи данных (HS-DSCH) генерируется только один 24-битный результат проверки циклически избыточным кодом для всего транспортного блока для цели обнаружения ошибки для данного блока. Если генерируется и передается в одном временном интервале передачи (TTI) множество кодовых блоков, приемник может правильно декодировать некоторые из кодовых блоков, но не остальные. В этом случае приемник будет передавать в качестве обратной связи неподтверждение (NAK) передатчику, поскольку CRC для транспортного блока не будет проверяться.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Следовательно, задачей настоящего изобретения является предоставление улучшенных способов и устройств для генерирования результатов проверки циклически избыточным кодом для множества кодовых блоков в системе связи.

Другой задачей настоящего изобретения является предоставление улучшенных способа и устройства для обнаружения ошибок в системе связи.

Согласно одному аспекту настоящего изобретения предоставлен способ для осуществления связи. CRC транспортного блока вычисляется для транспортного блока, включающего в себя множество информационных битов. Транспортный блок, включающий в себя CRC транспортного блока, сегментируется на множество подмножеств, и множество результатов проверки циклически избыточным кодом вычисляется для упомянутого множества подмножеств.

Множество результатов проверки циклически избыточным кодом и множество информационных битов передаются от первого узла второму узлу.

В ответ на получение множества результатов проверки циклически избыточным кодом и множества информационных битов, множество результатов проверки циклически избыточным кодом и множество информационных битов обрабатываются на втором узле.

Подмножество информационных битов может совместно кодироваться посредством определенного типа кода с прямым исправлением ошибок, такого как турбокод.

Подмножество информационных битов и по меньшей мере один результат проверки циклически избыточным кодом, который вычисляется на основе подмножества информационных битов, могут кодироваться совместно.

Первый результат проверки циклически избыточным кодом может быть вычислен для первого подмножества информационных битов, а вторые результаты проверки циклически избыточным кодом могут быть вычислены для второго подмножества информационных битов.

Первое подмножество информационных битов и второе подмножество информационных битов могут пересекаться друг с другом.

В качестве альтернативы, первое подмножество информационных битов и второе подмножество информационных битов могут быть отделены друг от друга.

Также в качестве альтернативы, второе подмножество информационных битов может включать в себя первое подмножество информационных битов.

По меньшей мере один результат проверки циклически избыточным кодом среди множества результатов проверки циклически избыточным кодом может быть вычислен на основе всех из информационных битов.

Согласно другому аспекту настоящего изобретения предоставлен способ для осуществления связи. По меньшей мере один транспортный блок информационных битов сегментируется на множество кодовых блоков. Множество результатов проверки циклически избыточным кодом кодовых блоков вычисляется для множества кодовых блоков, где по меньшей мере один результат проверки циклически избыточным кодом вычисляется на основе соответствующего кодового блока. Множество кодовых блоков и множество результатов проверки циклически избыточным кодом передаются от первого узла второму узлу.

Биты в кодовом блоке, выбираемые из множества кодовых блоков, могут совместно кодироваться с использованием определенного типа кода с прямым исправлением ошибок. В этом случае результат проверки циклически избыточным кодом кодового блока вычисляется на основе совместно кодированного кодового блока.

Каждый из множества результатов проверки циклически избыточным кодом кодовых блоков может быть вычислен на основе соответствующего одного из множества кодовых блоков.

Каждый из множества результатов проверки циклически избыточным кодом кодовых блоков может быть вычислен на основе по меньшей мере соответствующего одного из множества кодовых блоков.

Результат проверки циклически избыточным кодом транспортного блока может быть вычислен на основе транспортного блока до сегментирования транспортного блока.

Множество кодовых блоков может включать в себя по меньшей мере один кодовый блок, из которого не генерируется проверок циклически избыточным кодом в отношении кодовых блоков.

По меньшей мере один результат проверки циклически избыточным кодом кодового блока может быть вычислен на основе всех из множества кодовых блоков.

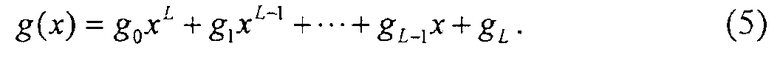

Согласно еще одному аспекту настоящего изобретения схема для генерирования результатов проверки циклически избыточным кодом в передачах данных оснащена: входным портом для приема информационных данных; выходным портом для вывода информационных данных и результатов проверки циклически избыточным кодом; модулем регистров сдвига с линейной обратной связью, подключенным с возможностью связи между входным и выходным портами и содержащим L регистров сдвига для преобразования информационных данных при помощи полинома g(x) генерирования результатов проверки циклически избыточным кодом, имеющего степень L-1; модулем регистров проверки циклически избыточным кодом, подключенным с возможностью связи между входным портом и модулем регистров сдвига с линейной обратной связью и содержащим L регистров проверки циклически избыточным кодом; первым переключателем, подключенным с возможностью связи между входным портом и модулем регистров проверки циклически избыточным кодом; вторым переключателем, подключенным с возможностью связи в контуре обратной связи модуля регистров сдвига с линейной обратной связью; третьим переключателем, подключенным с возможностью связи между модулем регистров сдвига с линейной обратной связью и модулем регистров проверки циклически избыточным кодом; и четвертым переключателем, подключенным с возможностью связи между входным портом, модулем регистров сдвига с линейной обратной связью и выходным портом и имеющим первое положение для соединения входного порта и выходного порта и второе положение для соединения модуля регистров сдвига с линейной обратной связью и выходного порта.

Модуль регистров сдвига с линейной обратной связью и модуль регистров проверки циклически избыточным кодом могут быть инициализированы состоянием из всех нулей. Первый переключатель может быть установлен для подключения входного порта к модулю регистров сдвига с линейной обратной связью. Второй переключатель может быть установлен для подключения контура обратной связи модуля регистров сдвига с линейной обратной связью. Третий переключатель может быть установлен для отключения модуля регистров сдвига с линейной обратной связью от модуля регистров проверки циклически избыточным кодом. Четвертый переключатель может быть установлен в первое положение для подключения входного порта к выходному порту. Кодовый блок информационных данных может быть принят с помощью входного порта. Первый переключатель может быть установлен для отключения входного порта от модуля регистров сдвига с линейной обратной связью. Второй переключатель может быть установлен для отключения контура обратной связи модуля регистров сдвига с линейной обратной связью. Третий переключатель может быть установлен для подключения модуля регистров сдвига с линейной обратной связью с модулем регистров проверки циклически избыточным кодом. Четвертый переключатель может быть установлен во второе положение для подключения модуля регистров сдвига с линейной обратной связью к выходному порту. В отношении модуля регистров сдвига с линейной обратной связью может быть выполнен L-кратный сдвиг для получения результатов проверки циклически избыточным кодом для кодового блока.

Согласно еще одному аспекту настоящего изобретения схема для генерирования результатов проверки циклически избыточным кодом в передачах данных оснащена входным портом для приема информационных данных; выходным портом для вывода информационных данных и результатов проверки циклически избыточным кодом; модулем регистров сдвига с линейной обратной связью, подключенным с возможностью связи между входным и выходным портами и содержащим L регистров сдвига для преобразования информационных данных при помощи полинома g(x) генерирования результатов проверки циклически избыточным кодом, имеющего степень L-1; L регистрами состояния, подключенными с возможностью связи к соответствующим регистрам из L регистров сдвига для записи и чтения значений данных в или из L регистров сдвига; первым переключателем, подключенным с возможностью связи между входным портом и модулем регистров сдвига с линейной обратной связью; вторым переключателем, подключенным с возможностью связи в контуре обратной связи модуля регистров сдвига с линейной обратной связью; и третьим переключателем, подключенным с возможностью связи между входным портом, модулем регистров сдвига с линейной обратной связью и выходным портом и имеющим первое положение для соединения входного порта и выходного порта и второе положение для соединения модуля регистров сдвига с линейной обратной связью и выходного порта.

Модуль регистров сдвига с линейной обратной связью и регистры состояния могут быть инициализированы состоянием из всех нулей. Первый переключатель может быть установлен для подключения входного порта к модулю регистров сдвига с линейной обратной связью. Второй переключатель может быть установлен для соединения контура обратной связи модуля регистров сдвига с линейной обратной связью. Третий переключатель может быть установлен в первое положение для соединения входного порта с выходным портом. Кодовый блок информационных данных может быть принят с помощью входного порта. Значения данных в L регистрах сдвига в модуле регистров сдвига с обратной связью соответственным образом записываются в соответствующие регистры состояния. Первый переключатель может быть установлен для отключения входного порта от модуля регистров сдвига с линейной обратной связью. Второй переключатель может быть установлен для отключения контура обратной связи модуля регистров сдвига с линейной обратной связью. Третий переключатель может быть установлен во второе положение для подключения модуля регистров сдвига с линейной обратной связью к выходному порту. В отношении модуля регистров сдвига с линейной обратной связью выполняется L-кратный сдвиг для получения результатов проверки циклически избыточным кодом для кодового блока. Затем первый переключатель может быть установлен для подключения входного порта к модулю регистров сдвига с линейной обратной связью; второй переключатель может быть установлен для подключения контура обратной связи модуля регистров сдвига с линейной обратной связью; и третий переключатель может быть установлен в первое положение для подключения входного порта к выходному порту. Значения данных в регистрах состояния соответственным образом записываются в соответствующие регистры сдвига в модуле регистров сдвига с обратной связью.

Согласно еще одному аспекту настоящего изобретения схема для генерирования результатов проверки циклически избыточным кодом в передачах данных оснащена входным портом для приема информационных данных; выходным портом для вывода информационных данных и результатов проверки циклически избыточным кодом; первым модулем регистров сдвига с линейной обратной связью, подключенным с возможностью связи между входным и выходным портами и содержащим L регистров сдвига для преобразования информационных данных при помощи полинома g(x) генерирования результатов проверки циклически избыточным кодом, имеющего степень L-1; вторым модулем регистров сдвига с линейной обратной связью, подключенным с возможностью связи между входным и выходным портами, находящимся параллельно первому модулю регистров сдвига с линейной обратной связью и содержащим L регистров сдвига для преобразования информационных данных при помощи полинома g(x) генерирования результатов проверки циклически избыточным кодом, имеющего степень L-1; первым переключателем, подключенным с возможностью связи между входным портом и общей точкой соединения между первым и вторым модулями регистров сдвига с линейной обратной связью; вторым переключателем, подключенным с возможностью связи в контуре обратной связи первого модуля регистров сдвига с линейной обратной связью; третьим переключателем, подключенным с возможностью связи между входным портом, общей точкой соединения между первым и вторым модулями регистров сдвига с линейной обратной связью и выходным портом и имеющим первое положение для подключения входного порта к выходному порту, второе положение для подключения первого модуля регистров сдвига с линейной обратной связью к выходному порту и третье положение для подключения второго модуля регистров сдвига с линейной обратной связью к выходного порту; и четвертым переключателем, подключенным с возможностью связи в контуре обратной связи второго модуля регистров сдвига с линейной обратной связью.

Первый и второй модули регистров сдвига с линейной обратной связью и модуль регистров проверки циклически избыточным кодом могут быть инициализированы состоянием из всех нулей. Первый переключатель может быть установлен для подключения входного порта к общей точке соединения между первым и вторым модулями регистров сдвига с линейной обратной связью; второй переключатель может быть установлен для соединения контура обратной связи первого модуля регистров сдвига с линейной обратной связью; третий переключатель может быть установлен в первое положение для соединения входного порта с выходным портом; и четвертый переключатель может быть установлен для соединения контура обратной связи второго модуля регистров сдвига с линейной обратной связью. Кодовый блок информационных данных может быть принят с помощью входного порта. Выполняется определение относительно того, является ли принятый кодовый блок последним кодовым блоком информационных данных. Когда принятый кодовый блок не является последним кодовым блоком информационных данных, первый переключатель может быть установлен для отключения входного порта от модуля регистров сдвига с линейной обратной связью; второй переключатель может быть установлен для отключения контура обратной связи модуля регистров сдвига с линейной обратной связью; и третий переключатель может быть установлен во второе положение для подключения первого модуля регистров сдвига с линейной обратной связью к выходному порту. В отношении первого модуля регистров сдвига с линейной обратной связью может быть выполнен L-кратный сдвиг для получения результатов проверки циклически избыточным кодом для кодового блока.

Когда принятый кодовый блок информационных данных является последним кодовым блоком информационных данных, третий переключатель может быть установлен в третье положение для подключения второго модуля регистров сдвига с линейной обратной связью к выходному порту; и четвертый переключатель может быть установлен для отключения контура обратной связи модуля регистров сдвига с линейной обратной связью. В отношении второго модуля регистров сдвига с линейной обратной связью может быть выполнен L-кратный сдвиг для получения результатов проверки циклически избыточным кодом для кодового блока.

Согласно дополнительному аспекту настоящего изобретения схема для генерирования результатов проверки циклически избыточным кодом в передачах данных оснащена входным портом для приема информационных данных; выходным портом для вывода информационных данных и результатов проверки циклически избыточным кодом; модулем регистров сдвига с линейной обратной связью, подключенным с возможностью связи между входным и выходным портами и содержащим L регистров сдвига для преобразования информационных данных при помощи полинома g(x) генерирования результатов проверки циклически избыточным кодом, имеющего степень L-1; первым переключателем, подключенным с возможностью связи между входным портом и модулем регистров сдвига с линейной обратной связью; вторым переключателем, подключенным с возможностью связи в контуре обратной связи модуля регистров сдвига с линейной обратной связью; и третьим переключателем, подключенным с возможностью связи между входным портом, модулем регистров сдвига с линейной обратной связью и выходным портом и имеющим первое положение для подключения входного порта к выходному порту и второе положение для подключения модуля регистров сдвига с линейной обратной связью к выходному порту.

Модуль регистров сдвига с линейной обратной связью может быть инициализирован состоянием из всех нулей. Первый переключатель может быть установлен для подключения входного порта к модулю регистров сдвига с линейной обратной связью; второй переключатель может быть установлен для подключения контура обратной связи модуля регистров сдвига с линейной обратной связью; и третий переключатель может быть установлен в первое положение для подключения входного порта к выходному порту. Кодовый блок информационных данных может быть принят через входной порт. Первый переключатель может быть установлен для отключения входного порта от модуля регистров сдвига с линейной обратной связью; второй переключатель может быть установлен для отключения контура обратной связи модуля регистров сдвига с линейной обратной связью; и третий переключатель может быть установлен во второе положение для подключения модуля регистров сдвига с линейной обратной связью к выходному порту. В отношении модуля регистров сдвига с линейной обратной связью может быть выполнен L-кратный сдвиг для получения результатов проверки циклически избыточным кодом для кодового блока.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Более полное понимание изобретения и множество его сопутствующих преимуществ будут с легкостью очевидны, в то время как оно становится лучше понятно посредством отсылки к последующему подробному описанию, при рассмотрении в сочетании с прилагаемыми чертежами, на которых одинаковые ссылочные символы указывают одинаковые или сходные компоненты, где:

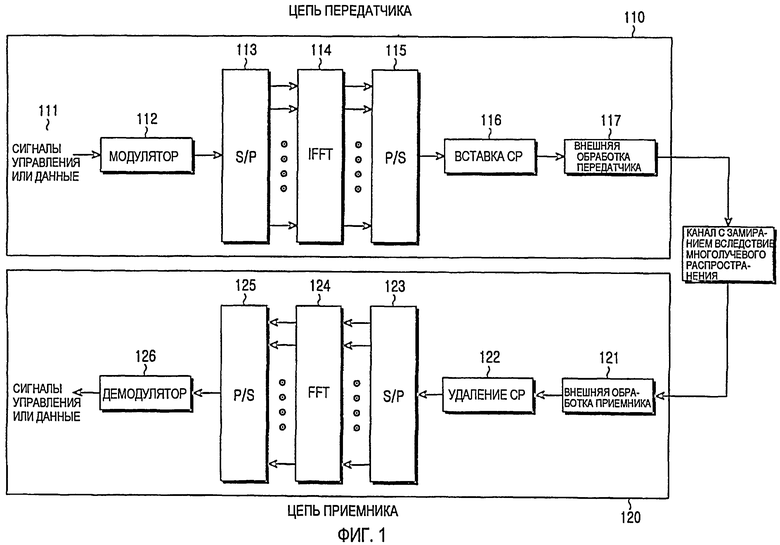

фиг. 1 является иллюстрацией схемы приемопередатчика с мультиплексированием с ортогональным частотным разделением каналов (OFDM), пригодного для осуществления принципов настоящего изобретения;

фиг. 2 является двухкоординатным графиком поднесущих OFDM, показывающих амплитуду как функцию частоты;

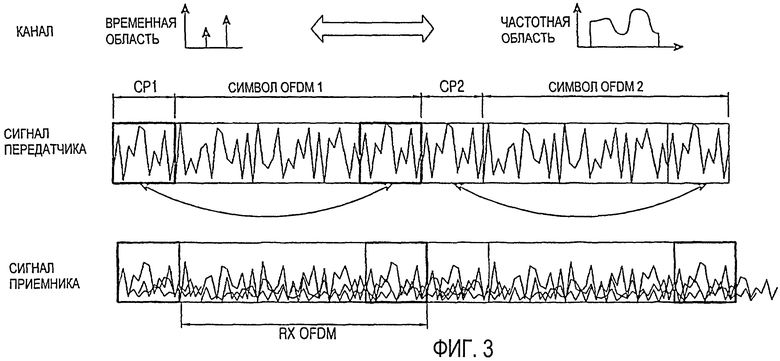

фиг. 3 является иллюстрацией волновых форм для символов OFDM во временной области;

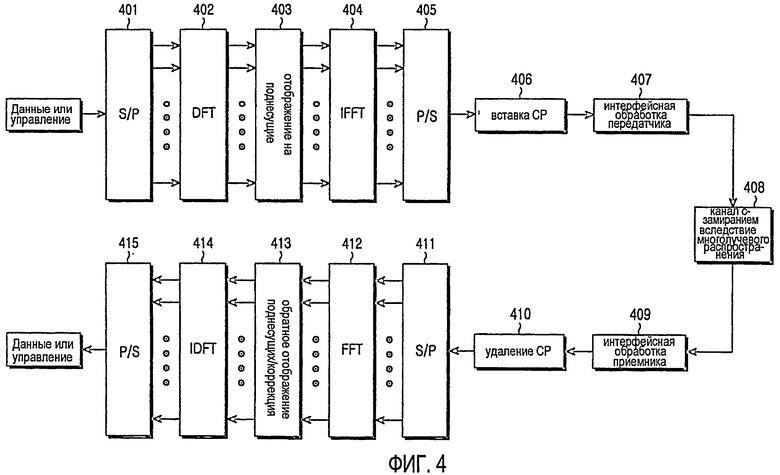

фиг. 4 является иллюстрацией цепи приемопередтчика с множественным доступом с частотным разделением каналов с одной несущей;

фиг. 5 схематически показывает цепь приемопередатчика с гибридным автоматическим запросом на повторную передачу данных (HARQ);

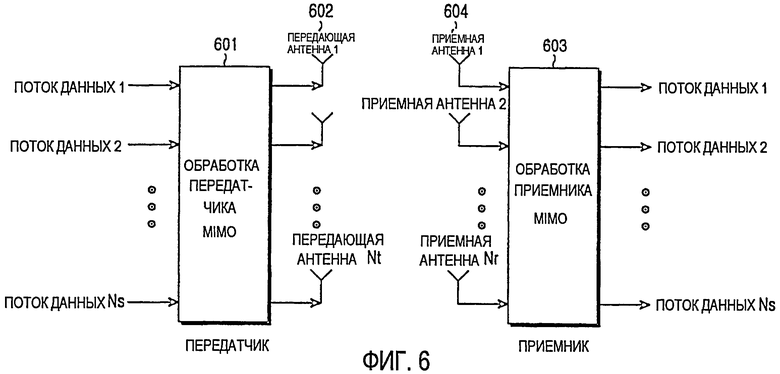

фиг. 6 схематически показывает систему со многими входами и многими выходами (MIMO);

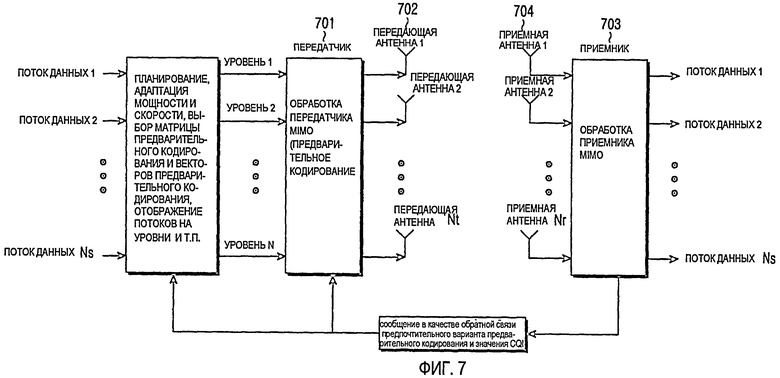

фиг. 7 схематически показывает систему MIMO с предварительным кодированием;

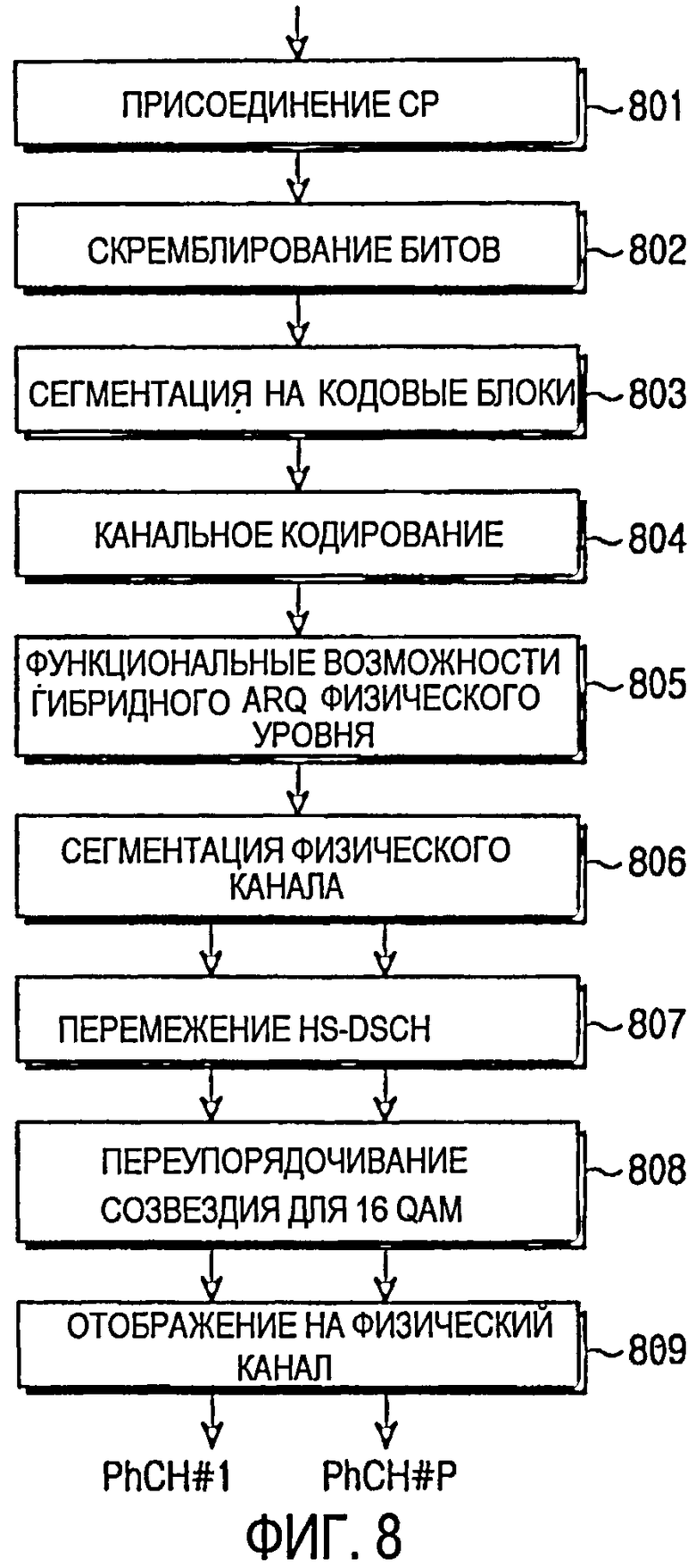

фиг. 8 схематически показывает цепочку кодирования для высокоскоростного совместно используемого канала передачи данных (HS-DSCH) в системе высокоскоростного пакетного доступа по нисходящей линии связи (HSDPA);

фиг. 9 схематично показывает результат проверки циклически избыточным кодом (CRC) транспортного блока и сегментацию кодового блока;

фиг. 10 является иллюстрацией использования регистра сдвига с линейной обратной связью (LFSR) для вычисления CRC;

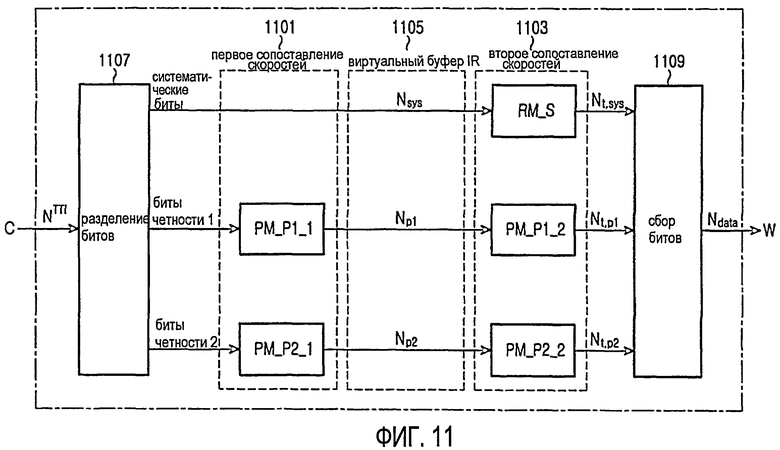

фиг. 11 схематически показывает функциональный узел гибридного ARQ высокоскоростного совместно используемого канала передачи данных (HS-DSCH);

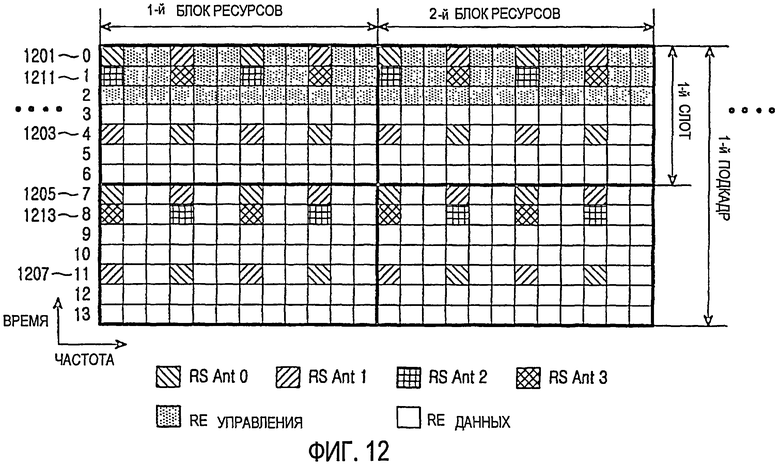

фиг. 12 схематически показывает структуру подкадра нисходящей связи согласно длительному циклу развития (LTE);

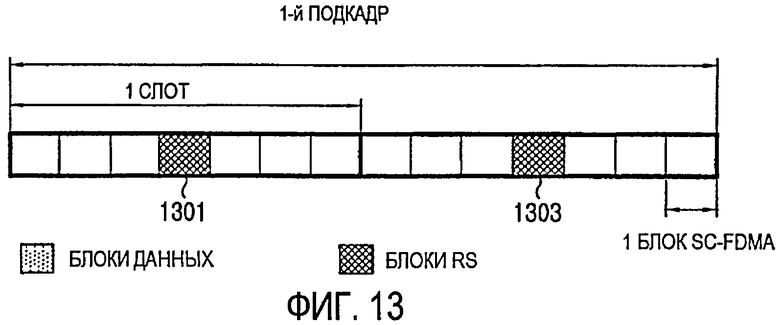

фиг. 13 схематично показывает структуру подкадра восходящей связи LTE;

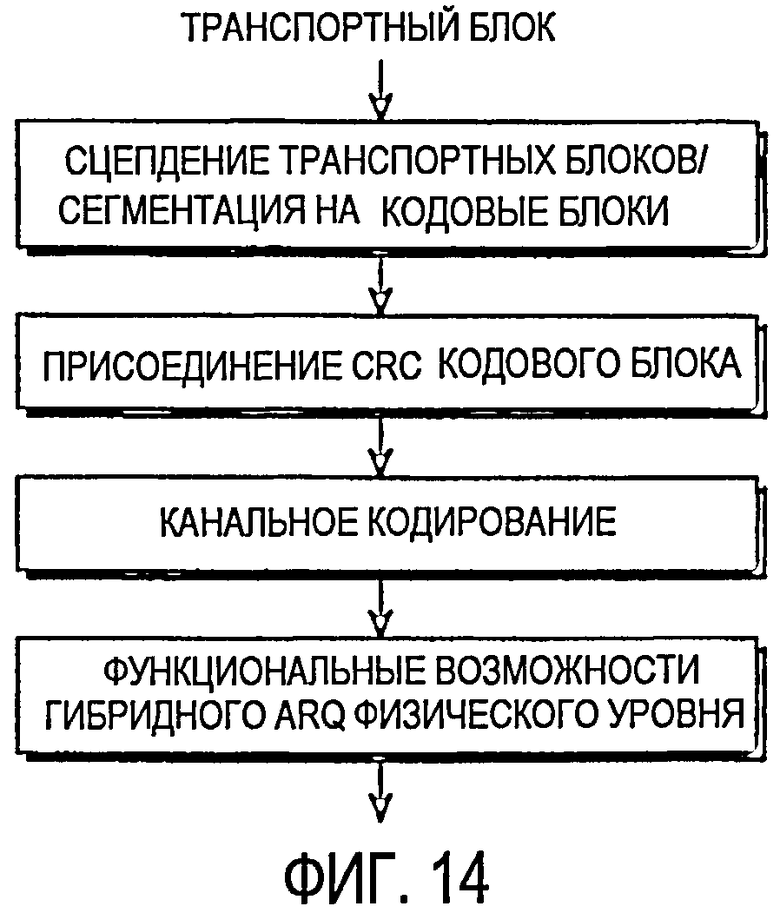

фиг. 14 схематично показывает кодовый блок CRC;

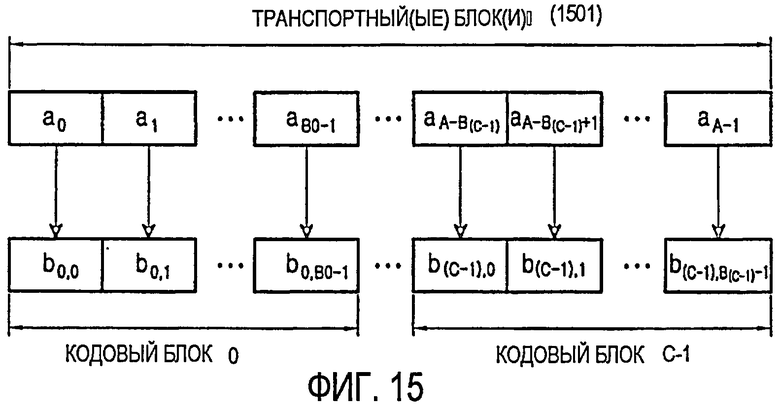

фиг. 15 схематично показывает сегментацию кодового блока;

фиг. 16 схематично показывает CRC кодового блока (CB) и CRC транспортного блока (TB) согласно одному варианту осуществления принципов настоящего изобретения;

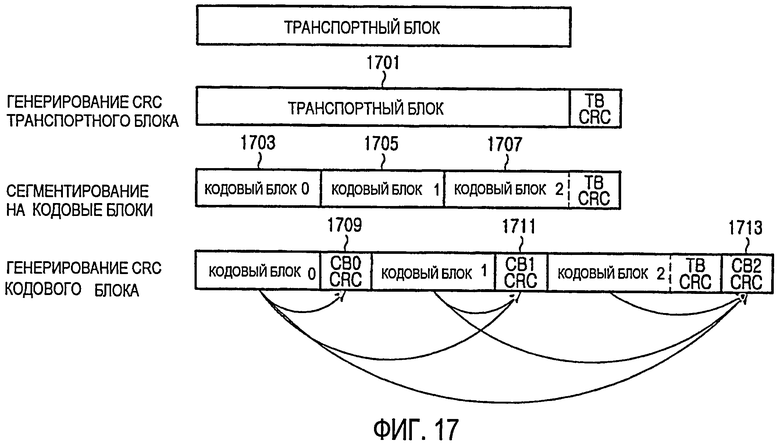

фиг. 17 схематично показывает CRC кодового блока (CB) и CRC транспортного блока (TB) согласно другому варианту осуществления принципов настоящего изобретения;

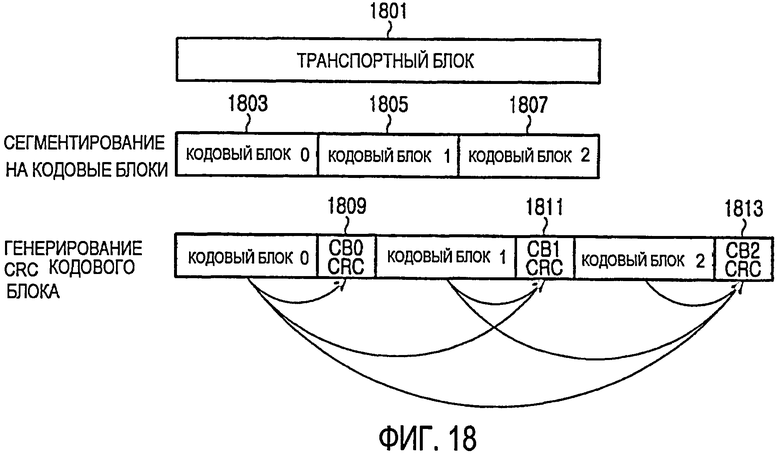

фиг. 18 схематично показывает CRC кодового блока (CB) и CRC транспортного блока (TB) согласно еще одному варианту осуществления принципов настоящего изобретения;

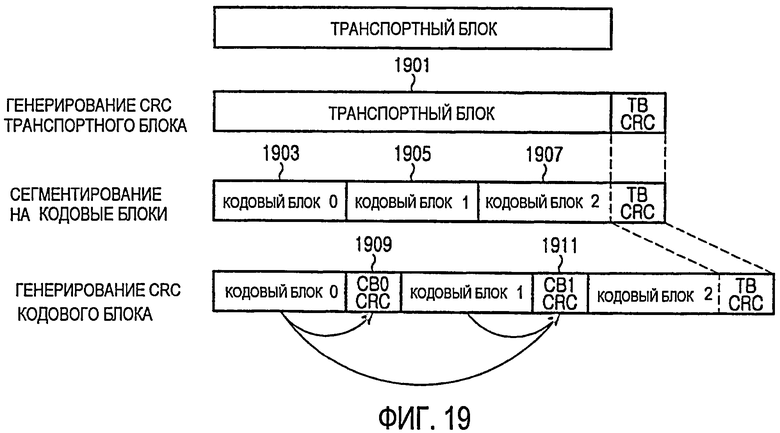

фиг. 19 схематично показывает CRC кодового блока (CB) и CRC транспортного блока (TB) согласно еще одному варианту осуществления принципов настоящего изобретения;

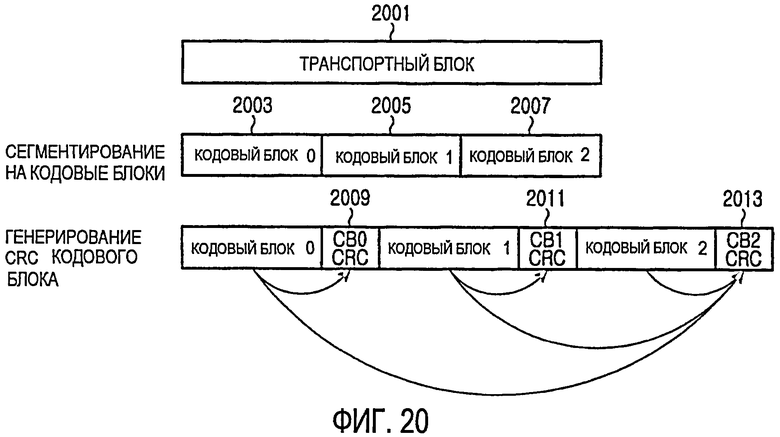

фиг. 20 схематично показывает CRC кодового блока (CB) и CRC транспортного блока (TB) согласно дополнительному варианту осуществления принципов настоящего изобретения;

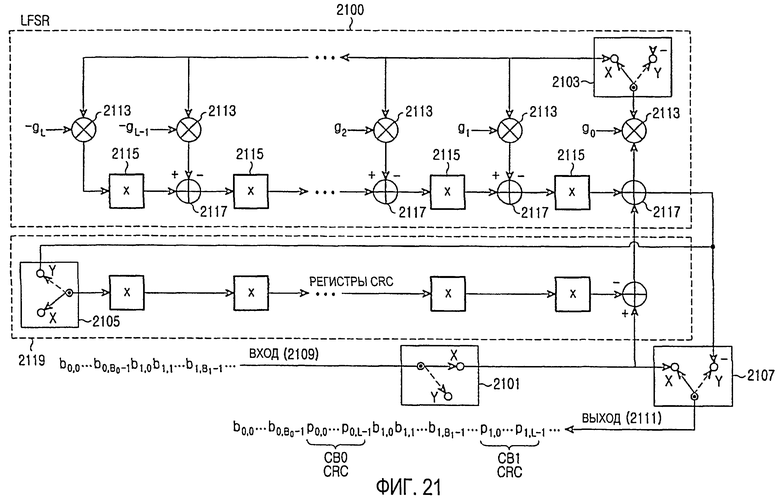

фиг. 21 схематически иллюстрирует схему вычисления CRC для множества кодовых блоков, сконструированную в качестве варианта осуществления согласно принципам настоящего изобретения;

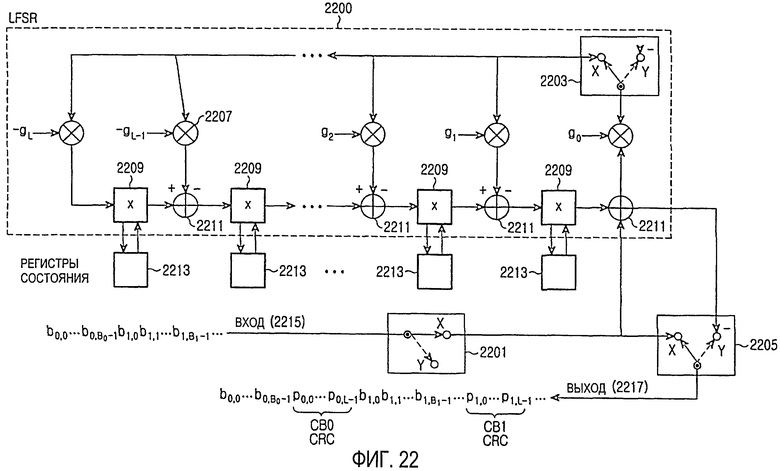

фиг. 22 схематически иллюстрирует схему вычисления CRC для множества кодовых блоков, сконструированную в качестве другого варианта осуществления согласно принципам настоящего изобретения;

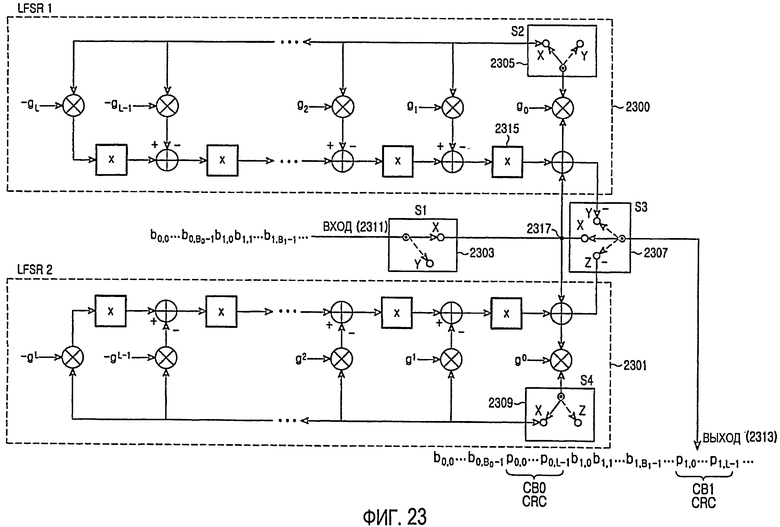

фиг. 23 схематически иллюстрирует схему вычисления CRC для множества кодовых блоков, сконструированную в качестве еще одного варианта осуществления согласно принципам настоящего изобретения;

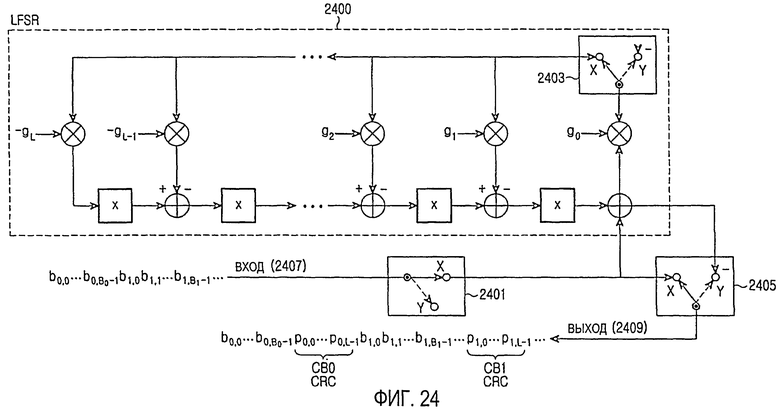

фиг. 24 схематически иллюстрирует схему вычисления CRC для множества кодовых блоков, сконструированную в качестве дополнительного варианта осуществления согласно принципам настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Мультиплексирование с ортогональным частотным разделением каналов (OFDM) является технологией для мультиплексирования данных в частотной области. Символы модуляции переносятся частотными поднесущими. Фиг. 1 иллюстрирует схему приемопередатчика с мультиплексированием с ортогональным частотным разделением каналов (OFDM). В системе связи, использующей технологию OFDM, в цепи 110 передатчика сигналы управления или данные 111 модулируются модулятором 112 в набор символов модуляции, которые затем конвертируются из последовательного представления в параллельное параллельно-последовательным (S/P) преобразователем 113. Модуль 114 быстрого обратного преобразования Фурье (IFFT) используется для преобразования сигналов из частотной области во временную область во множество символов OFDM. Циклический префикс (CP) или нулевой префикс (ZP) добавляется к каждому символу OFDM модулем 116 вставки CP для избежания или подавления влияния, обуславливаемого замиранием вследствие многолучевого распространения. В результате сигнал передается интерфейсным модулем 117 обработки передатчика (Tx), например, через антенну (не показана) или, в качестве альтернативы, посредством стационарной проводки или кабеля. В цепи 120 приемника, предполагая достижение отличной временной и частотной синхронизации, сигнал, принятый интерфейсным модулем 121 обработки приемника (Rx), обрабатывается модулем 122 удаления CP. Модуль 124 быстрого преобразования Фурье (FFT) переносит принятый сигнал из временной области в частотную область для дальнейшей обработки.

В системе OFDM каждый символ OFDM состоит из множества поднесущих. Каждая поднесущая в символе OFDM несет символ модуляции. Фиг. 2 иллюстрирует схему передачи OFDM, использующую поднесущую 1, поднесущую 2 и поднесущую 3. Поскольку каждый символ OFDM имеет конечную длительность во временной области, поднесущие перекрываются друг с другом в частотной области. Тем не менее, ортогональность поддерживается на частоте дискретизации, предполагая, что передатчик и приемник имеют идеальную частотную синхронизацию, как показано на фиг. 2. В случае частотного сдвига вследствие неидеальной частотной синхронизации или высокой подвижности ортогональность поднесущих на частоте дискретизации нарушается, что приводит к перекрестным помехам между несущими (ICI).

Иллюстрация во временной области переданных и принятых символов OFDM показана на фиг. 3. Как показано на фиг. 3, вследствие замирания из-за многолучевого распространения, часть CP (CP1, CP2) принятого сигнала часто повреждается предыдущим символом OFDM. До тех пор пока CP в значительной степени длинный, принятый символ OFDM без CP будет, тем не менее, содержать только свой собственный сигнал, свернутый каналом с замиранием, обусловленным многолучевым распространением. Вообще, быстрое преобразование Фурье (FFT) выполняется на стороне приемника для того, чтобы обеспечить частотную область для дополнительной обработки. Преимуществом OFDM перед другими схемами передачи является устойчивость к замиранию вследствие многолучевого распространения. Замирание вследствие многолучевого распространения во временной области транслируется в частотно избирательное замирание в частотной области. При добавлении циклического префикса или нулевого префикса межсимвольные помехи между соседними символами OFDM избегаются или в большой степени смягчаются. Более того, поскольку каждый символ модуляции переносится по узкой полосе частот, он испытывает замирание вследствие однолучевого распространения. Простая схема коррекции может быть использована для борьбы с частотно-избирательным замиранием.

Множественный доступ с частотным разделением каналов с одной несущей (SC-FDMA), который использует модуляцию одной несущей и корректировку в частотной области, является методикой, которая имеет эффективность и сложность, подобную системе OFDMA. Одним преимуществом SC-FDMA является то, что сигнал SC-FDMA имеет более низкое отношение пиковой к средней мощности (PAPR) вследствие присущей ему структуры с одной несущей. Низкий PAPR обычно приводит к высокой эффективности усилителя мощности, которая особенно важна для мобильных станций при восходящей передаче. SC-FDMA выбирается в качестве схемы восходящей связи множественного доступа в проекте партнерства в области систем связи третьего поколения длительного цикла развития (3 GPP LTE). Пример цепи приемопередатчика для SC-FDMA показан на фиг. 4. На стороне передатчика данные или сигналы управления преобразуются из последовательной формы в параллельную преобразователем 401 S/P. Дискретное преобразование Фурье (DFT) будет применяться к данным временной области или сигналу управления посредством преобразователя 402 DFT до того, как данные временной области будут отображены на набор поднесущих блоком 403 отображения на поднесущие. Для обеспечения низкого PAPR обычно выходной сигнал DFT в частотной области будет отображаться на набор смежных поднесущих. Затем будет применяться IFFT, обычно большей величины, чем DFT, посредством преобразователя 404 IFFT для преобразования сигнала обратно во временную область. После преобразования из параллельной формы в последовательную (P/S) преобразователем 405 P/S будет добавляться циклический префикс CP модулем 406 вставки CP к данным или сигналу управления до того, как данные или сигнал управления будут переданы интерфейсному модулю 407 обработки передатчика. Обработанный сигнал с добавленным циклическим префиксом часто упоминается как блок SC-FDMA. После того как сигнал проходит через канал связи 408, например канал с замиранием вследствие многолучевого распространения в беспроводной системе связи, приемник будет выполнять интерфейсную обработку приемника интерфейсным модулем 409 обработки приемника, удалять CP модулем 410 удаления CP, применять FFT преобразователем 412 FFT и коррекцию 413 частотной области. Обратное дискретное преобразование 414 Фурье (IDFT) будет применяться после того, как в отношении скорректированного сигнала выполняется обратное отображение в частотной области. Выходной сигнал IDFT будет пропускаться для дополнительной обработки во временной области, такой как демодуляция и декодирование, после преобразования из параллельной формы в последовательную (P/S) преобразователем 415 P/S.

В системах беспроводной передачи данных на основе пакетов сигналы управления, передаваемые через управляющие каналы, т.е. в передаче по каналам управления, обычно сопровождают сигналы данных, передаваемые через каналы данных, т.е., передачу данных. Информация канала управления, включающая в себя индикатор формата канала управления (CCFI), сигнал подтверждения (ACK), сигнал канала управления пакетными данными (PDCCH), несет информацию формата передачи для сигнала данных, такую как идентификатор (ID) пользователя, информацию назначения ресурсов, размер полезной нагрузки, модуляцию, информацию гибридного автоматического запроса на повторную передачу (HARQ), информацию, относящуюся к MIMO.

Гибридный автоматический запрос на повторную передачу (HARQ) широко используется в системах связи для борьбы с ошибками декодирования и повышения надежности. Фиг. 5 схематически показывает общую цепь приемопередатчика с гибридным автоматическим запросом на повторную передачу (HARQ), включающую в себя кодер 501, генератор 502 подпакетов, цепь 503 приемопередатчика и декодер 504. Каждый пакет данных кодируется с использованием некоторой схемы прямого исправления ошибок (FEC). Каждый подпакет, генерируемый в генераторе 502 подпакетов, может содержать только часть закодированных битов. Если передача для подпакета k терпит неудачу, что указывается посредством NAK в канале 505 подтверждения обратной связи, передается подпакет повторной передачи, подпакет k+1, для того чтобы помочь декодеру декодировать пакет. Подпакеты повторной передачи могут содержать закодированные биты, отличные от предыдущих подпакетов. Приемник может выполнять мягкое объединение или совместное декодирование всех принятых подпакетов для повышения шанса декодирования. Обычно конфигурируется максимальное количество передач, принимая во внимание надежность, задержку пакетов и сложность реализации.

Системы связи с множеством антенн, которые часто упоминаются как системы со многими входами и многими выходами (MIMO), широко используются в беспроводной связи для улучшения эффективности системы. В системе MIMO, показанной на фиг. 6, передатчик 601 имеет множество антенн 602, способных передавать независимые сигналы, а приемник 603 оборудован множеством приемных антенн 604. Системы MIMO вырождаются в систему с одним входом и множеством выходов (SIMO), если присутствует только одна антенна передачи или если передается только один поток данных. Системы MIMO вырождаются в системы с множеством входов и единственным выходом (MISO), если присутствует только одна приемная антенна. Системы MIMO вырождаются в системы с единственным входом и единственным выходом (SISO), если присутствует только одна передающая антенна и одна приемная антенна. Технология MIMO может существенно увеличивать пропускную способность и дальность связи системы без какого-либо увеличения ширины полосы пропускания или общей мощности передачи. Вообще, технология MIMO увеличивает спектральную эффективность системы беспроводной связи посредством использования дополнительной степени свободы в пространственной области из-за множества антенн. Существует много категорий технологий MIMO. Например, схемы пространственного мультиплексирования увеличивают скорость передачи посредством предоставления возможности многопотоковой передачи данных по нескольким антеннам. Способы разнесения передачи, такие как пространственно-временное кодирование, используют преимущество пространственного разнесения из-за множества передающих антенн. Способы разнесенного приема используют пространственное разнесение вследствие множества приемных антенн. Технологии диаграммы направленности улучшают усиление принятого сигнала и уменьшают помехи другим пользователям. Множественный доступ с пространственным разделением каналов (SDMA) позволяет передавать потоки сигналов от или к множеству пользователей по одним частотно-временным ресурсам. Приемники могут отделять множественные потоки данных посредством пространственной характеристики этих потоков данных. Отметим, что эти техники MIMO передачи не являются взаимоисключающими. Фактически много схем MIMO часто используется в усовершенствованных беспроводных системах.

Когда канал является предпочтительным, например скорость мобильного устройства является низкой, возможно использовать схему MIMO с замкнутым контуром для улучшения эффективности системы. В системах MIMO с замкнутым контуром приемники сообщают в качестве обратной связи состояние канала и/или предпочтительные схемы обработки Tx MIMO. Передатчик использует эту информацию обратной связи вместе с другими соображениями, такими как приоритет планирования, доступность данных и ресурсов, для совместной оптимизации схемы передачи. Популярная схема MIMO с замкнутым контуром называется предварительным кодированием MIMO. При условии предварительного кодирования потоки передаваемых данных предварительно перемножаются посредством матрицы до передачи на множество передающих антенн. Как показано на фиг. 7, допустим, что существует Nt передающих антенн 702 и Nr принимающих антенн 704. Обозначим канал между Nt передающими антеннами 702 и Nr принимающими антеннами 704 как H. Следовательно, H является матрицей Nt×Nr. Если передатчик 701 знает о H, передатчик может выбирать наиболее преимущественную схему передачи согласно H. Например, если целью является максимизация пропускной способности, матрица предварительного кодирования может быть выбрана так, чтобы быть правой сингулярной матрицей H, если знание о H доступно на передатчике. Посредством выполнения этого действующий канал для множества потоков данных на стороне 703 приемника может быть диагонализирован, исключая помехи между множеством потоков данных. Тем не менее, издержки, требуемые для сообщения в качестве обратной связи точного значения H, часто являются непомерными. Для того чтобы уменьшить издержки на обратную связь, набор матриц предварительного кодирования задается для квантования пространства возможных значений, которые может принимать H. С использованием квантования приемник сообщает в качестве обратной связи предпочтительную схему предварительного кодирования, обычно в виде индекса предпочтительной матрицы предварительного кодирования, ранг и индексы предпочтительных векторов предварительного кодирования. Приемник может также сообщать в качестве обратной связи ассоциированные значения CQI для предпочтительной схемы предварительного кодирования.

Другой перспективой системы MIMO является то, кодируются ли множественные потоки данных для передачи раздельно или вместе. Если все уровни передачи кодируются вместе, называем это системой MIMO с единственной кодовой группой (SCW).

В системах LTE, когда транспортный блок является большим, транспортный блок сегментируется на множество кодовых блоков, так что может быть сгенерировано множество кодовых пакетов, что является преимуществом вследствие полезных результатов, таких как предоставление возможности параллельной обработки или реализация конвейерной обработки и гибкий компромисс между потребляемой мощностью и сложностью аппаратного обеспечения. В качестве примера, процесс кодирования высокоскоростного совместно используемого канала передачи данных (HS-DSCH) в системе высокоскоростного пакетного доступа по нисходящей линии связи (HSDPA) проиллюстрирован на фиг. 8. В текущей конструкции HS-DSCH только один 24-битный результат проверки циклически избыточным кодом генерируется для всего транспортного блока для цели обнаружения ошибки для данного блока. Если генерируется и передается в одном временном интервале передачи (TTI) множество кодовых блоков, приемник может правильно декодировать некоторые из кодовых блоков, но не остальные. В этом случае приемник будет сообщать в качестве обратной связи неподтверждение (NAK) передатчику, поскольку CRC для транспортного блока не пройдет проверку. Ссылочные номера с 901 по 905 показывают отношение транспортного блока, CRC транспортного блока (TB CRC) и сегментацию на кодовых блоках на фиг. 9.

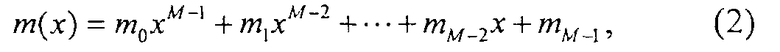

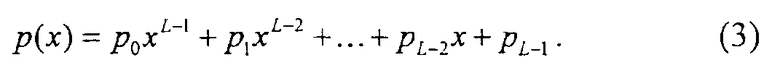

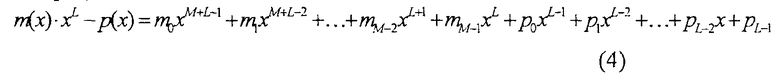

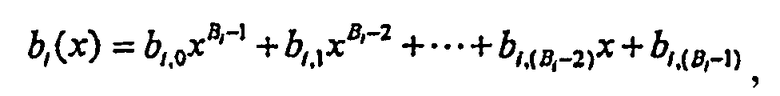

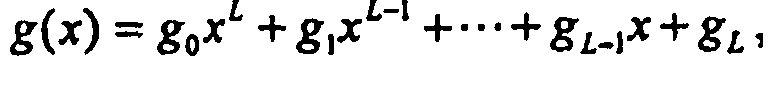

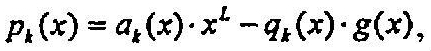

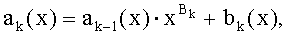

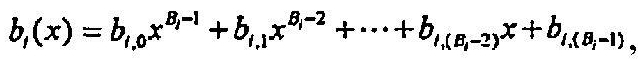

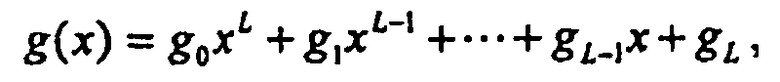

Предположим, что мы используем L-битовый полином для генерирования CRC кодового блока. Обозначим генерирующий CRC полином посредством

Вообще, для сообщения

кодирование CRC выполняется в систематизированном виде. Обозначим биты четности CRC сообщения как p 0 , p 1 ..., p L-1 , что также может быть представлено как полином

Полином

дает остаток, равный 0 при делении на g(x).

Отметим, что если каждый бит в сообщении является двоичным, сообщение может быть представлено в качестве полинома, определенного на двоичном поле Галуа (Galois) (GF(2)). В этом случае операция '+' и '-' является одной и той же. Другими словами, если биты сообщения являются двоичными, эти сообщения с присоединенными CRC могут быть представлены либо посредством m(x)·x L+p(x) либо m(x)·x L -p(x).

В оставшейся части описания данного изобретения ради удобства предполагаем, что биты сообщения являются двоичными. Раскрытые идеи в данном изобретении могут, тем не менее, конечно, применяться, когда биты сообщения являются не двоичными.

Одна причина популярности CRC заключается в простоте ее реализации. Вычисление CRC может быть легко реализовано регистром сдвига с линейной обратной связью (LFSR). LFSR может использоваться в качестве схемы для деления полинома. Как показано на фиг. 10, предположим, что используется L-битный CRC, LFSR 1000 имеет L регистров сдвига (R0~RL-1). Переключатели 1001, 1003 и 1005 первоначально помещены в положение X. Биты m 0, m 1 ,..., и mM-1 сообщения подаются на LFSR 1000 по одному за раз в порядке увеличения индекса. После того как последний бит (mM-1) подан на LFSR 100, переключатели 1001, 1003 и 1005 перемещаются в положение Y. LFSR 1000 сдвигается на другие L раз для создания CRC на выходе самого правого регистра. Отметим, что LFSR на фиг. 9 является только примером. Существуют определенно другие реализации LFSR для деления полиномов и вычисления CRC.

Функциональный узел гибридного ARQ сопоставляет количество битов на выходе канального кодера с общим количеством битов набора высокоскоростного совместно используемого физического канала нисходящей связи (HS-PDSCH), на которые отображается высокоскоростной совместно используемый канал передачи данных (HS-DSCH). Управление функциональным узлом гибридного ARQ осуществляется посредством параметров версии избыточности (RV). Точный набор битов на выходе функционального узла гибридного ARQ зависит от количества входных битов, количества выходных и параметров RV. Функциональный узел гибридного ARQ включает в себя две секции 1101 и 1103 сопоставления скоростей и виртуальный буфер 1105, как показано на фиг. 11. Выходные биты канального кодера сегментируются в систематические биты, биты четности 1 и биты четности 2 посредством секции 1107 разделения битов и подаются на секции сопоставления скоростей. Первая стадия 1101 сопоставления скоростей сопоставляет количество входных битов с виртуальным буфером 1105 IR, информация о котором предоставляется более высокими уровнями. Отметим, что если количество входных битов не превышает емкости виртуального буфера IR, первая секция 1101 сопоставления скоростей является прозрачной. Вторая секция 1103 сопоставления скоростей сопоставляет количество битов на выходе первой секции 1101 сопоставления скоростей с количеством битов физических каналов, доступных в наборе HS-PDSCH в TTI. Выходные биты второй секции 1103 сопоставления скоростей собираются секцией 1109 сбора битов и передаются в беспроводную сеть.

Структура подкадра нисходящей связи LTE показана на фиг. 12. В типичной конфигурации каждый подкадр имеет длину 1 мс, включая в себя 14 символов OFDM, как показано на вертикальной оси. Предположим, что символы OFDM в подкадре проиндексированы от 0 до 13. Опорные символы (RS) для антенны 0 и 1 расположены в символах OFDM 0 (1201), 4(1203), 7(1205) и 11(1207). Если присутствуют, опорные символы (RS) для антенн 2 и 3 расположены в символах OFDM 1(1211) и 8(1213). Каналы управления, включающие в себя индикатор формата канала управления (CCFI), канал подтверждения (ACK), канал управления пакетными данными (PDCCH), передаются в первом одном, двух или трех символах OFDM. Количество символов OFDM, используемых для канала управления, указывается CCFI. Например, каналы управления могут занимать первый символ OFDM, или первые два символа OFDM, или первые три символа OFDM. Каналы данных, например физический совместно используемый канал нисходящей линии связи (PDSCH), передается в других символах OFDM.

Структура подкадра восходящей связи (для передач данных) показана на фиг. 13. Отметим, что восходящая линия связи LTE является системой на основе SC-FDMA, которая очень похожа на систему OFDMA с некоторыми отличиями. Сходно с символом OFDM, каждый блок SC-FDMA имеет циклический префикс (CP). Для передач данных опорные сигналы (RS) расположены в четвертом блоке 1301 SC-FDMA и 11-м блоке 1303 SCFDMA, в то время как остаток блоков SC-FDMA несет данные. Отметим, что фиг. 13 показывает только структуру во временной области подкадра восходящей связи. Для каждого отдельного UE его передача может занимать только часть полной полосы пропускания в частотной области. И различные пользователи, и сигналы управления мультиплексируются в частотной области с помощью SC-FDMA.

В данном изобретении заявители предлагают способы и устройство для вычисления множества CRC для передачи с целью повышения надежности передачи и уменьшения сложности передатчика и приемника.

Аспекты, признаки и преимущества изобретения будут с легкостью очевидны из последующего подробного описания, просто посредством иллюстрирования некоторого количества конкретных вариантов осуществления и реализаций, включая наилучший режим, предполагаемый для реализации изобретения. Изобретение также допускает другие и отличные варианты осуществления, и его некоторые детали могут быть изменены в различных очевидных отношениях без отклонения от сущности и объема изобретения. Таким образом, чертежи и описание должны рассматриваться в качестве иллюстрации по сущности, а не в качестве ограничения. Изобретение проиллюстрировано в качестве примера, а не в качестве ограничения, на прилагаемых чертежах. В последующих иллюстрациях используется канал данных в системах LTE в качестве примера. Иллюстрируемая здесь методика, тем не менее, может, несомненно, быть использована в другом канале в системах LTE и других каналах данных, управления или тому подобного в других системах всякий раз, когда применимо.

Сначала проиллюстрируем концепцию транспортного блока, кодового блока и проверки циклически избыточным кодом (CRC) кодового блока. Часть цепи обработки кодирования на стороне передатчика показана на фиг. 14. Если необходимо, несколько транспортных блоков в TTI могут быть последовательно сцеплены. Если количество битов после сцепления транспортных блоков больше, чем Z, что равно максимальному размеру рассматриваемого кодового блока, то выполняется сегментирование на кодовые блоки после сцепления транспортных блоков. Отметим, что в данном изобретении транспортные блоки могут содержать или не содержать CRC транспортного блока до сегментирования. После сегментирования на кодовые блоки может быть сгенерирован CRC для некоторых или всех из кодовых блоков. После того как CRC кодового блока присоединен к соответствующему кодовому блоку, канальный кодер кодирует кодовый блок, к которому присоединен CRC. Функциональный узел гибридного ARQ сопоставляет количество битов, выводимых из канального кодера, с общим количеством битов набора высокоскоростного совместно используемого физического канала нисходящей связи (HS-PDSCH), на который отображается высокоскоростной совместно используемый канал передачи данных (HS-DSCH). Для целей иллюстрации предположим, что CRC кодового блока генерируется для каждого кодового блока, хотя идеи, раскрытые в данном изобретении, определенно применяются в других случаях. Для легкости иллюстрации, предполагаем, что присутствует только один транспортный блок. Все варианты осуществления в данном изобретении применимы, тем не менее, к случаям с множеством транспортных блоков и сцеплением транспортных блоков. Также отметим, что хотя авторы изобретения часто используют обработку передатчика для иллюстрации идей изобретения, все варианты осуществления в данном изобретении применимы к вычислению CRC и на передатчике, и на приемнике.

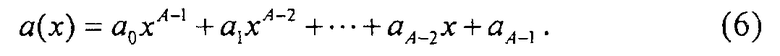

Обозначим входные биты для вычисления CRC как a 0 , a 1 ,..., a A-1, где A является размером транспортного блока. Мы называем входные биты информационными битами. Снова, способ, описанный в данном изобретении, применяется независимо от того, присутствует ли один или несколько транспортных блоков и содержит ли транспортный блок CRC транспортного блока или нет. Предположим, что мы используем L-битовый полином для генерирования CRC кодового блока. Обозначим генерирующий CRC полином посредством

Транспортный блок может быть представлен полиномом

Предположим по отношению сегментации на кодовые блоки, что сообщение транспортного блока сегментируется на C кодовых блоков. Обозначим биты в кодовом блоке i как b i,0 , b i,1 ,..., b i(Bi-1), где B i - размер кодового блока i, i=0, 1,..., C-1. Отметим, что полиномиальное представление кодового блока i есть

Очевидно,

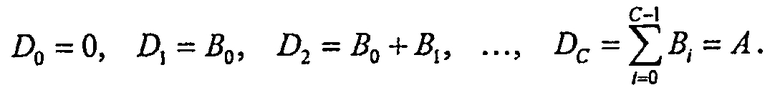

Без потери общности дополнительно предполагаем естественный порядок отображения информационных битов в транспортном блоке 1501 на кодовые блоки 1503,..., 1505, как показано на фиг. 15. Определим:

Другими словами,

Транспортный блок сегментирован на C кодовых блоков. Информационные биты в i-м кодовом блоке являются следующими:

Таким образом, отношение между транспортным блоком и кодовыми блоками может быть установлено следующим образом:

Дополнительно, определим:

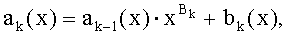

где a k (x) - полиномиальное представление информационных битов до k-го кодового блока, включающее информационные биты в предыдущих кодовых блоках.

Легко видеть, что a 0 (x)=b 0 (x), а a C-1 (x)=a(x). Ради простоты, в оставшейся части описания изобретения эти обозначения используются без повторного определения.

В первом варианте осуществления согласно принципам настоящего изобретения в передаче первого множества битов со вторым множеством CRC или в процессе приема такой передачи, по меньшей мере один CRC вычисляется на основе подмножества битов первого множества битов, так что по меньшей мере один бит первого множества битов не находится в упомянутом подмножестве. На примере, показанном на фиг. 15, CRC транспортного блока генерируется из транспортного блока, и транспортный блок 1601, включающий в себя CRC транспортного блока, сегментируется на кодовый блок 0 1603, кодовый блок 1 1605, кодовый блок 2 1607. CB0_CRC 1609 вычисляется на основе информационных битов в кодовом блоке 0 1603, но не на основе информационных битов в кодовом блоке 1 1605 или кодовом блоке 2 1607. При выполнении этого UE может использовать CB0_CRC 1609 для проверки того, приняты ли информационные биты в кодовом блоке 0 1603 правильно, до окончания обработки приемника для кодового блока 1 1605 и кодового блока 2 1607. Это свойство особенно полезно в смысле уменьшения сложности UE и экономии энергии. CRC кодового блока может быть использован для таких целей, как, но не в ограничительном смысле, обеспечение обнаружения ошибок для соответствующего кодового блока или кодовых блоков, ранней остановки итеративного турбодекодирования, чем можно добиться сохранения энергии и статистического мультиплексирования возможности декодирования между кодовыми блоками, обнаружения ошибки декодирования одного кодового блока, чем можно избежать ненужного декодирования других кодовых блоков в случае ошибки декодирования одного кодового блока, и т.д.

Во втором варианте осуществления согласно принципам настоящего изобретения при передаче первого множества битов со вторым множеством CRC или при обработке приемника такой передачи, по меньшей мере один CRC вычисляется на основе подмножества первого множества битов, которые совместно закодированы некоторым типом кода с прямым исправлением ошибок. Например, как показано на фиг. 15, CB0_CRC 1609 вычисляется на основе битов в кодовом блоке 0 1603 подмножества всех битов в транспортном блоке. Биты в кодовом блоке 0 1603 совместно кодируются посредством некоторого кода с прямым исправлением ошибок (FEC), такого как турбокод. Кодирование FEC иногда также называется канальным кодированием. Отметим, что CB0_CRC 1609 обычно также совместно кодируется с информационными битами в кодовом блоке 0 1603 для достижения защиты от ошибок для информационных битов и битов CRC. Посредством синхронизации блока информационных битов для вычисления CRC и блока информационных битов для канального кодирования FEC канала, UE может использовать CRC кодового блока во время процесса декодирования и определения того, декодирован ли соответствующий кодовый блок правильно. И этот процесс может быть выполнен раздельно для каждого кодового блока с CRC кодового блока, либо параллельно, либо и конвейерным, и последовательным способом.

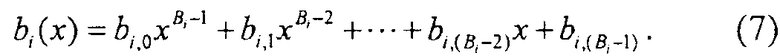

В третьем варианте осуществления согласно принципам настоящего изобретения при передаче первого множества битов со вторым множеством CRC или при обработке приемника такой передачи, первый CRC вычисляется на основе первого подмножества битов, в то время как второй CRC вычисляется на основе второго подмножества битов. Один пример показан на фиг. 16. В данном примере «подмножество битов» соответствует кодовому блоку. Транспортный блок 1601, включает в себя CRC транспортного блока, вычисленный для транспортного блока. Транспортный блок сегментирован на три кодовых блока. CRC вычисляется для каждого кодового блока. CB0_CRC 1609, который является CRC кодового блока, присоединенным к кодовому блоку 0 1603, выводится на основе битов в кодовом блоке 0; CB1_CRC 1611, который является CRC кодового блока, присоединенным к кодовому блоку 1 1605, выводится на основе битов в кодовом блоке 1; CB2_CRC 1613, который является CRC кодового блока, присоединенным к кодовому блоку 2 1607, выводится на основе битов в кодовом блоке 7, включая CRC транспортного блока. Также отметим, что в данном примере первое подмножество битов, из которых выводится первый CRC, не пересекается со вторым подмножеством битов, из которого выводится второй CRC. Подмножества битов могут, тем не менее, определенно пересекаться, без отклонения от раскрытия данного изобретения. Также отметим, что некоторые подмножества могут включать все биты при передаче. Также отметим, что не является необходимым вычислять CRC для всех кодовых блоков для использования данного изобретения. Некоторые кодовые блоки могут не иметь CRC кодового блока. Также отметим, что подмножество может также включать биты в нескольких кодовых блоках. Например, как показано на фиг. 17, CB0_CRC 1709 выводится на основе подмножества битов, которое включает биты в кодовом блоке 0 1703; CB1_CRC 1711 выводится на основе подмножества битов, которое включает биты в кодовом блоке 0 1709 и биты в кодовом блоке 1 1705; CB2_CRC 1713 выводится на основе подмножества битов, которое включает биты в кодовом блоке 0 1703, биты в кодовом блоке 1 1705 и биты в кодовом блоке 2 1707.

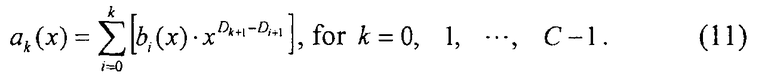

В четвертом варианте осуществления согласно принципам настоящего изобретения при передаче первого множества битов со вторым множеством CRC или при обработке приема такой передачи биты, на основе которых выводится первый CRC, являются подмножеством битов, на основе которых выводится второй CRC. Один пример показан на фиг. 17. Для целей иллюстрации показаны только три кодовых блока. CRC транспортного блока вычисляется для транспортного блока. Затем транспортный блок 1701, включающий в себя CRC транспортного блока, сегментируется на три кодовых блока. CRC вычисляется для каждого кодового блока. CB0_CRC 1709, который является CRC кодового блока, присоединенным к кодовому блоку 0 1703, выводится на основе битов в кодовом блоке 0; CB1_CRC 1711, который является CRC кодового блока, присоединенным к кодовому блоку 1 1705, выводится на основе битов в кодовом блоке 0 и в кодовом блоке 1; CB2_CRC 1713, который является CRC кодового блока, присоединенным к кодовому блоку 2 1707, выводится на основе битов в кодовом блоке 0 1703, кодовом блоке 1 1705 и кодовом блоке 2 1707. Выполняя это, мы улучшаем эффективность в плане неправильного обнаружения для этих CRC в сравнении с CRC, выведенными на основе одного кодового блока. Мы предполагаем, что транспортный блок представлен a(x)-a 0 x A-1 +a 1 x A-2 +...+a A-2 x+a A-1, где A - размер транспортного блока. Если используется CRC транспортного блока (TB CRC), TB CRC включается в сообщение. Как определялось ранее, транспортный блок a(x) сегментируется на C кодовых блоков с i-м кодовым блоком, представленным b i (x). Вычислим один CRC, а именно CB0_CRC, и присоединим его к первому кодовому блоку. CB0_CRC может быть выведен из некоторых или всех битов в первом кодовом блоке. Обозначим CB0_CRC посредством

Один пример вычисления CB0_CRC состоит в нахождении остатка от b 0 (x)·x L , деленного на полином g(x) генерации CRC, в котором p 0 (x) может быть представлен как

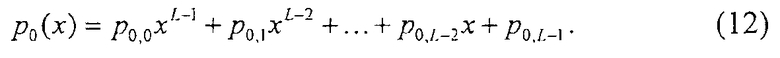

где q 0 (x) - частное от деления b 0 (x)-x L на g(x). Вычислим другой CRC, а именно CB1_CRC, и присоединим его ко второму кодовому блоку. CB1_CRC может быть выведен из одного или всех битов в первом кодовом блоке и некоторых или всех из битов во втором кодовом блоке. Обозначим CB1_CRC посредством

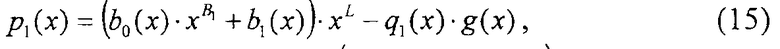

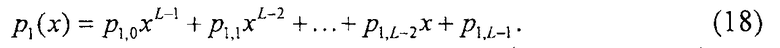

Один пример вычисления CB1_CRC состоит в нахождении остатка от деления b 0 (x)·x B1 +b 1 (x))·x L на полином g(x) генерации CRC, в котором p 1 (x) может быть представлен как

где q 1 (x) - частное от деления (b 0 (x)-x B1 +b 1 (x))·x L на g(x). Посредством выведения CB1_CRC на основе информационных битов в первом кодовом блоке и информационных битов во втором кодовом блоке мы уменьшаем возможность неправильного обнаружения, поскольку CB1_CRC может быть использован для обнаружения ошибки информационных битов в первом кодовом блоке и втором кодовом блоке.

Очевидно, если существует более двух кодовых блоков, мы можем расширить операции подобными способами. Например, CRC, присоединенный к кодовому блоку 2, может быть выведен из битов в кодовом блоке 0, кодовом блоке 1, кодовом блоке 2. В качестве альтернативы, CRC, присоединенный к одному кодовому блоку, не нуждается в том, чтобы быть выведенным на основе битов из всех предыдущих кодовых блоков, включая текущий кодовый блок. Например, CRC, присоединенный к кодовому блоку 2, может быть выведен из битов в кодовом блоке 1, кодовом блоке 2, но не из битов в кодовом блоке 0. Отметим, что данный вариант осуществления также применим, если нет CRC транспортного блока, как показано на фиг. 18. Если обнаружение ошибок CB CRC достаточно надежно, может не требоваться TB CRC.

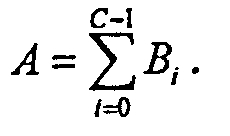

В пятом варианте осуществления, согласно принципам настоящего изобретения при передаче первого множества битов со вторым множеством CRC или при обработке приемника такой передачи, CRC транспортного блока выводится из всех битов в транспортном блоке до сегментации на кодовые блоки, пока присутствует по меньшей мере одно подмножество битов, из которых не вычисляется CRC кодового блока. Как показано на фиг. 19, CRC транспортного блока вычисляется на основе битов в транспортном блоке. Затем транспортный блок 1901, включающий в себя CRC транспортного блока, сегментируется на три кодовых блока. В данном примере CB0_CRC 1909 вычисляется на основе битов в кодовом блоке 0 1903; CB1_CRC 1911 вычисляется на основе битов в кодовом блоке 0 1903 и кодовом блоке 1 1905. Поскольку имеется CRC транспортного блока, который покрывает все биты в транспортном блоке, CRC кодового блока для кодового блока 2, тем не менее, не является необходимым. CB0_CRC 1909 может быть использован для остановки итераций турбодекодирования для кодового блока 0 1903; CB1_CRC 1911 может быть использован для остановки итераций турбодекодирования для кодового блока 1 1905; и TB_CRC может быть использован для остановки итерации турбодекодирования для кодового блока 2 1907. В то же время TB_CRC обеспечивает обнаружение ошибок для целого транспортного блока.

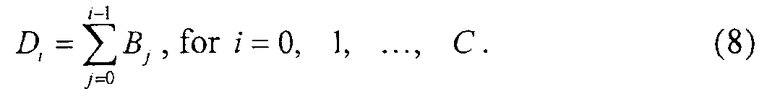

В шестом варианте осуществления согласно принципам настоящего изобретения при передаче первого множества информационных битов со вторым множеством CRC или при обработке приема такой передачи, первый CRC выводится из всех информационных битов, в то время как второй CRC выводится из подмножества информационных битов. Как показано на фиг. 20, CRC транспортного блока не вычисляется до сегментации на кодовые блоки. Транспортный блок 2001 сегментируется на три кодовых блока. CRC кодового блока вычисляется для каждого из трех кодовых блоков. CB0_CRC 2009 вычисляется из битов в кодовом блоке 0 2003; CB1_CRC 2011 выводится из битов кодового блока 1 2005; CB2_CRC 2013 выводится из битов кодового блока 0 2003, кодового блока 1 2005 и кодового блока 2 2007. CB0_CRC 2009 может быть использован для остановки итераций турбодекодирования или обнаружения ошибок для кодового блока 0 2003; CB1_CRC 2011 может быть использован для остановки итераций турбодекодирования или обнаружения ошибок для кодового блока 1 2005; а CB2_CRC 2013 может быть использован для остановки итерации турбодекодирования и обнаружения ошибок кодового блока 2 2007. В то же время CB2_CRC 2013 обеспечивает обнаружение ошибок для целого транспортного блока.

В последующих вариантах осуществления проиллюстрируем, как могут быть использованы схемы на основе регистра сдвига с линейной обратной связью (LFSR) для эффективного вычисления множества CRC для множества информационных битов. Отметим, что хотя мы используем генерирование CRC на стороне передатчика для целей иллюстрации, для специалиста в данной области техники будет просто применить эти способы к обработке приемника. Ради удобства, мы предполагаем, что схема вычисления CRC проинициализирована состоянием из всех нулей.

Идеи, раскрытые в данном изобретении, могут применяться, тем не менее, когда первоначальное состояние LFSR установлено в ненулевое состояние.

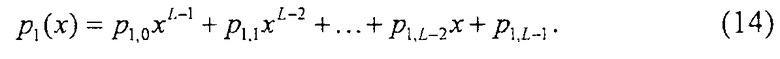

В седьмом варианте осуществления согласно принципам настоящего изобретения первое множество CRC для первого множества информационных битов может быть вычислено рекурсивно одной единственной схемой вычисления CRC. Вычислим один CRC, а именно CB0_CRC, и присоединим его к первому кодовому блоку. CB0_CRC может быть выведен из некоторых или всех битов в первом кодовом блоке. Обозначим CB0_CRC посредством

Один пример вычисления CB0_CRC состоит в нахождении остатка от деления b 0 (x)·x L на полином g(x) генерации CRC, в котором p 0 (x) может быть представлен как

где q 0 (x) - частное от деления b 0 (x)·x L на g(x). Вычислим другой CRC, а именно CB1_CRC, и присоединим его ко второму кодовому блоку. CB1_CRC может быть выведен из битов в первом кодовом блоке и битов во втором кодовом блоке. Обозначим CB1_CRC посредством

Другими словами, CB1_CRC является остатком от деления (b 0 (x)-x B1 +b 1 (x))·x L на полином g(x) генерации CRC, в котором p 1 (x) может быть представлен как

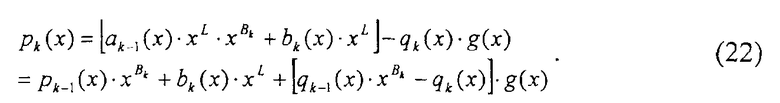

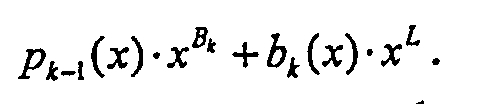

где q 1 (x) - частное от деления (b 0 (x)-x B1 +b 1 (x))·x L на g(x). Посредством выведения CB1_CRC на основе информационных битов в первом кодовом блоке и информационных битов во втором кодовом блоке, мы уменьшаем возможность неправильного обнаружения, поскольку CB1_CRC может быть использован для обнаружения ошибки в первом кодовом блоке и втором кодовом блоке. Сходным образом, CRC для k-го кодового блока может быть вычислен как остаток от деления a k (x)·x L на g(x). Другими словами,

где q 0 (x) - частное от деления a k (x)·x L на g(x). Отметим, что

Этот способ вычисления CRC хорошо сводится к простому способу вычисления CRC. CRC для k-го кодового блока может быть представлен как

Другими словами, CRC a

k

(x) такой же, как CRC  .

.

Один пример схемы для рекурсивного вычисления CRC p i (x), i=0, 1,..., C-1 показан на фиг. 21. Как показано на фиг. 21, схема для вычисления CRC сконструирована с входным портом 2109 для приема информационных данных, выходным портом 2111 для вывода информационных данных и CRC, модулем 2100 регистров сдвига с линейной обратной связью (LFSR), подключенным с возможностью связи между входным портом 2109 и выходным портом 2111. Модуль 2100 LFSR включает в себя L регистров 2115 сдвига, L вентилей 2113 "И" (AND) (представленных символами «x», окруженными окружностями) и L вентилей 2117 "Исключающее ИЛИ" (XOR) (представленных символами «+», окруженными окружностями). Модуль 2119 регистров проверки циклически избыточным кодом подключен между входным портом 2109 и модулем 2100 LFSR. Модуль 2119 регистров проверки циклически избыточным кодом включает в себя L регистров проверки циклически избыточным кодом. Первый переключатель 2101 расположен между входным портом 2109 и модулем 2119 регистров проверки циклически избыточным кодом. Первый переключатель имеет положение X для подключения входного порта 2109 к модулю 2119 регистров проверки циклически избыточным кодом, и положение Y для отключения входного порта 2109 от модуля 2119 регистров проверки циклически избыточным кодом. Второй переключатель 2103 расположен в контуре обратной связи модуля 2100 LFSR. Второй переключатель 2103 имеет положение X для подключения контура обратной связи модуля 2100 LFSR, и положение Y для отключения контура обратной связи модуля 2100 LFSR. Третий переключатель 2105 расположен между модулями 2100 LFSR и модулем 2119 регистров проверки циклически избыточным кодом. Третий переключатель 2105 имеет положение X для отключения модуля 2100 LFSR от модуля 2119 регистров проверки циклически избыточным кодом и положение Y для подключения модуля 2100 LFSR к модулю 2119 регистров проверки циклически избыточным кодом. Четвертый переключатель 2107 расположен между входным портом 2109, модулем 2100 LFSR и выходным портом 2111. Четвертый переключатель 2107 имеет положение X для подключения входного порта 2109 к выходному порту 2111 и положение Y для подключения модуля 2100 LFSR к выходному порту 2111. Переключатели могут быть любыми современными электронными переключателями, такими как, например, любые современные полевые транзисторы (FET). Соответствующая процедура для эксплуатации схемы, показанной на фиг. 21, очерчена следующим образом.

Проинициализировать модуль 2100 LFSR состоянием из всех нулей; установить k=0; проинициализировать регистры CRC нулями; установить все переключатели 2101, 2103, 2105 и 2107 в положение X.

Ввести b k (x) в схему по одному биту за раз. Отметим, что в отношении LFSR также выполнялся однократный сдвиг для каждого вводимого бита.

Переключить все переключатели 2101, 2103, 2105 и 2107 в положение Y.

Выполнить L-кратный сдвиг в отношении модуля 2100 LFSR и регистров CRC для вывода p k (x), который является L-битным CRC.

Сбросить модуль 2100 LFSR в состояние из всех нулей; Переключить все переключатели в положение X.

Увеличить k.

Если k<С, перейти на шаг 2.

CRC, присоединяемый к k-му кодовому блоку, может быть представлен уравнением 20:  .

.

Другими словами, CRC k-го кодового блока вычисляется на основе информационных битов k-го кодового блока и всех предшествующих кодовых блоков. Как можно видеть, вычисление CRC кодового блока аналогично вычислению CRC транспортного блока, за исключением того, что после ввода каждого кодового блока в схему CRC должен быть сохранен и добавлен обратно в некоторой точке в вычислении CRC для следующего кодового блока. В этом способе можно избежать отдельных схем и дополнительной сложности вычислений для вычисления CRC кодового блока и CRC транспортного блока. Фактически CRC последнего кодового блока равен CRC транспортного блока. Эта структура подходит к конвейерной структуре обработки множества кодовых блоков. В дополнение, показатель неправильного обнаружения для транспортного блока гарантирован на минимальном уровне. Отметим, что уравнение (20) подходит только для случая, когда вычисляется CRC k-го кодового блока на основе информационных битов k-го кодового блока и всех предыдущих кодовых блоков.

В качестве альтернативы, другой пример схемы для рекурсивного вычисления CRC p i (x), i=0, 1,..., C-1 показан на фиг. 22 согласно восьмому варианту осуществления принципов настоящего изобретения. Как показано на фиг. 22, схема сконструирована с входным портом 2215 для приема информационных данных, выходным портом 2217 для вывода информационных данных и CRC, модулем 2200 регистров сдвига с линейной обратной связью (LFSR), подключенным с возможностью связи между входным портом 2215 и выходным портом 2217. Модуль 2200 LFSR включает в себя L регистров. Схема построена дополнительно с L регистрами 2213 состояния, подключенными к соответствующим регистрам из L регистров сдвига для записи и чтения значений данных в или из L регистров сдвига. Первый переключатель 2201 расположен между входным портом 2215 и модулем 2200 LFSR. Первый переключатель 2201 имеет положение X для подключения входного порта 2215 и модуля 220 LFSR и положение Y для отключения входного порта 2215 и модуля 2200 LFSR. Второй переключатель 2203 расположен в контуре обратной связи модуля 2200 LFSR. Второй переключатель 2203 имеет положение X для подключения контура обратной связи модуля 2200 LFSR и положение Y для отключения контура обратной связи модуля 2200 LFSR. Третий переключатель 2205 расположен между входным портом 2215, модулем 2200 LFSR и выходным портом 2217. Третий переключатель 2205 имеет положение X для подключения входного порта 2215 к выходному порту 2217 и положение Y для подключения модуля 2200 LFSR к выходному порту 2217. Эта схема достигает того же вычисления CRC, что и схема, показанная на фиг. 21. Соответствующая процедура очерчивается следующим образом.

Проинициализировать модуль 2200 LFSR состоянием из всех нулей; установить k=0; проинициализировать регистры 2213 состояния нулями; установить все переключатели 2201, 2203 и 2205 в положение X.

Ввести b k (x) в схему через входной порт 2215 по одному биту за раз. Отметим, что в отношении LFSR также выполняется однократный сдвиг для каждого вводимого бита.

Записать значение регистров сдвига в модуле 2200 LFSR в соответствующие регистры 2213 состояния; переключить все переключатели 2201, 2203 и 2205 в положение Y.

Выполнить L-кратный сдвиг в отношении модуля 2200 LFSR для вывода p k (x), который является L-битным CRC.

Переключить все переключатели 2201, 2203 и 2205 в положение X; записать значение регистров 2213 состояния в соответствующие регистры сдвига в модуле 2200 LFSR.

Увеличить k.

Если k<С, перейти на шаг 2.

Другим способом вычисления CRC для нескольких кодовых блоков является использование двух LFSR согласно девятому варианту осуществления принципов настоящего изобретения. Как показано на фиг. 23, схема сконструирована с входным портом 2311 для приема информационных данных, выходным портом 2313 для вывода информационных данных и результатов проверки циклически избыточным кодом, первым модулем 2300 LFSR, подключенным между входным портом 2311 и выходным портом 2313 и включающим в себя L регистров сдвига, вторым модулем 2301 LFSR, подключенным между входным портом 2311 и выходным портом 2313, находящимся в параллельном подключении с первым модулем 2300 LFSR и содержащим L регистров сдвига. Первый переключатель 2303 расположен между входным портом 2311 и общей точкой 2317 подключения между первым и вторым модулями 2300 и 2301 LFSR. Первый переключатель имеет положение X для подключения входного порта 2311 к общей точке 2317 подключения, и положение Y для отключения входного порта 2311 от общей точки 2317 подключения. Второй переключатель 2305 расположен в контуре обратной связи модуля 2300 LFSR.

Второй переключатель 2305 имеет положение X для подключения контура обратной связи первого модуля 2300 LFSR и положение Y для отключения контура обратной связи первого модуля 2300 LFSR. Первый переключатель 2307 расположен между входным портом 2311, общей точкой 2317 подключения между первым и вторым модулями 2300 и 2301 LFSR и выходным портом 2313. Третий переключатель 2307 имеет положение X для подключения входного порта 2311 к выходному порту 2313, положение Y для подключения первого модуля 2300 LFSR и выходного порта 2313 и положение Z для подключения второго модуля 2301 LFSR и выходного порта 2313. Второй переключатель 2309 расположен в контуре обратной связи модуля 2301 LFSR. Второй переключатель 2309 имеет положение X для подключения контура обратной связи первого модуля 2301 LFSR и положение Z для отключения контура обратной связи первого модуля 2301 LFSR. Данный способ может быть очерчен следующим образом:

Проинициализировать первый модуль 2300 LFSR и второй модуль 2301 LFSR состоянием из всех нулей; установить k=0; установить все переключатели 2303, 2305 и 2309 в положение X.

Ввести b k (x) в схему через входной порт 2311 по одному биту за раз. Отметим, что в отношении и первого модуля 2300 LFSC, и второго модуля 2301 LFSR также выполняется однократный сдвиг для каждого вводимого бита.

Переключить первый переключатель 2303 в положение Y.

Если k=C-1, перейти к шагу 8; в противном случае, переключить переключатели 2305 и 2307 в положение Y.

Выполнить L-кратный сдвиг в отношении первого модуля 2300 LFSR для вывода p k (x), который является L-битным CRC для k-го кодового блока.

Переключить переключатели 2303, 2305 и 2307 в положение X; сбросить первый модуль 2300 LFSR.

Увеличить k, перейти на шаг 2.

Переключить переключатели 2305 и 2307 в положение Z.

Выполнить L-кратный сдвиг в отношении второго модуля 2301 LFSR для получения p C-1 (x), который является L-битным CRC для последнего кодового блока.

Этот способ вычисляет CRC k-го кодового блока только на основании информационных битов в k-м кодовом блоке за исключением последнего кодового блока. Следовательно, CRC k-го кодового блока кроме CRC последнего кодового блока может быть представлен посредством

где C - общее количество кодовых блоков. CRC последнего кодового блока вычисляется посредством LFSR2 и выводится из информационных битов во всех кодовых блоках. Следовательно, CRC последнего кодового блока может быть представлен как

Другим способом является вставка L нулей в положениях битов для всех CRC кодовых блоков в сообщение a(x) до ввода a(x) в схему вычисления CRC согласно десятому варианту осуществления принципов настоящего изобретения. Пример этого варианта осуществления проиллюстрирован на фиг. 24. Схема построена с входным портом 2407 для приема информационных данных, выходным портом 2409 для вывода информационных данных и CRC и модулем 2400 LFSR, подключенным между входным портом 2407 и выходным портом 2409 и включающим в себя L регистров сдвига для преобразования информационных данных с использованием полинома g(x) степени L-1 для генерирования результатов проверки циклически избыточным кодом. Первый переключатель 2401 расположен между входным портом 2407 и модулем 2400 LFSR. Первый переключатель 2401 имеет положение X для подключения входного порта 2407 к модулю 2400 LFSR и положение Y для отключения входного порта 2407 от модуля 2407 LFSR. Второй переключатель 2403 расположен в контуре обратной связи модуля 2400 LFSR. Второй переключатель 2403 имеет положение X для подключения контура обратной связи модуля 2400 LFSR и положение Y для отключения контура обратной связи модуля 2400 LFSR. Третий переключатель 2405 расположен между входным портом 2407, модулем 2400 LFSR и выходным портом 2409. Третий переключатель 2405 имеет положение X для подключения входного порта 2407 к выходному порту 2409 и положение Y для подключения модуля 2400 LFSR к выходному порту 2409. Отметим, что L нулей добавляются неявно посредством изменения положений переключателей из X в Y для L сдвигов. Существенно в данном случае то, что мы позволяем, чтобы первоначальное состояние LFSR было зависимо от предыдущих кодовых блоков и поэтому разрешаем текущему CRC защищать биты в текущем кодовом блоке и предыдущих кодовых блоках. Данный способ может быть очерчен следующим образом.

Проинициализировать модуль 2400 LFSR состоянием из всех нулей; установить k=0; установить все переключатели 2401, 2403 и 2405 в положение X.

Ввести b k (x) в схему через входной порт 2407 по одному биту за раз. Отметим, что в отношении LFSR также выполняется однократный сдвиг для каждого вводимого бита.

Переключить все переключатели 2401, 2403 и 2405 в положение Y.

Выполнить L-кратный сдвиг в отношении модуля 2400 LFSR для получения p k (x), который является L-битным CRC для k-го кодового блока.

Переключить все переключатели в положение X.

Увеличить k.

Если k<С, перейти на шаг 2.

Хотя изобретение было показано и описано в связи с предпочтительными вариантами осуществления, специалисту в данной области техники будет очевидно, что могут быть выполнены модификации и разновидности без отхода от сущности и объема изобретения, как определено прилагаемой формулой изобретения.

Изобретение относится к способам и устройствам для генерирования результатов проверки циклически избыточным кодом для множества кодовых блоков. Техническим результатом является создание улучшенных способов и устройств для генерирования результатов проверки циклически избыточным кодом для множества кодовых блоков в системе связи для обнаружения ошибок в системе связи. Указанный технический результат достигается тем, что способ генерирования результатов проверки циклически избыточным кодом (CRC) в отношении информационных битов и передачи этих информационных битов со сгенерированными CRC в системе связи содержит этапы, на которых вычисляют CRC транспортного блока для транспортного блока, включающего в себя множество информационных битов; сегментируют транспортный блок, включающий в себя CRC транспортного блока, на множество подмножеств; вычисляют множество CRC для этого множества подмножеств; и передают упомянутое множество подмножеств и упомянутое множество CRC для данного множества подмножеств. 7 н. и 11 з.п. ф-лы, 24 ил.

1. Способ генерирования результатов проверки циклически избыточным кодом (CRC) в отношении информационных битов и передачи этих информационных битов со сгенерированными CRC в системе связи, содержащий этапы, на которых

вычисляют CRC транспортного блока для транспортного блока, включающего в себя множество информационных битов;

сегментируют транспортный блок, включающий в себя CRC транспортного блока, на множество подмножеств;

вычисляют множество CRC для этого множества подмножеств; и

передают упомянутое множество подмножеств и упомянутое множество CRC для данного множества подмножеств.

2. Способ по п.1, в котором на этапе вычисления множества CRC для множества подмножеств вычисляют n-й CRC на основе n-го подмножества упомянутых информационных битов.

3. Способ по п.1, в котором на этапе вычисления множества CRC по меньшей мере один CRC среди упомянутого множества CRC вычисляют на основе упомянутого множества подмножеств.

4. Способ по п.1, в котором на этапе вычисления множества CRC последний CRC среди упомянутого множества CRC вычисляют на основе последнего подмножества, включающего в себя CRC транспортного блока.

5. Способ по п.1, дополнительно содержащий этап, на котором совместно кодируют упомянутое множество подмножеств информационных битов посредством конкретного типа кода с прямым исправлением ошибок.

6. Способ по п.5, в котором упомянутый конкретный тип кода с прямым исправлением ошибок содержит турбокод.

7. Способ по п.1, дополнительно содержащий этап, на котором совместно кодируют упомянутое множество подмножеств и по меньшей мере один CRC, который вычисляется на основе упомянутого множества подмножеств.

8. Способ по п.1, в котором подмножества из упомянутого их множества перекрываются друг с другом.

9. Способ по п.6, в котором подмножества из упомянутого их множества отделены друг от друга.

10. Способ по п.1, в котором по меньшей мере одно подмножество среди упомянутого множества подмножеств содержит по меньшей мере одно из других подмножеств.

11. Способ по п.1, в котором по меньшей мере один CRC среди упомянутого множества CRC вычисляют на основе всех из упомянутых информационных битов.

12. Способ по п.1, в котором каждый из упомянутого множества CRC вычисляют на основе сочетания соответствующего одного из упомянутого множества подмножеств и других подмножеств, которые продолжают это соответствующее подмножество.

13. Схема для генерирования результатов проверки циклически избыточным кодом при передаче данных, содержащая:

входной порт для приема информационных данных;

выходной порт для вывода информационных данных и результатов проверки циклически избыточным кодом;

модуль регистров сдвига с линейной обратной связью, подключенный между входным и выходным портами и содержащий L регистров сдвига для преобразования информационных данных при помощи полинома g(x) генерирования результатов проверки циклически избыточным кодом, имеющего степень L-1;

модуль регистров проверки циклически избыточным кодом, подключенный между входным портом и модулем регистров сдвига с линейной обратной связью и содержащий L регистров проверки циклически избыточным кодом;

первый переключатель, подключенный между входным портом и модулем регистров проверки циклически избыточным кодом;

второй переключатель, подключенный в контуре обратной связи модуля регистров сдвига с линейной обратной связью;

третий переключатель, подключенный между модулем регистров сдвига с линейной обратной связью и модулем регистров проверки циклически избыточным кодом;

четвертый переключатель, подключенный между входным портом, модулем регистров сдвига с линейной обратной связью и выходным портом и имеющий первое положение для подключения входного порта к выходному порту и второе положение для подключения модуля регистров сдвига с линейной обратной связью к выходному порту; и

при этом выполняется управление переключателями с первого по четвертый для последовательного выполнения первой операции инициализации модуля регистров сдвига с линейной обратной связью и модуля регистров проверки циклически избыточным кодом в состояние из всех нулей, второй операции последовательного ввода кодового блока информационных битов через входной порт, третьей операции L-кратного сдвига в отношении модуля регистров сдвига с линейной обратной связью для получения результатов проверки циклически избыточным кодом для этого кодового блока, и четвертой операции сброса модуля регистров сдвига с линейной обратной связью в состояние из всех нулей.