Изобретение относится к радиотехнике и связи, в частности к многоканальной передаче информации с использованием временного разделения каналов, и может найти применение при создании цифровых систем связи.

Известны способы селекции циклового синхронизирующего сигнала в системах передачи цифровой информации с временным разделением каналов, в соответствии с которыми осуществляют поиск сосредоточенной синхрогруппы во входном информационном потоке по априори известной эталонной синхрогруппе и известном периоде ее следования [1] .

Недостатком известных способов является ограниченная область применения, поскольку отсутствует возможность сихронного приема информации поочередно от нескольких источников сообщений, различающихся структурой цикла.

Наиболее близким по технической сущности к изобретению является способ селекции циклового синхронизирующего сигнала, в соответствии с которым на передающей стороне формируют информационные группы, в начале каждой из которых размещают синхрогруппу с числом символов, равным n, передают сформированную последовательность в виде биполярных импульсов по каналу связи, на приемной стороне выделяют синхрогруппу и формируют сигналы начала и окончания информационной группы [2] .

Однако известный способ обладает низкой точностью селекции циклового синхронизирующего сигнала. Этот недостаток обусловлен тем, что известный способ не позволяет выделять синхрогруппу из группового цифрового сигнала в том случае, если заранее не известен ее код и период следования.

Известно устройство цикловой синхронизации, содержащее регистр, блок сравнения и логические элементы И, НЕ [1] . Недостатком этого устройства являются ограниченные функциональные возможности.

Наиболее близким по технической сущности к предложенному является устройство цикловой синхронизации, содержащее регистр, блок управления, коммутатор, анализатор, делитель и решающий узел [2] . Недостатком известного устройства является низкая точность селекции циклового синхронизирующего сигнала, поскольку структура устройства обеспечивает работу только с априори известными параметрами синхрогруппы.

Цель изобретения - повышение точности селекции циклового синхронизирующего сигнала.

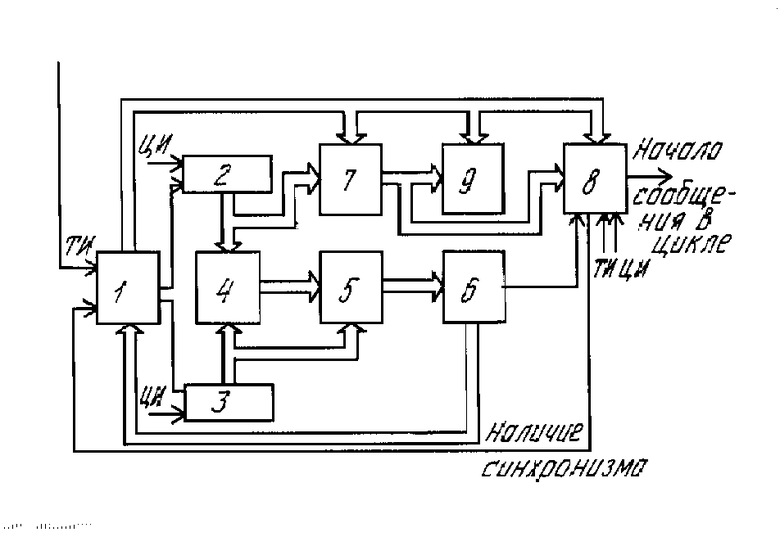

На чертеже представлена структурная схема устройства для выделения циклового синхронизирующего сигнала.

Способ выделения циклового синхронизирующего сигнала в системах передачи цифровой информации с временным разделением каналов заключается в следующем.

На передающей стороне циклически формируют последовательность двоичных сигналов сообщения, в начале которой размещают последовательность из n двоичных сигналов синхронизации (синхрогруппу), причем n = const для различных по своей структуре циклов. Сформированную таким образом последовательность двоичных сигналов передают по каналу связи, при этом число элементов в сообщении не превышает предельного значения Lmax, Lmax >3n - 1.

На приемной стороне запоминают в качестве первой эталонной синхрогруппы n первых входных двоичных сигналов, после чего в каждом из Lmax последующих тактов следования входных сигналов запоминают (i+1) эталонных синхрогрупп, состоящих из n принятых последними входных двоичных сигналов каждая, где i = 1,2. . . , j, . . . , Lmax. Затем в каждом из (Lmax + 2) последующих тактов следования входных двоичных сигналов сравнивают поразрядно каждую из полученных (Lmax + 1) эталонных синхрогрупп с входной последовательностью двоичных сигналов.

При совпадении j-й эталонной синхрогруппы с n следующими подряд двоичными сигналами входной последовательности (при условии, что дискретное значение по крайней мере одного из этих сигналов отлично от нуля) формируют импульсный сигнал. После этого на протяжении (2n-2) последующих тактов входной последовательности подсчитывают количество (Q) формируемых импульсных сигналов при условии, что каждый последующий (j+k) импульсный сигнал сформирован в результате совпадения n следующих подряд двоичных сигналов входной последовательности с (j+k) эталонной синхрогруппой, где k = = 1,2, . . . , (2n-2).

Если число Q cформированных импульсных сигналов оказалось равным Q = 2n - 2, то запоминают [j+(n-1)] -ю эталонную синхрогруппу в качестве искомой. После этого определяют длину цикла по числу тактов входной последовательности в интервале между появлениями двух импульсных сигналов, соответствующих совпадению [j + (n-1)] эталонной синхрогруппы с синхрогруппой во входной последовательности. В результате выполненных операций селектируется искомая синхрогруппа и определяется период ее следования (длина цикла), что впоследствии используется для поддержания цикловой синхронизации приема цифровой информации любыми известными способами.

Если же число Q сформированных импульсных сигналов после ( Lmax+ 1) тактов входной последовательности оказалось

Q <2n - 2, то процесс селекции циклового синхронизирующего сигнала повторяют заново, начиная с запоминания ( Lmax + 1) эталонных синхрогрупп. Это исключает "зависание" процесса выделения при отсутствии входной последовательности.

Таким образом, способ выделения циклового синхронизирующего сигнала обеспечивает точную селекцию искомой синхрогруппы при априори неизвестных коде синхрогруппы и длине цикла.

На чертеже приведена структурная схема устройства для осуществления предложенного способа.

В состав устройства входят блок управления 1, регистры 2 и 3, блок сравнения 4, блок селекции 5, блок накопителей 6, многоканальный мультиплексор 7, блок фазирования 8, дешифратор 9 номера синхрогруппы.

Устройство для выделения циклового синхронизирующего сигнала работает следующим образом.

На вход устройства поступают тактовые импульсы (ТИ) и цифровая информация (ЦИ). Блок управления 1 управляет записью ЦИ в регистр 2, а затем открывает регистр 3 для прохождения через него входного потока ЦИ. В процессе продвижения входного потока ЦИ через регистр 3 в блоке сравнения 4 происходит посимвольное сравнение эталонных синхрогрупп, хранящихся в регистре 2 с входной ЦИ, проходящей через регистр 3. При совпадении какой-либо эталонной синхрогруппы на выходе блока сравнения 4 появляется импульсный сигнал, по которому осуществляется идентификация данной группы. Указанная синхрогруппа в блоке селекции 5 проверяется (путем сравнения) на наличие в ней по крайней мере одного сигнала, дискретный уровень которого отличен от нуля.

При положительном результате на выходе блока селекции 5 появляется импульсный сигнал, который поступает на вход блока накопителей.

В блоке накопителей 6 подсчитывается число Q импульсных сигналов. Как только число импульсных сигналов достигает порогового значения, на выходе блока 6 появляются соответствующий сигнал превышения и код номера [j + (n-1)-й эталонной синхрогруппы.

Блок управления 1 преобразует код с выхода блока накопителей 6 в код управления многоканальным мультиплексором 7, который пропускает на выход код искомой синхрогруппы. Селектированная таким образом синхрогруппа запоминается в блоке фазирования 8 и может быть дешифрована с помощью дешифратора 9 номера синхрогруппы.

При появлении первого импульсного сигнала с выхода блока 6 накопителей в блоке 8 фазирования начинается отсчет числа тактов до следующего появления искомой синхрокомбинации, при появлении которой полученное значение длины цикла преобразуется в код длины цикла и запоминается в блоке 8. По найденным синхрокомбинации и длине цикла блок 8 осуществляет цикловое фазирование приема ЦИ в текущем сеансе связи и формирует при этом сигналы начала кодовой комбинации сообщения в цикле и наличия синхронизма. При попадании синхронизма блок управления вырабатывает соответствующие управляющие воздействия и работа устройства повторяется.

Таким образом, при использовании изобретения обеспечивается выделение цикловой синхрогруппы и определяется период ее следования. Это позволяет обеспечивать цикловую синхронизацию при априори неизвестной длине цикла и коде синхрогруппы, что повышает эффективность использования канала связи за счет исключения необходимости в организации дополнительного канала для передачи управляющей информации. (56) Е. М. Мартынов. Синхронизация в системах передачи дискретных сообщений. М. : Связь, 1972, с. 86-114.

М. Н. Колтунов и др. Синхронизация по циклам в цифровых системах связи. М. ; Связь, 1980, с. 138-147.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010437C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ ПО ВОКОДЕРНОМУ ТРАКТУ | 1991 |

|

RU2010439C1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1985 |

|

SU1286089A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| КОРРЕЛЯЦИОННЫЙ РАСХОДОМЕР | 1991 |

|

RU2010167C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ О СОСТОЯНИИ КОНТРОЛИРУЕМЫХ ПУНКТОВ И ТЕЛЕМЕХАНИЧЕСКАЯ СИСТЕМА "ЛИЛАНА" ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2010338C1 |

| ЦИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010239C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

Использование: для передачи информации с помощью двоичных сигналов, а именно для синхронизации источников и приемников сообщений в системах связи с многостанционным доступом. Сущность изобретения: на передающей стороне формирование длительности синхроцикла в текущем сеансе связи кодовых комбинаций сообщения осуществляют с разным числом символов для различных сеансов связи, а кодовые группы синхронизирующей информации выполняют различными для различных сеансов связи. На приемной стороне перед выделением кодовой группы синхронизирующей информации сначала определяют ее вид и длину цикла. Найденные параметры запоминаются и затем используются в текущем сеансе связи для поддержания цикловой синхронизации. Устройство для осуществления способа содержит блок управления 1, регистры 2 и 3, блок сравнения 4, блок селекции 5, блок накопителей 6, многоканальный мультиплексор 7, блок фазирования 8, дешифратор 9 номера синхрогруппы. 2 п. ф-лы. 1 ил.

СПОСОБ ВЫДЕЛЕНИЯ ЦИКЛОВОГО СИНХРОНИЗИРУЮЩЕГО СИГНАЛА В СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

1. Способ выделения циклового синхpонизиpующего сигнала в системах пеpедачи цифpовой инфоpмации с вpеменным pазделением каналов, заключающийся в том, что на пеpедающей стоpоне циклически с заданной тактовой частотой фоpмиpуют последовательность двоичных сигналов, состоящую из последовательности двоичных сигналов сообщения, пеpед котоpой фоpмиpуют последовательность из n двоичных сигналов цикловой синхpонизации, где n = const для pазличных сеансов связи и текущего вpемени пеpедачи сообщения, и пеpедают сфоpмиpованную последовательность двоичных сигналов по каналу связи, а на пpиемной стоpоне пpинимают последовательности двоичных сигналов и выделяют из них последовательность из n двоичных сигналов цикловой синхpонизации, отличающийся тем, что на пpиемной стоpоне пеpед выделением последовательности из n двоичных сигналов цикловой синхpонизации запоминают на интеpвале (Lmax + n) тактов (Lmax + 1) последовательностей по n двоичных сигналов в каждой, сдвинутых дpуг относительно дpуга на один такт, где L max > 3n - пpедельное число элементов в последовательности двоичных сигналов сообщения, в каждом последующем такте поpазpядно сpавнивают каждую из (Lmax + 1) запомненных последовательностей по n двоичных сигналов с пpинимаемой последовательностью двоичных сигналов, пpичем поpазpядное сpавнение осуществляют на последующем интеpвале (Lmax + n) тактов, фоpмиpуют импульсный сигнал пpи поpазpядном совпадении двоичных сигналов j-й последовательности двоичных сигналов, где 1 ≅ j ≅ Lmax + 1 из (Lmax + 1) запомненных последовательностей по n двоичных сигналов с n соответствующими двоичными сигналами пpинимаемой последовательности пpи условии, что по кpайней меpе один из совпавших двоичных сигналов отличен от нуля, пpи этом одновpеменно на интеpвале 2 (n - 1)-х тактов опpеделяют число q фоpмиpуемых импульсных сигналов и пpи q = 2(n + 1) опpеделяют искомую последовательность из n двоичных сигналов цикловой синхpонизации по [j + (n - 1)] -й последовательности двоичных сигналов из (Lmax + 1) запомненных последовательностей, а длину цикла опpеделяют по числу тактов между двумя соседними импульсными сигналами, соответствующими совпадению n двоичных сигналов пpинимаемой последовательности двоичных сигналов с последовательностью из n двоичных сигналов из (Lmax + 1) запомненных последовательностей, а пpи q < 2(n - 1) повтоpяют пpоцесс выделения сигналов цикловой синхpонизации, начиная с запоминания (Lmax + 1) последовательностей по n двоичных сигналов в каждой на следующем интеpвале (Lmax + n) тактов поступления пpинимаемой последовательности двоичных сигналов.

Авторы

Даты

1994-03-30—Публикация

1991-10-31—Подача