Изобретение относится к устройствам переключения и контроля исправности цепей управления систем управления, контроля, устройства связи и других устройств различных отраслей техники.

Известно релейное устройство для распределения импульсов тока, описанное, например, в [1], содержащее контрольные электромагнитные реле с рабочими обмотками, одна из которых включена последовательно с управляемой цепью. Число реле определяется числом управляемых цепей. Каждое реле представляет собой наращиваемый модуль. Устройство позволяет выяснить исправность цепи управления и в случае ее неисправности переключать управляющий сигнал на следующую исправную цепь.

К недостаткам такого устройства следует отнести низкое быстродействие, большое энергопотребление, а также значительную массу и размеры.

Известно также контрольно-распределительное многоразрядное релейное устройство, описанное, например, в [2], содержащее контрольное электромагнитное реле, обмотки которого включены последовательно в цепь нагрузки, и блокировочное электромагнитное реле, блокирующее в выключенном состоянии контрольное реле. Число пар реле определяется числом управляемых цепей. Каждая пара реле представляет собой наращиваемый модуль. Устройство позволяет выяснить исправность цепи управления и в случае ее неисправности переключать управляющий сигнал на следующую исправную цепь.

К недостаткам такого устройства также следует отнести низкое быстродействие, большое энергопотребление, значительную массу и размеры.

В качестве прототипа принято устройство, описанное в [2].

Целью настоящего изобретения является повышение быстродействия устройства, снижение его энергопотребления, массы и размеров.

Поставленная цель достигается тем, что контрольно-распределительное устройство образовано последовательно включенными ячейками /модулями/, реализованными на триггерах и логических элементах. Каждая ячейка содержит I-K-триггер и цепь контрольного тока, пропускаемого с инверсного выхода I-K-триггера на исполнительное устройство через резистор и диод.

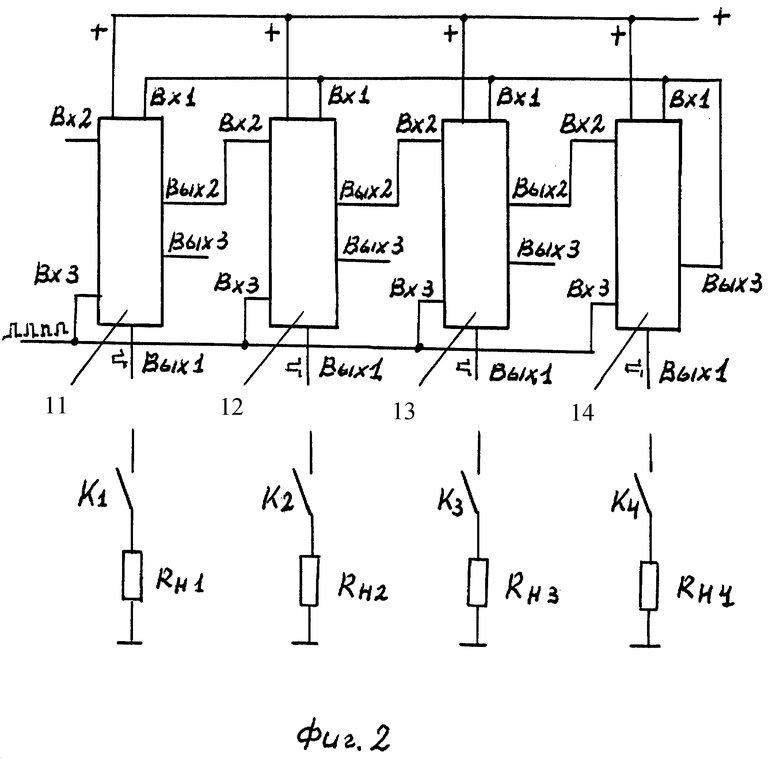

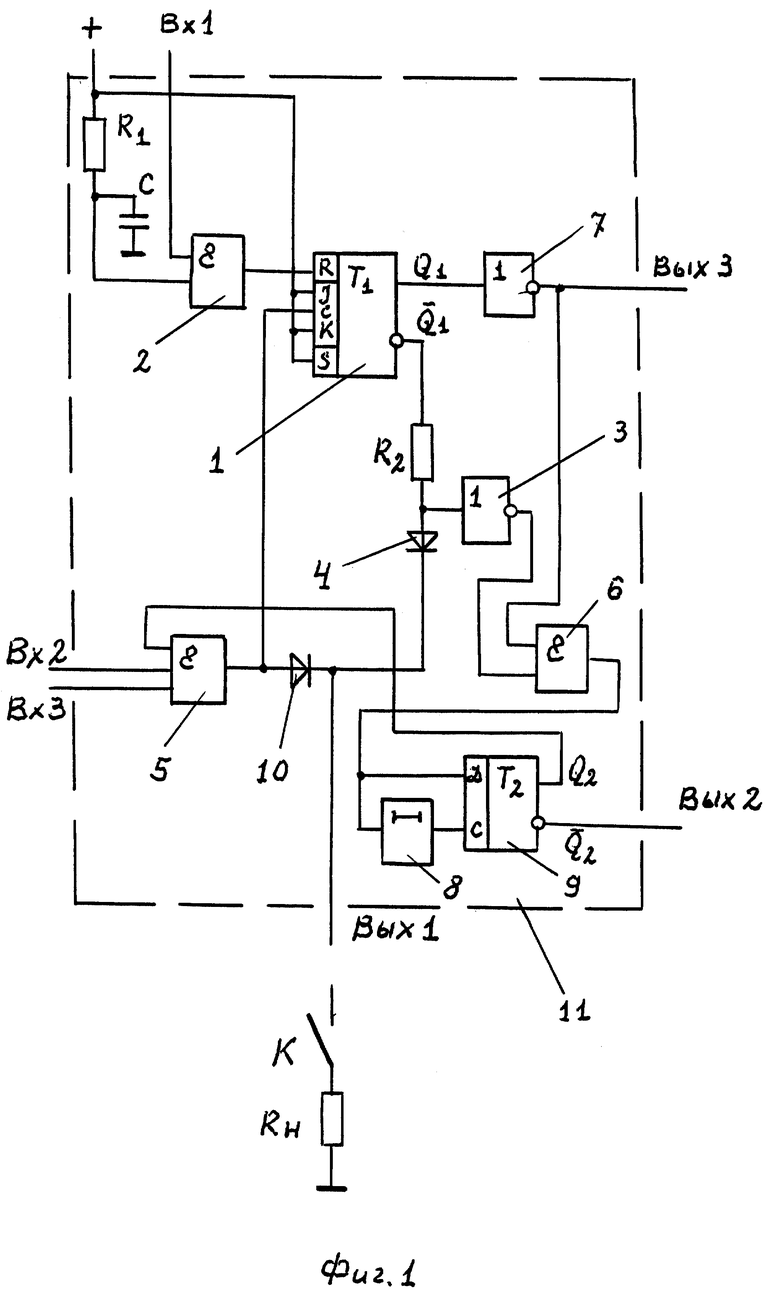

Сущность изобретения поясняется чертежами, где на фиг. 1 приведена схема ячейки /модуля/ контрольно-распределительного устройства, а на фиг. 2 - структура контрольно-распределительного устройства, например, на четыре канала распределения.

Контрольно-распределительное устройство представляет собой последовательный наращиваемый ряд ячеек /модулей/. Ячейка /фиг. 1/ содержит четыре входа и три выхода: I-K-триггер T1 1, к установочному входу R которого подсоединен первый двухвходовый элемент n2, к первому входу которого подсоединен вход Bx1 ячейки, а ко второму - первый резистор R1 и конденсатор C, подсоединенный второй стороной к общему минусу источника питания. К входу "+" /для источника питания/ подсоединены второй стороной первый резистор R1, информационные входы I и K и установочный вход S I-K-триггера 1. К инверсному выходу I-K-триггера подсоединен второй резистор R2, к которому в свою очередь подсоединен второй элемент НЕ 3 и анод первого диода 4, катод которого подсоединен к первому выходу Вых1 ячейки. Выход второго элемента НЕ 3 соединен со вторым входом двухвходового элемента n 6, первый вход которого соединен с выходом Вых 3 ячейки и выходом первого элемента НЕ 7, вход которого соединен с прямым выходом Q1 I-K-триггера T1 1. Выход двухвходового элемента И 6 соединен с входом D, а через линию задержки 8 - с синхровходом C D-триггера T2 9, прямой выход Q2 которого соединен с первым входом трехвходового элемента И 5, а инверсный выход  соединен с выходом Вых 2 ячейки. Второй вход трехвходового элемента И 5 соединен со входом Вх 2 ячейки, третий вход - с входом Вх 3 ячейки, а выход соединен с анодом второго диода 10, катод которого соединен с выходом Вых 1 ячейки. В целях усиления мощности выходного сигнала между катодом первого диода 4 и первым выходом Вых. 1 ячейки может быть включен усилитель мощности. Для исключения срабатывания внешнего исполнительного устройства /RH/ от контрольного тока сопротивление второго резистора R2 должно превосходить сопротивление внешней нагрузки RH по меньшей мере в десять раз. Внешний выключатель K предназначен для выключения внешней нагрузки /канала/.

соединен с выходом Вых 2 ячейки. Второй вход трехвходового элемента И 5 соединен со входом Вх 2 ячейки, третий вход - с входом Вх 3 ячейки, а выход соединен с анодом второго диода 10, катод которого соединен с выходом Вых 1 ячейки. В целях усиления мощности выходного сигнала между катодом первого диода 4 и первым выходом Вых. 1 ячейки может быть включен усилитель мощности. Для исключения срабатывания внешнего исполнительного устройства /RH/ от контрольного тока сопротивление второго резистора R2 должно превосходить сопротивление внешней нагрузки RH по меньшей мере в десять раз. Внешний выключатель K предназначен для выключения внешней нагрузки /канала/.

Контрольно-распределительное устройство /фиг. 2/ содержит по меньшей мере две ячейки /модуля/. Выходы "+" всех ячеек объединены с плюсом источника питания /+/. Входы Вх 1 также объединены, к ним подсоединен выход Вых. 3 только последней ячейки, например 14. Выходы Вых. 1 ячеек соединены со своими выключателями каналов, например K1-K4, которые управляют каналами распределения со своими нагрузками, например RH1-RH4, подключенными к минусу источника питания. Входы Вх.3 объединены и используются для подключения внешнего источника управляющих сигналов. Выход Вых. 2 первой ячейки соединен со входом Вх. 2 второй ячейки 12, выход Вых.2 второй ячейки 12 соединен со входом Вх. 2 третьей ячейки 13, выход Вых. 2 третьей ячейки 13 соединен со входом Вх. 2 четвертой ячейки 14. На вход Вх. 2 первой ячейки подается постоянный потенциальный сигнал логической единицы. Использование в качестве контрольного устройства I-K-триггера в источниках не обнаружено.

Работа ячейки /модуля/ контрольно-распределительного устройства осуществляется в следующей последовательности /фиг. 1/. Перед началом работы I-K-триггер T1 1 приводится в необходимое исходное выключенное состояние. При подаче на ячейку плюса источника питания через вход "+" сигнал логической единицы поступает на входы J, K, S триггера T1 1. Первоначально на вход R этого триггера поступает сигнал логического нуля /конденсатор C разряжен/, а по мере его зарядки на входе устанавливается сигнал логической единицы /при наличии единичного сигнала на первом входе первого элемента И 2/. На прямом выходе Q1 I-K-триггера T1 1 появляется сигнал логического нуля, а на инверсном Q - логической единицы. В этом состоянии, если цепь управления нагрузкой RH не оборвана /ключ управления каналом K также не выключен/, контрольный ток протекает через второй резистор R2, первый диод 4 и нагрузку RH. Ввиду того, что R2 > 10 RH, сигнал, снимаемый с первого диода 4, лежит в области логического нуля. После инвертирования этого сигнала вторым элементом НЕ 3 сигнал поступает на второй вход второго элемента И 6. Сигнал логического нуля, снимаемый с прямого выхода Q1 I-K-триггера T1 1, после инвертирования первым элементом НЕ 7 поступает на первый вход второго элемента n 6 и выход ячейки Вых. 3. Единичный сигнал с выхода второго элемента n 6 поступает на вход D и через линию задержки 8 - на вход C D-триггера T2 9. Триггер T2 9 включается /переключается в состояние единичного сигнала на прямом выходе Q2 и нулевого - на инверсном  /. Единичный сигнал с прямого выхода Q2 D-триггера передается на первый вход трехвходового элемента n 5, на второй вход которого подается внешний потенциальный единичный логический сигнал /только у первой ячейки устройства/.

/. Единичный сигнал с прямого выхода Q2 D-триггера передается на первый вход трехвходового элемента n 5, на второй вход которого подается внешний потенциальный единичный логический сигнал /только у первой ячейки устройства/.

Ячейка готова к работе. При этом ее I-K-триггер 1 находится в выключенном состоянии, а D-триггер T2 9 - во включенном.

Если цепь управления первым исполнительным устройством /RH1 фиг. 2/ не оборвана, первый управляющий сигнал от внешнего устройства через вход Вх. 3 ячейки и через трехвходовой элемент n 5 и второй диод 10 передается на выход Вых. 1 ячейки и далее через внешний выключатель управляемой цепи K на исполнительное устройство /фиг. 1/. После окончания распределяемого сигнала I-K-триггер T1 1 включается /переключается в единичное состояние на прямом выходе Q1 и нулевого - на инверсном выходе  /. При этом отключается второй резистор R2, выход Вых. 1 ячейки и нагрузка RH. Единичный сигнал с прямого выхода Q1 I-K-триггера T1 1 подается на первый элемент НЕ 7 и в нулевом виде поступает на второй элемент n 6 и далее на входы D и C D-триггера T2 9. Триггер выключается и передает нулевой сигнал на первый вход третьего элемента n 5, закрывая его. С инверсного выхода

/. При этом отключается второй резистор R2, выход Вых. 1 ячейки и нагрузка RH. Единичный сигнал с прямого выхода Q1 I-K-триггера T1 1 подается на первый элемент НЕ 7 и в нулевом виде поступает на второй элемент n 6 и далее на входы D и C D-триггера T2 9. Триггер выключается и передает нулевой сигнал на первый вход третьего элемента n 5, закрывая его. С инверсного выхода  D-триггера T2 9 единичный сигнал передается на выход Вых. 2 ячейки и далее через вход Вх. 2 следующей ячейки на ее третий элемент n 5, подготавливая передачу второго распределяемого сигнала на второе исполнительное устройство /RH2 фиг. 2/. Таким образом, после распределения первого импульса I-K-триггер T1 1 первой ячейки остается во включенном состоянии, а D-триггер T2 9 - в выключенном /фиг. 1/. Далее распределение управляющих сигналов по выходным каналам осуществляется аналогично.

D-триггера T2 9 единичный сигнал передается на выход Вых. 2 ячейки и далее через вход Вх. 2 следующей ячейки на ее третий элемент n 5, подготавливая передачу второго распределяемого сигнала на второе исполнительное устройство /RH2 фиг. 2/. Таким образом, после распределения первого импульса I-K-триггер T1 1 первой ячейки остается во включенном состоянии, а D-триггер T2 9 - в выключенном /фиг. 1/. Далее распределение управляющих сигналов по выходным каналам осуществляется аналогично.

Если цепь управления нагрузкой оборвана или преднамеренно выключена ключом K, при подаче питания на вход "+" контрольный ток через второй резистор R2 не протекает и анод первого диода 4 находится под положительным потенциалом. Второй элемент НЕ 3 подает на второй вход второго элемента n 6 нулевой логический сигнал, который передается на вход D и через линию задержки 9 на вход C D-триггера, который выключается. Сигнал логической единицы с его инверсного выхода  передается на выход Вых. 2 ячейки и далее на вход Вх.2 следующей ячейки /фиг. 2/, подготавливая ее к передаче сигнала на следующую нагрузку RH2. Таким способом осуществляется передача управляющего сигнала на следующий исправный канал управления.

передается на выход Вых. 2 ячейки и далее на вход Вх.2 следующей ячейки /фиг. 2/, подготавливая ее к передаче сигнала на следующую нагрузку RH2. Таким способом осуществляется передача управляющего сигнала на следующий исправный канал управления.

После окончания цикла распределения последний управляющий сигнал /на заднем фронте/ переключает I-K-триггер T1 1 своей ячейки /фиг. 1/ в состояние логической единицы на прямом выходе Q1. После инвертирования его первым элементом НЕ 7 сигнал логического нуля передается на выход Вых. 3 последней ячейки и на входы Вх. 1 всех ячеек /фиг. 2/. Этот сигнал в нулевой форме передается через первые элементы n 2 на входы R I-K-триггеров T1 1 всех ячеек /фиг. 1/, переключая их в единичное исходное состояние на инверсных выходах  и нулевое - на прямых выходах Q1. Устройство готово к следующему циклу распределения управляющих сигналов.

и нулевое - на прямых выходах Q1. Устройство готово к следующему циклу распределения управляющих сигналов.

Ячейки приводятся в исходное состояние следующим образом. При включении на ячейку питания первоначально I-K-триггер T1 1 может оказаться в любом состоянии. Если на прямом его выходе Q1 возникнет нулевой сигнал, то после первого элемента НЕ 7 единичный сигнал подается на выход Вых. 3 последней ячейки и далее на входы Вх. 1 всех ячеек и их первые элементы n 2. Это позволяет привести в исходное выключенное состояние I-K-триггера T1 1 всех ячеек посредством своих цепочек R1C. Если на прямом выходе возникает единичный сигнал, то после первого элемента НЕ 7 последней ячейки нулевой сигнал поступает на первые элементы НЕ 2 всех ячеек и входы R I-K-триггеров T1 1, также переводя их в необходимое выключенное состояние. Первые диоды 4 и вторые 10 необходимы для гальванической развязки выходов третьих элементов n 5 и входов вторых элементов НЕ 3.

Литература.

1. Релейное устройство для распределения импульсов тока. А.С. СССР N 119216, 21 с 47/01.

2. Контрольно-распределительное многоразрядное релейное устройство. А.С. СССР N 1099331, H 01 H 47/00. Бюл. изобр. N 23. 1984 год.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРЕКЛЮЧАТЕЛЬ ДВУХТАКТНЫЙ | 1997 |

|

RU2118043C1 |

| ТАЙМЕР | 1996 |

|

RU2103808C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2115227C1 |

| ФОРМИРОВАТЕЛЬ ГРУППЫ ИМПУЛЬСОВ | 1996 |

|

RU2103807C1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1997 |

|

RU2147788C1 |

| ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 2002 |

|

RU2221328C1 |

| ПЕРЕКЛЮЧАТЕЛЬ УПРАВЛЯЮЩИХ КАНАЛОВ | 1997 |

|

RU2103814C1 |

| ФЕРРИД-ТРИГГЕР | 1997 |

|

RU2115974C1 |

Изобретение относится к устройствам переключения и контроля исправности цепей управления систем управления, контроля, устройства связи и других устройств различных отраслей техники. Техническим результатом является повышение быстродействия устройства, снижение его энергопотребления, массы и размеров. Для этого каждая ячейка заявленного устройства содержит резисторы, элементы И, триггеры, элемент НЕ и линию задержки. 1 з.п.ф-лы, 2 ил.

| Индуктивный преобразователь | 1955 |

|

SU109931A1 |

| Коммутатор | 1982 |

|

SU1146818A1 |

| Коммутатор | 1984 |

|

SU1205313A1 |

| Коммутатор | 1981 |

|

SU1026306A1 |

| US 3546394 A, 08.12.1970. | |||

Авторы

Даты

2000-09-10—Публикация

1999-05-20—Подача