Изобретение относится к устройствам коммутации и может найти применение в системах управления, контроля, измерения, вычислительных устройствах, устройствах связи различных отраслей техники.

Известен переключатель /R-S-триггер/, описанный, например, в [1], содержащий два элемента И-НЕ с перекрестной обратной связью, два входа и два выхода. К недостаткам такого устройства следует отнести необходимость изменения на противоположные значения двух входных сигналов по двум каналам для переключения устройства в исходное состояние /выключение/.

Известен также переключатель /J-K-триггер/, описанный, например, в [2], содержащий также два элемента И-НЕ с перекрестной обратной связью, схему управления на цифровых элементах /МЭЦС/ или транзисторах, 5 входов и два выхода. К недостаткам такого устройства следует отнести переключение устройства после окончания управляющего сигнала, что создает задержку выходного сигнала относительно входного.

Вместе с тем многие цифровые системы не допускают такой задержки и требуют управления переключателем двумя тактами по единственному каналу /переключатель с памятью/.

В качестве прототипа принято устройство, описанное в [2].

Целью настоящего изобретения является расширение функциональных возможностей, а именно возможность управления переключателем по одному каналу двумя тактами и исключение задержки выходного сигнала относительно входного.

Поставленная цель достигается тем, что в устройство дополнительно введены один двухвходовой элемент И-НЕ, два двухвходовых элемента И, один трехвходовой элемент ИЛИ и одна линия задержки.

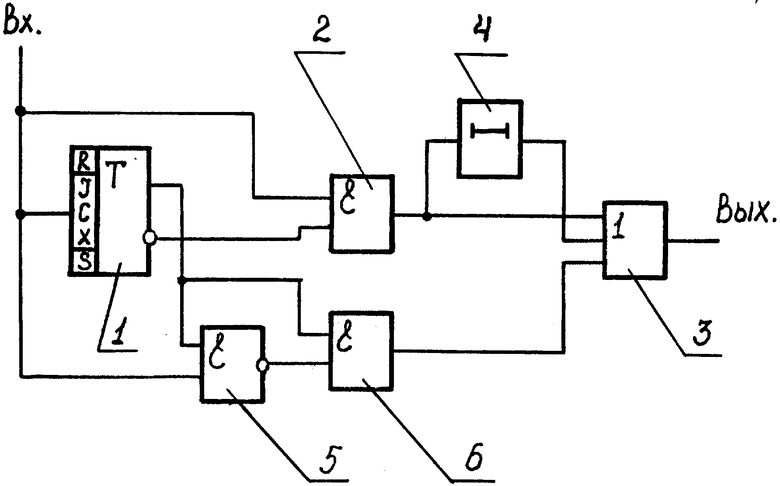

На чертеже приведена схема переключателя двухтактного.

Устройство содержит вход Вх, выход Вых, J-K-триггер 1, первый двухвходовой элемент И 2, трехвходовой элемент ИЛИ 3, линию задержки 4, двухвходовой элемент И-НЕ 5 и второй двухвходовой элемент И 6. Вход Вх устройства соединен со входом С J-K-триггера 1, первым входом первого двухвходового элемента И 2 и вторым входом двухвходового элемента И-НЕ 5. Прямой выход J-K-триггера 1 соединен с первым входом второго двухвходового элемента И 6 и первым входом двухвходового элемента И-НЕ 5, выход которого соединен со вторым входом второго двухвходового элемента И 6. Выходы первого 2 и второго 6 двухвходовых элементов И соединены с первым и третьим входами трехвходового элемента ИЛИ 3 соответственно, причем выход первого элемента И 2 также соединен со входом линии задержки 3, выход которой соединен со вторым входом трехвходового элемента ИЛИ 3, выход которого в свою очередь соединен с выходом Вых устройства.

Использование J-K-триггера, элемента И-НЕ, двух элементов И, одного элемента ИЛИ и одной линии задержки для достижения поставленной цели в источниках не обнаружено. Устройство работает следующим образом. J-K-триггер 1 для реализации счетного режима работы должен иметь на входах J и K потенциальный единичный сигнал. В исходное состояние устройство приводится подачей кратковременного нулевого сигнала на вход R при потенциальном единичном сигнале на входе S J-K-триггера 1. При этом на прямом выходе J-K-триггера 1 устанавливается нулевой, а на инверсном - единичный сигнал. На выходе Вых устройства устанавливается нулевой сигнал. В таком состоянии устройство готово к функционированию. При поступлении на вход Вх устройства первого управляющего сигнала /первый такт/ единичный сигнал поступает на вход С J-K-триггера 1, первый вход первого двухвходового элемента И 2 и первый вход двухвходового элемента И-НЕ 5. На выходе первого элемента И 2 появляется при этом единичный сигнал, поступающий на первый вход двухвходового элемента ИЛИ, на выходе которого и выходе устройства появляется единичный сигнал. Одновременно единичный сигнал поступает на вход линии задержки 4. На выходе двухвходового элемента И-НЕ 5 сохраняется единичный сигнал, передаваемый на второй вход второго двухвходового элемента И 6, на выходе которого сохраняется нулевой сигнал. После окончания на входе Вх устройства первого управляющего сигнала J-K-триггер 1 переключается в состояние единичного сигнала на прямом выходе и нулевого - на инверсном. При этом на выходе двухвходового элемента И-НЕ 5 сохраняется единичный сигнал, а на выходе второго двухвходового элемента И 6 появляется единичный сигнал, передаваемый на третий вход трехвходового элемента ИЛИ 3. На время переключения J-K-триггера 1 и второго элемента И 6 элемент ИЛИ 3 сохраняет на своем выходе единичный сигнал за счет задержки единичного сигнала на своем втором входе единичного выходного сигнала линии задержки 4. На выходе первого двухвходового элемента И 2 появляется нулевой сигнал, не изменяющий единичный сигнал на выходе Вых устройства. Второй входной управляющий сигнал /второй такт/ поступает на второй вход двухвходового элемента И-НЕ 5, переключая его единичный выходной сигнал на нулевой, который подается на второй вход второго двухвходового элемента И 6. На его выходе появляется нулевой сигнал, который поступает на третий вход элемента ИЛИ 3. При этом элемент ИЛИ 3 приобретает на всех входах нулевые сигналы и на выходе Вых устройства появляется нулевой сигнал. После окончания второго входного сигнала J-K-триггер 1 переходит в нулевое состояние прямого и единичного - инверсного выходов. Схема устройства переходит в исходное состояние.

Таким образом единичный выходной сигнал устройства появляется при появлении первого управляющего сигнала /на фронте сигнала первого такта/, а исчезает при появлении второго управляющего сигнала /на фронте сигнала второго такта/, что практически исключает задержку выходного сигнала относительно входного.

Для нормального функционирования устройства необходимо иметь время задержки сигнала линией задержки 4.

tзд≥tпк.тр+tпк.н,

tпк.тр и tпк.п - время переключения J-K-триггера и элемента И соответственно.

Литература:

1. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л.: Энергоатомиздат, 1986, с. 167, рис. 10-4.

2. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л.: Энергоатомиздат, 1986, с. 181, рис. 10-13.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЬНО-РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1999 |

|

RU2156042C1 |

| ФОРМИРОВАТЕЛЬ ГРУППЫ ИМПУЛЬСОВ | 1996 |

|

RU2103807C1 |

| ЛИНИЯ ЗАДЕРЖКИ СИГНАЛА | 1998 |

|

RU2130231C1 |

| ТАЙМЕР | 1996 |

|

RU2103808C1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1997 |

|

RU2147788C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2117387C1 |

| ПЕРЕКЛЮЧАТЕЛЬ УПРАВЛЯЮЩИХ КАНАЛОВ | 1997 |

|

RU2103814C1 |

| СЕЛЕКТОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ | 1997 |

|

RU2118044C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

Изобретение относится к устройствам коммутации и может найти применение в системах управления, контроля, измерения, вычислительных устройствах, устройствах связи различных отраслей техники. Технический результат заключается в том, что устройство позволяет переключать выходной сигнал без задержки относительно входного сигнала. Устройство осуществляет управление двумя последовательными сигналами с использованием одного канала управления. Переключатель содержит JK-триггер, два элемента И, элементы ИЛИ, И - НЕ и линию задержки. 1 ил.

Переключатель двухтактный, содержащий вход, выход и JK-триггер, отличающийся тем, что в него дополнительно введены элементы двухвходовой И - НЕ, трехвходовой ИЛИ, два двухвходовых элемента И и линия задержки, причем вход устройства соединен с входом CJK-триггера, первым входом первого двухвходового элемента И и вторым входом двухвходового элемента И - НЕ, прямой выход JK-триггера соединен с первым входом двухвходового элемента И - НЕ и первым входом второго двухвходового элемента И, к второму входу которого подсоединен выход двухвходового элемента И - НЕ, а инверсный выход JK-триггера соединен с вторым входом первого двухвходового элемента И, выход которого соединен с первым входом трехвходового элемента ИЛИ и входом линии задержки, выход которого соединен с вторым входом трехвходового элемента ИЛИ, к третьему входу которого подсоединен выход второго двухвходового элемента И, а выход устройства соединен с выходом трехвходового элемента ИЛИ.

| Формирователь импульсов | 1984 |

|

SU1226624A1 |

| Формирователь импульсов | 1980 |

|

SU1083349A1 |

| Зельдин Е.А | |||

| Цифровые интегральные микросхемы в информационно-измерительной аппаратуре | |||

| - Л.: Энергоатомиздат, 1986, стр.167, рис.10 - 4,с.181, рис.10 - 13 | |||

| Угрюмов В.П | |||

| Проектирование элементов и узлов ЭВМ | |||

| - М.: Высшая школа, 1987, с.157, рис.9.25. | |||

Авторы

Даты

1998-08-20—Публикация

1997-06-09—Подача