Изобретение относится к области автоматики и импульсной техники и может найти применение в системах управления, контроля, устройствах связи и других устройствах различных отраслей техники.

Известно устройство, описанное, например в [1], содержащее несколько последовательно включенных ячеек (модулей), реализованных на триггерах. Устройство позволяет подсчитывать импульсы в арифметическом двоичном коде.

К недостаткам такого устройства следует отнести разрушение двоичного кода при отключении источника питания.

Известно также устройство, описанное, например в [2], содержащее несколько последовательно включенных ячеек (модулей), каждая из которых представляет собой феррид-триггер.

К недостаткам такого устройства следует отнести низкое быстродействие, обусловленное последовательным срабатыванием ячеек.

В качестве прототипа принято устройство, описанное в [2].

Целью настоящего изобретения является повышение быстродействия, а также исключение разрушения выходного двоичного кода при отключении источника питания.

Поставленная цель достигается тем, что между разрядами (ячейками) счетчика (кроме первого и второго) установлены логические ячейки, позволяющие получить одновременное срабатывание нескольких ячеек. Счетчики могут быть суммирующие и вычитающие.

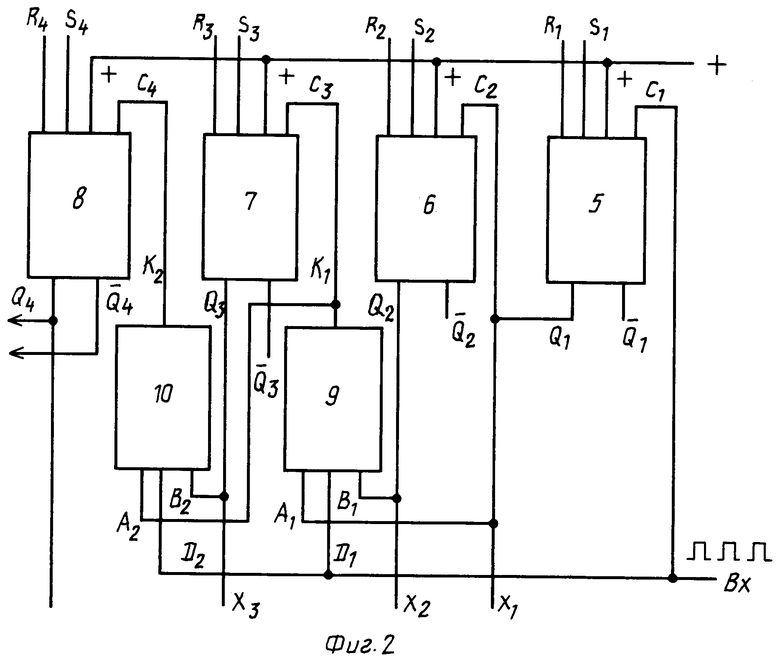

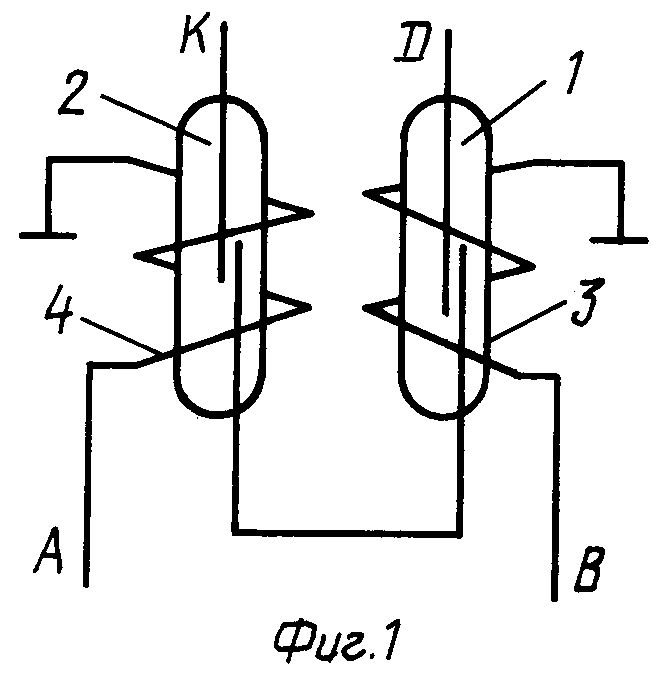

Сущность изобретения поясняется чертежами, где на фиг.1 приведена схема логической ячейки (элемент И), а на фиг.2 - схема предлагаемого параллельного суммирующего двоичного счетчика импульсов.

Параллельный суммирующий двоичный счетчик импульсов состоит из наращиваемых последовательно включенных по меньшей мере двух бистабильных ячеек [3] , каждая из которых имеет счетный вход С, установочные входы R и S для установки начального кода счетчика (посредством шифратора), вход (+), прямой выход Q и инверсный выход  . Вход Вх счетчика (фиг.2) служит для восприятия подсчитываемых импульсов. Входы (+) всех ячеек счетчика, например четырех 5, 6, 7, 8, соединены с плюсом (+) источника питания. Прямой выход Q предыдущей ячейки счетчика соединен со счетным входом С последующей ячейки счетчика, кроме первых двух ячеек, посредством логических ячеек (фиг.1). Каждая логическая ячейка (9 и 10) содержит два замыкающих геркона (1 и 2 фиг.1), каждый из которых имеет обмотку управления (3 и 4). Логическая ячейка имеет входы А, В, D и выход К. Вход А логической ячейки соединен с началом обмотки 4 первого геркона 2, вход В - с началом обмотки 3 второго геркона 1, вход D соединен с первым контакт-деталью второго геркона 1, выход К соединен с первым контакт-деталью первого геркона 2. Второй контакт-деталь первого геркона 2 соединен со вторым контакт-деталью второго геркона 1. Концы обмоток соединены с массой (минусом) источника питания. Управляющие входы А логических ячеек (фиг.2) соединены со счетными входам С, а управляющие входы В - с прямыми выходами Q предыдущих ячеек счетчика. Управляющие входы D всех логических ячеек и счетный вход С первой ячейки счетчика соединены со входом Вх счетчика импульсов. Прямой выход Q первой ячейки счетчика соединен со счетным входом С второй ячейки счетчика. Выходы К логических ячеек соединены со счетными входами С последующих ячеек счетчика.

. Вход Вх счетчика (фиг.2) служит для восприятия подсчитываемых импульсов. Входы (+) всех ячеек счетчика, например четырех 5, 6, 7, 8, соединены с плюсом (+) источника питания. Прямой выход Q предыдущей ячейки счетчика соединен со счетным входом С последующей ячейки счетчика, кроме первых двух ячеек, посредством логических ячеек (фиг.1). Каждая логическая ячейка (9 и 10) содержит два замыкающих геркона (1 и 2 фиг.1), каждый из которых имеет обмотку управления (3 и 4). Логическая ячейка имеет входы А, В, D и выход К. Вход А логической ячейки соединен с началом обмотки 4 первого геркона 2, вход В - с началом обмотки 3 второго геркона 1, вход D соединен с первым контакт-деталью второго геркона 1, выход К соединен с первым контакт-деталью первого геркона 2. Второй контакт-деталь первого геркона 2 соединен со вторым контакт-деталью второго геркона 1. Концы обмоток соединены с массой (минусом) источника питания. Управляющие входы А логических ячеек (фиг.2) соединены со счетными входам С, а управляющие входы В - с прямыми выходами Q предыдущих ячеек счетчика. Управляющие входы D всех логических ячеек и счетный вход С первой ячейки счетчика соединены со входом Вх счетчика импульсов. Прямой выход Q первой ячейки счетчика соединен со счетным входом С второй ячейки счетчика. Выходы К логических ячеек соединены со счетными входами С последующих ячеек счетчика.

Использование герконной логической ячейки и размещение ее между соседними бистабильными ячейками счетчика в источниках не обнаружено.

Работа ячейки [3] параллельного суммирующего двоичного счетчика импульсов осуществляется в следующей последовательности. Вход Вх счетчика предназначен для восприятия входных подсчитываемых сигналов.

Перед началом работы ячейка приводится в необходимое начальное состояние. Для выключенного состояния (Q=0) на установочный вход R подается кратковременный сигнал логической единицы (0-->1-->0) при отсутствии или нулевом сигнале на установочном входе S. При этом на прямом выходе Q ячейки счетчика устанавливается сигнал Q=0, а на инверсном  . Для включенного состояния (Q= 1) на установочный вход S подается кратковременный сигнал логической единицы (0-->1-->0) при отсутствии или нулевом сигнале на установочном входе R. При этом на прямом выходе ячейки счетчика устанавливается сигнал Q=1, а на инверсном

. Для включенного состояния (Q= 1) на установочный вход S подается кратковременный сигнал логической единицы (0-->1-->0) при отсутствии или нулевом сигнале на установочном входе R. При этом на прямом выходе ячейки счетчика устанавливается сигнал Q=1, а на инверсном  . Работа логической ячейки (фиг.1) осуществляется в следующей последовательности. При поступлении сигнала только на один из управляющих входов А или В срабатывает (замыкается) только один геркон (1 или 2). Герконы включены последовательно, поэтому на выходе К логической ячейки сигнал отсутствует. И только при одновременном поступлении единичных сигналов на управляющие входы А и В срабатывают (замыкаются) оба геркона, на выходе К появляется единичный выходной сигнал. Вход D предназначен для восприятия управляющего входного сигнала от входа Вх счетчика. Выходы х1; х2; х3; х4 предназначены для снятия выходного двоичного кода счетчика.

. Работа логической ячейки (фиг.1) осуществляется в следующей последовательности. При поступлении сигнала только на один из управляющих входов А или В срабатывает (замыкается) только один геркон (1 или 2). Герконы включены последовательно, поэтому на выходе К логической ячейки сигнал отсутствует. И только при одновременном поступлении единичных сигналов на управляющие входы А и В срабатывают (замыкаются) оба геркона, на выходе К появляется единичный выходной сигнал. Вход D предназначен для восприятия управляющего входного сигнала от входа Вх счетчика. Выходы х1; х2; х3; х4 предназначены для снятия выходного двоичного кода счетчика.

Параллельный двоичный счетчик импульсов (фиг.2) работает в следующей последовательности. При поступлении и окончании первого подсчитываемого сигнала, например, после обнуления счетчика на счетный вход С1 первой (младшей) ячейки 5, на ее прямом выходе устанавливается сигнал Q1=1, а на инверсном выходе  . Сигнал Q1= 1 передается на счетный вход С2 второй ячейки 6 счетчика, подготавливая ее к переключению. Одновременно единичный сигнал передается на управляющий вход А1 логической ячейки 9, подготавливая ее к срабатыванию. На выходе счетчика (х4; х3; х2; х1) устанавливается код 0001. Второй сигнал (после окончания), поступивший на счетный вход С1, возвращает ячейку 5 в исходное состояние Q1=0,

. Сигнал Q1= 1 передается на счетный вход С2 второй ячейки 6 счетчика, подготавливая ее к переключению. Одновременно единичный сигнал передается на управляющий вход А1 логической ячейки 9, подготавливая ее к срабатыванию. На выходе счетчика (х4; х3; х2; х1) устанавливается код 0001. Второй сигнал (после окончания), поступивший на счетный вход С1, возвращает ячейку 5 в исходное состояние Q1=0,  и переключает ячейку 6 в состояние Q2=1,

и переключает ячейку 6 в состояние Q2=1,  . На выходе счетчика устанавливается код 0010.

. На выходе счетчика устанавливается код 0010.

После окончания третьего поступившего сигнала ячейка 5 устанавливается в состояние Q1=1,  , вызывая срабатывание логической ячейки 9. На ее выходе появляется сигнал К1=1, подготавливающий к переключению ячейку 7 счетчика. На выходе счетчика устанавливается код 0011.

, вызывая срабатывание логической ячейки 9. На ее выходе появляется сигнал К1=1, подготавливающий к переключению ячейку 7 счетчика. На выходе счетчика устанавливается код 0011.

После окончания четвертого импульса ячейка 5 счетчика устанавливается в состояние Q1= 0,  , что вызывает появление сигналов Q2=0,

, что вызывает появление сигналов Q2=0,  . В результате исчезновения сигналов А1(Q1=0) и В1(Q2=0) исчезает сигнал С3(К1= 0) и на выходе счетчика устанавливается код 0100.

. В результате исчезновения сигналов А1(Q1=0) и В1(Q2=0) исчезает сигнал С3(К1= 0) и на выходе счетчика устанавливается код 0100.

После окончания пятого поступившего на счетчик сигнала ячейки 5 устанавливается Q1= 1,  . Ячейка 6 счетчика и остальные ячейки сохраняют свое прежнее состояние. На выходе счетчика устанавливается код 0101.

. Ячейка 6 счетчика и остальные ячейки сохраняют свое прежнее состояние. На выходе счетчика устанавливается код 0101.

После окончания шестого сигнала ячейка 5 счетчика устанавливается в состояние Q1=0,  , переключая ячейку счетчика 6 в состояние Q2=1,

, переключая ячейку счетчика 6 в состояние Q2=1,  . Остальные ячейки сохраняют свое прежнее состояние. На выходе счетчика устанавливается код 0110.

. Остальные ячейки сохраняют свое прежнее состояние. На выходе счетчика устанавливается код 0110.

После окончания седьмого сигнала ячейка 5 счетчика устанавливается в состояние Q1=1,  , подготавливая к переключению ячейку счетчика 6. На выходе счетчика устанавливается код 0111.

, подготавливая к переключению ячейку счетчика 6. На выходе счетчика устанавливается код 0111.

После окончания восьмого сигнала ячейка 5 счетчика устанавливается в состояние Q1=0,  , переключая ячейку 6 счетчика в состояние Q2=0,

, переключая ячейку 6 счетчика в состояние Q2=0,  , что переводит сигналы в состояния С3=0, Q3=0, C4=0, Q4=1. На выходе счетчика устанавливается код 1000.

, что переводит сигналы в состояния С3=0, Q3=0, C4=0, Q4=1. На выходе счетчика устанавливается код 1000.

Дальнейшая работа счетчика осуществляется аналогично.

При любом переходе состояний счетчика переключение его ячеек осуществляется одновременно (параллельно), что сокращает время установки кода.

Подключение входов Аi и Вi логических ячеек вместо прямых к инверсным выходам ячеек счетчика преобразовывает его из суммирующего в вычитающий.

Источники информации

1. Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств, М., "Советское радио", 1973, стр.137, рис.5.1.

2. Патент РФ 2115227 С1. Последовательный реверсивный двоичный счетчик импульсов.

3. Патент РФ 2115190 С1, Феррид-триггер.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2115227C1 |

| КОНТРОЛЬНО-РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1999 |

|

RU2156042C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

| ФЕРРИД-ТРИГГЕР | 1997 |

|

RU2115974C1 |

| ТАЙМЕР | 1996 |

|

RU2100901C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2117387C1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2015 |

|

RU2604334C2 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2103813C1 |

| ФЕРРИД-ТРИГГЕР | 1997 |

|

RU2115190C1 |

| СЕЛЕКТОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ | 1997 |

|

RU2118044C1 |

Изобретение относится к области автоматики и импульсной техники и может найти применение в системах управления, контроля, измерений, устройствах связи и других устройствах различных отраслей техники. Техническим результатом является повышение быстродействия. Технический результат достигается за счет того, что параллельный двоичный счетчик импульсов содержит наращиваемый ряд идентичных бистабильных ячеек, у которого выходы предыдущих ячеек соединены с входами последующих посредством логических герконных ячеек. 2 ил.

Параллельный двоичный счетчик импульсов, содержащий один вход Вх для восприятия подсчитываемых импульсов и выходы по числу разрядов и состоящий из наращиваемых двух бистабильных ячеек, каждая из которых имеет счетный вход С, установочные входы R и S для установки начального кода счетчика, вход /+/, прямой выход Q и инверсный выход  , входы /+/ всех ячеек соединены с плюсом /+/ источника питания, отличающийся тем, что содержит логические ячейки, каждая из которых содержит два замыкающих геркона, каждый из которых имеет свою обмотку управления, каждая логическая ячейка имеет три управляющих входа: А, В и D и выход К, причем вход А логической ячейки соединен с началом обмотки управления первого геркона, вход В - с началом обмотки управления второго геркона, концы упомянутых обмоток соединены с "минусом" источника питания, вход D соединен с первой контакт-деталью второго геркона, выход К логической ячейки соединен с первой контакт-деталью первого геркона, вторая контакт-деталь первого геркона соединена со второй контакт-деталью второго геркона, управляющие входы А логических ячеек соединены со счетными входами С бистабильных ячеек, а управляющие входы В - с прямыми выходами Q предыдущих бистабильных ячеек счетчика, управляющие входы D всех логических ячеек и счетный вход С первой бистабильной ячейки счетчика соединены с входом Вх счетчика импульсов, прямой выход Q первой бистабильной ячейки счетчика соединен со счетным входом С второй бистабильной ячейки счетчика, выходы К логических ячеек соединены со счетными входами С последующих бистабильных ячеек счетчика.

, входы /+/ всех ячеек соединены с плюсом /+/ источника питания, отличающийся тем, что содержит логические ячейки, каждая из которых содержит два замыкающих геркона, каждый из которых имеет свою обмотку управления, каждая логическая ячейка имеет три управляющих входа: А, В и D и выход К, причем вход А логической ячейки соединен с началом обмотки управления первого геркона, вход В - с началом обмотки управления второго геркона, концы упомянутых обмоток соединены с "минусом" источника питания, вход D соединен с первой контакт-деталью второго геркона, выход К логической ячейки соединен с первой контакт-деталью первого геркона, вторая контакт-деталь первого геркона соединена со второй контакт-деталью второго геркона, управляющие входы А логических ячеек соединены со счетными входами С бистабильных ячеек, а управляющие входы В - с прямыми выходами Q предыдущих бистабильных ячеек счетчика, управляющие входы D всех логических ячеек и счетный вход С первой бистабильной ячейки счетчика соединены с входом Вх счетчика импульсов, прямой выход Q первой бистабильной ячейки счетчика соединен со счетным входом С второй бистабильной ячейки счетчика, выходы К логических ячеек соединены со счетными входами С последующих бистабильных ячеек счетчика.

| ПОСЛЕДОВАТЕЛЬНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2115227C1 |

| Герконовое реле с двумя устойчивыми состояниями | 1980 |

|

SU879670A1 |

| Релейный счетчик | 1978 |

|

SU843250A1 |

| Электромагнитное реле | 1981 |

|

SU972609A2 |

| ФЕРРИД-ТРИГГЕР | 1997 |

|

RU2115974C1 |

| ФЕРРИД-ТРИГГЕР | 1997 |

|

RU2115190C1 |

| Двоичный релейный счетчик импульсов | 1972 |

|

SU489228A1 |

Авторы

Даты

2004-01-10—Публикация

2002-04-15—Подача