Изобретение относится к электронным схемам для возбуждения соленоида, а более конкретно к таким электронным схемам возбуждения, которые используют широтно-импульсную модуляцию.

Соленоид представляет собой электромеханическое устройство, которое преобразует электрический сигнал, подаваемый на обмотку соленоида, в соответствующее механическое движение металлического предмета, например стержня, расположенного внутри катушки. Электрический ток, протекающий через обмотку катушки, создает магнитное поле, которое притягивает или отталкивает металлический предмет. Металлический предмет обычно соединен с механическим устройством, например исполнительным механизмом, которое перемещается вместе с металлическим предметом, двигающимся под действием магнитного поля соленоида.

Соленоиды широко применяются во многих военных и промышленных устройствах. Например, соленоиды используются в летательных аппаратах для управления различными механическими устройствами и параметрами.

Для возбуждения обмотки соленоида, то есть для управления ею, используются различные электронные схемы, см. , например, патенты США 4381532, 4546403, 4556926, 4764840, 4949215 и 5345181. Типичная схема содержит соленоид, соединенный последовательно с источником напряжения, транзистором и датчиком-резистором. Напряжение на датчике-резисторе показывает, какой ток течет через обмотку соленоида. Обычно необходимо управлять током через соленоид так, чтобы этот ток не превышал заданного значения, в противном случае соленоид выйдет из строя.

Напряжение с датчика-резистора обычно подается на один из входов компаратора, на другой вход которого подается опорное напряжение. Если напряжение на датчике-резисторе превышает опорное напряжение, сигнал на выходе компаратора переключается из одного состояния в другое. Соответствующая схема обработки сигнала, включенная после компаратора, переключает транзистор, включенный последовательно с соленоидом, в закрытое состояние. Это предотвращает чрезмерное увеличение тока через соленоид.

Соответственно, главной целью настоящего изобретения является создание электронного устройства возбуждения (управления) для соленоида, причем с использованием метода широтно-импульсной модуляции.

Целью настоящего изобретения является ограничение электрического тока, текущего по обмотке соленоида, заранее заданным максимальным значением, что обеспечивает нормальную работу соленоида.

Другой целью настоящего изобретение является обнаружение размыкания катушки соленоида.

Еще одной целью настоящего изобретения является использование схемы широтно-импульсной модуляции для возбуждения соленоида таким образом, что во время повторяющихся интервалов, или окон, ток через обмотку соленоида протекает в течение части каждого окна, независимо от того, имеет место превышение максимального тока или нет.

Вышеупомянутые и другие цели и преимущества этого изобретения будут более понятны из последующего описания со ссылками на прилагаемый чертеж.

Краткое описание изобретения

Чтобы преодолеть недостатки известных устройств и достичь целей, перечисленных выше, заявители предлагают электронную схему возбуждения с широтно-импульсной модуляцией для соленоида.

В предпочтительном варианте выполнения изобретения обмотка соленоида последовательно соединена с источником напряжения, первым транзистором и первым датчиком-резистором. Первый транзистор и первый датчик-резистор соединены с нижним концом обмотки соленоида. Второй транзистор и второй датчик-резистор, совместно с соответствующей схемой предотвращения перегрузки, соединены с верхним концом обмотки соленоида. Ток через обмотку соленоида определяют через соответствующее напряжение на первом датчике-резисторе. Компаратор сравнивает это напряжение с опорным напряжением, которое соответствует состоянию перегрузки соленоида. Если напряжение на датчике-резисторе превышает опорное напряжение, то наступает состояние перегрузки соленоида. В этом случае первый транзистор закрывается, тем самым отключая источник напряжения от соленоида до тех пор, пока ток через соленоид не упадет ниже уровня перегрузки.

Используется принцип периодически повторяющихся временных интервалов, далее называемых "окнами", согласно которому напряжение к соленоиду всегда приложено в течение первых 25 процентов длительности окна, независимо от того, наступила перегрузка или нет. В течение остальных 75 процентов длительности окна напряжение на соленоид подается лишь в случае, если в течение предыдущего окна не было перегрузки. И наоборот, напряжение на соленоид не подается, если в течение предыдущего окна была перегрузка. Незадолго до окончания заранее заданного количества окон напряжение на соленоид не подается в течение определенного периода времени и осуществляется проверка, не разомкнута ли обмотка соленоида. Эта проверка осуществляется путем сравнения напряжения на одном конце соленоида с опорным напряжением, соответствующим состоянию разрыва цепи. Для этого средства обнаружения разомкнутого состояния обмотки соленоида содержат средства сравнения напряжения на одном конце соленоида с опорным напряжением соленоида, указывающим на разомкнутое состояние соленоида, с получением результирующего сигнала, соответствующего результату сравнения, причем если напряжение на конце соленоида меньше, чем опорное напряжение соленоида, то имеет место размыкание обмотки соленоида, а если напряжение на конце соленоида больше, чем опорное напряжение соленоида, то размыкания обмотки соленоида нет. То есть, если произошел разрыв, то компаратор переключается в другое состояние и соответствующая схема обработки сигнала предотвращает дальнейшую подачу тока в обмотку соленоида. Кроме того, через заданное время после приложения напряжения к обмотке соленоида осуществляется проверка соответствия норме напряжения на соленоиде.

Краткое описание чертежа

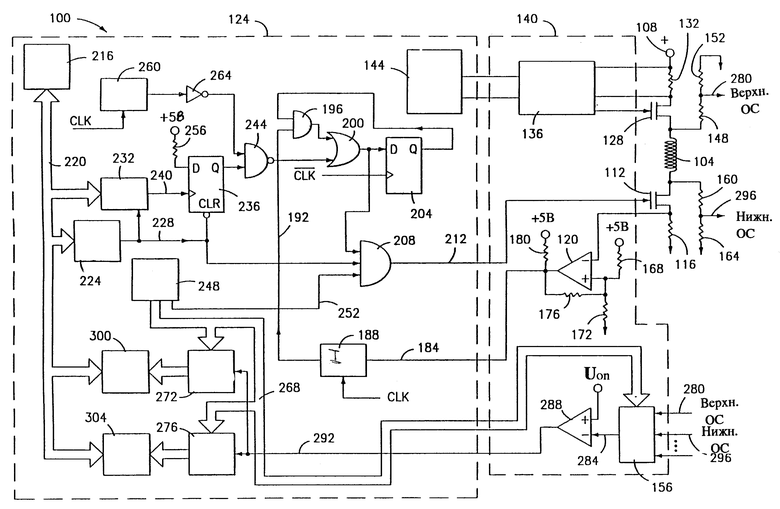

На единственном чертеже представлена электронная схема возбуждения, в которой для управления током через соленоид используется широтно-импульсная модуляция согласно настоящему изобретению.

Подробное описание предпочтительных вариантов выполнения изобретения

На чертеже подробно показан предпочтительный вариант выполнения электронной схемы 100 возбуждения согласно настоящему изобретению. Обмотка 104 соленоида последовательно соединена с источником 108 напряжения, первым транзистором 112 и первым датчиком-резистором 116. Напряжения на датчике-резисторе 116 показывает величину тока в соленоиде 104. Это напряжение подается в компаратор 120, который сравнивает его с опорным напряжением, и если напряжение на датчике-резисторе 116 превышает опорное напряжение, то имеет место перегрузка по току. Сигнал с выхода компаратора 120 подается в соответствующую схему обработки, входящую в интегральную схему 124, представляющую собой матрицу логических элементов. Эта матрица логических элементов выключает транзистор 112, тем самым выключая ток через соленоид 104.

Первый транзистор 112 имеет два выходных электрода, один из которых соединен с нижним концом обмотки соленоида 104, а другой - с одним из выводов первого датчика-резистора 116. Другой вывод первого датчика-резистора 116 соединен с нулевым проводом. Верхний конец соленоида 104 соединен с одним из двух выходных электродов второго транзистора 128, а второй выходной электрод второго транзистора 128 соединен с вторым датчиком-резистором 132.

Верхний вывод второго датчика-резистора 132 соединен с источником 108 напряжения. Затвор второго транзистора 128 и оба вывода второго датчика-резистора 132 соединены с верхней схемой 136 интерфейса соленоида, входящей в интегральную схему 140 интерфейса соленоида. Верхняя схема 136 интерфейса соленоида также соединена с верхней схемой 144 управления, входящей в матрицу 124 логических элементов. Как верхняя схема 136 интерфейса соленоида, так и верхняя схема 144 управления более подробно описаны ниже. Верхний конец соленоида 104 соединен также с двумя последовательными резисторами 148 и 152. Точка соединения этих резисторов 148 и 152 соединена со входом мультиплексора 156, размещенного в интегральной схеме 140 интерфейса соленоида. Кроме того, нижний конец соленоида 104 соединен с аналогичными двумя резисторами 160 и 164, соединенными последовательно. Средняя точка соединения этих резисторов 160 и 164 соединена со вторым входом мультиплексора 156. Две пары резисторов 148, 152, 160, 164, соленоид 104, два транзистора 112 и 128, два датчика-резистора 116 и 132, а также источник 108 напряжения могут располагаться вне схемы 140 интерфейса соленоида. Кроме того, схема 140 интерфейса соленоида может быть расположена вне интегральной схемы 124 матрицы логических элементов. Однако следует понимать, что расположение всех компонентов, изображенных на чертеже, в одной или нескольких интегральных схемах представлено лишь в качестве примера.

Величина напряжения в узле, то есть точке соединения одного из выходных электродов первого транзистора 112 и первого датчика-транзистора 116, пропорциональна величине электрического тока, протекающего через обмотку 104 соленоида. Это напряжение подается на инвертирующий вход операционного усилителя, включенного как компаратор 120. Неинвертирующий вход компаратора 120 находится под постоянным опорным напряжением, приложенным к нему через цепь резистивного делителя, состоящую из резисторов 168 и 172. Это опорное напряжение соответствует условию перегрузки соленоида 104. Между неинвертирующим входом компаратора 120 и выходом компаратора 120 включен резистор 176. Кроме того, на выходе компаратора установлен нагрузочный резистор 180.

Пока ток через соленоид 104 остается ниже уровня, соответствующего перегрузке, напряжение на неинвертирующем входе компаратора 120 превышает напряжение на его инвертирующем входе и на выходе компаратора 120 устанавливается высокий логический уровень. С другой стороны, если существует перегрузка, напряжение на инвертирующем входе компаратора 120 превысит напряжение на его неинвертирующем входе и на выходе компаратора установится низкий логический уровень.

Через сигнальную линию 184 выход компаратора соединен с фильтром 188, расположенным в матрице 124 логических элементов. Фильтр 188 осуществляет функцию задержки, чтобы выходной сигнал компаратора 184 оставался в одном из двух логических состояний в течение заранее заданного количества тактов синхронизации. Для этого в фильтр 188 подается сигнал синхронизации ("CLK") с частотой приблизительно 1,25 МГц. В результате каждый интервал синхронизации составляет приблизительно 0,8 микросекунд. В варианте выполнения изобретения, представленном для примера, для того, чтобы новый логический уровень прошел через фильтр 188 в сигнальную линию 192, уровень напряжения на выходе компаратора должен оставаться неизменным в течение по меньшей мере трех интервалов синхронизации, или 2,4 мкс. Затем, если сигнал 184 с выхода компаратора остается равным тому же логическому уровню еще в течение двух интервалов синхронизации, то есть 1,6 мкс (всего 4,0 мкс), этот выходной сигнал, соответствующий новому логическому уровню, пройдет через фильтр 188 на его выход - сигнальную линию 192. Таким образом фильтр 188 осуществляет задержку приблизительно на 1,6 мкс.

В предпочтительном варианте выполнения изобретения фильтр 188 работает только "в одном направлении", то есть задержка осуществляется только в случае, когда логический уровень на выходе компаратора 184 свидетельствует, что через соленоид 104 идет ток, а затем логический уровень переключается в состояние, свидетельствующее о перегрузке. Таким образом, фильтр 188 осуществляет задержку только в условиях перегрузки. Фильтр не действует в случае, когда во-первых, через соленоид 104 ток не идет и, во-вторых, через соленоид 104 течет такой ток, что сигнал на выходе компаратора 120 переключается из низкого логического уровня в высокий. Такое изменение логического уровня будет передано через фильтр 188 в сигнальную линию 192 непосредственно. Однако следует понимать, что по желанию фильтр 188 может быть настроен для работы "в двух направлениях", то есть задержка будет осуществляться, когда ток начинает течь через соленоид.

Сигнал, соответствующий логическому уровню на выходе фильтра 188, через линию 192 подается на один вход вентиля 196 "И" с двумя входами. Выход вентиля 196 "И" соединен с входом вентиля 200 "ИЛИ" с двумя входами. Выход вентиля 200 "ИЛИ" соединен со входом D данных первого триггера 204. Выход Q первого триггера 204 соединен со вторым входом вентиля 196 "И" с двумя входами. Первый триггер 204 является триггером, запускаемым положительным фронтом, и тактируется инверсным сигналом синхронизации, то есть "CLK". Выход вентиля 200 "ИЛИ" также соединен с одним из входов вентиля 208 "И" с тремя входами. Выход этого вентиля 208 "И" с тремя входами через линию 212 соединен с затвором первого транзистора 112.

Чтобы через соленоид 104 протекал ток, первый транзистор 112 должен быть открыт. Таким образом, напряжение на затворе первого транзистора 112 должно соответствовать высокому логическому уровню. Чтобы сигнал на выходе вентиля 208 "И" с тремя входами соответствовал высокому логическому уровню, сигналы, соответствующие высокому логическому уровню должны быть поданы на каждый из трех его входов. Ниже будет описана схема подачи сигналов на эти три входа вентиля 208 "И".

Массив 124 логических элементов содержит центральный процессор 216, который управляет рядом функций схемы 100 согласно настоящему изобретению. Посредством шины 220 центральный процессор 216 соединен с разными компонентами, один из которых является регистром 224 разрешения работы соленоида. Шина 220 представляет собой множество сигнальных линий, включая линии адреса, данных и управления.

Регистр 224 разрешения работы соленоида является многоразрядным регистром, причем каждый разряд соответствует одному из соленоидов 104 с соответствующей схемой, показанной на чертеже. Следует понимать, что, хотя это и не показано, схем 100, показанных на чертеже, может быть множество, по одной для каждого соленоида 104. Центральный процессор 216 может как считывать информацию из регистра 224 разрешения работы соленоида, так и записывать ее в него. Когда центральный процессор желает использовать схему широтно-импульсной модуляции согласно настоящему изобретению, он записывает логическую единицу в соответствующий разряд регистра 224 разрешения работы соленоида для управления его работой. С другой стороны, если желательно управлять работой соленоида 104 в другом режиме, нежели режим широтно- импульсной модуляции, (например, в режиме постоянного тока), центральный процессор 216 записывает в соответствующий разряд регистра 224 разрешения работы соленоида логический нуль. Через сигнальную линию 228 сигнал, соответствующий логическому уровню разряда регистра разрешения работы соленоида, подается на средний вход вентиля 208 "И" с тремя входами. Таким образом, для того, чтобы схема широтно-импульсной модуляции согласно настоящему изобретению могла быть использована, этот разряд регистра 224 разрешения работы соленоида должен иметь высокий логический уровень.

Выход регистра 224 разрешения работы соленоида через линию 228 соединен также с разрешающим входом счетчика 232. Счетчик 232 через шину 220 соединен также с центральным процессором 216. Счетчик 232 включает соленоид 104 при включении питания схемы 100, изображенной на чертеже, или после сброса питания схемы 100.

Первоначально, после включения питания схемы 100 или после сброса (т.е. при выполнении одного или нескольких заданных условий), центральный процессор записывает в соответствующий разряд регистра 224 логический ноль. Поскольку через линию 228 этот регистр соединен со входом "сброса" ("CLR") второго триггера 236, выход Q триггера 236 также устанавливается в низкое логическое состояние. Из-за этого происходит "сброс" второго триггера. Затем центральный процессор 216 записывает в этот разряд регистра 224 разрешения работы соленоида логическую единицу. Это разрешает счетчику 232 начать обратный отсчет от начального значения, которое запрограммировано центральным процессором 216 через шину 220. В варианте выполнения изобретения, показанном в качестве примера, счетчик 232 осуществляет обратный отсчет в течение заранее заданного периода времени, равного 512 миллисекунд (с интервалами 8 мс), в течение этого времени сигнал на выходе счетчика 232 и на линии 240 соответствует низкому логическому уровню. Через линию 240 выход счетчика соединен с тактовым входом второго триггера 236. В течение времени, пока счетчик 232 осуществляет обратный отсчет, сигнал на выходе Q второго триггера 236 продолжает соответствовать низкому логическому уровню. Выход Q второго триггера 236 соединен с одним из входов вентиля 244 "И-НЕ" с двумя входами. Выход вентиля 244 "И-НЕ" с двумя входами соединен с одним из входов вентиля 200 "ИЛИ" с двумя входами. Низкий логический уровень на этом входе вентиля 244 "И-НЕ" с двумя входами устанавливает на его выходе высокий логический уровень, что устанавливает на выходе вентиля 200 "И" с двумя входами также высокий логический уровень.

В это же время схема 248 синхронизации, которая может быть выполнена в виде известного конечного автомата, подает через линию 252 сигнал на третий вход вентиля 208 "И" с тремя входами. В течение времени, пока счетчик 232 осуществляет обратный счет, схема 248 синхронизации поддерживает через линию 252 на третьем входе вентиля 208 "И" с тремя входами высокий логический уровень.

Таким образом, из предыдущего изложения понятно, что пока счетчик 232 в течение 512 мс осуществляет обратный счет, первый транзистор 112 открыт, позволяя току течь через обмотку 104 соленоида. Обычно этот начальный период времени соответствует минимальному времени, необходимому для "втягивания" соленоида 104. Однако поскольку счетчик 232 программируется центральным процессором через шину 220, счетчик 232 может быть установлен на любое желаемое значение, лишь бы оно обеспечило достаточно времени для того, чтобы соленоид 104 втянулся.

Таким образом, центральный процессор 216, регистр 224 разрешения работы соленоида, счетчик 232 и триггер 226 образуют средства для разрешения средствам переключения пропускать ток через соленоид в течение заранее заданного периода времени (в приведенном примере - 512 мс) при выполнении одного или нескольких заданных условий (например, в ответ на включение или сброс), причем этот заранее заданный период времени не зависит от множества повторяющихся временных интервалов.

По окончании этого периода в 512 мс счетчик 232 оканчивает счет и сигнал на выходе счетчика 232 и шины 240 устанавливается в высокое логическое состояние. Поскольку второй триггер запускается положительным фронтом сигнала, переход сигнала на выходе счетчика 232 от низкого логического уровня к высокому логическому уровню приводит к тому, что сигнал на выходе Q второго триггера 236 переключится из низкого логического уровня в высокий логический уровень, так как на вход D данных триггера 236 через резистор 256 подан высокий логический уровень (то есть +5 В). В это время соленоид 104 "втянут" и начинается нормальная работа схемы 100 согласно настоящему изобретению.

Согласно настоящему изобретению в процессе нормальной работы схема 100 работает в режиме широтно-импульсной модуляции в течение множества периодически повторяющихся интервалов, или "окон". В предпочтительном варианте выполнения изобретения, представленном лишь в качестве примера, длительность каждого окна составляет 160 мкс. Первые 25% времени, или 40 мкс, в течение каждого окна через обмотку 104 соленоида протекает ток, независимо от того, имеет ли место перегрузка. Протекает или нет ток в течение оставшихся 75% времени, то есть 120 мкс из каждых 160 мкс, определяется тем, зафиксирована ли перегрузка в любой момент в течение предыдущих 160 мкс.

Согласно настоящему изобретению, схема 100 осуществляет эту периодическую широтно-импульсную модуляцию с помощью счетчика 260 широтно-импульсной модуляции, на который подается сигнал синхронизации. В начале каждого из повторяющихся временных окон счетчик 260 широтно-импульсной модуляции начинает обратный отсчет. Интервалы между счетными импульсами счетчика 260 широтно-импульсной модуляции составляют, например, 40 мкс. В то время, пока счетчик 260 ведет обратный отсчет, сигнал на его выходе соответствует высокому логическому уровню. Выход счетчика соединен с инвертором 264, который преобразует сигнал высокого логического уровня на выходе счетчика 260 широтно-импульсной модуляции в сигнал низкого логического уровня на то время, пока счетчик 260 широтно-импульсной модуляции производит обратный отсчет. Выход инвертора 264 соединен со вторым входом вентиля 244 "И-НЕ" с двумя входами. Низкий логический уровень на этом входе приводит к тому, что сигнал на выходе вентиля 244 "И-НЕ" с двумя входами будет соответствовать высокому логическому уровню независимо от сигнала на другом входе вентиля 244 "И-НЕ" с двумя входами. Высокий логический уровень на выходе вентиля 244 "И-НЕ" с двумя входами приводит к тому, что сигнал на выходе вентиля 200 "ИЛИ" соответствует высокому логическому уровню. Поскольку выход вентиля 200 "ИЛИ" соединен с одним из входов вентиля 208 "И" с тремя входами, первый транзистор 112 будет открыт в течение этих 40 мкс в начале каждого окна длительностью 160 мкс. В результате в течение этого времени через соленоид 104 протекает ток.

Когда спустя 40 мкс счетчик 260 широтно-импульсной модуляции закончит счет, сигнал на выходе счетчика 260 широтно-импульсной модуляции переходит в низкий логический уровень. Тогда на выходе инвертора 264 будет высокий логический уровень. Поскольку оба входа вентиля 244 "И-НЕ" с двумя входами имеют высокий логический уровень, то на выходе вентиля 244 "И-НЕ" с двумя входами устанавливается низкий логический уровень.

Поскольку на одном из входов вентиля 200 "ИЛИ" с двумя входами установлен низкий логический уровень, то высокий логический уровень на выходе вентиля 200 "ИЛИ" определяется логическим уровнем на его другом входе. Как описано выше, этот второй вход вентиля 200 "ИЛИ" соединен с выходом вентиля 196 "И" с двумя входами, один из входов которого соединен с выходом фильтра 188. Другой вход вентиля 196 "И" с двумя входами соединен с выходом Q первого триггера 204.

Таким образом, сигнал на втором входе вентиля 200 "ИЛИ" будет иметь высокий логический уровень только если нет перегрузки соленоида 104. Использование первого триггера 204 обеспечивает схеме 100 "память", так как схема 100 способна выключить ток через соленоид 104, если перегрузка была обнаружена в любой момент в течение предшествующего окна длительностью 160 мкс. Если перегрузка произошла, то схема 100 согласно настоящему изобретению отключает ток через обмотку 104 соленоида по окончании первых 40 мкс окна длительностью 160 мкс, следующего за тем окном длительностью 160 мкс, в течение которого была обнаружена перегрузка. И наоборот, если в течение предшествующего окна длительностью 160 мкс перегрузка не наблюдалась, то схема 100 согласно настоящему изобретению разрешает протекание тока через обмотку 104 соленоида по окончании 40-микросекундного начального интервала последующего периода времени, равного 160 мкс.

В течение всего времени нормальной работы схемы 100, как описано ранее, схема 248 синхронизации устанавливает высокий логический уровень на линии 252, идущей на третий вход вентиля 208 "ИЛИ" с тремя входами. Схема 248 синхронизации прерывает ток через обмотку 104 соленоида в заранее заданные интервалы времени так, чтобы можно было осуществить проверку на размыкание обмотки 104 соленоида. В предпочтительном варианте выполнения изобретения, приведенном здесь только для примера, устройство 248 синхронизации отсчитывает 64 окна по 160 мкс каждое, то есть 10,24 мс. В течение последних 40 мкс 64-ого временного окна схема 248 синхронизации выдает сигнал низкого логического уровня на третий вход вентиля 208 "И" с тремя входами. В течение этих 40 мкс схема 248 синхронизации выдает сигналы адреса и управления на шину 268, которая соединена с двумя демультиплексорами 272 и 276 и мультиплексором 156. Схема 248 выдает нужный адрес в мультиплексор 156 для выбора сигнала 280 обратной связи от верхнего вывода ("верхн. ОС") обмотки 104 соленоида. Этот сигнал 280 напряжения проходит через мультиплексор 156 на его выход и выдается в сигнальную линию 284. Выход мультиплексора 284 соединен с инвертирующий входом операционного усилителя, включенного как компаратор 288. На неинвертирующий вход компаратора 288 подается опорное напряжение Uоп. Если произошло размыкание обмотки, то напряжение на инвертирующем входе компаратора 288 меньше, чем опорное напряжение на неинвертирующем входе компаратора 288. Тогда компаратор выдает на сигнальную линию 292 сигнал высокого логического уровня. С другой стороны, если размыкания обмотки нет (то есть соленоид 104 работает нормально), сигнал на выходе компаратора 288 и линии 292 имеет низкий логический уровень.

В то время, когда схема 248 синхронизации дает команду мультиплексору 156 выбрать сигнал 280 обратной связи от верхнего вывода ("верхн. ОС") обмотки 104 соленоида, схема 248 синхронизации обращается к верхнему демультиплексору 272, который содержит многоразрядный регистр сдвига. Сигнал с выхода компаратора с линии 292 сдвигается в верхний демультиплексор 272. Демультиплексор 272 содержит множество разрядов, каждый из которых соответствует одному из множества сигналов обратной связи как от верхнего, так и от нижнего вывода ("верхн. ОС" - 280, "нижн. ОС" - 296) соленоида, поступающих от множества схем, аналогичных схеме 100, выполненной согласно настоящему изобретению. Содержимое регистра сдвига демультиплексора в параллельном коде поступает на выход демультиплексора. Сигнал в параллельном коде подается на регистр 300 "выключения", данные из которого могут считываться процессором 216. Регистр назван регистром выключения, поскольку он хранит информацию о состоянии обмотки 104 соленоида в течение времени, когда ток через обмотку 104 соленоида выключен (то есть, о "выключенном" состоянии соленоида).

Аналогично, в течение упомянутых выше 40 мкс в конце 64-ого окна длительностью 160 мкс устройство синхронизации 248 дает команду мультиплексору 156 пропустить сигнал обратной связи от нижнего вывода ("нижн. ОС") соленоида на выход мультиплексора и в линию 284, где он сравнивается в компараторе 288 с опорным напряжением. Аналогично, если имеет место размыкание обмотки, то на выходе компаратора 288 устанавливается высокий логический уровень. С другой стороны, если соленоид 104 работает нормально, сигнал на выходе компаратора 288 имеет низкий логический уровень. В любом случае сигнал, соответствующий состоянию компаратора 288, сдвигается в верхний демультиплексор 272 и в результате попадает в регистр 300 "выключения".

В некоторый момент времени в течение периода длительностью 10,24 мс, состоящего из 64 окон длительностью 160 мкс каждое, схема 248 синхронизации дает команду мультиплексору 156 передать уровень напряжения сигнала 280 обратной связи от верхнего вывода соленоида и сигнала 296 обратной связи от нижнего вывода соленоида (однако неодновременно) для сравнения с опорным напряжением в компараторе 288. Обычно схема 248 синхронизации осуществляет это в течение первых 40 мкс в течение любого окна, когда известно, что соленоид 104 включен. Этот тест представляет собой проверку того, что на соленоид подано напряжение. Схема 248 синхронизации обращается к нижнему демультиплексору 276 для сдвига результатов этих двух тестов через демультиплексор 276 в регистр 304 "включения", который также доступен для чтения центральному процессору 216.

Согласно настоящему изобретению, схема 100 содержит также верхнюю схему 136 интерфейса, расположенную в интегральной схеме 140 интерфейса соленоида, совместно с верхней схемой управления 144, расположенной в матрице 124 логических элементов; обе схемы 136 и 144 управляют "верхним", то есть находящейся под более высоким потенциалом, выводом соленоида 104. Верхняя схема 144 управления может содержать регистр разрешения работы соленоида, который аналогичен описанному выше регистру 224, используемому для управления нижней стороной соленоида 104. Выход верхней схемы 144 управления соединен с верхней схемой 136 мультиплексора, который может содержать компаратор, два входа которого соединены с выводами верхнего датчика-резистора 132.

Если перегрузка соленоида 104 будет обнаружена в верхней части схемы, падение напряжения на верхнем датчике-резисторе 132 превысит заранее заданную величину и в результате верхний транзистор 128 закроется за счет подачи сигнала низкого логического уровня на затвор этого транзистора 128. В случае, когда соленоид работает нормально, падение напряжение на верхнем датчике-резисторе 132 не превышает порог перегрузки и второй транзистор 128 открыт, позволяя току протекать через соленоид.

В противоположность схеме, которая управляет соленоидом со стороны нижнего вывода, схема, которая управляет соленоидом со стороны верхнего вывода, не обязана работать в режиме широтно-импульсной модуляции. То есть, она может работать просто в режиме постоянного тока. Следует понимать, что верхняя схема 144 управления и верхняя схема 136 интерфейса могут содержать известные схемы и они не составляют предмет настоящего изобретения. Кроме того, такая схема может быть изъята из любой схемы управления и верхний конец обмотки 104 соленоида может быть непосредственно соединен с источником 108 напряжения.

Схема 100 возбуждения с широтно-импульсной модуляцией была описана при ее использовании для управления соленоидом с нижней стороны. Однако это сделано лишь для примера и вместо этого схема может быть соединена с верхним выводом соленоида 104. Кроме того, конкретные компоненты, выполняющие в схеме 100 конкретные функции, приведены только для примера и следует понимать, что могут быть использованы и другие компоненты. Эти компоненты известны специалистам в данной области. Кроме того, длительность повторяющихся временных "окон" приведена только в качестве примера, так же как и разделение каждого окна в отношении 25/75%.

Специалистам в данной области должно быть понятно, что могут быть сделаны очевидные структурные модификации без отхода от идеи изобретения. Поэтому объем изобретения определяется не описанными вариантами выполнения, а формулой изобретения.

Электронная схема используется для возбуждения соленоида с применением широтно-импульсной модуляции. Соленоид последовательно соединен с транзистором и датчиком-резистором. Падение напряжения на резисторе сравнивается с опорным значением для определения состояния перегрузки соленоида. Схема работает по принципу периодически повторяющихся временных интервалов, причем ток протекает через соленоид в начале каждого временного интервала, независимо от того, имеет ли место перегрузка. Если в течение временного интервала была обнаружена перегрузка, тогда в течение следующего временного интервала ток через соленоид выключают по окончании начального интервала в этом окне. Напротив, если в течение временного интервала не была обнаружена перегрузка, тогда току позволяют течь в течение всего следующего временного интервала. Кроме того, имеется цепь обратной связи для обнаружения разрыва обмотки соленоида в конце одного из временных интервалов после прохождения множества таких интервалов. Технический результат заключается в возможности ограничения электрического тока, текущего по обмотке соленоида и обнаружения размыкания катушки соленоида. 7 з.п. ф-лы, 1 ил.

| US 4764840 A, 18.06.1988 | |||

| Устройство для управления индуктивной нагрузкой со встроенным контролем | 1989 |

|

SU1624543A1 |

| SU 1592878 A1, 15.09.1990 | |||

| Устройство для управления электромагнитами | 1984 |

|

SU1229851A2 |

| US 4556926 A, 03.12.1985 | |||

| EP 0449543 A1, 02.10.1991. | |||

Авторы

Даты

2000-10-10—Публикация

1996-07-22—Подача