Изобретение относится к системам телекоммуникаций и вычислительной техники и может найти применение для измерения параметров ошибок, искажающих данные в каналах передачи или воспроизведения информации со вставками/выпадениями бит.

Известно устройство, предназначенное для тестирования каналов связи с использованием псевдослучайной последовательности (PN-последовательности) [1] , приемная часть которого содержит два генератора PN-последовательности, две схемы сравнения последовательностей, счетчик подсчитывающий число совпадающих бит, четыре триггера и логические элементы И, ИЛИ, НЕ.

Известное устройство формирует поток ошибочных бит, обнаруженных в принятом из канала тестовом сигнале, путем сравнения последовательности бит тестового сигнала с битами PN-последовательности, восстановленной первым генератором. Устройство обнаруживает нарушение синхронизации (из-за вставок или выпадений бит) между последовательностью бит тестового сигнала и восстановленной PN-последовательностью и осуществляет повторную синхронизацию для предотвращения неверного формирования потока ошибочных бит. Определение нарушения синхронизации осуществляется с помощью второго генератора PN-последовательности путем опознания в потоке ошибочных бит сдвинутой по фазе PN-последовательности.

Недостатки устройства:

- относительно высокая вероятность ошибочного определения нарушения синхронизации из-за небольшой длины анализируемого при опознании PN-последовательности участка потока ошибочных бит;

- добавление достаточно большого количества ложных ошибочных бит в формируемый поток ошибочных бит из-за нарушения синхронизации, что объясняется относительно большой величиной задержки принятия решения о восстановлении синхронизации;

- отсутствие возможности измерения величин вставок или выпадений бит и места их расположения.

Известно устройство для измерения уровня ошибок в канале [2], измеряющее уровень ошибок в процессе передачи данных с использованием PN-последовательности. Устройство содержит последовательно-параллельный преобразователь, сеть корреляторов, умножитель в конечном поле, схему сравнения, буферную память данных, ряд дополнительных блоков.

Устройство [2] так же, как устройство [1], формирует поток ошибочных бит путем сравнения последовательности бит тестового сигнала с битами реконструированной сетью корреляторов PN-последовательности. Сеть корреляторов поддерживает правильную синхронизацию между последовательностью бит тестового сигнала и реконструированной PN-последовательностью даже при наличии вставок или выпадений бит в тестовом сигнале. В устройстве [2] устранено добавление ложных ошибочных бит в формируемый поток ошибок из-за нарушения синхронизации.

Недостатками устройства [2] являются:

- аддитивные ошибки, возможные после вставок или выпадений бит, могут привести к значительной задержке переключения на необходимую фазу РN-последовательности выхода сети корреляторов и, следовательно, к добавлению в поток ошибочных бит некоторого числа неверно определенных ошибок;

- отсутствие возможности измерения величин вставок или выпадений бит и места их расположения.

Известно устройство [3] для определения нарушения синхронизации между последовательностью бит тестового сигнала и восстановленной в приемном устройстве PN-последовательностью, предусматривающее восстановление синхронизации для предотвращения неверного формирования потока ошибочных бит. Устройство содержит генератор PN-последовательности, схему сравнения последовательностей бит, i корреляторов, i пороговых детекторов, анализатор суммы взаимно корреляционных функций, анализатор проскальзываний бит, анализатор уровня ошибок.

Для определения нарушения синхронизации используются i корреляторов, каждый из которых вычисляет взаимно корреляционную функцию между одним из i сегментов эталонной PN-последовательности и принятой из канала тестовой последовательностью. Выходные сигналы корреляторов обрабатываются пороговыми детекторами и суммируются. Смещение максимумов в полученной сумме взаимно корреляционных функций говорит о нарушении синхронизации. Для ограничения неверного формирования потока ошибочных бит генератор эталонной PN-последовательности синхронизируется по каждому выделенному максимуму.

Недостатки устройства:

- добавление достаточно большого количества ложных ошибочных бит в формируемый поток ошибочных бит из-за нарушения синхронизации, так как возможна относительно большая величина временного интервала между вставкой (выпадением) бит и ресинхронизацией генератора PN-последовательности, которая осуществляется дискретно (i раз на периоде PN-последовательности);

- невозможность достаточно точного определения места вставки или выпадения бит (можно только определить интервал между двумя максимумами, в котором они произошли).

Наиболее близким по технической сущности к заявляемому изобретению является выбранное в качестве прототипа устройство, предназначенное для измерения уровня битовых ошибок в канале [4], содержащее два генератора PN-последовательности, две схемы сравнения последовательностей бит, четыре сдвиговых регистра для задержки кадров, четыре детектора проскальзываний (вставок или выпадений) кадров, счетчик ошибочных бит, счетчик проскальзываний, контроллер, различную логику.

Устройство-прототип аналогично устройствам [1, 2, 3] формирует поток ошибочных бит, обнаруженных в принятом из канала тестовом сигнале, путем сравнения последовательности бит тестового сигнала с битами PN-последовательности, восстановленной основным PN-генератором. Устройство также обнаруживает нарушение синхронизации (из-за вставок или выпадений кадров) между последовательностью бит тестового сигнала и восстановленной PN-последовательностью и осуществляет повторную синхронизацию для предотвращения неверного формирования потока ошибочных бит. Обнаружение проскальзываний и определение их величины осуществляется с помощью четырех детекторов проскальзываний, каждый из которых сравнивает восстановленную PN-последовательность с одной из четырех смещенных последовательностей бит тестового сигнала.

В отличие от ранее рассмотренных устройств [1, 2] в устройстве-прототипе реализован подсчет числа проскальзываний.

К недостаткам прототипа можно отнести:

- определяется проскальзывание только небольшого числа кадров (одного или двух);

- аддитивные ошибки, возможные после проскальзываний, могут привести к значительной задержке обнаружения нарушения синхронизации и, следовательно, к добавлению в счетчик ошибочных бит некоторого числа неверно определенных ошибок;

- отсутствие возможности измерения места расположения ошибочных бит и проскальзываний в потоке данных.

Технической задачей изобретения является определение размеров и места расположения вставок и выпадений бит в потоке данных из канала, минимизируя влияние расположенных рядом аддитивных ошибок, а также более точное восстановление потока аддитивных ошибок, минимизируя влияние вставок и выпадений бит.

Поставленная техническая задача решается тем, что в известное устройство, содержащее первый регистр сдвига, второй регистр сдвига, схему сравнения последовательностей, причем вход первого регистра сдвига является входом устройства для анализируемой битовой последовательности, первый выход первого регистра сдвига соединен со входом второго регистра сдвига, выход второго регистра сдвига соединен с первым входом схемы сравнения последовательностей, согласно изобретению введены преобразователь синхросимволов в локаторы, первый вычитатель, первый счетчик, буфер относительных локаторов, первая схема сравнения кодов, блок нахождения существенного относительного локатора, буфер существенных относительных локаторов, буфер весов существенных относительных локаторов, блок принятия решения о наличии ошибок, блок формирования потока состояний канала, причем входы преобразователя синхросимволов в локаторы соединены со вторыми выходами первого регистра сдвига, первые входы первого вычитателя соединены с выходами преобразователя синхросимволов в локаторы, вторые входы первого вычитателя соединены с выходами первого счетчика, выходы первого вычитателя соединены со входами буфера относительных локаторов, с первыми входами первой схемы сравнения кодов и с первыми входами блока нахождения существенного относительного локатора, выходы буфера относительных локаторов соединены со вторыми входами первой схемы сравнения кодов и со вторыми входами блока нахождения существенного относительного локатора, выход первой схемы сравнения кодов соединен с третьим входом блока нахождения существенного относительного локатора, первые выходы блока нахождения существенного относительного локатора соединены со входами буфера существенных относительных локаторов и с первыми входами блока принятия решения о наличии ошибок, вторые выходы блока нахождения существенного относительного локатора соединены со входами буфера весов существенных относительных локаторов и со вторыми входами блока принятия решения о наличии ошибок, выходы буфера существенных относительных локаторов соединены с третьими входами блока принятия решения о наличии ошибок, выходы буфера весов существенных относительных локаторов соединены с четвертыми входами блока принятия решения о наличии ошибок, первый выход блока принятия решения о наличии ошибок соединен с первым входом блока формирования потока состояний канала, второй выход блока принятия решения о наличии ошибок соединен со вторым входом блока формирования потока состояний канала, третьи выходы блока принятия решения о наличии ошибок соединены с третьими входами блока формирования потока состояний канала, четвертый выход блока принятия решения о наличии ошибок соединен с четвертым входом блока формирования потока состояний канала, пятый выход блока принятия решения о наличии ошибок является выходом "Отказ от измерения" устройства, первый выход блока формирования потока состояний канала является выходом устройства "Строб записи", вторые выходы блока формирования потока состояний канала являются выходами "Тип ошибки" устройства, третьи выходы блока формирования потока состояний канала являются выходами "Размер ошибки" устройства, причем блок нахождения существенного относительного локатора содержит первый мультиплексор, первый-одиннадцатый шинные формирователи, первый-шестой буферные регистры, первый селектор нулевого кода, оперативное запоминающее устройство, первый элемент И, устройство инициализации, устройство управления, причем первые входы первого мультиплексора являются первыми входами блока нахождения существенного относительного локатора, вторые входы первого мультиплексора являются вторыми входами блока нахождения существенного относительного локатора, вход разрешения работы устройства управления является третьим входом блока нахождения существенного относительного локатора, вход управления первого мультиплексора соединен с первым выходом устройства управления, выходы первого мультиплексора соединены со входами данных первого шинного формирователя и со входами данных второго шинного формирователя, вход управления первого шинного формирователя соединен со вторым выходом устройства управления, вход управления второго шинного формирователя соединен с третьим выходом устройства управления, выходы первого шинного формирователя соединены с шиной адреса, выходы второго шинного формирователя соединены с шиной данных, первые адресные входы оперативного запоминающего устройства соединены с шиной адреса, второй адресный вход оперативного запоминающего устройства соединен с третьим входом первого элемента И, с четвертым выходом устройства управления и с третьим выходом устройства инициализации, третий адресный вход оперативного запоминающего устройства соединен со вторым входом первого элемента И, с пятым выходом устройства управления и с четвертым выходом устройства инициализации, вход управления чтением/записью оперативного запоминающего устройства соединен с первым входом первого элемента И и с шестым выходом устройства управления, вход выборки оперативного запоминающего устройства соединен с двадцать четвертым выходом устройства управления, выходы данных оперативного запоминающего устройства соединены с шиной данных, входы первого селектора нулевого кода соединены с шиной адреса, выход первого селектора нулевого кода соединен с четвертым входом первого элемента И, входы данных первого буферного регистра соединены с шиной данных, первый управляющий вход первого буферного регистра соединен с восьмым выходом устройства управления, второй управляющий вход первого буферного регистра соединен с девятым выходом устройства управления, выходы первого буферного регистра соединены со входами данных третьего шинного формирователя и со входами данных четвертого шинного формирователя, управляющий вход третьего шинного формирователя соединен с десятым выходом устройства управления, выходы третьего шинного формирователя соединены с шиной адреса, управляющий вход четвертого шинного формирователя соединен с одиннадцатым выходом устройства управления, выходы четвертого шинного формирователя соединены с шиной данных, входы данных второго буферного регистра соединены с шиной данных, первый управляющий вход второго буферного регистра соединен с двенадцатым выходом устройства управления, второй управляющий вход второго буферного регистра соединен с тринадцатым выходом устройства управления, третий управляющий вход второго буферного регистра соединен с четырнадцатым выходом устройства управления, выходы второго буферного регистра соединены со входами данных пятого шинного формирователя и со входами данных шестого шинного формирователя, управляющий вход пятого шинного формирователя соединен с пятнадцатым выходом устройства управления, выходы пятого шинного формирователя соединены с шиной адреса, управляющий вход шестого шинного формирователя соединен с шестнадцатым выходом устройства управления, выходы шестого шинного формирователя соединены с шиной данных, входы данных третьего буферного регистра соединены с шиной данных, управляющий вход третьего буферного регистра соединен с семнадцатым выходом устройства управления, выходы третьего буферного регистра соединены со входами данных седьмого шинного формирователя и со входами данных восьмого шинного формирователя, управляющий вход седьмого шинного формирователя соединен с восемнадцатым выходом устройства управления, выходы седьмого шинного формирователя соединены с шиной адреса, управляющий вход восьмого шинного формирователя соединен с девятнадцатым выходом устройства управления, выходы восьмого шинного формирователя соединены с шиной данных, входы данных четвертого буферного регистра соединены с шиной данных, первый управляющий вход четвертого буферного регистра соединен с двадцатым выходом устройства управления, второй управляющий вход четвертого буферного регистра соединен с двадцать первым выходом устройства управления, выходы четвертого буферного регистра соединены со входами данных девятого шинного формирователя и со входами данных десятого шинного формирователя, управляющий вход девятого шинного формирователя соединен с двадцать вторым выходом устройства управления, выходы девятого шинного формирователя соединены с шиной адреса, управляющий вход десятого шинного формирователя соединен с двадцать третьим выходом устройства управления, выходы десятого шинного формирователя соединены с шиной данных, входы данных пятого буферного регистра соединены с шиной данных, управляющий вход пятого буферного регистра соединен с выходом первого элемента И, выходы пятого буферного регистра соединены со входами данных одиннадцатого шинного формирователя и являются первыми выходами блока нахождения существенного относительного локатора, выходы одиннадцатого шинного формирователя соединены с шиной адреса, управляющий вход одиннадцатого шинного формирователя соединен с управляющим входом шестого буферного регистра и с седьмым выходом устройства управления, входы данных шестого буферного регистра соединены с шиной данных, выходы шестого буферного регистра являются вторыми выходами блока нахождения существенного относительного локатора, первый вход устройства инициализации и тактовый вход устройства управления соединены с шиной второго тактового сигнала, вторые входы устройства инициализации соединены с шиной кода размера окна, третий вход устройства инициализации соединен с шиной инициализации, первые выходы устройства инициализации соединены с шиной адреса, вторые выходы устройства инициализации соединены с шиной данных, причем устройство инициализации содержит второй счетчик, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, второй селектор нулевого кода, вторую схему сравнения кодов, двенадцатый шинный формирователь, тринадцатый шинный формирователь, четырнадцатый шинный формирователь, причем тактовый вход второго счетчика является первым входом устройства инициализации, вторые входы второго мультиплексора соединены с первыми входами второй схемы сравнения кодов и являются вторыми входами устройства инициализации, первые входы второго мультиплексора и вторые входы третьего мультиплексора соединены с шиной нулевого кода, первые входы третьего мультиплексора соединены с шиной единичного кода, первые выходы второго счетчика соединены со входами второго селектора нулевого кода, со вторыми входами второй схемы сравнения кодов, с третьими и четвертыми входами четвертого мультиплексора и со входами данных четырнадцатого шинного формирователя, вторые выходы второго счетчика соединены с управляющими входами четвертого мультиплексора и со входами данных тринадцатого шинного формирователя, выход второго селектора нулевого кода соединен с управляющим входом второго мультиплексора, выход второй схемы сравнения кодов соединен с управляющим входом третьего мультиплексора, выходы второго мультиплексора соединены с первыми входами четвертого мультиплексора, выходы третьего мультиплексора соединены со вторыми входами четвертого мультиплексора, выходы четвертого мультиплексора соединены со входами данных двенадцатого шинного формирователя, управляющий вход двенадцатого шинного формирователя соединен с управляющим входом тринадцатого шинного формирователя, с управляющим входом четырнадцатого шинного формирователя и является третьим входом устройства инициализации, выходы двенадцатого шинного формирователя являются вторыми выходами устройства инициализации, выходы тринадцатого шинного формирователя являются третьим и четвертым выходами устройства инициализации, выходы четырнадцатого шинного формирователя являются первыми выходами устройства инициализации, причем блок принятия решения о наличии ошибок содержит второй вычитатель, третий вычитатель, первый сумматор, второй сумматор, третью схему сравнения кодов, четвертую схему сравнения кодов, пятую схему сравнения кодов, шестую схему сравнения кодов, седьмую схему сравнения кодов, пятый мультиплексор, шестой мультиплексор, третий счетчик, четвертый счетчик, преобразователь локаторов в синхробиты, схему сравнения последовательностей, второй элемент И, третий элемент И, четвертый элемент И, первый инвертор, JK-триггер, третий селектор нулевого кода, умножитель на два, элемент И-НЕ, причем вторые входы второго вычитателя соединены с первыми входами третьего вычитателя, со вторыми входами шестого мультиплексора и являются первыми входами блока принятия решения о наличии ошибок, первые входы четвертой схемы сравнения кодов соединены со вторыми входами шестой схемы сравнения кодов и являются вторыми входами блока принятия решения о наличии ошибок, первые входы второго вычитателя соединены со вторыми входами третьего вычитателя, с первыми входами шестого мультиплексора и являются третьими входами блока принятия решения о наличии ошибок, вторые входы четвертой схемы сравнения кодов соединены с первыми входами пятой схемы сравнения кодов и являются четвертыми входами блока принятия решения о наличии ошибок, выход четвертой схемы сравнения кодов соединен с первым управляющим входом четвертого счетчика, с управляющим входом шестого мультиплексора, с J-входом JK-триггера и с третьим входом четвертого элемента И, выходы шестого мультиплексора соединены с первыми входами первого сумматора, выходы третьего счетчика соединены со вторыми входами первого сумматора, выходы первого сумматора соединены с преобразователем локаторов в синхробиты, выход преобразователя локаторов в синхробиты соединен со вторым входом схемы сравнения последовательностей, выход схемы сравнения последовательностей соединен с первым входом третьего элемента И, вторые входы пятой схемы сравнения кодов и первые входы шестой схемы сравнения кодов соединены с шиной кода порога, выход пятой схемы сравнения кодов соединен с первым входом второго элемента И, выход шестой схемы сравнения кодов соединен со вторым входом второго элемента И, выход второго элемента И соединен со вторым входом третьего элемента И, со входом первого инвертора и с первым входом четвертого элемента И, выход третьего элемента И является четвертым выходом блока принятия решения о наличии ошибок, выход первого инвертора является пятым выходом блока принятия решения о наличии ошибок, выходы второго вычитателя соединены с первыми входами пятого мультиплексора и с первыми входами третьей схемы сравнения кодов, выходы третьего вычитателя соединены со вторыми входами пятого мультиплексора и со вторыми входами третьей схемы сравнения кодов, выход третьей схемы сравнения кодов соединен с управляющим входом пятого мультиплексора, со вторым входом элемента И-НЕ и является вторым выходом блока принятия решения о наличии ошибок, выходы пятого мультиплексора соединены со входами третьего селектора нулевого кода, со вторыми входами второго сумматора и являются третьими выходами блока принятия решения о наличии ошибок, инверсный выход третьего селектора нулевого кода соединен с четвертым входом четвертого элемента И, прямой выход третьего селектора нулевого кода соединен с K-входом JK-триггера и со вторым управляющим входом четвертого счетчика, тактовый вход JK-триггера и тактовый вход четвертого счетчика соединены с шиной первого тактового сигнала, инверсный выход JK-триггера соединен со вторым входом четвертого элемента И, выход четвертого элемента И является первым выходом блока принятия решения о наличии ошибок, выходы четвертого счетчика соединены со входами умножителя на два, выходы умножителя на два соединены с первыми входами второго сумматора, выходы второго сумматора соединены с первыми входами седьмой схемы сравнения кодов, вторые входы седьмой схемы сравнения кодов соединены с шиной кода размера окна, выход седьмой схемы сравнения кодов соединен с первым входом элемента И-НЕ, выход элемента И-НЕ соединен с третьим входом третьего элемента И, причем блок формирования потока состояний канала содержит D-триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый элемент И, шестой элемент И, первый элемент ИЛИ, второй элемент ИЛИ, второй инвертор, пятый счетчик, седьмой мультиплексор, восьмой мультиплексор, причем D-вход D-триггера соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является четвертым входом блока формирования потока состояний канала, тактовый вход D-триггера соединен со вторым входом пятого элемента И, со входом второго инвертора, с тактовым входом пятого счетчика и с шиной третьего тактового сигнала, выход D-триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом седьмого мультиплексора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом пятого элемента И и с первым входом второго элемента ИЛИ, выход пятого элемента И соединен с первым входом первого элемента ИЛИ, второй вход первого элемента ИЛИ соединен со вторым входом второго элемента ИЛИ и является первым входом блока формирования потока состояний канала, выход первого элемента ИЛИ соединен со вторым входом шестого элемента И, первый вход шестого элемента И соединен с шиной четвертого тактового сигнала, выход шестого элемента И является первым выходом блока формирования потока состояний канала, выход второго элемента ИЛИ соединен со входом загрузки пятого счетчика, входы данных пятого счетчика соединены с шиной единичного кода, выходы пятого счетчика соединены с первыми входами восьмого мультиплексора, второй вход седьмого мультиплексора является вторым входом блока формирования потока состояний канала, вторые входы восьмого мультиплексора являются третьими входами блока формирования потока состояний канала, выход второго инвертора соединен с управляющим входом седьмого мультиплексора и с управляющим входом восьмого мультиплексора, выход седьмого мультиплексора и выход второго инвертора являются вторыми выходами блока формирования потока состояний канала, выходы восьмого мультиплексора являются третьими выходами блока формирования потока состояний канала.

Взаимодействие введенных функциональных блоков позволяет использовать предлагаемое устройство для измерения параметров ошибок в любых битовых каналах и получать с его помощью в реальном времени непосредственно поток состояний исследуемого канала, включающий кроме информации о пакетах аддитивных ошибок и промежутков между ними также исчерпывающую информацию об ошибках синхронизации (тип ошибки: вставка или выпадение бит и размер ошибки синхронизации - количество бит вставок или выпадений). Введение (помимо некоторых вспомогательных элементов) блока нахождения существенного локатора 8 (предусматривающего обработку относительных локаторов по мажоритарному принципу) для оценки расположения обрабатываемого бита в тестовой последовательности позволяет получать точную информацию об ошибках синхронизации на исследуемом участке последовательности на следующем этапе обработки (блоком принятия решения о наличии ошибок 11). Введение блока формирования потока состояний канала позволяет приводить к удобному для регистрации виду информацию, получаемую с выхода блока принятия решения о наличии ошибок 11.

Сущность изобретения заключается в следующем. Для обнаружения ошибок синхронизации используются тестовые последовательности (M-последовательности, последовательности Де Брейна, модифицированные последовательности Де Брейна), характеризующиеся тем, любые расположенные подряд m бит последовательности (синхросимволы) однозначно определяют ее фазу. Принятая из канала тестовая последовательность преобразуется в поток синхросимволов, в котором выделяются две последовательности одинаковой длины (окна). На основании анализа синхросимволов в каждом окне формируются левая и правая оценки расположения текущего анализируемого бита тестовой последовательности (находящегося в центре между окнами). Найденные оценки позволяют определить наличие и величину вставок или выпадений бит на анализируемом участке тестовой последовательности. По разности оценок можно судить о величине вставки или выпадения. Если разность оценок равна нулю, то вставки или выпадения бит на анализируемом участке тестовой последовательности отсутствуют. Использование мажоритарного принципа анализа синхросимволов при определении оценок позволяет с высокой точностью локализовывать ошибки синхронизации на фоне аддитивных ошибок и определять количество бит вставок и выпадений.

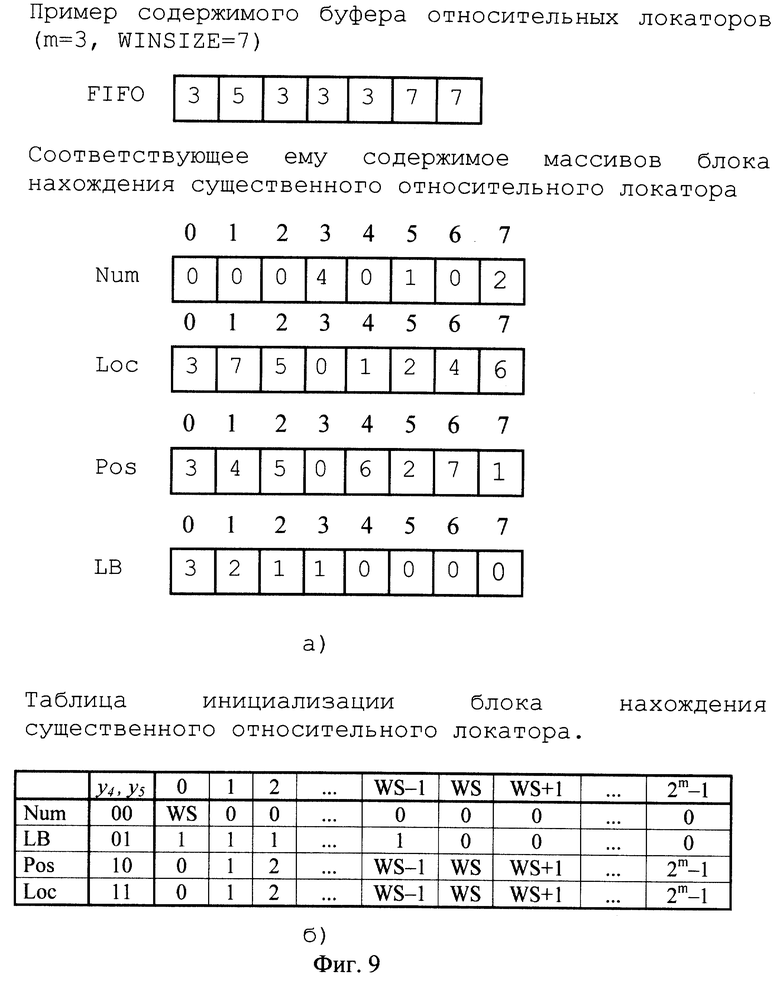

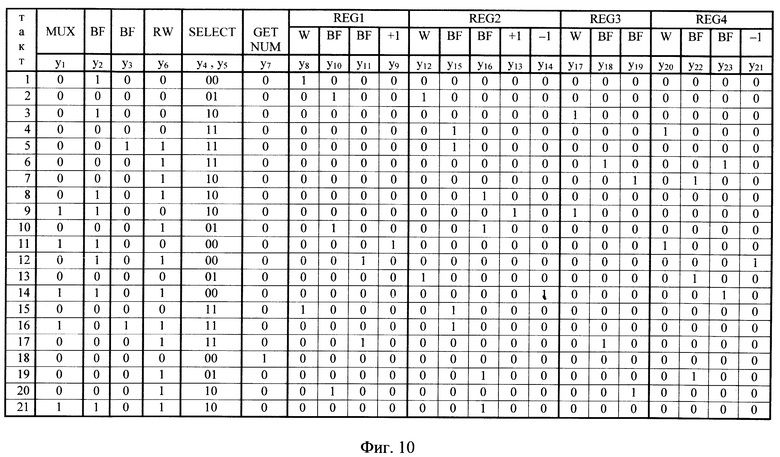

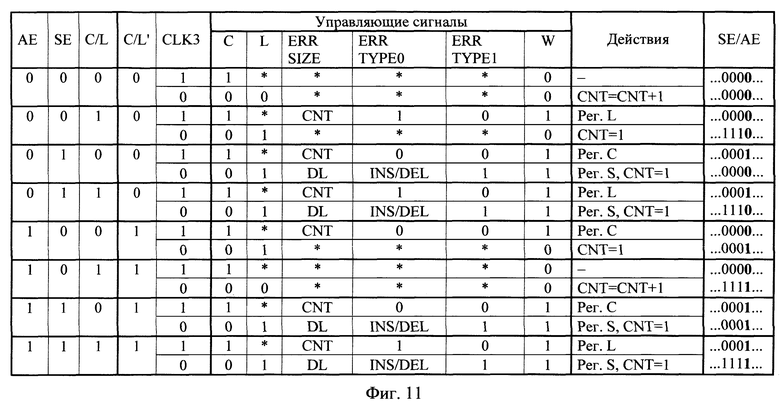

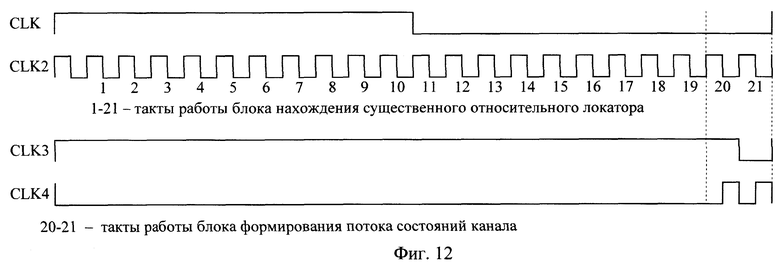

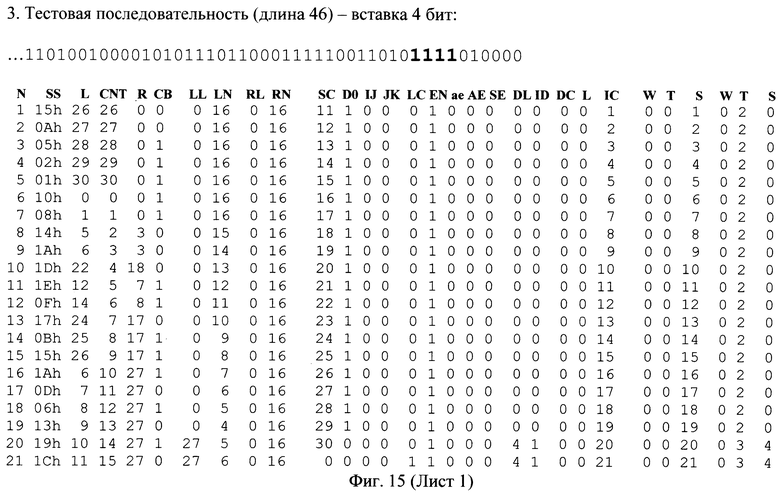

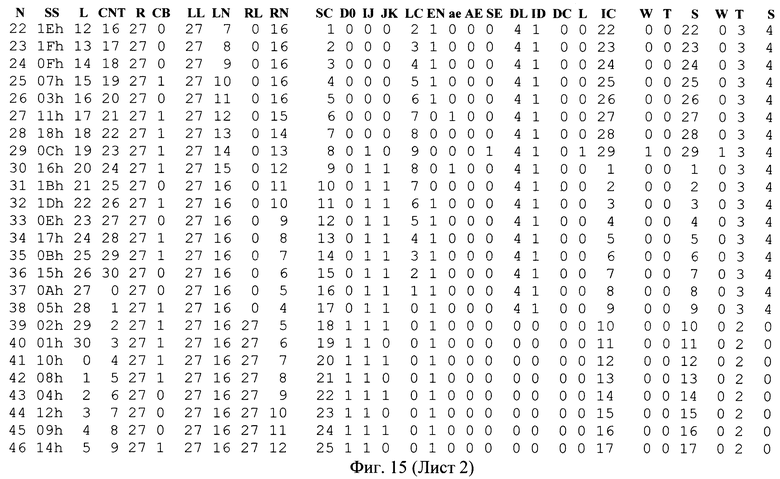

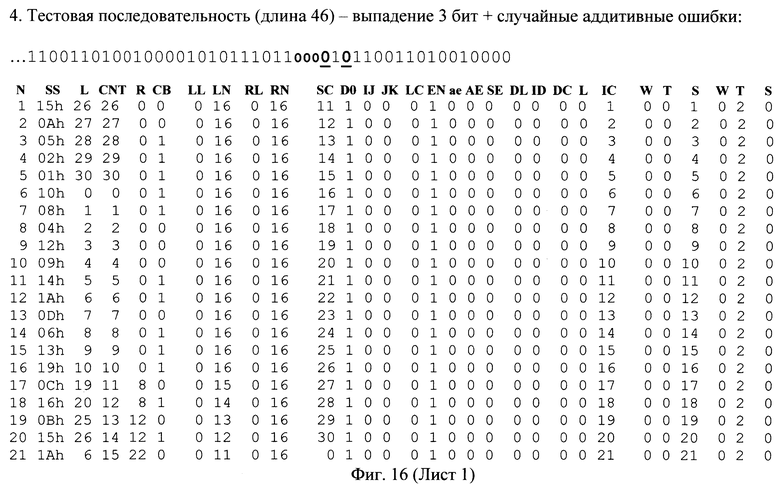

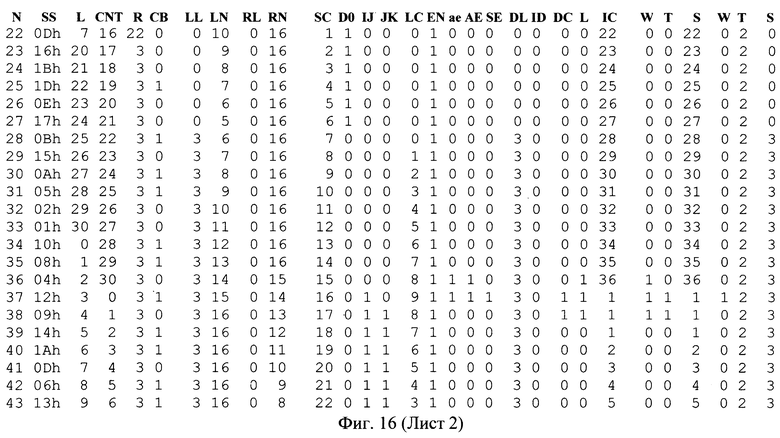

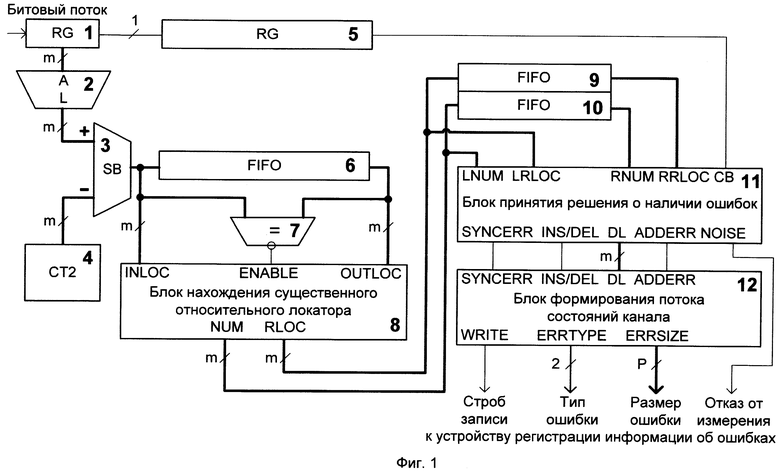

На фиг. 1 приведена функциональная схема предлагаемого устройства измерения параметров ошибок в канале; на фиг.2 приведена функциональная схема блока нахождения существенного относительного локатора; на фиг.3 приведена функциональная схема устройства инициализации (блока нахождения существенного относительного локатора); на фиг.4 приведена функциональная схема блока принятия решения о наличии ошибок; на фиг.5 приведена функциональная схема блока формирования потока состояний канала; на фиг.6 показан линейный регистр сдвига с обратными связями для случая m=5, генерируемая данным регистром М-последовательность, а также таблица соответствия локаторов и синхросимволов для этой последовательности; на фиг.7 поясняется принцип замены двух блоков нахождения существенного относительного локатора на один с буферизацией его выходных данных; на фиг.8 приведен алгоритм функционирования блока нахождения существенного относительного локатора; на фиг.9 приведен пример содержимого буфера относительных локаторов и соответствующее ему содержимое четырех массивов (которые выделяются в оперативном запоминающем устройстве), а также в таблице приведены значения, которыми заполняются массивы в начале работы устройства; на фиг.10 приведена таблица управляющих сигналов y1...y23. генерируемых устройством управления блоком нахождения существенного относительного локатора; на фиг.11 приведена таблица, поясняющая работу блока формирования потока состояний канала; на фиг.12 приведены временные диаграммы тактовых сигналов устройства измерения параметров ошибок в канале; на фиг.13-16 приведены примеры работы устройства измерения параметров ошибок при различных конфигурациях ошибок.

В описании устройства и на чертежах используются следующие обозначения:

m - степень порождающего многочлена М-последовательности (число ступеней линейного регистра сдвига с обратными связями),

n - период псевдослучайной последовательности,

А - синхросимвол,

L - локатор синхросимвола,

СТ2 - двоичный счетчик,

RG - регистр,

SM - сумматор,

SB - вычитатель,

FIFO - буфер (набор регистров, последовательно соединенных m-разрядными шинами),

BF - шинный формирователь,

RAM - оперативное запоминающее устройство,

MUX - мультиплексор,

ША - шина адреса,

ШД - шина данных,

УИ - устройство инициализации,

УУ - устройство управления,

INLOC - входящий относительный локатор (in locator),

OUTLOC - выходящий относительный локатор (out locator),

ENABLE - сигнал разрешения работы блока нахождения существенного относительного локатора,

RLOC - существенный относительный локатор (relative locator),

NUM - вес существенного относительного локатора (number),

LRLOC - существенный относительный локатор левого окна (left relative locator),

LNUM - вес существенного относительного локатора левого окна,

RRLOC - существенный относительный локатор правого окна (right relative locator),

RNUM - вес существенного относительного локатора правого окна,

СВ - центральный бит (общий для левого и правого окон) (central bit),

SYNCERR, SE - сигнал ошибки синхронизации (synchronization error),

INS/DEL - тип ошибки синхронизации: вставка или выпадение бит (insertion/deletion),

DL - размер ошибки синхронизации (количество бит),

NOISE - сигнал невозможности корректного измерения параметров ошибок (шум),

ADDERR, АЕ - сигнал аддитивной ошибки,

WRITE - строб записи для внешнего устройства регистрации информации об ошибках,

ERRTYPE - тип ошибки (error type),

ERRSIZE - размер ошибки (error size),

WINSIZE, WS - размер буфера относительных локаторов (window size),

INIT - сигнал инициализации для устройства инициализации блока нахождения существенных относительных локаторов,

THRESHOLD - порог для весов существенных относительных локаторов левого и правого окон,

CLK - первый тактовый сигнал,

CLK2 - второй тактовый сигнал,

CLK3 - третий тактовый сигнал,

CLK4 - четвертый тактовый сигнал,

REG1 - буферный регистр 16,

REG2 - буферный регистр 19,

REG3 - буферный регистр 22,

REG4 - буферный регистр 25.

Num - массив, предназначенный для хранения количества соответствующих локаторов (number),

Loc - массив, в котором хранятся локаторы в порядке убывания их частоты появления в буфере относительных локаторов (locator),

Pos - массив, взаимно обратный к массиву Loc (position),

LB - массив, предназначенный для хранения левых границ групп одинаковых количеств локаторов, как если бы локаторы были отсортированы (left bound),

Numi, Loci, Posi, LB1 - обозначения, отражающие содержимое буферных регистров REG1, REG2, REG3, REG4 и относящиеся к обработке входящего существенного относительного локатора (INLOC),

Num2, Eoc2, Pos2, LB2 - обозначения, отражающие содержимое буферных регистров REG1, REG2, REG3, REG4 и относящиеся к обработке выходящего существенного относительного локатора (OUTLOC),

ПЗУ - постоянное запоминающее устройство.

Устройство измерения параметров ошибок (фиг.1) содержит первый регистр сдвига (1), второй регистр сдвига (5), преобразователь синхросимволов в локаторы (2), первый вычитатель (3), первый счетчик (4), буфер относительных локаторов (6), первую схему сравнения кодов (7), блок нахождения существенного относительного локатора (8), буфер существенных относительных локаторов (9), буфер весов существенных относительных локаторов (10), блок принятия решения о наличии ошибок (11), блок формирования потока состояний канала (12).

На вход первого регистра сдвига (1) подается анализируемая битовая последовательность. Первый выход первого регистра сдвига (1) соединен со входом второго регистра сдвига (5). Выход второго регистра сдвига (5) соединен с первым входом схемы сравнения последовательностей (52). Входы преобразователя синхросимволов в локаторы (2) соединены со вторыми выходами первого регистра сдвига (1). Первые входы первого вычитателя (3) соединены с выходами преобразователя синхросимволов в локаторы (2), вторые входы первого вычитателя (3) соединены с выходами первого счетчика (4), выходы первого вычитателя (3) соединены со входами буфера относительных локаторов (6), с первыми входами первой схемы сравнения кодов (7) и с первыми входами блока нахождения существенного относительного локатора (8). Выходы буфера относительных локаторов (6) соединены со вторыми входами первой схемы сравнения кодов (7) и со вторыми входами блока нахождения существенного относительного локатора (8). Выход первой схемы сравнения кодов (7) соединен с третьим входом блока нахождения существенного относительного локатора (8). Первые выходы блока нахождения существенного относительного локатора (8) соединены со входами буфера существенных относительных локаторов (9) и с первыми входами блока принятия решения о наличии ошибок (11), вторые выходы блока нахождения существенного относительного локатора (8) соединены со входами буфера весов существенных относительных локаторов (10) и со вторыми входами блока принятия решения о наличии ошибок (11). Выходы буфера существенных относительных локаторов (9) соединены с третьими входами блока принятия решения о наличии ошибок (11). Выходы буфера весов существенных относительных локаторов (10) соединены с четвертыми входами блока принятия решения о наличии ошибок (11). Первый выход блока принятия решения о наличии ошибок (11) соединен с первым входом блока формирования потока состояний канала (12), второй выход блока принятия решения о наличии ошибок (11) соединен со вторым входом блока формирования потока состояний канала (12), третьи выходы блока принятия решения о наличии ошибок (11) соединены с третьими входами блока формирования потока состояний канала (12), четвертый выход блока принятия решения о наличии ошибок (11) соединен с четвертым входом блока формирования потока состояний канала (12), пятый выход блока принятия решения о наличии ошибок (11) формирует сигнал "Отказ от измерения" для устройства регистрации информации об ошибках. Первый выход блока формирования потока состояний канала (12) формирует сигнал "Строб записи" для устройства регистрации информации об ошибках, вторые выходы блока формирования потока состояний канала (12) формируют сигнал "Тип ошибки" для устройства регистрации информации об ошибках, третьи выходы блока формирования потока состояний канала (12) формируют сигнал "Размер ошибки" для устройства регистрации информации об ошибках.

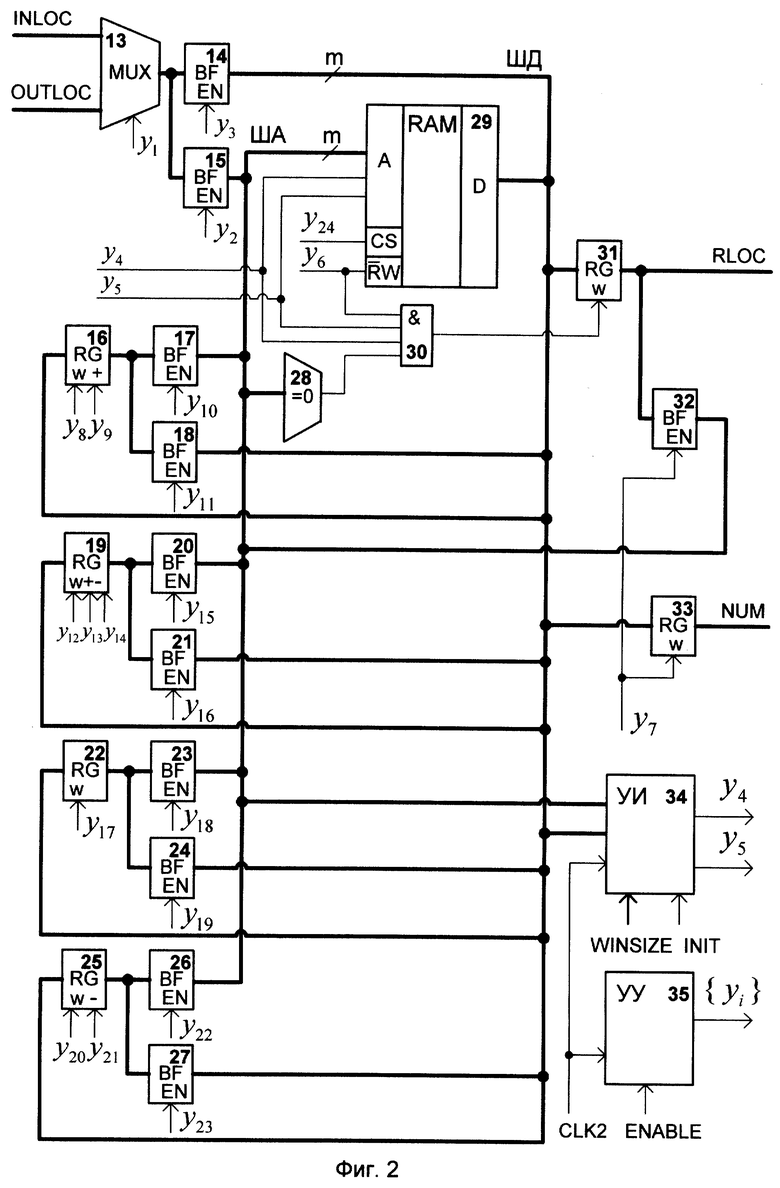

Блок нахождения существенного относительного локатора (фиг.2) содержит первый мультиплексор (13), первый шинный формирователь (15), второй шинный формирователь (14), третий шинный формирователь (17), четвертый шинный формирователь (18), пятый шинный формирователь (20), шестой шинный формирователь (21), седьмой шинный формирователь (23), восьмой шинный формирователь (24), девятый шинный формирователь (26), десятый шинный формирователь (27), одиннадцатый шинный формирователь (32), первый буферный регистр (16), второй буферный регистр (19), третий буферный регистр (22), четвертый буферный регистр (25), пятый буферный регистр (31), шестой буферный регистр (33), первый селектор нулевого кода (28), оперативное запоминающее устройство (29), первый элемент И (30), устройство инициализации (34), устройство управления (35).

Первые входы первого мультиплексора (13) являются первыми входами блока нахождения существенного относительного локатора (8), вторые входы первого мультиплексора (13) являются вторыми входами блока нахождения существенного относительного локатора (8), вход разрешения работы устройства управления (35) является третьим входом блока нахождения существенного относительного локатора (8). Вход управления первого мультиплексора (13) соединен с первым выходом устройства управления (35), выходы первого мультиплексора (13) соединены со входами данных первого шинного формирователя (15) и со входами данных второго шинного формирователя (14). Вход управления первого шинного формирователя (15) соединен со вторым выходом устройства управления (35), вход управления второго шинного формирователя (14) соединен с третьим выходом устройства управления (35), выходы первого шинного формирователя (15) соединены с шиной адреса, выходы второго шинного формирователя (14) соединены с шиной данных. Первые адресные входы оперативного запоминающего устройства (29) соединены с шиной адреса, второй адресный вход оперативного запоминающего устройства (29) соединен с третьим входом первого элемента И (30), с четвертым выходом устройства управления (35) и с третьим выходом устройства инициализации (34), третий адресный вход оперативного запоминающего устройства (29) соединен со вторым входом первого элемента И (30), с пятым выходом устройства управления (35) и с четвертым выходом устройства инициализации (34), вход управления чтением/записью оперативного запоминающего устройства (29) соединен с первым входом первого элемента И (30) и с шестым выходом устройства управления (35), вход выборки оперативного запоминающего устройства (29) соединен с двадцать четвертым выходом устройства управления (35), выходы данных оперативного запоминающего устройства (29) соединены с шиной данных. Входы первого селектора нулевого кода (28) соединены с шиной адреса, выход первого селектора нулевого кода (28) соединен с четвертым входом первого элемента И (30). Входы данных первого буферного регистра (16) соединены с шиной данных, первый управляющий вход первого буферного регистра (16) соединен с восьмым выходом устройства управления (35), второй управляющий вход первого буферного регистра (16) соединен с девятым выходом устройства управления (35), выходы первого буферного регистра (16) соединены со входами данных третьего шинного формирователя (17) и со входами данных четвертого шинного формирователя (18). Управляющий вход третьего шинного формирователя (17) соединен с десятым выходом устройства управления (35), выходы третьего шинного формирователя (17) соединены с шиной адреса. Управляющий вход четвертого шинного формирователя (18) соединен с одиннадцатым выходом устройства управления (35), выходы четвертого шинного формирователя (18) соединены с шиной данных. Входы данных второго буферного регистра (19) соединены с шиной данных, первый управляющий вход второго буферного регистра (19) соединен с двенадцатым выходом устройства управления (35), второй управляющий вход второго буферного регистра (19) соединен с тринадцатым выходом устройства управления (35), третий управляющий вход второго буферного регистра (19) соединен с четырнадцатым выходом устройства управления (35), выходы второго буферного регистра (19) соединены со входами данных пятого шинного формирователя (20) и со входами данных шестого шинного формирователя (21). Управляющий вход пятого шинного формирователя (20) соединен с пятнадцатым выходом устройства управления (35), выходы пятого шинного формирователя (20) соединены с шиной адреса. Управляющий вход шестого шинного формирователя (21) соединен с шестнадцатым выходом устройства управления (35), выходы шестого шинного формирователя (21) соединены с шиной данных. Входы данных третьего буферного регистра (22) соединены с шиной данных, управляющий вход третьего буферного регистра (22) соединен с семнадцатым выходом устройства управления (35), выходы третьего буферного регистра (22) соединены со входами данных седьмого шинного формирователя (23) и со входами данных восьмого шинного формирователя (24). Управляющий вход седьмого шинного формирователя (23) соединен с восемнадцатым выходом устройства управления (35), выходы седьмого шинного формирователя (23) соединены с шиной адреса. Управляющий вход восьмого шинного формирователя (24) соединен с девятнадцатым выходом устройства управления (35), выходы восьмого шинного формирователя (24) соединены с шиной данных. Входы данных четвертого буферного регистра (25) соединены с шиной данных, первый управляющий вход четвертого буферного регистра (25) соединен с двадцатым выходом устройства управления (35), второй управляющий вход четвертого буферного регистра (25) соединен с двадцать первым выходом устройства управления (35), выходы четвертого буферного регистра (25) соединены со входами данных девятого шинного формирователя (26) и со входами данных десятого шинного формирователя (27). Управляющий вход девятого шинного формирователя (26) соединен с двадцать вторым выходом устройства управления (35), выходы девятого шинного формирователя (26) соединены с шиной адреса. Управляющий вход десятого шинного формирователя (27) соединен с двадцать третьим выходом устройства управления (35), выходы десятого шинного формирователя (27) соединены с шиной данных. Входы данных пятого буферного регистра (31) соединены с шиной данных, управляющий вход пятого буферного регистра (31) соединен с выходом первого элемента И (30), выходы пятого буферного регистра (31) соединены со входами данных одиннадцатого шинного формирователя (32) и являются первыми выходами блока нахождения существенного относительного локатора (8). Выходы одиннадцатого шинного формирователя (32) соединены с шиной адреса, управляющий вход одиннадцатого шинного формирователя (32) соединен с управляющим входом шестого буферного регистра (33) и с седьмым выходом устройства управления (35). Входы данных шестого буферного регистра (33) соединены с шиной данных, выходы шестого буферного регистра (33) являются вторыми выходами блока нахождения существенного относительного локатора (8). На первый вход устройства инициализации (34) и на тактовый вход устройства управления (35) подается второй тактовый сигнал, на вторые входы устройства инициализации (34) подается код размера окна, на третий вход устройства инициализации (34) подается сигнал инициализации, первые выходы устройства инициализации (34) соединены с шиной адреса, вторые выходы устройства инициализации (34) соединены с шиной данных.

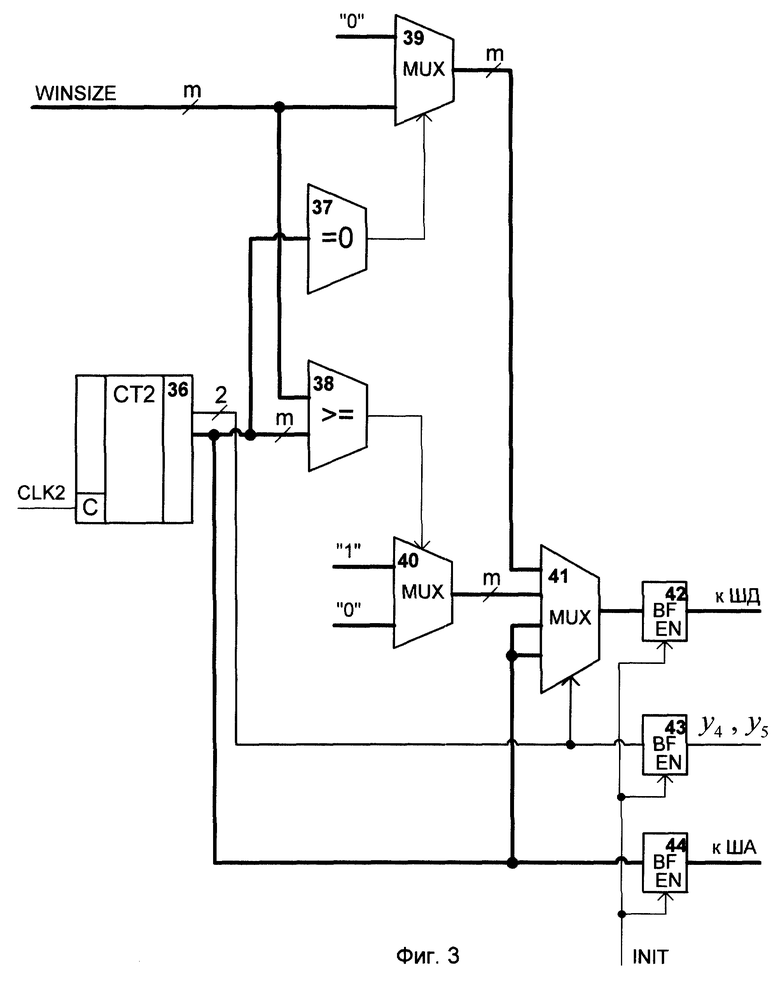

Устройство инициализации (фиг. 3) содержит второй счетчик (36), второй мультиплексор (39), третий мультиплексор (40), четвертый мультиплексор (41), второй селектор нулевого кода (37), вторую схему сравнения кодов (38), двенадцатый шинный формирователь (42), тринадцатый шинный формирователь (43), четырнадцатый шинный формирователь (44).

Тактовый вход второго счетчика (36) является первым входом устройства инициализации (34). Вторые входы второго мультиплексора (39) соединены с первыми входами второй схемы сравнения кодов (38) и являются вторыми входами устройства инициализации (34). На первые входы второго мультиплексора (39) и на вторые входы третьего мультиплексора (40) подается код нуля, на первые входы третьего мультиплексора (40) подается код единицы. Первые выходы второго счетчика (36) соединены со входами второго селектора нулевого кода (37), со вторыми входами второй схемы сравнения кодов (38), с третьими и четвертыми входами четвертого мультиплексора (41) и со входами данных четырнадцатого шинного формирователя (44). Вторые выходы второго счетчика (36) соединены с управляющими входами четвертого мультиплексора (41) и со входами данных тринадцатого шинного формирователя (43). Выход второго селектора нулевого кода (37) соединен с управляющим входом второго мультиплексора (39). Выход второй схемы сравнения кодов (38) соединен с управляющим входом третьего мультиплексора (40). Выходы второго мультиплексора (39) соединены с первыми входами четвертого мультиплексора (41). Выходы третьего мультиплексора (40) соединены со вторыми входами четвертого мультиплексора (41). Выходы четвертого мультиплексора (41) соединены со входами данных двенадцатого шинного формирователя (42). Управляющий вход двенадцатого шинного формирователя (42) соединен с управляющим входом тринадцатого шинного формирователя (43), с управляющим входом четырнадцатого шинного формирователя (44) и является третьим входом устройства инициализации (34). Выходы двенадцатого шинного формирователя (42) являются вторыми выходами устройства инициализации (34), выходы тринадцатого шинного формирователя (43) являются третьим и четвертым выходами устройства инициализации (34), выходы четырнадцатого шинного формирователя (44) являются первыми выходами устройства инициализации (34).

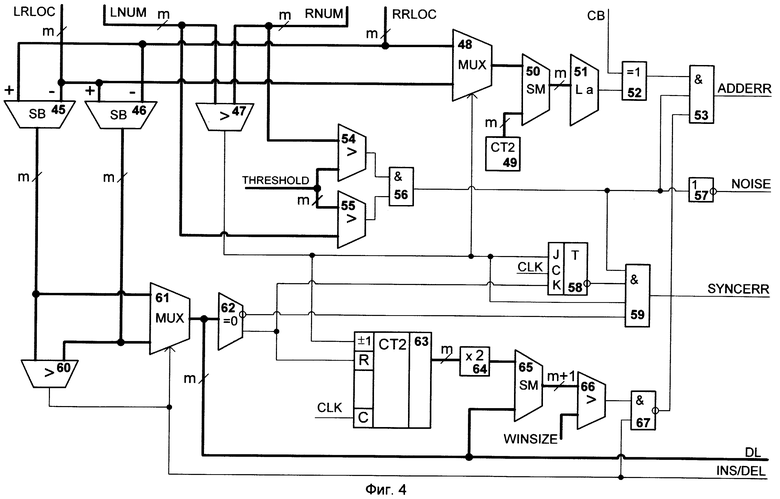

Блок принятия решения о наличии ошибок (фиг.4) содержит второй вычитатель (45), третий вычитатель (46), первый сумматор (50), второй сумматор (65), третью схему сравнения кодов (60), четвертую схему сравнения кодов (47), пятую схему сравнения кодов (54), шестую схему сравнения кодов (55), седьмую схему сравнения кодов (66), пятый мультиплексор (61), шестой мультиплексор (48), третий счетчик (49), четвертый счетчик (63), преобразователь локаторов в синхробиты (51), схему сравнения последовательностей (52), второй элемент И (56), третий элемент И (53), четвертый элемент И (59), первый инвертор (57), JK-триггер (58), третий селектор нулевого кода (62), умножитель на два (64), элемент И-НЕ (67).

Вторые входы второго вычитателя (45) соединены с первыми входами третьего вычитателя (46), со вторыми входами шестого мультиплексора (48) и являются первыми входами блока принятия решения о наличии ошибок (11). Первые входы четвертой схемы сравнения кодов (47) соединены со вторыми входами шестой схемы сравнения кодов (55) и являются вторыми входами блока принятия решения о наличии ошибок (11). Первые входы второго вычитателя (45) соединены со вторыми входами третьего вычитателя (46), с первыми входами шестого мультиплексора (48) и являются третьими входами блока принятия решения о наличии ошибок (11). Вторые входы четвертой схемы сравнения кодов (47) соединены с первыми входами пятой схемы сравнения кодов (54) и являются четвертыми входами блока принятия решения о наличии ошибок (11), выход четвертой схемы сравнения кодов (47) соединен с первым управляющим входом четвертого счетчика (63), с управляющим входом шестого мультиплексора (48), с J-входом JK-триггера (58) и с третьим входом четвертого элемента И (59). Выходы шестого мультиплексора (48) соединены с первыми входами первого сумматора (50). Выходы третьего счетчика (49) соединены со вторыми входами первого сумматора (50), выходы первого сумматора (50) соединены с преобразователем локаторов в синхробиты (51), выход преобразователя локаторов в синхробиты (51) соединен со вторым входом схемы сравнения последовательностей (52), выход схемы сравнения последовательностей (52) соединен с первым входом третьего элемента И (53). На вторые входы пятой схемы сравнения кодов (54) и на первые входы шестой схемы сравнения кодов (55) подается код порога. Выход пятой схемы сравнения кодов (54) соединен с первым входом второго элемента И (56). Выход шестой схемы сравнения кодов (55) соединен со вторым входом второго элемента И (56). Выход второго элемента И (56) соединен со вторым входом третьего элемента И (53), со входом первого инвертора (57) и с первым входом четвертого элемента И (59). Выход третьего элемента И (53) является четвертым выходом блока принятия решения о наличии ошибок (11). Выход первого инвертора (57) является пятым выходом блока принятия решения о наличии ошибок (11). Выходы второго вычитателя (45) соединены с первыми входами пятого мультиплексора (61) и с первыми входами третьей схемы сравнения кодов (60). Выходы третьего вычитателя (46) соединены со вторыми входами пятого мультиплексора (61) и со вторыми входами третьей схемы сравнения кодов (60). Выход третьей схемы сравнения кодов (60) соединен с управляющим входом пятого мультиплексора (61), со вторым входом элемента И-НЕ (67) и является вторым выходом блока принятия решения о наличии ошибок (11). Выходы пятого мультиплексора (61) соединены со входами третьего селектора нулевого кода (62), со вторыми входами второго сумматора (65) и являются третьими выходами блока принятия решения о наличии ошибок (11). Инверсный выход третьего селектора нулевого кода (62) соединен с четвертым входом четвертого элемента И (59), прямой выход третьего селектора нулевого кода (62) соединен с K-входом JK-триггера (58) и со вторым управляющим входом четвертого счетчика (63). На тактовый вход JK-триггера (58) и на тактовый вход четвертого счетчика (63) подается первый тактовый сигнал. Инверсный выход JK-триггера (58) соединен со вторым входом четвертого элемента И (59), выход четвертого элемента И (59) является первым выходом блока принятия решения о наличии ошибок (11). Выходы четвертого счетчика (63) соединены со входами умножителя на два (64), выходы умножителя на два (64) соединены с первыми входами второго сумматора (65), выходы второго сумматора (65) соединены с первыми входами седьмой схемы сравнения кодов (66). На вторые входы седьмой схемы сравнения кодов (66) подается код размера окна, выход седьмой схемы сравнения кодов (66) соединен с первым входом элемента И-НЕ (67), выход элемента И-НЕ (67) соединен с третьим входом третьего элемента И (53).

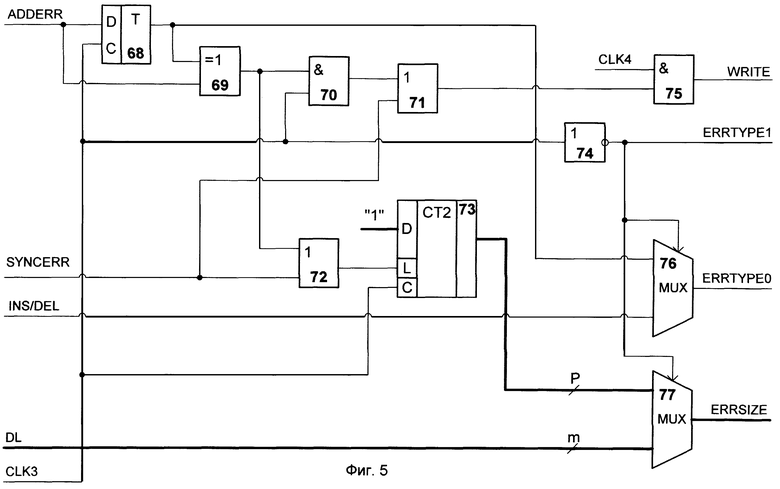

Блок формирования потока состояний канала (фиг.5) содержит D-триггер (68), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (69), пятый элемент И (70), шестой элемент И (75), первый элемент ИЛИ (71), второй элемент ИЛИ (72), второй инвертор (74), пятый счетчик (73), седьмой мультиплексор (76), восьмой мультиплексор (77).

D-вход D-триггера (68) соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (69) и является четвертым входом блока формирования потока состояний канала (12), тактовый вход D-триггера (68) соединен со вторым входом пятого элемента И (70), со входом второго инвертора (74), с тактовым входом пятого счетчика (73) и на него подается третий тактовый сигнал, выход D-триггера (68) соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (69) и с первым входом седьмого мультиплексора (76). Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (69) соединен с первым входом пятого элемента И (70) и с первым входом второго элемента ИЛИ (72). Выход пятого элемента И (70) соединен с первым входом первого элемента ИЛИ (71). Второй вход первого элемента ИЛИ (71) соединен со вторым входом второго элемента ИЛИ (72) и является первым входом блока формирования потока состояний канала (12). Выход первого элемента ИЛИ (71) соединен со вторым входом шестого элемента И (75). На первый вход шестого элемента И (75) подается четвертый тактовый сигнал, выход шестого элемента И (75) является первым выходом блока формирования потока состояний канала (12). Выход второго элемента ИЛИ (72) соединен со входом загрузки пятого счетчика (73). На входы данных пятого счетчика (73) подается код единицы, выходы пятого счетчика (73) соединены с первыми входами восьмого мультиплексора (77). Второй вход седьмого мультиплексора (76) является вторым входом блока формирования потока состояний канала (12). Вторые входы восьмого мультиплексора (77) являются третьими входами блока формирования потока состояний канала (12). Выход второго инвертора (74) соединен с управляющим входом седьмого мультиплексора (76) и с управляющим входом восьмого мультиплексора (77). Выход седьмого мультиплексора (76) и выход второго инвертора (74) являются вторыми выходами блока формирования потока состояний канала (12). Выходы восьмого мультиплексора (77) являются третьими выходами блока формирования потока состояний канала (12).

Работа устройства измерения параметров ошибок в канале основывается на использовании в качестве тестовых последовательностей, передаваемых через канал, последовательностей, характеризующихся тем, что любые расположенные подряд m бит последовательности однозначно определяют ее фазу (расположение всех бит последовательности). К таким последовательностям относятся М-последовательности, двоичные последовательности Де Брейна, а также модифицированные двоичные последовательности Де Брейна.

М-последовательность представляет собой двоичную линейную рекуррентную последовательность, каждый член которой с номером j+m является линейной комбинацией предшествующих m членов:

aj+m=c1aj+m-1+c2aj+m-2+...+cmaj,

где коэффициенты сk, принимают значения из двоичного поля. Для построения такой последовательности достаточно знать m следующих подряд символов (бит).

М-последовательность имеет период n= -2m-l (m - степень порождающего многочлена последовательности). Выборка из последовательности n взятых подряд m-битных символов является перестановкой чисел от 1 до 2m-1 Aj=(aj, aj+1, . . . aj+m-1), j=0,1,..., n-1. В изобретении Аj будет называться синхросимволом, а индекс j - локатором синхросимвола (локатор фактически является порядковым номером синхросимвола на одном периоде тестовой последовательности). При этом элемент аj будет называться синхробитом, а индекс j при нем - локатором синхробита.

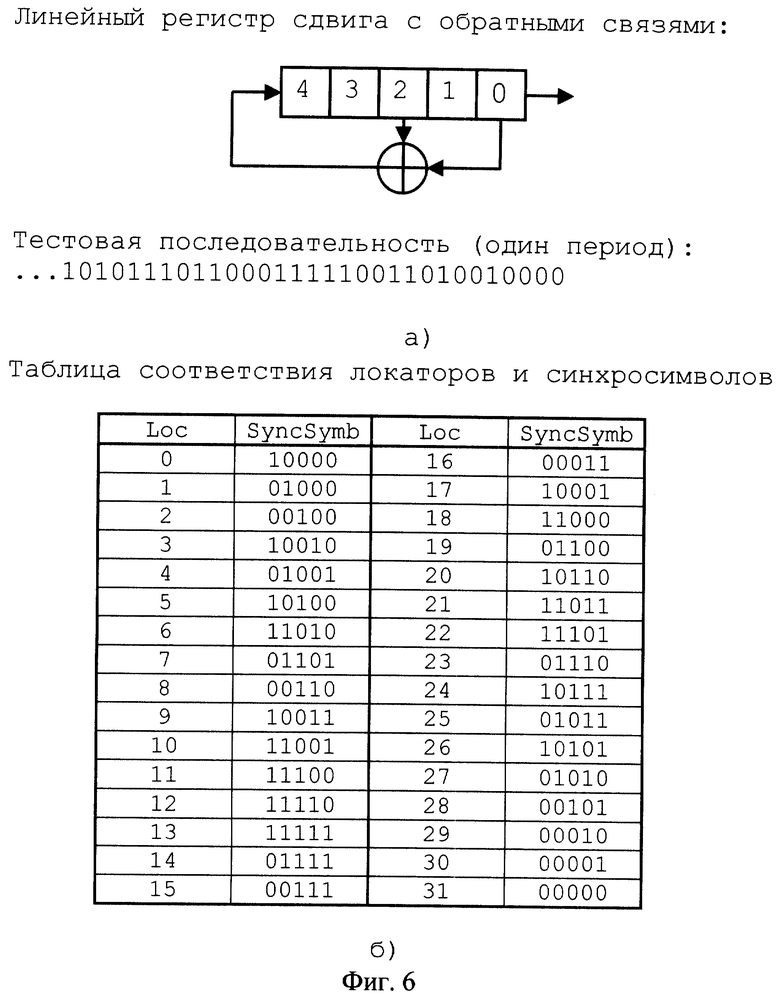

На фиг. 6а показан линейный регистр сдвига с обратными связями, который соответствует порождающему многочлену f(x)=x5+x2+1 (в данном случае m=5), и генерируемая данным регистром М-последовательность. Последующие биты М-последовательности расположены на рисунке слева по отношению к предыдущим битам. На фиг.6б приведена таблица соответствия локаторов и синхросимволов для этой последовательности. Ниже эта последовательность будет использоваться для иллюстрации работы устройства.

Определение величин вставок и выпадений с использованием рассмотренных тестовых последовательностей может быть выполнено следующим образом.

Принятая из канала тестовая последовательность преобразуется в поток синхросимволов, в котором выделяются две последовательности одинаковой длины k, имеющие один общий синхробит аi:

(Ai+k-1, Аi+k-2,..., Аi+1, Аi)

и

(Ai-m+1, Ai-m,..., Ai-k+2-m+1, Ai-k+1-m+1).

В изобретении эти последовательности будут называться соответственно левым и правым окнами.

В каждом окне можно найти локаторы синхросимволов и пересчитать их по модулю n относительно синхробита ai. Таким образом получаются два вектора оценок локатора текущего бита аi:

{L(Ai+k-1)-k+1, L(Ai+k-2)-k+2,..., L(Ai+1)-l, L(Ai)}

и

{L(Ai-m+1)+m-1, L(Аi-m)+ m,..., L(Ai-k+2-m+1)+k-2+m-1;

L(Ai-k+1-m+1)+k-1+m-1}.

Здесь L(Ai) обозначает оператор нахождения локатора синхросимвола Аi.

Анализируя эти вектора можно сформировать оценки локаторов слева Ll и справа Lr. В качестве оценки целесообразно выбрать локатор, который чаще всего встречается в векторе окна. В изобретении он будет называться существенным локатором. Количество вхождений локатора в вектор окна будет называться его весом.

Существенный локатор однозначно определяет фазу последовательности в окне. По разности существенных локаторов левого и правого окон ΔL можно судить о величине вставки ΔLinsertion или выпадения ΔLdeletion.

ΔLinsertion=(Lr-Ll) mod n; (1)

ΔLdeletion=(Ll-Lr) mod n.

Если ΔL=0, то вставки или выпадения бит отсутствуют. Величина вставок и выпадений определяется с точностью до периода n

М-последовательности. Меньшая из величин ΔLinsertion и ΔLdeletion определяет, что произошло: вставка или выпадение.

Расположение вставок или выпадений в тестовой последовательности определяется моментом времени превышения веса существенного локатора левого окна над весом существенного локатора правого окна.

Для определения вставок и выпадений имеет значение разность оценок локаторов текущего бита справа и слева, оценки значений самих локаторов в явном виде находить необязательно. Поэтому процедура нахождения вставок и выпадений может быть видоизменена с целью упрощения реализации следующим образом.

Сначала поток синхросимволов Аi преобразуется в поток локаторов L(Ai). Затем локаторы преобразуются в относительные локаторы rLi путем вычитания из них i по модулю n, где i переменная, идентифицирующая текущий обрабатываемый бит тестовой последовательности, которая инкрементируется на каждом такте работы устройства. Последовательность относительных локаторов в случае отсутствия ошибок будет представлять собой константную последовательность. Для любого i-го бита тестовой последовательности соответствующий локатор может быть восстановлен путем прибавления к относительному локатору значения i по модулю n.

Для оценки относительного локатора текущего бита слева и справа в последовательности относительных локаторов выделяются два окна:

{rLi+k-1, rLi+k-2,..., rLi+1, rLi}

и

{rLi-m+l, rLi-m,..., rLi-k+2-m+1, rLi-k+1-m+1}.

Существенные относительные локаторы этих окон дадут оценки относительных локаторов текущего бита слева rLi и справа rLr. Формула (1) при этом примет вид

ΔLinsertion=(rLr-rLl) mod n; (2)

ΔLdeletion=(rLl-rLr) mod n.

Устройство измерения параметров ошибок в канале работает следующим образом.

m-разрядный регистр сдвига 1 (фиг.1) преобразует входную битовую тестовую последовательность в последовательность синхросимволов, которая в свою очередь преобразователем синхросимволов в локаторы 2 преобразуется в последовательность локаторов. Преобразователь синхросимволов в локаторы 2 может быть реализован на ПЗУ (емкостью 2m m-разрядных слов).

Вычитатель 3 вычитает из каждого локатора, поступающего на вход текущее значение счетчика 4, содержащего переменную i. Таким образом получается последовательность относительных локаторов, которая с выхода вычитателя 3 поступает на вход буфера относительных локаторов 6. В случае использования в качестве тестовой последовательности М-последовательности, в эталонной тестовой последовательности отсутствует нулевой синхросимвол (фиг.6), которому соответствует локатор 2m-l (все единицы). Но он может встретиться в принятой из канала тестовой последовательности из-за ошибок. Поэтому вычитатель 3 должен отслеживать появление на входе локатора 2m-l и выдавать на выход значение 2m-1 (не производя при этом собственно вычитание). Это необходимо для исключения влияния несуществующих в эталонной последовательности заведомо ошибочных локаторов на принятие решения о наличии ошибок синхронизации. В случае использования в качестве тестовых последовательностей Де Брейна это не требуется и вычитатель 3 является обычной схемой вычитания (поскольку при этом период последовательности и соответственно модуль равны n=2m).

Регистр сдвига 5 предназначен для задержки бит тестовой последовательности, которая затем используется для обнаружения аддитивных ошибок. Эта задержка необходима для согласования моментов принятия решения о наличии аддитивных ошибок и ошибок синхронизации. Число ступеней регистра сдвига 5 равно WINST7E-1 (на единицу меньше размера окна).

Блок нахождения существенного относительного локатора 8, в основу работы которого положен мажоритарный принцип, в каждом такте формирует локатор (RLOC), который в данный момент чаще всех остальных локаторов встречается в буфере относительных локаторов 6. Этому существенному локатору соответствует вес (NUM), т.е. количество появлений локатора в буфере относительных локаторов 6, который также присутствует на выходе блока 8. Число ступеней буфера относительных локаторов равно WINSIZE (размер окна) и не должно превышать порога 2m-1 (это связано с емкостью оперативного запоминающего устройства 29 в блоке нахождения существенных относительных локаторов 8). Если поступающий на вход буфера относительных локаторов 6 и выходящий из него относительные локаторы совпадают, то обработка не требуется и существенный относительный локатор не меняется. Поэтому блок нахождения существенного относительного локатора активизируется только в том случае, если входящий и выходящий относительные локаторы различны. Сигнал разрешения работы (ENABLE) блока нахождения существенного относительного локатора 8 формируется схемой сравнения кодов 7. В случае отсутствия любых ошибок блок нахождения существенного относительного локатора 8 бездействует.

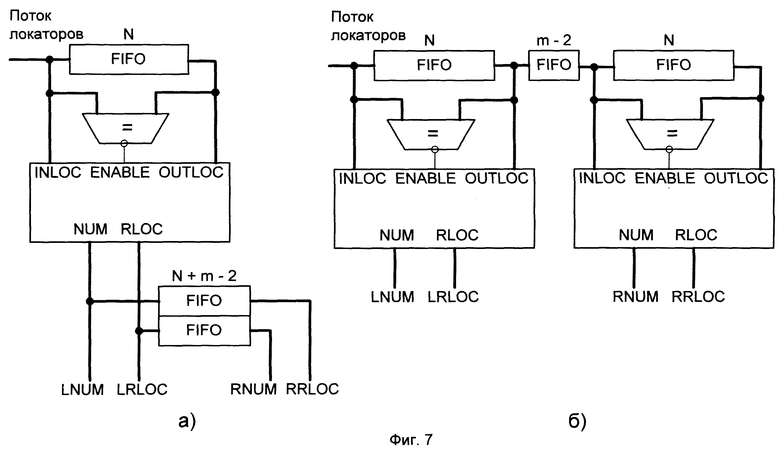

Поток существенных относительных локаторов и их весов задерживается буфером существенных относительных локаторов 9 и буфером весов существенных относительных локаторов 10 соответственно, которые содержат по WTNSIZE+m-2 ступеней каждый. Локаторы и веса на входах буферов соответствуют левому окну, а задержанные локаторы и задержанные веса на выходе буферов соответствуют правому окну. Применение одного блока нахождения существенного относительного локатора для двух окон значительно упрощает устройство. Это возможно из-за полной функциональной эквивалентности совокупности 6, 7, 8, 9 и 10 блоков устройства (как это проиллюстрировано на фиг.7а) совокупности блоков, показанной на фиг.7б.

Блок принятия решения о наличии ошибок 11 на основе анализа разности существенных относительных локаторов левого и правого окон (LRLOC и RRLOC), а также значения их весов (LNUM и RNUM) принимает решение о наличии в данный момент времени ошибки синхронизации (вставка/выпадение бит). В случае обнаружения ошибки синхронизации на выход блока принятия решения о наличии ошибок 11 выдается сигнал SYNCERR, а также сопутствующие ему сигналы: INS/DEL (тип обнаруженной ошибки синхронизации: вставка или выпадение) и DL (размер ошибки синхронизации - количество бит). Блок принятия решения о наличии ошибок также по существенным относительным локаторам восстанавливает правильное значение центрального бита анализируемого участка тестовой последовательности и производит сравнение с его действительным (задержанным) значением, которое поступает со второго регистра сдвига 5. В случае неравенства этих бит фиксируется аддитивная ошибка. Если эта ошибка не была вызвана вставкой бит, то на выход блока принятия решения о наличии ошибок 11 выдается сигнал о наличии аддитивной ошибки ADDERR. В случае, если уровень аддитивных ошибок превысил заданный порог и веса существенных относительных локаторов уменьшились настолько, что невозможно корректное принятие решения о наличии ошибок в данный момент, то выдается сигнал NOISE (невозможность корректного измерения параметров ошибок) для устройства регистрации информации об ошибках. Присутствие данного сигнала говорит о том, что вся выдаваемая устройством измерения параметров ошибок информация в данный момент неверна, и это должно быть учтено при последующей обработке потока состояний канала.

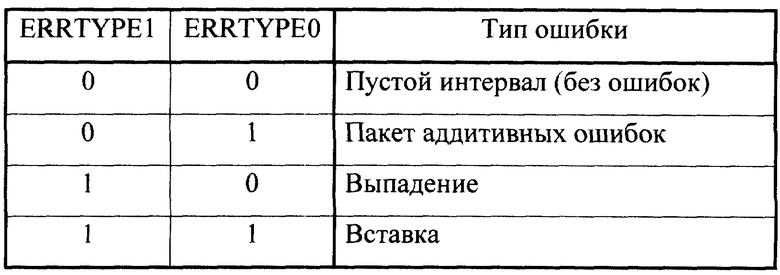

Блок формирования потока состояний канала 12 на основе информации, поступающей с блока принятия решения о наличии ошибок 11, формирует для устройства регистрации информации об ошибках стробы записи WRITE и сопутствующую им информацию о состоянии канала за некоторый промежуток времени: тип ошибки ERRTYPE и размер ошибки ERRSIZE. Безошибочные состояния и аддитивные ошибки собираются блоком формирования потока состояний канала в пакеты. Блоком выделяются 4 типа состояний канала, как показано в таблице.

Рассмотрим подробнее работу основных блоков устройства измерения параметров ошибок в канале.

Блок нахождения существенного относительного локатора (фиг.2) представляет собой автомат, содержащий оперативное запоминающее устройство, в котором выделены четыре одинаковых участка памяти, шесть буферных регистров, устройство управления, устройство инициализации и ряд вспомогательных элементов. Данный автомат позволяет реализовывать следующие простые операции: пересылку данных между оперативным запоминающим устройством и одним из четырех регистров, пересылку данных между двумя регистрами (для этого используются шинные формирователи), операции инкремента (прибавление единицы) и декремента (вычитание единицы) регистров. Операция пересылки реализуется следующим образом. Пересылка данных из одного регистра в другой производится непосредственно через шину данных. Пересылка данных между ячейкой оперативного запоминающего устройства и одним из четырех регистров также производится через шину данных, но требует выбора одного из четырех участков памяти путем выставления на старшие разряды шины адреса значения от нуля до трех, а на младшие разряды шины адреса - номера ячейки. Сигналы y1...y23 определяют источник и приемник при передаче данных, а также задают тип арифметической операции для буферных регистров.

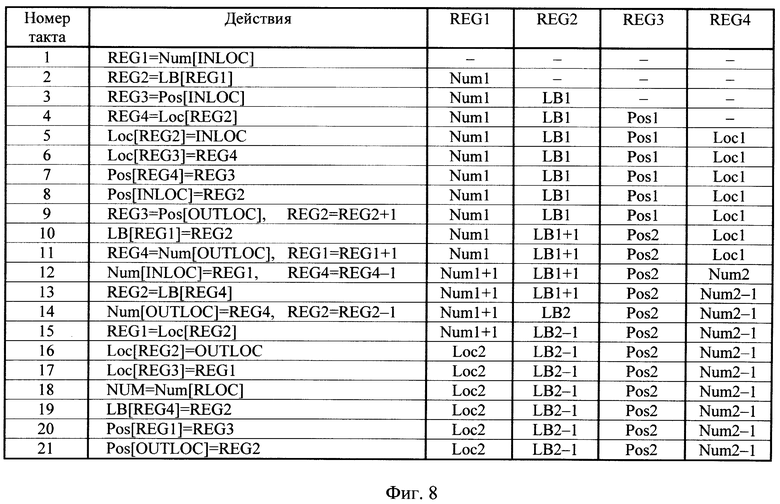

Блок нахождения существенного относительного локатора реализует алгоритм, приведенный на фиг.8. В алгоритме можно условно выделить две независимые части: обработка входящего локатора и затем обработка выходящего локатора. В правой части таблицы приведено содержимое каждого из четырех буферных регистров (16, 19, 22 и 25) до выполнения операции, указанной в левой половине таблицы.

Выделенные в оперативном запоминающем устройстве четыре участка памяти предназначены для хранения следующих массивов. В массиве Num хранятся количества соответствующих относительных локаторов, присутствующих в данный момент в буфере относительных локаторов (индексом в массиве является локатор). Массив Loc предназначен для хранения локаторов в порядке убывания их количества, т. е. по нулевому адресу хранится локатор, чаще всего встречающийся в данный момент в буфере относительных локаторов (существенный локатор), а по самому старшему адресу хранится локатор, реже всего встречающийся в данный момент в буфере относительных локаторов (индексом в массиве является порядковый номер локатора). Массив Pos предназначен для хранения позиций локаторов в отсортированном массиве (индексом в массиве является локатор). Массив Pos является взаимно обратным к массиву Loc, т.е. для массивов Loc и Pos выполняются соотношения Loc[Pos[i]]=i и Pos[Loc[i]]=i, где i - произвольный индекс. Массив LB предназначен для хранения левых границ групп одинаковых количеств локаторов, как если бы локаторы были отсортированы.

На фиг.9а приведен пример содержимого буфера относительных локаторов 6 и соответствующее ему корректное содержимое четырех массивов (Num, Loc, Pos и LB) блока нахождения существенных относительных локаторов 8 для случая m=3.

С помощью селектора нулевого кода 28 и элемента И 30 отслеживается запись в массив локаторов Loc по нулевому адресу. В этом случае значение (существенный относительный локатор), присутствующее на шине данных, записывается в буферный регистр 31. Таким образом элементы 28, 30 уменьшают время работы блока нахождения существенного относительного локатора 8 за счет исключения дополнительной операции чтения из массива Loc по нулевому адресу для определения существенного относительного локатора.

Для реализации алгоритма (фиг.8) устройство управления 35 обеспечивает в течение 21 такта CLK2 выдачу управляющих сигналов y1...y23, приведенных на фиг.10. Сигнал у24, отвечающий за выбор кристалла оперативного запоминающего устройства 29, устанавливается в логическую единицу в каждом такте CLK2 спустя некоторое время после установления данных на шинах адреса и данных и сбрасывается через некоторый промежуток времени, обеспечивающий гарантированную запись. Данные на выходе блока нахождения существенного относительного локатора 8 (значение существенного относительного локатора и его вес) готовы уже к концу 18 такта CLK2.

Устройство инициализации (фиг.3) предназначено для первоначального заполнения ячеек оперативного запоминающего устройства. В самом начале работы устройства измерения параметров ошибок в канале предполагается, что буфер относительных локаторов 6 инициализируется нулевыми значениями. Поэтому устройство инициализации 34 заполняет четыре массива значениями, приведенными в таблице на фиг.9б. Ячейки оперативного запоминающего устройства 29 будут заполнены указанными значениями спустя 2m+2 тактов после подачи сигнала INTT. После этого сигнал INIT должен быть снят. Устройство инициализации тактируется сигналом CLK2.

Блок принятия решения о наличии ошибок (фиг.4) функционирует следующим образом. Вычитателем 45 из локатора правого окна вычитается локатор левого окна, а вычитателем 46 из локатора левого окна вычитается локатор правого окна. Оба вычитателя осуществляют вычитание по модулю n. Из полученных двух значений схемой сравнения 60 и мультиплексором 61 выбирается меньшее значение ΔL, тем самым определяется размер ошибки синхронизации, которая присутствует в данный момент в пределах двух окон. Если ΔL=0, то ошибки синхронизации на анализируемом отрезке последовательности отсутствуют (этот факт определяется селектором нулевого кода 62). На выходе схемы сравнения кодов 60 присутствует код логической единицы в случае обнаружения вставки бит и код логического нуля в случае обнаружения выпадения бит (либо в случае, если ΔL=0).

Если обнаружена ошибка синхронизации (на инверсном выходе селектора нулевого кода 62 присутствует логическая единица) и вес существенного относительного локатора левого окна стал превышать вес существенного относительного локатора правого окна (на выходе схемы сравнения кодов присутствует логическая единица), а в предыдущем такте (состояние JK-триггера 58) было наоборот (вес существенного относительного локатора правого окна превышал вес существенного относительного локатора левого окна), то это означает, что центр ошибки синхронизации в данный момент находится между двумя окнами и требуется ее регистрация. В этот момент на выходе элемента И 59 присутствует сигнал обнаружения ошибки синхронизации (логическая единица). Таким образом, информация о параметрах ошибки синхронизации (INS/DEL, DL) присутствует все время на выходе блока принятия решения о наличии ошибок, пока ошибка синхронизации находится в пределах двух окон, но сигнал о ее обнаружении выдается только тогда, когда центр ошибки синхронизации находится в центре между двух окон (там где они виртуально перекрываются на один бит). В случае отсутствия ошибок синхронизации происходит сброс JK-триггера 58. Применение JK-триггера в схеме обусловлено необходимостью исключения возможного "дребезга" сигнала на выходе элемента 47 при обнаружении ошибки синхронизации (наличие логического нуля на прямом выходе селектора нулевого кода 62), что приведет к регистрации более чем одной ошибки синхронизации.

Цепочка элементов 48, 49, 50, 51 (счетчик 49 и сумматор 50 функционируют по модулю n) предназначена для восстановления правильного значения центрального бита. С помощью мультиплексора 48 выбирается существенный относительный локатор, имеющий больший вес. Счетчик 49 (тактируется сигналом CLK), функционирующий по модулю n, смещен в меньшую сторону (по модулю n) относительно счетчика 4 на величину числа ступеней регистра сдвига 5, т.е. на WINSIZE-1. Это необходимо для обратного преобразования относительного локатора с выхода мультиплексора 49 в истинный локатор, который в свою очередь преобразователем локаторов в синхробиты 51 преобразуется в правильный бит, расположенный в центре между двух окон. Фактически производится операция, обратная к операции производимой элементами 2, 3, 4 на начальном этапе, за исключением того, что не требуется полного восстановления синхросимвола, а достаточно восстановить один его бит. Далее, схемой сравнения последовательностей 52 (которая фактически представляет собой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ) производится сравнение восстановленного правильного бита и действительного центрального бита, задержанного регистром сдвига 5. Логическая единица, присутствующая на выходе элемента И 53, означает факт обнаружения аддитивной ошибки. Преобразователь локаторов в синхробиты 51 может быть реализован на ПЗУ (емкостью 2m 1-разрядных слов, т.е. бит).

В случае, если вес хотя бы одного существенного локатора (для определения этого факта служит цепочка элементов из двух схем сравнения кодов 54, 55 и элемента И 56) сильно уменьшился (что определяется порогом THRESHOLD), то это означает, что в канале наблюдается большой уровень аддитивных ошибок. Последнее обстоятельство в этом случае делает невозможным корректное измерение параметров ошибок, поэтому в этот момент на выходе элемента И 56 присутствует логический ноль, что блокирует выдачу информации об ошибках (сигналы ADDERR и SYNCERR) и на выход блока принятия решения о наличии ошибок выдается сигнал шум (NOISE), который должен быть использован устройством регистрации информации об ошибках при дальнейшей обработке потока состояний канала.

Цепочка элементов, состоящая из счетчика 63, умножителя на два 64, сумматора 65, схемы сравнения кодов 66 и элемента И 67, предназначена для блокировки регистрации аддитивных ошибок на некоторое время при обнаружении ошибки синхронизации типа вставки бит, поскольку в этом случае аддитивные ошибки обусловлены последней. Счетчик 63 сбрасывается в случае отсутствия ошибок синхронизации, а при обнаружении начинает считать в сторону увеличения до тех пор, пока центр ошибки синхронизации находится в пределах левого окна (что определяется соотношением весов существенных относительных локаторов), а затем в сторону уменьшения, когда центр ошибки синхронизации переместится в правое окно. Заметим, что ошибка синхронизации начинает регистрироваться с момента, когда ее центр находится в центре левого окна, и до того момента, когда ее центр будет находиться в центре правого окна. Фактически указанной цепочкой элементов проверяется условие:

CNT+ΔL/2 > WINSIZE/2

или

2•CNT+ΔL > WINSIZE,

где CNT - текущее состояние счетчика, ΔL - размер ошибки синхронизации.

В случае выполнения указанного условия и если тип ошибки синхронизации вставка, то осуществляется блокировка регистрации аддитивных ошибок (пока биты вставки полностью не переместятся в правое окно).

Счетчик 63 является счетчиком с блокировкой нуля, т.е. текущее значение счетчика не меняется при достижении счетчиком значения нуля при обратном счете (от больших значений к меньшим). Умножитель на два фактически не является функциональным элементом, поскольку реализуется простой перестановкой проводников в шине.

Блок формирования потока состояний канала (фиг.5) на основе информации, получаемой от блока принятия решения о наличии ошибок 11 (сигналы SYNCERR, ADDERR, INS/DEL и DL), осуществляет сборку последовательных безошибочных состояний канала и последовательностей ошибок в пакеты, а также распределяет во времени регистрацию ошибок синхронизации и аддитивных ошибок при одновременном появлении сигналов ADDERR и SYNCERR (для этого используются тактовый сигнал CLK3). D-триггер 68 предназначен для определения окончания потока одинаковых состояний канала (безошибочные состояния, либо аддитивные ошибки). Для этого элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 69 осуществляется сравнение предыдущего состояния канала (состояние D-триггера) и текущего (текущее значение сигнала ADDERR). При обнаружении указанного события происходит загрузка кода единицы в счетчик 73 путем подачи логической единицы на вход загрузки счетчика L (load). Счетчик 73 предназначен для подсчета интервалов безошибочных состояний канала, а также длин пакетов аддитивных ошибок. Поэтому размерность счетчика и шины на выходе счетчика 73 (Р) определяется наибольшей длиной интервала одинаковых состояний (2p). Функционирование блока формирования потока состояний канала 12 поясняет таблица, приведенная на фиг. 11, где приведены осуществляемые блоком действия и выдаваемые на выход сигналы в зависимости от сигналов на входе и текущего состояния D-триггера 68. В первых трех колонках таблицы приведены все возможные комбинации входных сигналов на входе АЕ, SE (ADDERR и SYNCERR соответственно) и состояния D-триггера (C/L). Если C/L=0, то это означает, что в данный момент осуществляется подсчет счетчиком 73 безошибочных состояний канала, иначе равенство C/L=1 означает, что осуществляется подсчет аддитивных ошибок. C/L' - состояние D-триггера, в которое осуществляется переход в следующем такте. В последней колонке таблицы приведена часть потока состояний сигналов SYNCERR (SE) и ADDERR (АЕ) в предшествующие моменты времени, соответствующие каждой из рассматриваемых ситуаций (жирным шрифтом выделено текущее состояние сигналов SYNCERR и ADDERR).

Примечания к таблице.

Управляющие сигналы:

С - тактовый вход счетчика 73,

L - вход загрузки счетчика 73,

W - сигнал записи WRITE,

ERRTYPEO, ERRTYPE1 -линии шины ERRTYPE.

Действия:

CNT=CNT+1 - инкремент счетчика 73,

Per. S - регистрация ошибки синхронизации,

Per. L - регистрация пакета аддитивных ошибок,

Per. С - регистрация безошибочного интервала.

На фиг. 12 приведены временные диаграммы тактовых сигналов устройства измерения параметров ошибок в канале. Один такт CLK соответствует времени поступления одного бита тестовой последовательности в устройство. Тактовый сигнал CLK2 необходим для работы блока нахождения существенного относительного локатора 8. Устройство управления 35 пропускает один такт тактового сигнала CLK2, это обусловлено тем, что для работы преобразователя синхросимволов в локаторы 2 требуется некоторое время и, следовательно, данные на его выходе появятся не в начале такта (т.к. предполагается, что преобразователь синхросимволов в локаторы будет реализовываться на ПЗУ). Блок формирования потока состояний канала 12 начинает работать параллельно с блоком нахождения существенного относительного локатора 8 с двадцатого такта. Это возможно, поскольку данные на выходе последнего готовы уже к концу восемнадцатого такта. Таким образом экономятся два такта работы (CLK2) всего устройства в целом. Тактовый сигнал CLK3 необходим для разнесения во времени регистрации аддитивных ошибок и ошибок синхронизации. Тактовый сигнал CLK4 предназначен для формирования строба записи (сигнал WRITE) для устройства регистрации информации об ошибках, которое должно регистрировать информацию об ошибках по переднему фронту сигнала WRITE.

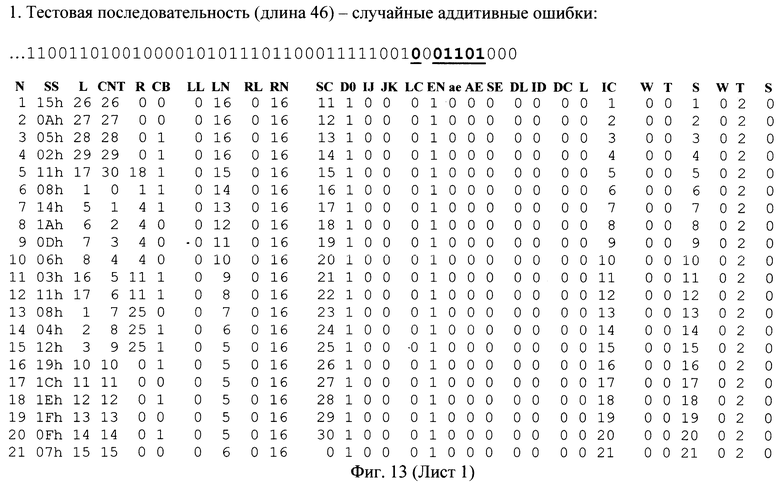

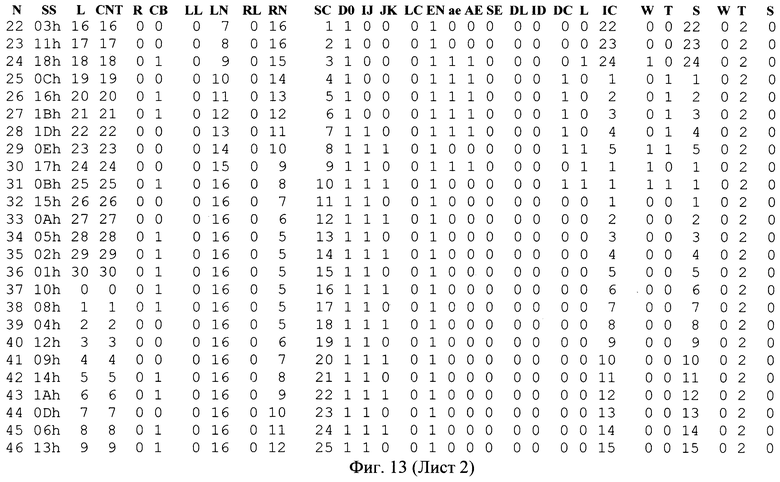

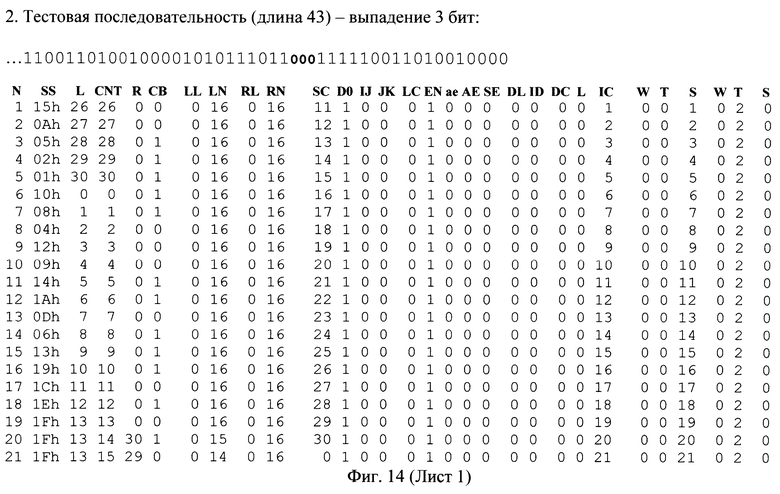

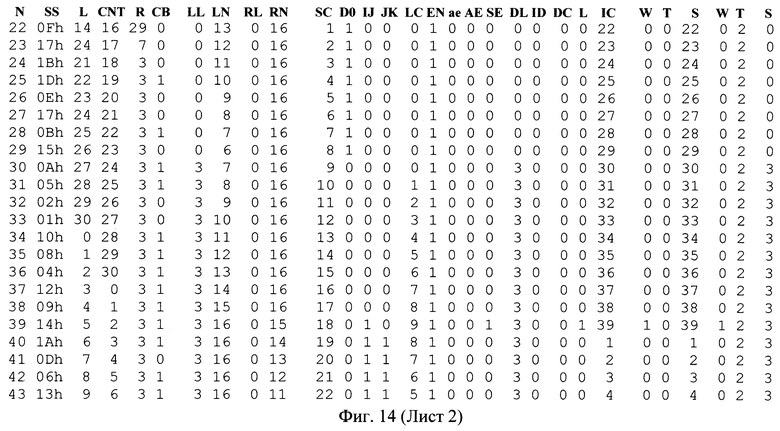

На фиг. 13-16 приведены примеры работы устройства измерения параметров ошибок в случаях четырех различных конфигураций ошибок. В качестве тестовой используется М-последовательность, полученная с помощью линейного регистра сдвига с обратными связями, приведенного на фиг.6а (m=5). Последующие биты М-последовательности расположены на фигурах слева по отношению к предыдущим битам.

Условные сокращения, используемые в таблицах (по порядку).

N - номер такта,

SS - текущий синхросимвол (выход регистра сдвига 1),

L - текущий локатор (выход преобразователя синхросимволов в локаторы 2),

CNT - текущее значение счетчика 4,

R - текущее значение относительного локатора (выход вычитателя 4),

СВ - значение центрального бита (выход регистра сдвига 5),

LL - существенный относительный локатор для левого окна (выход блока нахождения существенного относительного локатора RLOC),

LN - вес существенного относительного локатора для левого окна (выход блока нахождения существенного относительного локатора NUM),

RL - существенный относительный локатор для правого окна (выход буфера существенных относительных локаторов 9),

RN - вес существенного относительного локатора для правого окна (выход блока нахождения существенного относительного локатора 10),

SC - текущее значение смещенного счетчика 49 (shifted counter),

DO - текущее значение на прямом выходе селектора нулевого кода 62 (DL= 0),

IJ - текущее значение на J-входе JK-триггера 58,

JK - текущее значение на прямом выходе JK-триггера 58,

LC - текущее значение счетчика 63,

EN - текущее значение на выходе элемента И-НЕ 67 (сигнал разрешения регистрации аддитивных ошибок),

ае - наличие аддитивной ошибки (выход схемы сравнения последовательностей 52),