13

чинается по внешнему запускающему IM пульсу, поступающему на вход блока 15 управления, на выходах которого в зависимости от значения кода режима вырабатывается последовательность управляющих сигналов, соответствующих многоканальному или одноканальному преобразованию, В многоканальном режиме на вход суммирования счетчика 8 поступают импульсы переноса со счетчика 7, по которым предьщущее содержимое счетчика 8 запоминается в регистре 9 на время такта. Выходной код счетчика 8 управляет цифроаналоговым преобразователем 10, напряжение с которого поступает через делитель 2 на первые входы блока 1 компараторов для сравнения с входными сигналами. Причем в этом режиме генераторы 13, 4 стабильного тока отключены от входа

1

Изобретение относится к области автоматики и измерительной техники и может быть использовано в -системах управления для параллельного квантования со средней частотой больщого числа аналоговых сигналов и для кван- тования с высокой часто той одиночных аналоговых сигналов.

Целью изобретения является расти- рение области применения за счет увеличения динамического диапазона преобразования.

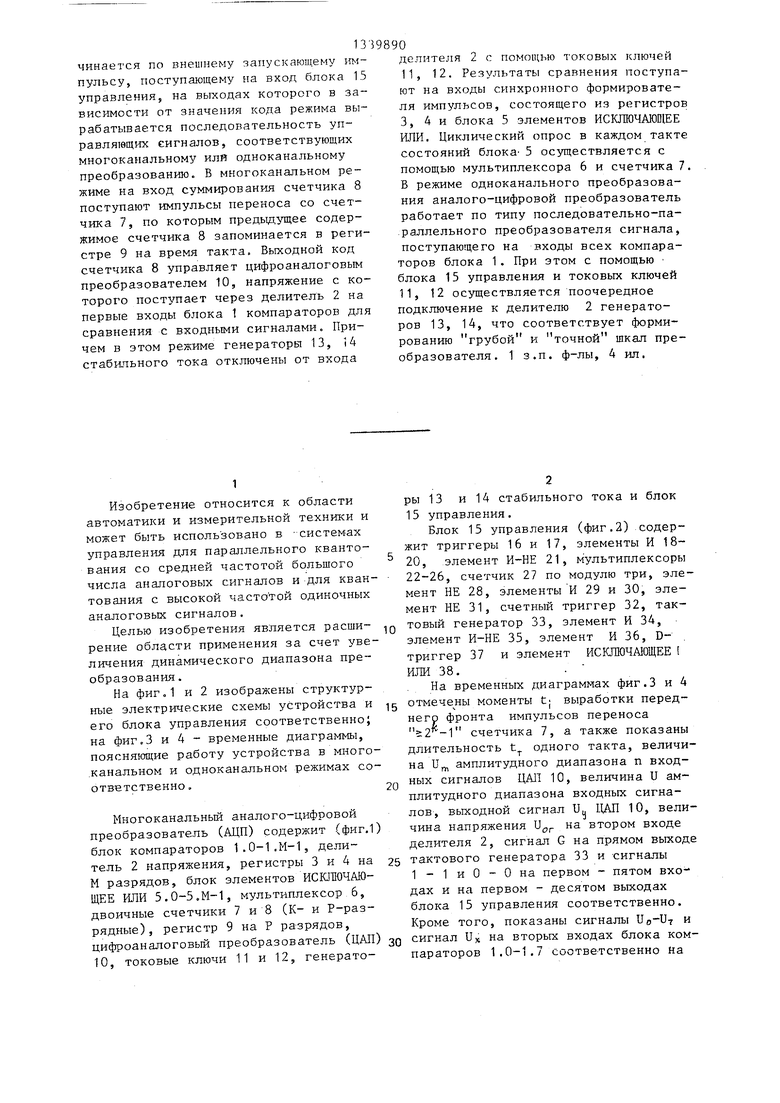

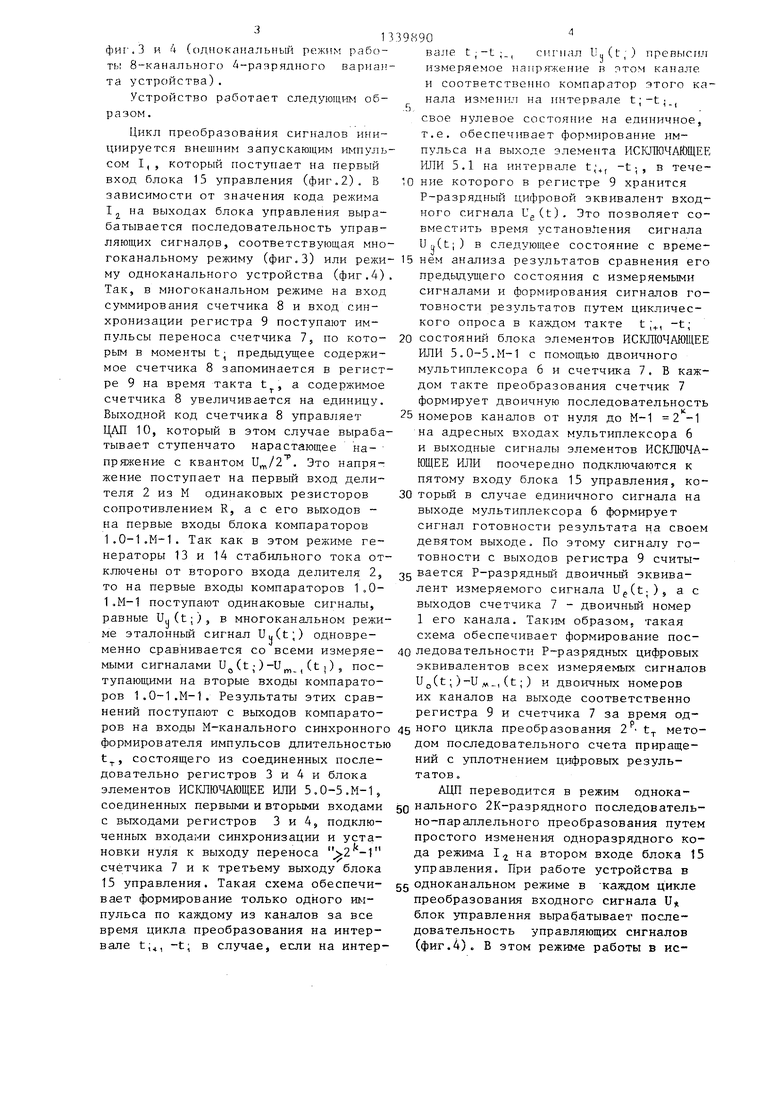

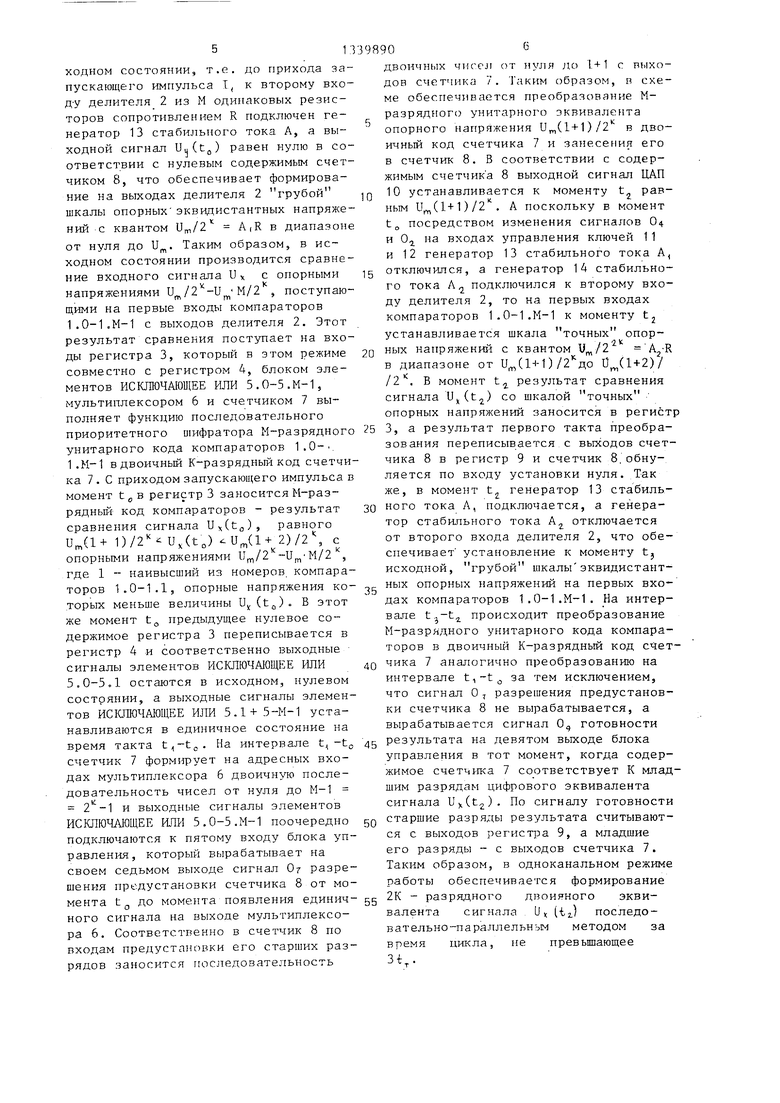

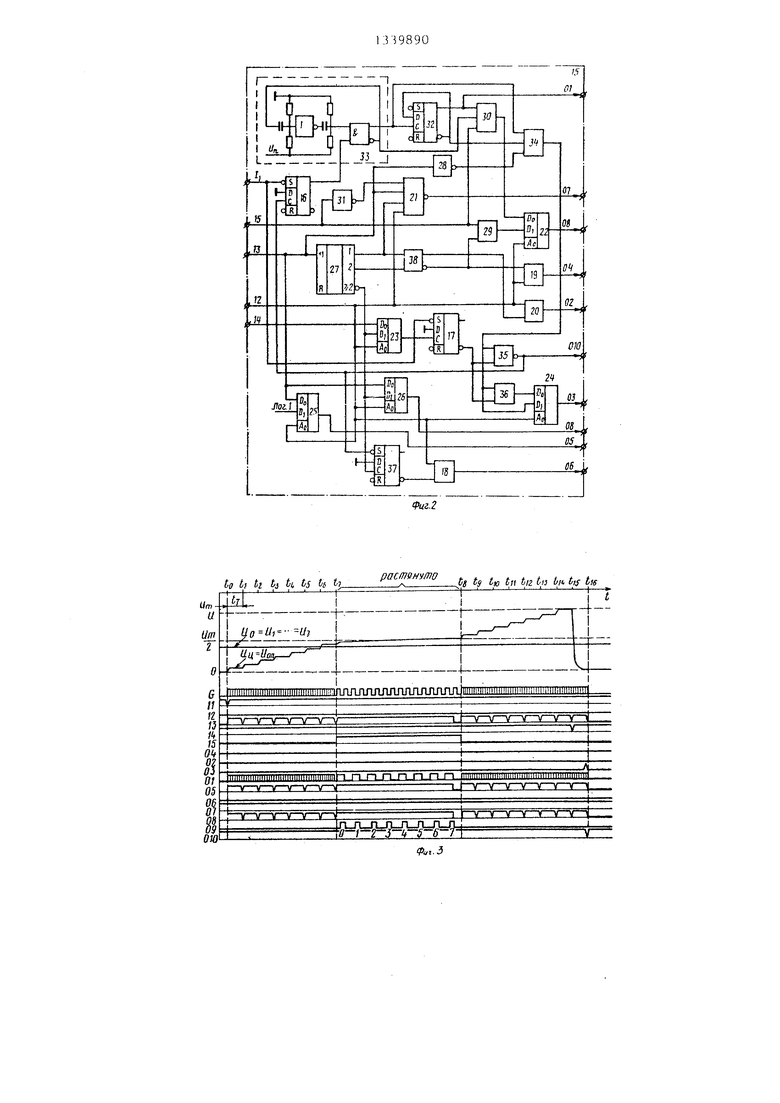

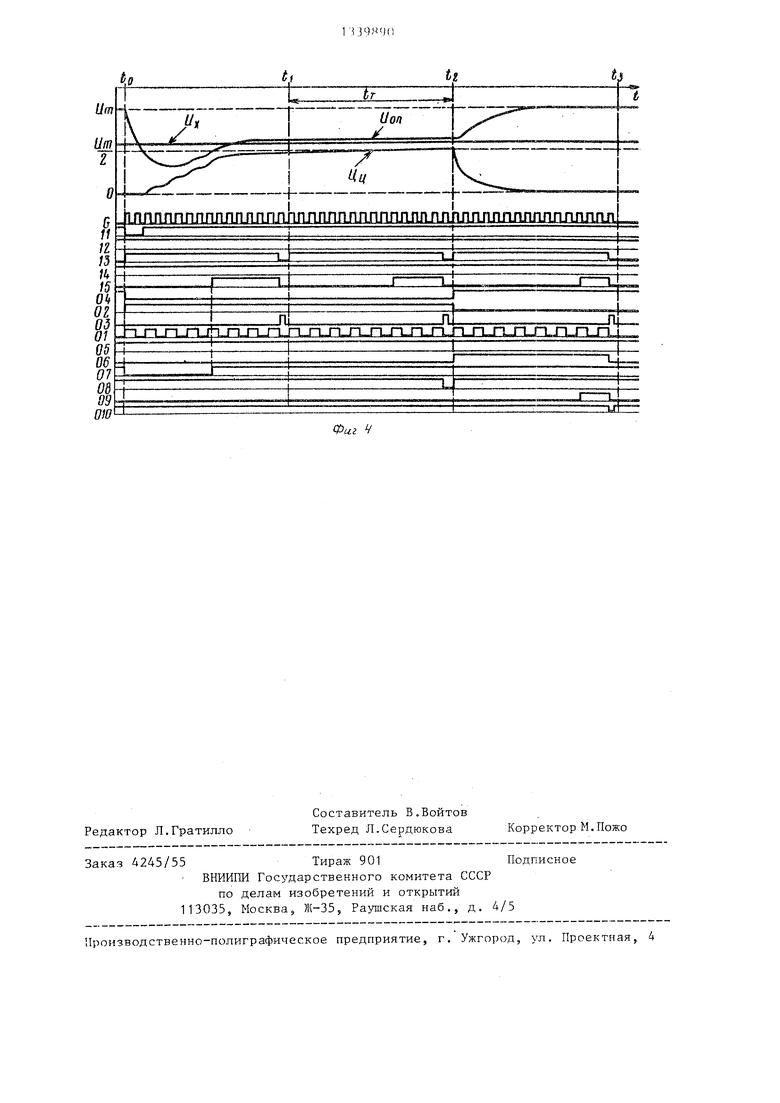

На фиг«1 и 2 изображены структурные электрические схемы устройства и его блока управления соответственно; на фиг.З и 4 - временные диаграммы, поясняющие работу устройства в много- .канальном и одноканальном режимах соответственно,

Многоканальный аналого-цифровой преобразователь (АЦП) содержит (фиг.1) блок компараторов 1.0-1.М-1, делитель 2 напряжения, регистры 3 и 4 на М разрядов, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.0-5.М-1, мультиплексор 6, двоичные счетчики 7 и 8 (К- и Р-раз- рядные), регистр 9 на Р разрядов, цифроаналоговый преобразователь (ЦАП) 10, токовые ключи 11 и 12, генерато890

делителя 2 с помощью токовых ключей 11, 12. Результаты сравнения поступают на входы синхронного формирователя импульсов, состоящего из регистров 3, 4 и блока 5 элементов ИСКЛЮЧАЮП1ЕЕ ИЛИ. Циклический опрос в каждом такте состояний блока 5 осуществляется с помощью мультиплексора 6 и счетчика. В режиме одноканального преобразования аналого-цифровой преобразователь работает по типу последовательно-параллельного преобразователя сигнала, поступающего на входы всех компараторов блока 1. При этом с помощью блока 15 управления и токовых ключей 11, 12 осуществляется поочередное подключение к делителю 2 генераторов 13, 14, что соответствует формированию грубой и точной шкал преобразователя. 1 з.п. ф-лы, 4 ил.

ры 13 и 14 стабильного тока и блок 15 управления.

Блок 15 управления (фиг.2) .содержит триггеры 16 и 17, элементы И 18- 20, элемент И-НЕ 21, мультиплексоры 22-26, счетчик 27 по модулю три, элемент НЕ 28, элементы И 29 и 30, элемент НЕ 31, счетный триггер 32, тактовый генератор 33, элемент И 34, элемент И-НЕ 35, элемент И 36, D- триггер 37 и элемент ИСКЛЮЧАЮЩЕЕ 1 ИЛИ 38,

На временных диаграммах фиг.З и 4 отмече 1Ы моменты t| выработки переднего фронта импульсов переноса счетчика 7, а также показаны длительность t одного такта, величина U, амплитудного диапазона п входных сигналов ЦАП 10, величина U амплитудного диапазона входных сигналов, выходной сигнал Un ЦАП 10, величина напряжения U,. на втором входе делителя 2, сигнал G на прямом выход тактового генератора 33 и сигналы 1 - 1 и О - О на первом - пятом входах и на первом - десятом выходах блока 15 управления соответственно. Кроме того, показаны сигналы Uo-Uy и сигнал и на вторых входах блока компараторов 1.0-1.7 соответственно на

П

фиг.З и 4 (одноканальиьцЧ режим работы 8-канального Д-разрядного вариа) та устройства).

Устройство работает следующим образом .

Цикл преобразования сигналов инициируется внешним запускающим импульсом I,, который поступает на первый вход блока 15 управления (фиг,2). В зависимости от значения кода режима I на выходах блока управления вырабатывается последовательность управ

ляющих сигналов, соответствующая мно- U(j(t;) в следующее состояние с време- гоканальному режиму (фиг.З) или режи- 15 нем анализа результатов сравнения его му одноканального устройства (фиг.4). Так, в многоканальном режиме на вход суммирования счетчика 8 и вход синхронизации регистра 9 поступают импульсы переноса счетчика 7, по кото- 20 состояний блока элементов ИСКЛЮЧАЮЩЕЕ

предьщ тцего состояния с измеряемыми сигналами и формирования сигналов готовности результатов путем циклического опроса в каждом такте t ,v, -t;

ИЛИ 5.0-5.М-1 с помощью двоичного мультиплексора 6 и счетчика 7. В каждом такте преобразования счетчик 7 формирует двоичную последовательность Выходной код счетчика 8 управляет 25 номеров каналов от нуля до М-1 2-1 ЦАП 10, который в этом случае выраба- на адресных входах мультиплексора 6

и выходные сигналы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ поочередно подключаются к пятому входу блока 15 управления, ко- 30 торый в случае единичного сигнала на выходе мультиплексора 6 формирует сигнал готовности результата на своем девятом выходе. По этому сигналу готовности с выходов регистра 9 считы- ключены от второго входа делителя 2, 35 вается Р-разрядный двоичный эквива- то на первые входы компараторов 1,0- лент измеряемого сигнала Ug(t;)5 а с

выходов счетчика 7 - двоичный номер 1 его канала. Таким образом, такая

рым в моменты t; предыдущее содержимое счетчика 8 запоминается в регистре 9 на время такта t, а содержимое счетчика 8 увеличивается на единицу.

тывает ступенчато нарастающее напряжение с квантом и„/2 . Это напряжение поступает на первый вход делителя 2 из М одинаковых резисторов сопротивлением R, а с его выходов - на первые входы блока компараторов 1.0-1.М-1. Так как в этом режиме генераторы 13 и 14 стабильного тока от1.М-1 поступают одинаковые сигналы, равные Uu(t;), в многоканальном режиме эталонный сигнал Uu(t;) одновресхема обеспечивает формирование посменно сравнивается со всеми измеряе- 40 ледовательности Р-разрядньгх цифровых

эквивалентов всех измеряемых сигисшов Uj,(t; )-и ,,, (t;) и двоичных номеров их каналов на выходе соответственно

мыми сигналами U (t )-U (t.) , поступающими на вторые входы компараторов 1.0-1.М-1. Результаты этих сравнений поступают с выходов компарато- регистра 9 и счетчика 7 за время одров на входы М-канального синхронного 45 ного цикла преобразования 2 t мето- формирователя импульсов длительностью

-т

ДОМ последовательного счета приращений с уплотнением цифровых результатов .

АЦП переводится в режим однока- 5Q нального 2К-разрядного последовательно-параллельного преобразования путем простого изменения одноразрядного кода режима 1 на втором входе блока 15 управления. При работе устройства в 15 управления. Такая схема обеспечи- 55 одноканальном режиме в -каждом цикле

преобразования входного сигнала V блок управления вьфабатывает последовательность управляющих сигналов (фиг.4). В этом режиме работы в иссостоящего из соединенных последовательно регистров 3 и 4 и блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.0-5.М-1, соединенных первыми и вторыми входами с выходами регистров 3 и 4, подключенных входами синхронизации и установки нуля к выходу переноса 2 -1 счётчика 7 и к третьему выходу блока

вает формирование только одного пульса по каждому из каналов за все время цикла преобразования на интервале t;, -t; в случае, если на интер

4

вале t;-t;.| сигнал 1Ц(1,) превысил измеряемое .кение в этом канале и cooTBeTCTBCFiHo компаратор этого канала изменил на интервале t;-tj.,

свое нулевое состояние на единичное $ т.е. обеспечивает формирование импульса на выходе элемента ИСКЛЮЧАЙЩЕЕ ИЛИ 5.1 на интервале t; + , t; , в тече- ние которого в регистре 9 хранится Рразрядный цифровой эквивалент входного сигнала Ug(t). Это позволяет совместить время установ тения сигнала

U(j(t;) в следующее состояние с време- нем анализа результатов сравнения его состояний блока элементов ИСКЛЮЧАЮЩЕЕ

предьщ тцего состояния с измеряемыми сигналами и формирования сигналов готовности результатов путем циклического опроса в каждом такте t ,v, -t;

схема обеспечивает формирование посэквивалентов всех измеряемых сигисшов Uj,(t; )-и ,,, (t;) и двоичных номеров их каналов на выходе соответственно

регистра 9 и счетчика 7 за время од ного цикла преобразования 2 t мето-

двоичных чисел от нуля до 1+1 с выходов счетчика 7. Таким образом, в схеме обеспечиЕ ается преобразование М- разрядного унитарного эквивалента опорного напряжения Vl(l + )/2

5

ичныи код счетчика

в двои занесения его

20

ходном состоянии, т.е. до прихода запускающего импульса 1( к второму входу делителя 2 из М одинаковых резисторов сопротивлением R подключен генератор 13 стабильного тока Л, а выходной сигнал UuCt) равен нулю в соответствии с нулевым содержимым счетчиком 8, что обеспечивает формирование на выходах делителя 2 грубой 0 шкалы опорных эквидистантных напряжений с квантом Urr,/2 A|R в диапазоне от нуля до и„. Таким образом, в исходном состоянии производится сравнение входного сигнала U с опорными

VК

напряжениями , поступающими на первые входы компараторов 1.0-1.М-1 с выходов делителя 2. Этот результат сравнения поступает на входы регистра 3, который в зтом режиме совместно с регистром 4, блоком элементов ИСКЛЮЧАЮЩЕЕ ИЛИ S.O-S.M-I, мультиплексором 6 и счетчиком 7 выполняет функдию последовательного опорных напряжений заносится в регистр приоритетного шифратора М-разрядного 25 3, а результат первого такта преобра- унитарного кода компараторов 1.0-.. зования переписывается с выходов счет- 1 .М-1 в двоичный К-разрядньм код счетчика 7 . С приходом запускающего импульса в момент tо в регистр 3 заносится М-раз- рядньш код компараторов - результат 30 сравнения сигнала UyCto), равного и„(1+ D/Z U,(t,) -и()/2 с опорными напряжениями , где 1 - наивысший из номеров компараторов 1.0-1.1, опорные напряжения ко- g ных опорных напряжений на первых вхо- торых меньше величины ). В этот дах компараторов 1.0-1.М-1. На интер- же момент t предыдущее нулевое содержимое регистра 3 переписывается в регистр 4 и соответственно выходные сигналы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.0-5.1 остаются в исходном, нулевом состоянии, а выходные сигналы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1+5-М-1 устанавливаются в единичное состояние на время такта t,-t(,. На интервале t,-t счетчик: 7 формирует на адресных входах мультиплексора 6 двоичную последовательность чисел от нуля до М-1 2 -1 и выходные сигналы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.0-5.М-1 поочередно подключаются к пятому входу блока уп- paвлeнIiя, который вырабатывает на своем седьмом выходе сигнал О/ разрешения предустановки счетчика 8 от мо

в счетчик 8. В соответствии с содержимым счетчика 8 выходной сигнал ЦАП 10 устанавливается к моменту t. равным и(1+1)/2 . А поскольку в момент t посредством изменения сигналов 04 и 0 на входах управления ключей 11 и 12 генератор 13 стабильного тока А, g отключился, а генератор 14 стабильного тока А подключился к второму входу делителя 2, то на первых входах компараторов 1.0-1.М-1 к моменту tj устанавливается шкала точных опорных напряжений с квантом в диапазоне от U(H-1)/2 до 1(1 + 2)/ /2 . В момент t результат сравнения сигнала ) со шкалой точных

чика 8 в регистр 9 и счетчик 8.обнуляется по входу установки нуля. Так же, в момент t генератор 13 стабильного тока А, подключается, а генератор стабильного тока А отключается от второго входа делителя 2, что обеспечивает установление к моменту tj исходной, грубой шкалы эквидистантвале t.j-t происходит преобразование М-разрядного унитарного кода компараторов в двоичный К-разрядный код счетчика 7 аналогично преобразованию на интервале ti-t за тем исключением, что сигнал О-, разрешения предустановки счетчика 8 не вырабатывается, а вырабатывается сигнал 0 готовности g результата на девятом выходе блока управления в тот момент, когда содержимое счетчика 7 соответствует К младшим разрядам цифрового эквивалента сигнала ). По сигналу готовности старшие разряды результата считываются с выходов регистра 9, а младшие его разряды - с выходов счетчика 7. Таким образом, в одноканальном режиме работы обеспечивается формирование

40

50

мента t до момента появления единич- 55 разрядного двоияного эквиного сигнала на выходе мультиплексора 6. Соответственно в счетчик 8 по входам предустановки его старших разрядов заносится последовательность

39890G

двоичных чисел от нуля до 1+1 с выходов счетчика 7. Таким образом, в схеме обеспечиЕ ается преобразование М- разрядного унитарного эквивалента опорного напряжения Vl(l + )/2

5

в ичныи код счетчика

и занесения его

опорных напряжений заносится в регистр 3, а результат первого такта преобра- зования переписывается с выходов счет- ных опорных напряжений на первых вхо- дах компараторов 1.0-1.М-1. На интер-

в счетчик 8. В соответствии с содержимым счетчика 8 выходной сигнал ЦАП 10 устанавливается к моменту t. равным и(1+1)/2 . А поскольку в момент t посредством изменения сигналов 04 и 0 на входах управления ключей 11 и 12 генератор 13 стабильного тока А, отключился, а генератор 14 стабильного тока А подключился к второму входу делителя 2, то на первых входах компараторов 1.0-1.М-1 к моменту tj устанавливается шкала точных опорных напряжений с квантом в диапазоне от U(H-1)/2 до 1(1 + 2)/ /2 . В момент t результат сравнения сигнала ) со шкалой точных

опорных напряжений заносится в регист 3, а результат первого такта преобра- зования переписывается с выходов счет- ных опорных напряжений на первых вхо- дах компараторов 1.0-1.М-1. На интер-

чика 8 в регистр 9 и счетчик 8.обнуляется по входу установки нуля. Так же, в момент t генератор 13 стабильного тока А, подключается, а генератор стабильного тока А отключается от второго входа делителя 2, что обеспечивает установление к моменту tj исходной, грубой шкалы эквидистантопорных напряжений заносится в регистр 3, а результат первого такта преобра- зования переписывается с выходов счет- ных опорных напряжений на первых вхо- дах компараторов 1.0-1.М-1. На интер-

вале t.j-t происходит преобразование М-разрядного унитарного кода компараторов в двоичный К-разрядный код счетчика 7 аналогично преобразованию на интервале ti-t за тем исключением, что сигнал О-, разрешения предустановки счетчика 8 не вырабатывается, а вырабатывается сигнал 0 готовности результата на девятом выходе блока управления в тот момент, когда содеримое счетчика 7 соответствует К младим разрядам цифрового эквивалента сигнала ). По сигналу готовности старшие разряды результата считываются с выходов регистра 9, а младшие его разряды - с выходов счетчика 7. Таким образом, в одноканальном режиме работы обеспечивается формирование

валента сигнала U, ({,2} последовательно-параллельным методом за время цикла, не превьппающее 3i..

- 13

ет уляриля структура ЛЦП позволяет практически полностью совместить элементы многоканального устройства последовательного счета приращений с уплотнением, цифровых результатов и од- ноканального устройства последовательно-параллельного типа, обеспечивает расширение допустимого частотного спектра измеряемых сигналов в многоканальном режиме в М раз и в одно- канальном режиме в 2 Р/3 раз и соответственно расширяет область применения предлагаемой схемы по сравнению со схемой последовательного счета приращений с цифровым коммутатором.

Формула изобретения

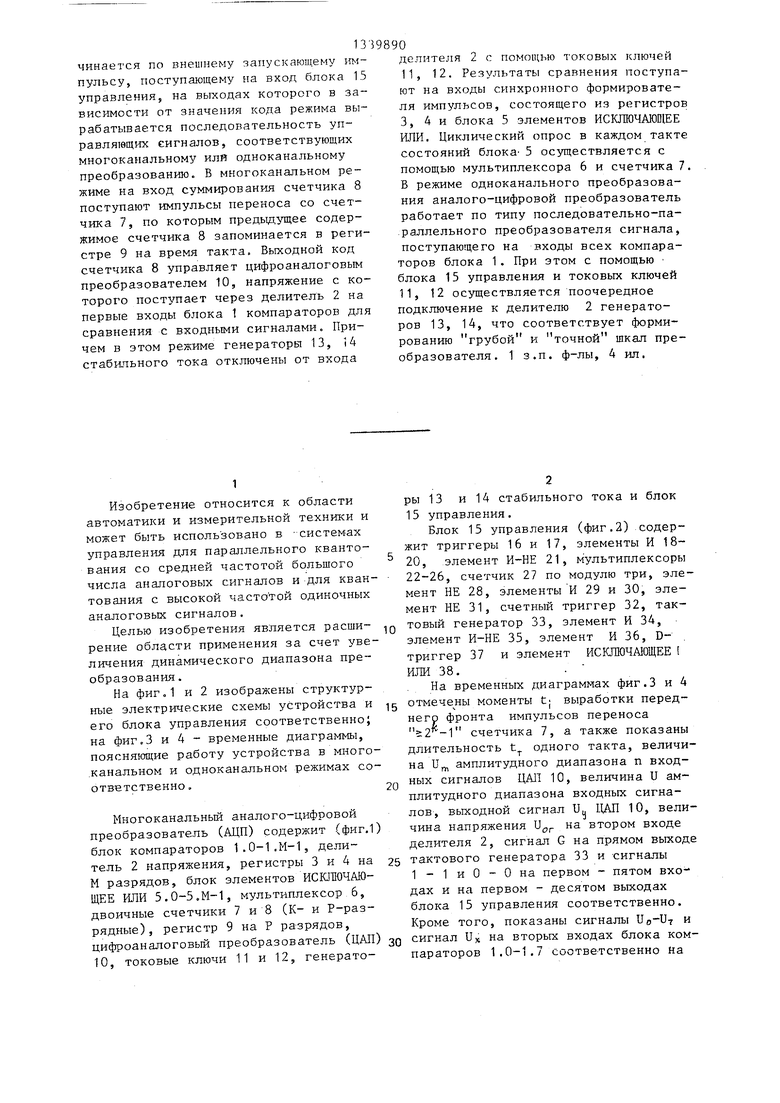

1. Многоканальньй аналого-цифровой преобразователь, содержащий блок компараторов, первые входы которого являются соответствующими шинами входных сигналов, первый регистр, выходы которого являются соответствующими выходными шинами, мультиплексор, адресные входы которого соединены с соответствующими выходами разрядов первого двоичного счетчика, цифроаналого- вьй преобразователь, входы которого соответственно объединены с информационными входами первого регистра и подключены к соответствующим выходам разрядов второго счетчика, и блок управления, первый вход которого является шиной запуска, а первый выход соединен со счетным входом первого двоичного счетчика, отличающийся тем, что, с целью расширения области применения за счет увеличения динамического диапазона преобразования, в него введены второй и третий регистры, делитель напряжения, первьй и второй токовые ключи, первый и второй генераторы стабильного тока и блок элементов ИСКЛЮЧАЮП1ЕЕ ИЛИ, первые входы которого соответственно объединены с информационными входами третьего регистра и подключены к соответствующим выходам второго регистра, информационные входы которого соответственно соединены с выходами блока компараторов, вторые входы которого подключены к соответствующим выходам делителя напряжения, первьш вход которого соединен с выходом циф- роаналогового преобразователя, а второй вход подключен к выходу второго токового ключа, токовый вход которого

8

соединен с пыходпм второго генсраторл стабильного тока, а вход управления- с вторым рзыходоь блока управления,

второй вход которого является шиной „

режима, а третий вход объединен с

входами синхронизации второго и третьего pertiCTpoB и подключен к выходу переноса первого двоичного счетчика,

выходы разрядов которого являются со- ответствующ11ми шинами номера канала и соответственно подключены к информационным входам старших разрядов второго двоичного счетчика, информа5 ционные входы младших разрядов которого являются шиной логического нуля, а выход переноса соединен с четвертым входом блока управления, пятый вход котого соединен с выходом мультиплекQ сора, информационные входы которого соединены с соответствующими выходами блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которого соединены с соответствующими выходами третьего реги5 стра, вход сброса которого объединен с входом сброса второго регистра и подключен к третьему выходу блока управления, четвертый выход которого подключен к входу управления первого

0 токового ключа, токовый вход которого соединен с выходом первого генератора стабильного тока, а выход - с , вторым входом делителя напряжения, при этом пя.тый, шестой и седьмой вы- ходы блока управления подключены соответственно к счетному входу и входам сброса и записи второго двоичного счетчика, восьмой выход блока управления соединен с входом синхронизации

0 первого регистра, а девятый и десятый выходы являются соответственно шиной готовности и шиной окончания преобразования.

2, Преобразователь по п.1, о т 5личающийся тем, что блок управления вьтолнен на первом, втором, третьем, четвертом, пятом, шестом и седьмом элементах И, первом и втором элементах И-НЕ, первом, втоQ ром, третьем, четвертом и пятом мультиплексорах, счетчике по модулю три, первом и втором элементах НЕ, счетном триггере, первом, втором и третьем D-триггерах, элементе ИСКЛЮЧАЮg ЩЕЕ ИЛИ и тактовом генераторе, прямой выход которого соединен с первым входом шестого элемента И, второй вход которого объединен с D-входом счетно- .го триггера и подключен к инверсному

выходу счетного триггера, прямой выход которого соединен с первым входом пятого элемента И и является первым выходом блока управления, а С-вход счетного триггера соединен с прямым выходом тактового генератора, инверс- выход которого подключен к второму входу пятого элемента И, а вход управления соединен с прямым выходом первого D-триггера, D-вход которого объединен с D-входами второго и третьего D-триггеров и является шиной нулевого потенциала, S-вход первого D-триггера объединен с S-входом второго D-триггера и является первым входом блока управления, а С-вход объединен с S-входом третьего D-триггера и подключен к выходу второго элемента И-НЕ, первый вход которого объединен с первым входом седьмого элемента И и первым информационным входом третьего мультиплексора и подключен к выходу шестого элемента И, а второй вход второго элемента И-НЕ объединен с вторым входом седьмого элемента И и подключен к инверсному выходу второго D-триггера, С-вход которого соединен с выходом второго мультиплексора, адресный вход кото рого объединен с адресными входами первого, третьего, четвертого и пятого мультиплексоров, первыми входами первого, второго и третьего элементов И, первым входом первого элемента И-НЕ и является вторым входом блока управления, вторым выходом которого является выход третьего элемента И, второй вход которого подключен к пер- воьгу выходу элемента ИСКШОЧАЮЩЕЕ ИЛИ, первьй и второй входы которого подключены к соответствующим информационным выходам счетчика по модулю три, счетный вход которого через первый элемент НЕ подключен к третьему входу шестого элемента И, при этом выход седьмого элемента И соединен с вторым

10

15

20

25

30

35

40

45

401 )

ииформяц К|Иныг- тг етьего мультиплексора, выход которого является третьим выходом блсжа управления, четвертым выходом которого является выход второго элемента И, второй вход которого объединен с первым входом четвертого элемента И и подключен к второму выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый информационный вход четвертого мультиплексора является шиной логической единипы, а первые информа- ционные входы второго и пятого мультиплексоров объединены с С-входом третьего D-триггера и подключены к выходу переполнения счетчика по модулю три, счетный вход которого объединен с вторыми информационными входами четвертого и пятого мультиплексоров, вторым входом первого элемента И-НЕ и является третьим входом блока управления, четвертым входом которого является второй информационный вход второго мультиплексора, а пятым и шестым выходом - соответственно выходы четвертого мультиплексора и первого элемента И, второй вход которого соединен с инверсным выходом третьего триггера, причем седьмым выходом блока управления является выход первого элемента И-НЕ, третий вход которого соединен с первым информационным выходом счетчика по модулю три, а четвертый вход - с выходом второго элемента НЕ, вход которого объединен с вторым входом четвертого элемента И и третьим входом пятого элемента И и является пятым входом блока управления, восьмым выходом которого является выход пятого мультиплексора, девятым выходом - выход первого мультиплексора, первый и второй информационные входы которого соответственно подключены к выходам четвертого и пятого элементов И, десятым выходом блока управления является выход второго элемента И-НЕ.

ys.. tg tg tio tt tilZ tl bll, ttS ttS

1 111 I

J e-Ui- u,

1ЕцглАллллпш1шгллшг|1

.

V-у-y-y-tf-V

1

.

Редактор Л.Гратилло

Составитель В.Войтов Техред Л.Сердюкова

Заказ 4245/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

Изобретение относится к автоматике и измерительной технике и может быть использовано в системах управления для параллельного квантования со средней частотой большого числа аналоговых сигналов и для квантования с высокой частотой одиночных аналоговых сигналов. Цель изобретения - расширение, области применения за счет увеличения динамического диапазона преобразования. Цикл преобразования аналого-цифрового преобразователя наСО ОО со о

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы АЦП и ЦАП | |||

| М.: Энергия, 1978, с | |||

| Котел | 1921 |

|

SU246A1 |

| Гнатек Ю.Р | |||

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям | |||

| М., 1982, с | |||

| ПРИБОР ДЛЯ ОПРЕДЕЛЕНИЯ СКОРОСТИ ТЕЧЕНИЯ ВОДЫ И ОДНОВРЕМЕННОГО ПОЛУЧЕНИЯ ПРОБ ЕЕ | 1925 |

|

SU425A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-09-23—Публикация

1985-01-06—Подача