Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем.

В результате проведенных патентно-информационных исследований аналогов предлагаемого изобретения не обнаружено.

Задачей изобретения является создание устройства, обеспечивающего сопряжение внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом с возможностью самотестирования устройства сопряжения, а также с возможностью приема и выдачи разовых команд.

Сущность изобретения заключается в том, что устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом содержит блок управления ведущего устройства, формирователь прерываний, регистр адреса чтения-записи, мультиплексор адреса-данных, регистр данных записи ведущего устройства, регистр данных чтения ведущего устройства, магистральный приемопередатчик сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства, блок формирования контрольных разрядов данных ведущего устройства, магистральный приемопередатчик сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, магистральный приемопередатчик сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства, блок управления ведомого устройства, мультиплексор адреса чтения-записи в оперативное запоминающее устройство, регистр данных записи ведомого устройства, регистр данных чтения ведомого устройства, оперативное запоминающее устройство, регистр адреса оперативного запоминающего устройства, регистр разрешенных зон адресов внешнего магистрального параллельного интерфейса, блок сравнения адреса, магистральный приемопередатчик сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, блок формирования контрольных разрядов данных ведомого устройства, магистральный приемопередатчик сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства, магистральный приемопередатчик сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства, устройство управления, дешифратор адреса внутрисистемной параллельной магистрали, регистр управления, регистр идентификатора, регистр статуса, согласующее устройство, контроллер разовых команд, формирователь выходных разовых команд, приемник входных разовых команд, магистральный приемопередатчик сигналов данных внутрисистемной параллельной магистрали, магистральный приемопередатчик сигналов адреса внутрисистемной параллельной магистрали, внутреннюю магистраль данных, внутреннюю магистраль управления, магистраль управления ведущего устройства, магистраль управления ведомого устройства, вход-выход данных внутрисистемной параллельной магистрали, вход адреса внутрисистемной параллельной магистрали, вход-выход управления внутрисистемной параллельной магистрали, вход-выход внешнего магистрального параллельного интерфейса, выход разовых команд, вход разовых команд, при этом вход блока управления ведущего устройства, первый вход блока управления ведомого устройства, управляющие входы регистра адреса чтения-записи, регистра управления, регистра идентификатора, регистра статуса, контроллера разовых команд при помощи внутренней магистрали управления соединены со вторым входом-выходом устройства управления, второй выход блока управления ведущего устройства соединен со входом формирователя прерываний, вход-выход блока управления ведущего устройства соединен с первым входом-выходом магистрального приемопередатчика сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства, управляющие входы мультиплексора адреса-данных, регистра данных записи ведущего устройства, регистра данных чтения ведущего устройства, магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства при помощи магистрали управления ведущего устройства соединены с первым выходом блока управления ведущего устройства, вход мультиплексора адреса-данных соединен с выходом регистра адреса чтения-записи, первый вход-выход мультиплексора адреса-данных соединен со входом регистра данных чтения ведущего устройства и выходом регистра данных записи ведущего устройства, второй вход-выход мультиплексора адреса-данных соединен с первым входом-выходом магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства и со входом блока формирования контрольных разрядов данных ведущего устройства, выход которого соединен с первым входом-выходом магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, управляющие входы мультиплексора адреса чтения-записи оперативного запоминающего устройства, регистра данных записи ведомого устройства, регистра данных чтения ведомого устройства, оперативного запоминающего устройства, регистра адреса оперативного запоминающего устройства, регистра разрешенных зон адресов внешнего магистрального параллельного интерфейса, магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства при помощи магистрали управления ведомого устройства соединены с выходом блока управления ведомого устройства, вход-выход блока управления ведомого устройства соединен с первым входом-выходом магистрального приемопередатчика сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства, к первому входу блока сравнения адреса подключен выход регистра разрешенных зон адресов внешнего магистрального параллельного интерфейса, ко второму входу блока сравнения адреса подключен выход мультиплексора адреса чтения- записи оперативного запоминающего устройства, выход блока сравнения адреса подключен к второму входу блока управления ведомого устройства, выход мультиплексора адреса чтения-записи оперативного запоминающего устройства соединен со входом данных регистра адреса оперативного запоминающего устройства, выход которого соединен со входом адреса оперативного запоминающего устройства, входы-выходы данных регистров управления, идентификатора и статуса, контроллера разовых команд, входы данных регистра адреса чтения-записи, регистров данных записи ведущего и ведомого устройств, регистра разрешенных зон адресов внешнего магистрального параллельного интерфейса, выходы данных регистров данных чтения ведущего и ведомого устройств соединены при помощи внутренней магистрали данных со вторым входом-выходом магистрального приемопередатчика сигналов данных внутрисистемной параллельной магистрали, первый вход-выход которого является входом-выходом данных внутрисистемной параллельной магистрали, вход дешифратора адреса внутрисистемной параллельной магистрали соединен с выходом магистрального приемопередатчика сигналов адреса внутрисистемной параллельной магистрали, вход которого является входом данных внутрисистемной параллельной магистрали, выход дешифратора адреса внутрисистемной параллельной магистрали соединен со /входом устройства управления, первый вход-выход устройства управления, первый и второй выходы формирователя прерываний образуют вход-выход управления внутрисистемной параллельной магистрали, вход регистра данных чтения ведомого устройства, выход регистра данных записи ведомого устройства, первый вход мультиплексора адреса чтения- записи оперативного запоминающего устройства, вход-выход данных оперативного запоминающего устройства, вход блока формирования контрольных разрядов данных ведомого устройства соединены с первым входом-выходом магистрального приемопередатчика сигналов адреса- данных внешнего магистрального параллельного интерфейса ведомого устройства, выход блока формирования контрольных разрядов данных ведомого устройства соединен с первым входом-выходом магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства, второй вход мультиплексора адреса чтения-записи оперативного запоминающего устройства соединен с выходом регистра адреса чтения-записи, вторые входы-выходы магистральных приемопередатчиков сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего и ведомого устройств, вторые входы-выходы магистральных приемопередатчиков сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего и ведомого устройств, вторые входы-выходы магистральных приемопередатчиков сигналов управления внешнего магистрального параллельного интерфейса ведущего и ведомого устройств соединены с первым входом-выходом согласующего устройства, второй вход-выход которого является входом-выходом внешнего магистрального параллельного интерфейса, выход контроллера разовых команд соединен со входом формирователя выходных разовых команд, выход которого является выходом разовых команд, вход контроллера разовых команд соединен с выходом приемника входных разовых команд, вход которого является входом разовых команд.

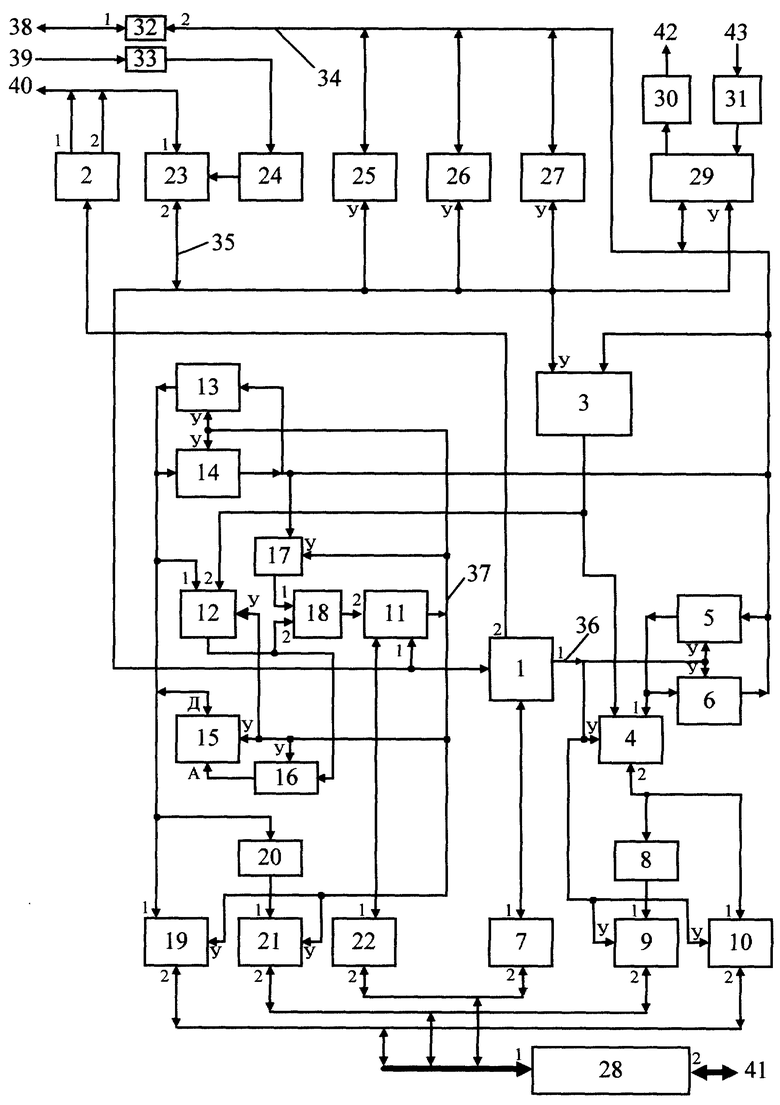

Сущность изобретения поясняется чертежом, на котором обозначены:

1 - блок управления ведущего устройства;

2 - формирователь прерываний;

3 - регистр адреса чтения-записи;

4 - мультиплексор адреса-данных;

5 - регистр данных записи ведущего устройства;

6 - регистр данных чтения ведущего устройства;

7 - магистральный приемопередатчик сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства;

8 - блок формирования контрольных разрядов данных ведущего устройства;

9 - магистральный приемопередатчик сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства;

10 - магистральный приемопередатчик сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства;

11 - блок управления ведомого устройства;

12 - мультиплексор адреса чтения-записи оперативного запоминающего устройства;

13 - регистр данных записи ведомого устройства;

14 - регистр данных чтения ведомого устройства;

15 - оперативное запоминающее устройство (ОЗУ);

16 - регистр адреса оперативного запоминающего устройства;

17 - регистр разрешенных зон адресов внешнего магистрального параллельного интерфейса;

18 - блок сравнения адреса;

19 - магистральный приемопередатчик сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства;

20 - блок формирования контрольных разрядов данных ведомого устройства,

21 - магистральный приемопередатчик сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства;

22 - магистральный приемопередатчик сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства;

23 - устройство управления;

24 - дешифратор адреса внутрисистемной параллельной магистрали;

25 - регистр управления;

26 - регистр идентификатора;

27 - регистр статуса;

28 - согласующее устройство;

29 - контроллер разовых команд;

30 - формирователь выходных разовых команд;

31 - приемник входных разовых команд;

32 - магистральный приемопередатчик сигналов данных внутрисистемной параллельной магистрали;

33 - магистральный приемопередатчик сигналов адреса внутрисистемной параллельной магистрали;

34 - внутренняя магистраль данных;

35 - внутренняя магистраль управления;

36 - магистраль управления ведущего устройства;

37 - магистраль управления ведомого устройства;

38 - вход-выход данных внутрисистемной параллельной магистрали;

39 - вход адреса внутрисистемной параллельной магистрали;

40 - вход-выход управления внутрисистемной параллельной магистрали;

41 - вход-выход внешнего магистрального параллельного интерфейса;

42 - выход разовых команд;

43 - вход разовых команд.

В предлагаемом устройстве сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом:

Вход блока 1 управления ведущего устройства, первый вход блока 11 управления ведомого устройства, управляющие входы (У) регистра 3 адреса чтения-записи, регистра 25 управления, регистра 26 идентификатора, регистра 27 статуса, контроллера 29 разовых команд при помощи внутренней магистрали 35 управления соединены со вторым входом-выходом устройства 23 управления.

Второй выход блока 1 управления ведущего устройства соединен со входом формирователя 2 прерываний.

Вход-выход блока 1 управления ведущего устройства соединен с первым входом-выходом магистрального приемопередатчика 7 сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства.

Управляющие входы (У) мультиплексора 4 адреса-данных, регистра 5 данных записи ведущего устройства, регистра 6 данных чтения ведущего устройства, магистрального приемопередатчика 9 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, магистрального приемопередатчика 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства при помощи магистрали 36 управления ведущего устройства соединены с первым выходом блока 1 управления ведущего устройства.

Вход мультиплексора 4 адреса-данных соединен с выходом регистра 3 адреса чтения-записи, первый вход-выход мультиплексора 4 адреса-данных соединен со входом регистра 6 данных чтения ведущего устройства и выходом регистра 5 данных записи ведущего устройства, второй вход-выход мультиплексора 4 адреса-данных соединен с первым входом-выходом магистрального приемопередатчика 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства и со входом блока 8 формирования контрольных разрядов данных ведущего устройства, выход которого соединен с первым входом-выходом магистрального приемопередатчика 9 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства.

Управляющие входы (У) мультиплексора 12 адреса чтения-записи ОЗУ, регистра 13 данных записи ведомого устройства, регистра 14 данных чтения ведомого устройства, ОЗУ 15, регистра 16 адреса ОЗУ, регистра 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса, магистрального приемопередатчика 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, магистрального приемопередатчика 21 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства при помощи магистрали 37 управления ведомого устройства соединены с выходом блока 11 управления ведомого устройства.

Вход-выход блока 11 управления ведомого устройства соединен с первым входом-выходом магистрального приемопередатчика 22 сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства.

К первому входу блока 18 сравнения адреса подключен выход регистра 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса, ко второму входу блока 18 сравнения адреса подключен выход мультиплексора 12 адреса чтения-записи ОЗУ, выход блока 18 сравнения адреса подключен к второму входу блока 11 управления ведомого устройства.

Выход мультиплексора 12 адреса чтения-записи ОЗУ соединен со входом данных регистра 16 адреса ОЗУ, выход регистра 16 адреса ОЗУ соединен со входом адреса (А) ОЗУ 15.

Входы-выходы данных регистров 25, 26 и 27 управления, идентификатора и статуса, контроллера 29 разовых команд, входы данных регистра 3 адреса чтения-записи, регистров 5 и 13 данных записи ведущего и ведомого устройств, регистра 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса, выходы данных регистров 6 и 14 данных чтения ведущего и ведомого устройств соединены при помощи внутренней магистрали 34 данных со вторым входом-выходом магистрального приемопередатчика 32 сигналов данных внутрисистемной параллельной магистрали, первый вход-выход которого является входом-выходом 38 данных внутрисистемной параллельной магистрали данных.

Вход дешифратора 24 адреса внутрисистемной параллельной магистрали соединен с выходом магистрального приемопередатчика 33 сигналов адреса внутрисистемной параллельной магистрали, вход которого является входом 39 адреса внутрисистемной параллельной магистрали устройства сопряжения.

Выход дешифратора 24 адреса внутрисистемной параллельной магистрали соединен со входом устройства 23 управления.

Первый вход-выход устройства 23 управления, первый и второй выходы формирователя 2 прерываний образуют вход-выход 40 управления внутрисистемной параллельной магистрали устройства сопряжения.

Вход регистра 14 данных чтения ведомого устройства, выход регистра 13 данных записи ведомого устройства, первый вход мультиплексора 12 адреса чтения-записи ОЗУ, вход-выход данных (Д) ОЗУ 15, вход блока 20 формирования контрольных разрядов данных ведомого устройства соединены с первым входом-выходом магистрального приемопередатчика 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, выход блока 20 формирования контрольных разрядов данных ведомого устройства соединены с первым входом-выходом магистрального приемопередатчика 21 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства. Второй вход мультиплексора 12 адреса чтения-записи ОЗУ соединен с выходом регистра 3 адреса чтения-записи.

Вторые входы-выходы магистральных приемопередатчиков 10 и 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего и ведомого устройств, вторые входы-выходы магистральных приемопередатчиков 9 и 21 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего и ведомого устройств, вторые входы-выходы магистральных приемопередатчиков 7 и 22 сигналов управления внешнего магистрального параллельного интерфейса ведущего и ведомого устройств соединены с первым входом-выходом согласующего устройства 28, второй вход-выход которого является входом-выходом 41 внешнего магистрального параллельного интерфейса устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом.

Выход контроллера 29 разовых команд соединен со входом формирователя 30 выходных разовых команд, выход которого является выходом 42 разовых команд устройства сопряжения, вход контроллера 29 разовых команд соединен с выходом приемника 31 входных разовых команд, вход которого является входом 43 разовых команд устройства сопряжения.

Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом обеспечивает связь различных вычислительных устройств (например, бортовой цифровой вычислительной машины) с устройствами и системами по внешнему магистральному параллельному интерфейсу в соответствии с ГОСТ 26765.51-86.

Вычислительное устройство, использующее устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом может являться ведомым (пассивным) или ведущим (активным) устройством на внешнем магистральном параллельном интерфейсе. Режим работы устанавливается программно по командам вычислительного устройства. При работе в режиме ведущего устройства устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом обеспечивает режим одиночного адресного обмена, осуществляя по командам вычислительного устройства чтение или запись данных (шестнадцатиразрядных слов). Остальные (внешние) устройства, подключенные к магистрали выполняют роль ведомых (пассивных) устройств. Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом обеспечивает режим передачи управления магистралью по запросам устройств, готовых к выполнению функции ведущего.

По завершении процедуры передачи управления магистралью, вычислительное устройства, использующее устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом становится ведомым устройством на внешнем магистральном параллельном интерфейсе. Данный режим устанавливается по включению питания изделия или программно. При этом обмен информацией между вычислительным устройством и устройством, ставшим ведущим, осуществляется через ОЗУ 15, входящее в состав устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом. При снятии сигнала "Подтверждение Запроса" (ПЗ), вычислительное устройство снова становится ведущим устройством на внешнем магистральном параллельном интерфейсе.

Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом обеспечивает прием одного системного радиального прерывания.

Устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом обеспечивает прием и выдачу 8-ми разовых команд в соответствии с ГОСТ 18997-79.

Устройство 23 управления управляет взаимодействием устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом с процессором вычислительного устройства, подключенного к входу-выходу 38, входу 39 и входу-выходу 40 данных, адреса и управления внутрисистемной параллельной магистрали.

Дешифратор 24 адреса внутрисистемной параллельной магистрали обеспечивает распознавание адреса при обращении к устройству сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом со стороны внутрисистемной параллельной магистрали.

При обращении к устройству сопряжения, устройство 23 управления формирует сигналы управления устройствами устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом на внутренней магистрали 35 управления, а также сигналы управления магистральными приемопередатчиками 32 и 33 сигналов данных и адреса внутрисистемной параллельной магистрали.

Блок 1 управления ведущего устройства, регистр 3 адреса чтения-записи, мультиплексор 4 адреса-данных, регистр 5 данных записи ведущего устройства, регистр 6 данных чтения ведущего устройства, магистральный приемопередатчик 7 сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства, блок 8 формирования контрольных разрядов данных ведущего устройства, магистральный приемопередатчик 9 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, магистральный приемопередатчик 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства обеспечивают обмен данными по внешнему магистральному параллельному интерфейсу в режиме ведущего устройства, контроль времени обмена по внешнему магистральному параллельному интерфейсу, прием и формирование сигналов передачи управления магистральным параллельным интерфейсом, формирование контрольных разрядов данных и формирование сигнала прерывания.

Блок 1 управления ведущего устройства обеспечивает формирование сигналов записи и чтения данных для регистров 5 и 6 данных записи и чтения ведущего устройства, формирование сигналов управления магистральными приемопередатчиками 7, 9, 10 сигналов управления, контрольных разрядов данных и адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства, формирование временной диаграммы обмена в соответствии с ГОСТ 26765.51-86 (ведущее устройство), прием и формирование сигналов передачи управления магистральным параллельным интерфейсом, контроль времени обмена по внешнему магистральному параллельному интерфейсу и формирование сигнала прерывания на внутрисистемной параллельной магистрали при отсутствии сигнала ответа в течение заданного времени.

Регистр 5 данных записи ведущего устройства предназначен для хранения данных, подготовленных для передачи от данного устройства сопряжения в устройства, подключенные к внешнему магистральному параллельному интерфейсу при работе устройства сопряжения в режиме ведущего устройства. По завершении обращения к данному регистру со стороны внутрисистемной параллельной магистрали под управлением блока 1 управления ведущего устройства формируется циклограмма записи по внешнему магистральному параллельному интерфейсу.

Регистр 6 данных записи ведущего устройства предназначен для хранения данных, принятых по внешнему магистральному параллельному интерфейсу при работе устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом в режиме ведущего устройства. По завершении обращения к данному регистру, под управлением блока 1 управления ведущего устройства формируется циклограмма чтения по внешнему магистральному параллельному интерфейсу.

Регистр 3 адреса записи-чтения содержит адрес запоминающих устройств, подключенных к внешнему магистральному параллельному интерфейсу при операциях чтении-записи по внешнему магистральному параллельному интерфейсу, когда устройство сопряжения работает в режиме ведущего устройства. Когда устройство сопряжения работает в режиме ведомого устройства, регистр 3 адреса чтения-записи содержит адрес ОЗУ 15 устройства сопряжения.

При записи данных по внешнему магистральному параллельному интерфейсу блок 8 формирования контрольных разрядов данных ведущего устройства обеспечивает аппаратное формирование и выдачу контрольных разрядов данных (дополнение до нечетного количества единиц в каждом байте данных).

Магистральные приемопередатчики 7, 9 и 10 сигналов управления, контрольных разрядов данных и адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства обеспечивают электрическое сопряжение устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом с согласующим устройством 28.

Согласующее устройство 28 обеспечивает согласование нагрузки.

Блок 11 управления ведомого устройства, регистр 3 адреса чтения-записи, мультиплексор 12 адреса чтения-записи в ОЗУ, регистр 13 данных записи ведомого устройства, регистр 14 данных чтения ведомого устройства, ОЗУ 15, регистр 16 адреса ОЗУ, регистр 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса, блок 18 сравнения адреса, магистральный приемопередатчик 22 сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства, блок 20 формирования контрольных разрядов данных ведомого устройства, магистральный приемопередатчик 21 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства, магистральный приемопередатчик 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства обеспечивают обмен данными по внешнему магистральному параллельному интерфейсу в режиме ведомого устройства, контроль разрешенных зон адресов внешнего магистрального параллельного интерфейса, формирование обращений к ОЗУ 15, формирование контрольных разрядов данных.

Блок 11 управления ведомого устройства обеспечивает формирование сигналов обмена в соответствии с временной диаграммой по ГОСТ 26765.51-86 (ведомое устройство), формирование сигналов чтения и записи в ОЗУ 15, а также формирование сигналов записи и чтения в регистры 13 и 14 данных записи и чтения ведомого устройства и регистр 16 адреса ОЗУ, а также формирование сигналов управления магистральными приемопередатчиками 22, 21, 19 сигналов управления, контрольных разрядов данных и адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства.

Регистр 13 данных записи ведомого устройства предназначен для хранения данных, подготовленных для записи в ОЗУ 15.

Регистр 14 данных чтения ведомого устройства предназначен для хранения данных, прочитанных из ОЗУ 15. При обращении к регистру 14 данных чтения ведомого устройства, осуществляется чтение данных из ОЗУ 15.

Оперативное запоминающее устройство 15 служит для хранения данных выдаваемых и принимаемых по внешнему магистральному параллельному интерфейсу при работе в режиме ведомого устройства (пассивном режиме). Доступ к ОЗУ 15 со стороны внутрисистемной параллельной магистрали (вычислительного устройства, использующего устройство сопряжения) осуществляется через регистры 13 и 14 данных записи и чтения ведомого устройства.

Мультиплексор 12 адреса чтения-записи в ОЗУ обеспечивает передачу или адреса из регистра 3 адреса чтения-записи (при обращении со стороны внутрисистемной параллельной магистрали, то есть со стороны вычислительного устройства, использующего устройство сопряжения), или адреса, принятого по внешнему магистральному параллельному интерфейсу. При обращении со стороны внешнего магистрального параллельного интерфейса для временного хранения адреса ОЗУ 15, принятого по внешнему магистральному параллельному интерфейсу используется регистр 16 адреса ОЗУ.

При записи данных по внешнему магистральному параллельному интерфейсу блок 20 формирования контрольных разрядов данных ведомого устройства обеспечивает аппаратное формирование и выдачу контрольных разрядов данных (дополнение до нечетного количества единиц в каждом байте данных).

При обращении к ОЗУ 15 по внешнему магистральному параллельному интерфейсу блок 18 сравнения адреса сравнивает старшие разряды принятого адреса с данными регистра 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса. Если принятый адрес соответствует диапазону адресов внешнего магистрального параллельного интерфейса, отведенному для данного устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом блок 18 сравнения адреса формирует соответствующий сигнал, который поступает на второй вход блока 11 управления ведомого устройства, что разрешает обмен по внешнему магистральному параллельному интерфейсу.

Магистральные приемопередатчики 22, 21 и 19 сигналов управления, контрольных разрядов данных и адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства обеспечивают электрическое сопряжение с согласующим устройством 28.

Контроллер 29 разовых команд содержит регистр для хранения 8-ми выходных разовых команд, а также, содержит вход входных разовых команд данных с 8-разрядного приемника входных разовых команд.

Приемник 31 входных разовых команд выполнен на компараторах и обеспечивает прием разовых команд, поступающих со входа 43 разовых команд в виде сигнала "ключ на корпус/разрыв". Входная цепь каждого разряда входных разовых команд содержит резистор привязки к напряжению питания и защитный диод, обеспечивающий прием входных сигналов напряжением до 27 В. С выхода компараторов сигналы разовых команд через контроллер 29 разовых команд доступны по чтению через соответствующий порт ввода-вывода внутрисистемной параллельной магистрали.

Выходные разовые команды, выдаваемые через выход 42 разовых команд, формируются записью в соответствующий порт ввода-вывода по внутрисистемной параллельной магистрали и сохраняются в регистре выходных разовых команд контроллера 29 разовых команд. Выход каждого разряда регистра разовых команд контроллера 29 разовых команд подключен к схеме формирования выходных разовых команд формирователя 30 выходных разовых команд.

Схемы формирования выходных разовых команд формирователя 30 выходных разовых команд выполнены на транзисторах с открытым истоком. Выходные разовые команды выдаются в виде сигнала "ключ на корпус/разрыв цепи". В качестве защитного элемента в каждый блок формирования выходных разовых команд установлен резистор.

Взаимодействие вычислительного устройства, подключенного к устройству сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом, производится по внутрисистемной параллельной магистрали через порты ввода-вывода внутрисистемной параллельной магистрали (магистрали ISA), чем обеспечивается доступ к регистрам устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом.

Управление режимами работы устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом (ведущее или ведомое устройство на внешнем магистральном параллельном интерфейсе, разрешение или запрещение формирования прерываний на внутрисистемной параллельной магистрали при поступлении сигналов прерывания по внешнему магистральному параллельному интерфейсу или при поступлении запроса на передачу функции ведущего устройства к другому устройству, управление режимами передачи функций ведущего устройства) осуществляется путем записи соответствующих разрядов регистра 25 управления.

Регистр 26 идентификатора обеспечивает выдачу на внутрисистемную параллельную магистраль кода идентификатора платы устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом.

Регистр 27 статуса используется для осуществления контроля за работой устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом (контроля за состоянием обмена по внешнему магистральному параллельному интерфейсу).

Так как доступ к внешнему магистральному параллельному интерфейсу в режиме ведущего и ведомого устройства обеспечиваются независимо различными элементами устройства сопряжения, причем, обмен в режиме ведомого устройства приходит независимо от обмена по внутрисистемной параллельной магистрали (независимо от вычислительного устройства, использующего устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом), то возможен режим, когда часть элементов устройства сопряжения, обеспечивающая работу в режиме ведущего устройства, осуществляет доступ по внешнему магистральному параллельному интерфейсу к ОЗУ 15, то есть, другая часть элементов устройства сопряжения одновременно обеспечивает обмен по внешнему магистральному параллельному интерфейсу в режиме ведомого устройства. Для этого адрес на внешнем магистральном параллельном интерфейсе, задаваемый ведущим устройством, должен соответствовать диапазону, который определен значением, записанным в регистре 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса. Это обеспечивает возможность самотестирования устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом.

Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом работает следующим образом.

При работе в режиме ведущего устройства (активном режиме) обмен по магистральному параллельному интерфейсу инициируется сигналами, поступающими по внутрисистемной параллельной магистрали.

Запись данных по внешнему магистральному параллельному интерфейсу происходит следующим образом. Режим записи данных в устройства, подключенные к внешнему магистральному параллельному интерфейсу (к входу-выходу 41 внешнего магистрального параллельного интерфейса) инициируется по завершении записи данных в регистр 5 записи данных ведущего устройства. Запись данных в регистр 5 записи данных ведущего устройства происходит при появлении сигнала записи в случае, когда адрес, выставленный на внутрисистемной параллельной магистрали соответствует адресу порта ввода-вывода данного регистра. Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом автоматически разворачивает циклограмму записи в соответствии с ГОСТ 26765.51- 86, осуществляя запись данных из регистра 5 записи данных ведущего устройства, хранящемуся в регистре 3 адреса чтения-записи. Для этого под управлением блока 1 управления ведущего устройства (сигналы от этого устройства поступают к соответствующим устройствам устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом по магистрали 36 управления ведущего устройства), вначале мультиплексор 4 адреса-данных подключает к первому входу-выходу магистрального приемопередатчика 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства и ко входу блока 8 формирования сигналов контрольных разрядов данных ведущего устройства выход регистра 3 адреса чтения-записи, и адрес из регистра 3 адреса чтения-записи поступает через магистральный приемопередатчик 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства и согласующее устройство 28 на внешний магистральный параллельный интерфейс, при этом также выдаются контрольные разряды с выхода блока 8 формирования контрольных разрядов данных ведущего устройства через магистральный приемопередатчик 9 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, выдаются и принимаются соответствующие сигналы управления с входа-выхода блока 1 управления ведущего устройства через магистральный приемопередатчик 7 сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства. Затем мультиплексор 4 адреса-данных подключает к первому входу-выходу магистрального приемопередатчика 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства и ко входу блока 8 формирования сигналов контрольных разрядов данных ведущего устройства выход регистра 5 данных записи ведущего устройства и данные из этого регистра аналогичным образом передаются по внешнему магистральному параллельному интерфейсу.

Режим чтения данных из устройств, подключенные к внешнему магистральному параллельному интерфейсу (к входу-выходу 41 внешнего магистрального параллельного интерфейса) инициируется либо по завершении записи адреса в регистр 3 адреса чтения-записи, либо по завершении чтения данных из регистра 6 данных чтения ведущего устройства. При этом устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом автоматически разворачивает циклограмму чтения в соответствии с ГОСТ 26765.51-86, осуществляя чтение данных в регистр 6 данных чтения ведущего устройства из устройств, подключенных к внешнему магистральному параллельному интерфейсу по адресу, хранящемуся в регистре 3 адреса чтения-записи. При этом в начале так же, как и при операции записи, происходит передача адреса из регистра 3 адреса чтения-записи на магистральный параллельный интерфейс, а затем, когда мультиплексор 4 подключает вход регистра 6 данных чтения ведущего устройства к первому входу-выходу магистрального приемопередатчика 10 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства, происходит передача данных с внешнего магистрального параллельного интерфейса в регистр 6 данных чтения ведущего устройства. Эти данные затем могут быть прочитаны вычислительным устройством, подключенным к устройству сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом путем чтения соответствующего порта ввода-вывода внутрисистемной параллельной магистрали.

При операциях чтения и записи в режиме ведущего устройства в регистр 27 статуса выдается информация о нахождении устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом в состоянии взаимодействия по внешнему магистральному параллельному интерфейсу. При этом осуществляется приостановка циклов внутрисистемной параллельной магистрали до момента завершения цикла обмена по внешнему магистральному параллельному интерфейсу.

Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом контролирует время от момента формирования сигналов чтения или записи до появления сигнала ответа (сигнала квитирования). При отсутствии сигнала ответа (сигнала квитирования) в течение заданного времени автоматически прерывает процедуру обмена по внешнему магистральному параллельному интерфейсу и формирует соответствующий разряд в регистре 27 статуса, который обнуляется по завершении обращения к порту данного регистра.

При успешном завершении обмена по внешнему магистральному параллельному интерфейсу осуществляется увеличение состояния младшего байта регистра 3 адреса чтения-записи на единицу.

При поступлении по магистральному параллельному интерфейсу сигнала запроса на управление внешним магистральным параллельным интерфейсом в соответствующем разряде регистра 27 статуса устанавливается признак запроса на управление внешним магистральным параллельным интерфейсом, а также при помощи формирователя 2 прерывания формируется сигнал прерывания на внутрисистемной параллельной магистрали. В случае, если при этом вычислительное устройство, подключенное к устройству сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом, получив сигнал прерывания, принимает решение о передаче управления внешним магистральным параллельным интерфейсом и записывает в соответствующий разряд регистра 25 управления признак разрешения передачи управления внешним магистральным параллельным интерфейсом, то инициируется процедура передачи управления внешним магистральным параллельным интерфейсом устройству, готовому к выполнению функции ведущего. Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом становится ведомым устройством на внешнем магистральном параллельном интерфейсе.

Обмен информацией между устройством сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом и устройством, ставшим ведущим, осуществляется через ОЗУ 15 следующим образом. Адрес, поступающий по внешнему магистральному параллельному интерфейсу через магистральный приемопередатчик 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства и мультиплексор 12 адреса чтения-записи в ОЗУ, поступает на вход блока 18 сравнения адреса, а также записывается в регистр 16 адреса ОЗУ и поступает на адресный вход (А) ОЗУ 15. Блок 18 сравнения адреса сравнивает старшие разряды принятого адреса с данными регистра 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса. Если принятый адрес соответствует диапазону адресов внешнего магистрального параллельного интерфейса, отведенному для данного устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом, блок 18 сравнения адреса формирует соответствующий сигнал, который поступает на второй вход блока 11 управления ведомого устройства, которое выдает по магистрали 37 управления ведомого устройства на управляющий вход (У) ОЗУ 15 соответствующую команду чтения или записи.

При чтении ОЗУ 15 выдает через свой вход-выход данных (Д) данные на первый вход-выход магистрального приемопередатчика 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства и на вход блока 20 формирования контрольных разрядов данных ведомого устройства. Эти данные через магистральный приемопередатчик 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства и согласующее устройство 28 выдаются на внешний магистральный параллельный интерфейс, при этом также выдаются контрольные разряды с выхода блока 20 формирования контрольных разрядов данных ведомого устройства через магистральный приемопередатчик 21 сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства, выдаются и принимаются соответствующие сигналы управления с входа-выхода блока 11 управления ведомого устройства через магистральный приемопередатчик 22 сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства.

При записи данных по внешнему магистральному параллельному интерфейсу в ОЗУ 15, эти данные поступают через магистральный приемопередатчик 19 сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства на вход-выход данных (Д) ОЗУ 15 и записываются в него, а также поступают и передаются соответствующие сигналы управления через магистральный приемопередатчик 22 сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства.

Доступ к ОЗУ 15 обеспечивается также и со стороны внутрисистемной параллельной магистрали. При этом запись данных инициируется при обращении к регистру 13 данных записи ведомого устройства. Для осуществления операции записи в ОЗУ 15, вначале в регистр 3 адреса чтения-записи записывается адрес, по которому будет производиться запись в ОЗУ 15, при этом, блок 11 управления ведомого устройства переключает мультиплексор 12 адреса чтения-записи в ОЗУ, и адрес с выхода регистра 3 адреса чтения-записи записывается в регистр 16 адреса ОЗУ и с его выхода поступает на адресный вход (А) ОЗУ 15. Затем в регистр 13 данных записи ведомого устройства записываются данные для записи, которые с выхода регистра 13 данных записи ведомого устройства поступают на вход-выход данных (Д) ОЗУ 15.

Чтение данных со стороны внутрисистемной параллельной магистрали из ОЗУ 15 инициируется при обращении к регистру 14 данных чтения ведомого устройства. При этом, аналогично операции записи, вначале в регистр 3 адреса чтения-записи записывается адрес, по которому будет производиться чтение из ОЗУ 15. Затем производиться чтение, данные с входа-выхода данных (Д) ОЗУ 15 поступают на вход регистра 14 данных чтения ведомого устройства, записываются в него и передаются на внутрисистемную параллельную магистраль.

После завершения цикла обмена по внутрисистемной параллельной магистрали, адрес, хранящийся в регистре 3 адреса чтения-записи автоматически увеличивается на единицу, что позволяет производить дальнейшие операции чтения или записи без записи нового адреса в регистр 3 адреса чтения-записи.

Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом обеспечивает равноприоритетный доступ к ОЗУ 15 как со стороны внешнего магистрального параллельного интерфейса, так и со стороны внутрисистемной параллельной магистрали.

Если адрес на внешнем магистральном параллельном интерфейсе, задаваемый устройством сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом при работе в режиме ведущего устройства соответствует диапазону, который определен значением, записанным в регистре 17 разрешенных зон адресов внешнего магистрального параллельного интерфейса, то часть элементов устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом, отвечающая за работу в режиме ведомого устройства, одновременно обеспечивает обмен по внешнему магистральному параллельному интерфейсу в режиме ведомого устройства, то есть осуществляется доступ по внешнему магистральному параллельному интерфейсу к ОЗУ 15. Это обеспечивает возможность самотестирования устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом.

Таким образом, предлагаемое изобретение обеспечивает сопряжение внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом с возможностью самотестирования устройства сопряжения, а также с возможностью приема и выдачи разовых команд.

Представленные чертежи и описание устройства сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом позволяют, используя существующую элементную базу, изготовить его промышленным способом и использовать в вычислительных устройствах различного назначения, что характеризует предлагаемое изобретение как промышленно применимое.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ С ИНТЕРФЕЙСОМ ПОСЛЕДОВАТЕЛЬНОГО КОДА | 2000 |

|

RU2201617C2 |

| АДАПТЕР РАДИАЛЬНЫХ КАНАЛОВ ИНФОРМАЦИОННОГО ОБМЕНА | 2000 |

|

RU2159954C1 |

| Способ передачи данных по шине, система связи для осуществления данного способа и устройство автоматической защиты для предотвращения аварийной ситуации на объекте управления | 2018 |

|

RU2705421C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2012 |

|

RU2524852C2 |

| АДАПТЕР МУЛЬТИПЛЕКСНЫХ КАНАЛОВ ИНФОРМАЦИОННОГО ОБМЕНА | 2000 |

|

RU2163728C1 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| МНОГОКАНАЛЬНЫЙ АДАПТЕР АНАЛОГОВОГО ВВОДА-ВЫВОДА | 2000 |

|

RU2183857C1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем. Техническим результатом является обеспечение сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом с возможностью самотестирования устройства. Устройство содержит блоки управления ведущего и ведомого устройств, формирователи прерываний, выходных разовых команд, регистры адреса чтения-записи, данных записи ведущего и ведомого устройств, данных чтения ведущего и ведомого устройств, адреса оперативного запоминающего устройства, разрешенных зон адресов внешнего магистрального параллельного интерфейса управления, идентификатора, статуса, мультиплексоры адреса-данных, адреса чтения-записи оперативного запоминающего устройства, блоки формирования контрольных разрядов ведомого и ведущего устройств, оперативное запоминающее устройство, устройство управления, блок сравнения адреса, дешифратор адреса внутрисистемной параллельной магистрали, согласующее устройство, контроллер разовых команд, магистральные приемопередатчики сигналов. 1 ил.

Устройство сопряжения внутрисистемной параллельной магистрали с внешним магистральным параллельным интерфейсом, характеризующееся тем, что оно содержит блок управления ведущего устройства, формирователь прерываний, регистр адреса чтения-записи, мультиплексор адреса-данных, регистр данных записи ведущего устройства, регистр данных чтения ведущего устройства, магистральный приемопередатчик сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства, блок формирования контрольных разрядов данных ведущего устройства, магистральный приемопередатчик сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, магистральный приемопередатчик сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства, блок управления ведомого устройства, мультиплексор адреса чтения-записи в оперативное запоминающее устройство, регистр данных записи ведомого устройства, регистр данных чтения ведомого устройства, оперативное запоминающее устройство, регистр адреса оперативного запоминающего устройства, регистр разрешенных зон адресов внешнего магистрального параллельного интерфейса, блок сравнения адреса, магистральный приемопередатчик сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, блок формирования контрольных разрядов данных ведомого устройства, магистральный приемопередатчик сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства, магистральный приемопередатчик сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства, устройство управления, дешифратор адреса внутрисистемной параллельной магистрали, регистр управления, регистр идентификатора, регистр статуса, согласующее устройство, контроллер разовых команд, формирователь выходных разовых команд, приемник входных разовых команд, магистральный приемопередатчик сигналов данных внутрисистемной параллельной магистрали, магистральный приемопередатчик сигналов адреса внутрисистемной параллельной магистрали, внутреннюю магистраль данных, внутреннюю магистраль управления, магистраль управления ведущего устройства, магистраль управления ведомого устройства, вход-выход данных внутрисистемной параллельной магистрали, вход адреса внутрисистемной параллельной магистрали, вход-выход управления внутрисистемной параллельной магистрали, вход-выход внешнего магистрального параллельного интерфейса, выход разовых команд, вход разовых команд, при этом вход блока управления ведущего устройства, первый вход блока управления ведомого устройства, управляющие входы регистра адреса чтения-записи, регистра управления, регистра идентификатора, регистра статуса, контроллера разовых команд при помощи внутренней магистрали управления соединены со вторым входом-выходом устройства управления, второй выход блока управления ведущего устройства соединен со входом формирователя прерываний, вход-выход блока управления ведущего устройства соединен с первым входом-выходом магистрального приемопередатчика сигналов управления внешнего магистрального параллельного интерфейса ведущего устройства, управляющие входы мультиплексора адреса-данных, регистра данных записи ведущего устройства, регистра данных чтения ведущего устройства, магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства при помощи магистрали управления ведущего устройства соединены с первым выходом блока управления ведущего устройства, вход мультиплексора адреса-данных соединен с выходом регистра адреса чтения-записи, первый вход-выход мультиплексора адреса-данных соединен со входом регистра данных чтения ведущего устройства и выходом регистра данных записи ведущего устройства, второй вход-выход мультиплексора адреса-данных соединен с первым входом-выходом магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего устройства и со входом блока формирования контрольных разрядов данных ведущего устройства, выход которого соединен с первым входом-выходом магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего устройства, управляющие входы мультиплексора адреса чтения-записи оперативного запоминающего устройства, регистра данных записи ведомого устройства, регистра данных чтения ведомого устройства, оперативного запоминающего устройства, регистра адреса оперативного запоминающего устройства, регистра разрешенных зон адресов внешнего магистрального параллельного интерфейса, магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства при помощи магистрали управления ведомого устройства соединены с выходом блока управления ведомого устройства, вход-выход блока управления ведомого устройства соединен с первым входом-выходом магистрального приемопередатчика сигналов управления внешнего магистрального параллельного интерфейса ведомого устройства, к первому входу блока сравнения адреса подключен выход регистра разрешенных зон адресов внешнего магистрального параллельного интерфейса, ко второму входу блока сравнения адреса подключен выход мультиплексора адреса чтения-записи оперативного запоминающего устройства, выход блока сравнения адреса подключен к второму входу блока управления ведомого устройства, выход мультиплексора адреса чтения-записи оперативного запоминающего устройства соединен со входом данных регистра адреса оперативного запоминающего устройства, выход которого соединен со входом адреса оперативного запоминающего устройства, входы-выходы данных регистров управления, идентификатора и статуса, контроллера разовых команд, входы данных регистра адреса чтения-записи, регистров данных записи ведущего и ведомого устройств, регистра разрешенных зон адресов внешнего магистрального параллельного интерфейса, выходы данных регистров данных чтения ведущего и ведомого устройств соединены при помощи внутренней магистрали данных со вторым входом-выходом магистрального приемопередатчика сигналов данных внутрисистемной параллельной магистрали, первый вход-выход которого является входом-выходом данных внутрисистемной параллельной магистрали, вход дешифратора адреса внутрисистемной параллельной магистрали соединен с выходом магистрального приемопередатчика сигналов адреса внутрисистемной параллельной магистрали, вход которого является входом данных внутрисистемной параллельной магистрали, выход дешифратора адреса внутрисистемной параллельной магистрали соединен со входом устройства управления, первый вход-выход устройства управления, первый и второй выходы формирователя прерываний образуют вход-выход управления внутрисистемной параллельной магистрали, вход регистра данных чтения ведомого устройства, выход регистра данных записи ведомого устройства, первый вход мультиплексора адреса чтения-записи оперативного запоминающего устройства, вход-выход данных оперативного запоминающего устройства, вход блока формирования контрольных разрядов данных ведомого устройства соединены с первым входом-выходом магистрального приемопередатчика сигналов адреса-данных внешнего магистрального параллельного интерфейса ведомого устройства, выход блока формирования контрольных разрядов данных ведомого устройства соединен с первым входом-выходом магистрального приемопередатчика сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведомого устройства, второй вход мультиплексора адреса чтения-записи оперативного запоминающего устройства соединен с выходом регистра адреса чтения-записи, вторые входы-выходы магистральных приемопередатчиков сигналов адреса-данных внешнего магистрального параллельного интерфейса ведущего и ведомого устройств, вторые входы-выходы магистральных приемопередатчиков сигналов контрольных разрядов данных внешнего магистрального параллельного интерфейса ведущего и ведомого устройств, вторые входы-выходы магистральных приемопередатчиков сигналов управления внешнего магистрального параллельного интерфейса ведущего и ведомого устройств соединены с первым входом-выходом согласующего устройства, второй вход-выход которого является входом-выходом внешнего магистрального параллельного интерфейса, выход контроллера разовых команд соединен со входом формирователя выходных разовых команд, выход которого является выходом разовых команд, вход контроллера разовых команд соединен с выходом приемника входных разовых команд, вход которого является входом разовых команд.

| RU 2058042 C1, 10.04.1996 | |||

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| US 4371928 A, 01.02.1983 | |||

| US 5148527 A, 15.09.1992. | |||

Авторы

Даты

2001-04-20—Публикация

2000-05-11—Подача