Изобретение относится к области обработки аналоговых и дискретных сигналов и может быть использовано для сопряжения различных вычислительных систем с исполнительными устройствами и датчиками, использующими как аналоговые сигналы, так и разовые команды (дискретные сигналы).

Известно устройство для сопряжения ЭВМ с каналами связями [1], содержащее коммутатор входных каналов, блок преобразования последовательного кода в параллельный, шину информационной магистрали устройства, приемопередатчик, блок обмена, генератор синхроимпульсов, блок выходных усилителей (формирователей), блок памяти микрокоманд, арифметико-логический блок, регистр режима, дешифратор микрокоманд и блок квитирования обмена.

Известно многоканальное устройство для ввода-вывода аналоговой информации [2], которое содержит коммутаторы с первого по четвертый, инвертор, блок памяти, цифроаналоговый преобразователь, усилитель, компаратор, блок сопряжения (контроллер внешней интерфейсной магистрали информационного обмена), арифметико-логический блок, регистр и умножитель.

Известен также многоканальный адаптер аналогового ввода-вывода [3], являющийся по технической сущности наиболее близким к предлагаемому устройству. Этот многоканальный адаптер содержит цифроаналоговый преобразователь, контроллер внешней интерфейсной магистрали информационного обмена, первый усилитель, дополнительно содержит аналого-цифровой преобразователь, m-1 цифроаналоговых преобразователей, микропроцессор, устройство управления аналого-цифровым преобразователем, устройство управления цифроаналоговыми преобразователями, второй усилитель, третий усилитель, четвертый усилитель, первый ключ включения тестового режима, второй ключ включения тестового режима, третий ключ включения тестового режима, четвертый ключ включения тестового режима, первый мультиплексор, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, m ключей, формирователь опорного напряжения, блок синхронизации, внутреннюю параллельную интерфейсную магистраль информационного обмена, внутреннюю последовательную интерфейсную магистраль информационного обмена.

Устройство-прототип не обеспечивает ввод-вывод сигналов разовых команд (дискретных сигналов) и надежное формирование команды через заданный интервал (интервалы) времени.

Задачей, решаемой изобретением, является создание устройства ввода-вывода, обеспечивающего наряду с вводом-выводом аналоговых сигналов ввод-вывод сигналов разовых команд (дискретных сигналов) и надежное формирование команды через заданный интервал (интервалы) времени.

Сущность изобретения заключается в том, что устройство ввода-вывода содержит приемопередатчик магистрального канала информационного обмена, контроллер магистрального канала информационного обмена, микроЭВМ, дешифратор, первый триггер, второй триггер, буферный элемент, аналого-цифровой преобразователь, мультиплексор, многоканальный цифроаналоговый преобразователь, приемник разовых команд, формирователь разовых команд, внутреннюю магистраль информационного обмена, трехканальный таймер, мажоритарную схему, при этом вход-выход приемопередатчика магистрального канала информационного обмена является входом-выходом магистрального канала информационного обмена устройства ввода-вывода, контроллер магистрального канала информационного обмена соединен с приемопередатчиком магистрального канала информационного обмена, интерфейсный вход-выход контроллера магистрального канала информационного обмена, интерфейсный вход-выход микроЭВМ, выход данных аналого-цифрового преобразователя, вход кода номера канала мультиплексора, выход данных приемника разовых команд, вход данных формирователя разовых команд соединены между собой при помощи внутренней магистрали информационного обмена, разряды адреса с нулевого по второй внутренней магистрали информационного обмена соединены с соответствующими входами дешифратора, нулевой разряд данных внутренней магистрали информационного обмена соединен с входом данных первого триггера, выход буферного элемента соединен с пятнадцатым разрядом данных внутренней магистрали информационного обмена, сигнал чтения внутренней магистрали информационного обмена соединен с первым разрешающим входом дешифратора, сигнал записи внутренней магистрали информационного обмена соединен с нулевым разрешающим выходом дешифратора, выход последовательного интерфейса микроЭВМ соединен со входом многоканального цифроаналогового преобразователя, выходы которого являются выходами аналоговых сигналов устройства ввода-вывода, первый выход дешифратора соединен с управляющим входом многоканального цифроаналогового преобразователя, второй выход дешифратора соединен со входом сигнала сброса трехканального таймера, третий выход дешифратора соединен со входом синхронизации первого триггера, выход первого триггера соединен с входом сигнала разрешения счета трехканального таймера, четвертый выход дешифратора соединен с управляющим входом формирователя разовых команд, пятый выход дешифратора соединен с управляющим входом приемника разовых команд, шестой выход дешифратора соединен с управляющим входом мультиплексора, седьмой выход дешифратора соединен со входом сигнала запуска аналого-цифрового преобразователя, восьмой выход дешифратора соединен с управляющим входом аналого-цифрового преобразователя, выход мультиплексора соединен со входом аналогового сигнала аналого-цифрового преобразователя, первый, второй, третий выходы трехканального таймера соединены соответственно с первым, вторым, третьим входами мажоритарной схемы, выход которой является выходом сигнала таймера устройства ввода-вывода, выход сигнала готовности аналого-цифрового преобразователя соединен со входом синхронизации второго триггера, входы мультиплексора являются входами аналоговых сигналов устройства ввода-вывода, входы приемника разовых команд являются входами разовых команд устройства ввода-вывода, выходы формирователя разовых команд являются выходами разовых команд устройства ввода-вывода, седьмой выход дешифратора соединен со входом сброса второго триггера, вход данных которого подключен к источнику сигнала логической единицы, восьмой выход дешифратора соединен с разрешающим входом буферного элемента, выход второго триггера соединен со входом данных буферного элемента,

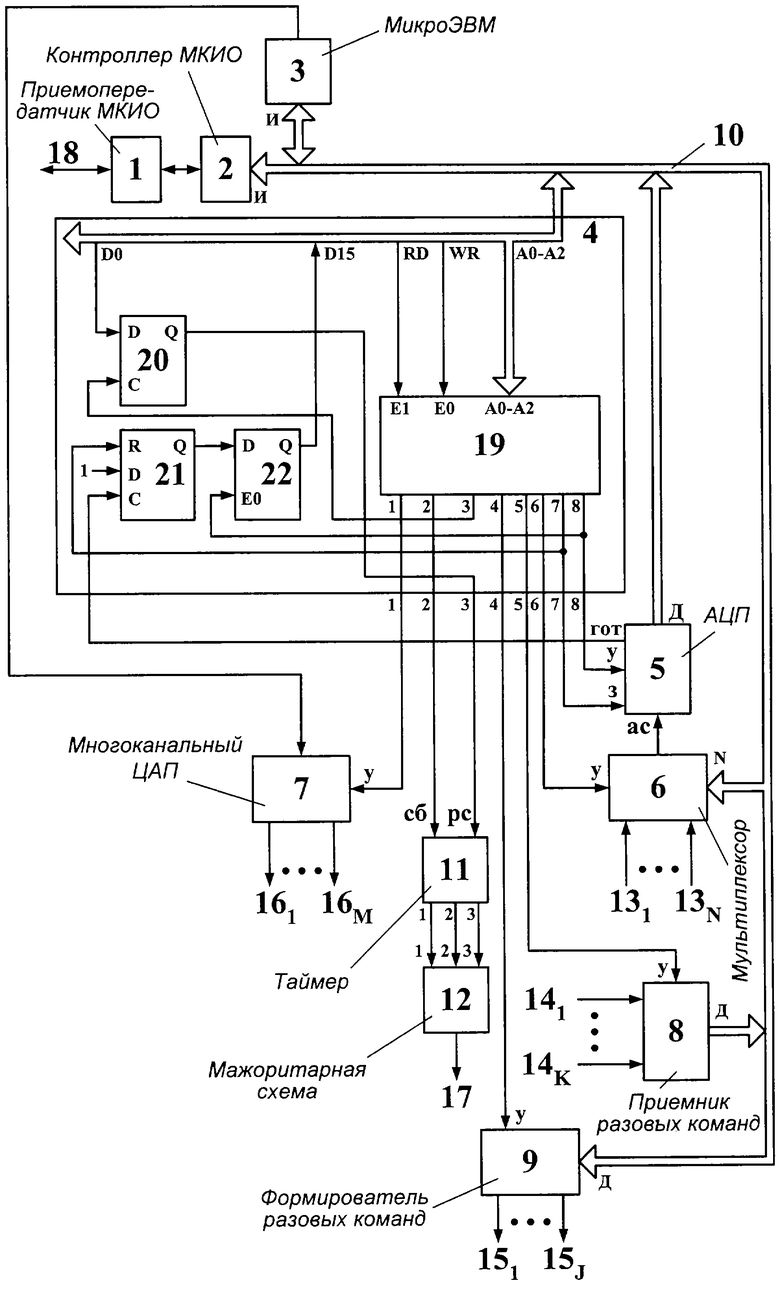

Сущность изобретения поясняется чертежом, на котором обозначены:

1 - приемопередатчик магистрального канала информационного обмена (МКИО),

2 - контроллер МКИО,

3 - микроЭВМ (ЭВМ - электронно-вычислительная машина),

4 - устройство управления (УУ),

5 - аналого-цифровой преобразователь (АЦП),

6 - мультиплексор,

7 - многоканальный цифроаналоговый преобразователь (ЦАП),

8 - приемник разовых команд,

9 - формирователь разовых команд,

10 - внутренняя магистраль информационного обмена,

11 - трехканальный таймер,

12 - мажоритарная схема,

131 - первый вход аналогового сигнала;

13N - N-й вход аналогового сигнала;

141 - первый вход разовых команд;

14к - К-й вход разовых команд;

151 - первый выход разовых команд;

15J - J-й выход разовых команд;

161 - первый выход аналогового сигнала;

16м - М-й выход аналогового сигнала;

17 - выход сигнала таймера;

18 - вход-выход магистрального канала информационного обмена;

19 - дешифратор;

20 - первый триггер;

21 - второй триггер;

22 - буферный элемент.

При этом вход-выход приемопередатчика 1 магистрального канала информационного обмена является входом-выходом 18 магистрального канала информационного обмена устройства ввода-вывода, контроллер 2 магистрального канала информационного обмена соединен с приемопередатчиком 1 магистрального канала информационного обмена.

Дешифратор 19, первый и второй триггеры 20 и 21, буферный элемент 22 образуют устройство 4 управления, первый, второй, четвертый, пятый, шестой, седьмой и восьмой выходы дешифратора 19 являются соответственно первым, вторым, четвертым, пятым, шестым, седьмым и восьмым выходами устройства 4 управления, выход первого триггера 20 является третьим выходом устройства 4 управления, вход сигнала синхронизации (С) второго триггера 21 является входом устройства 4 управления, седьмой выход дешифратора 19 соединен со входом сброса (R) второго триггера 21, вход данных которого подключен к источнику сигнала логической единицы, восьмой выход дешифратора 19 соединен с разрешающим входом (Е0) буферного элемента 22, выход второго триггера 21 соединен со входом данных (D) буферного элемента 22, разряды адреса с нулевого по второй (А0-А2) внутренней магистрали 10 информационного обмена соединены с соответствующими входами дешифратора 19, нулевой разряд данных (D0) внутренней магистрали 10 информационного обмена соединен с входом данных первого триггера 20, выход буферного элемента 22 соединен с пятнадцатым разрядом данных (D15) внутренней магистрали 10 информационного обмена, сигнал чтения (RD) внутренней магистрали 10 информационного обмена соединен с первым разрешающим входом (Е1) дешифратора 19, сигнал записи (WR) внутренней магистрали 10 информационного обмена соединен с нулевым разрешающим входом (Е0) дешифратора 19, третий выход дешифратора 19 соединен со входом синхронизации (С) первого триггера 20.

Интерфейсный вход-выход (И) контроллера 2 магистрального канала информационного обмена, интерфейсный вход-выход (И) микроЭВМ 3, вход-выход устройства 4 управления, выход данных (Д) аналого-цифрового преобразователя 5, вход кода номера канала (N) мультиплексора 6, выход данных (Д) приемника 8 разовых команд, вход данных (Д) формирователя 9 разовых команд соединены между собой при помощи внутренней магистрали 10 информационного обмена.

Выход последовательного интерфейса микроЭВМ 3 соединен со входом многоканального цифроаналогового преобразователя 7, выходы которого являются выходами 161, . ..,16М с первого по М-й аналоговых сигналов устройства ввода-вывода, первый выход устройства 4 управления соединен с управляющим входом (У) многоканального цифроаналогового преобразователя 7, второй выход устройства 4 управления соединен со входом сигнала сброса (сб) трехканального таймера 11, третий выход устройства 4 управления соединен с входом сигнала разрешения счета (рс) трехканального таймера 11, четвертый выход устройства 4 управления соединен с управляющим входом (У) формирователя 9 разовых команд, пятый выход устройства 4 управления соединен с управляющим входом (У) приемника 8 разовых команд, шестой выход устройства 4 управления соединен с управляющим входом (У) мультиплексора 6, седьмой выход устройства 4 управления соединен со входом сигнала запуска (3) аналого-цифрового преобразователя 5, восьмой выход устройства 4 управления соединен с управляющим входом (У) аналого-цифрового преобразователя 5.

Выход мультиплексора 6 соединен с входом аналогового сигнала (ас) аналого-цифрового преобразователя 5, первый, второй, третий выходы трехканального таймера 11 соединены соответственно с первым, вторым, третьим входами мажоритарной схемы 12, выход которой является выходом 17 сигнала таймера устройства ввода-вывода.

Выход сигнала готовности (гот) аналого-цифрового преобразователя 5 соединен со входом устройства 4 управления. Входы мультиплексора 6 являются входами 131,...,13N с первого по N-й аналоговых сигналов устройства ввода-вывода, входы приемника 8 разовых команд являются входами 141,...,14К с первого по К-й разовых команд устройства ввода-вывода, выходы формирователя 9 разовых команд являются выходами 151,..., 15J с первого по J-й разовых команд устройства ввода-вывода.

Контроллер 2 магистрального канала информационного обмена обеспечивает обмен по магистральному каналу информационного обмена в режиме оконечного устройства.

Трехканальный таймер 11 и мажоритарная схема 12 служат для выдачи на выход 17 сигнала таймера сигнала по прошествии заданного промежутка времени. Трехканальный таймер 11 представляет собой три идентичных канала. Мажоритарная схема 12 служит для обеспечения работоспособности в случае отказа одного из каналов трехканального таймера 11.

Буферный элемент 22 представляет собой логическую схему, сигнал на выходе Q которой повторяет сигнал на входе D данных при наличии управляющего сигнала на разрешающем входе Е0 и не зависит от сигнала на входе D данных при отсутствии сигнала на разрешающем входе Е0 [переходит в третье (отключенное) состояние].

Приемник 8 разовых команд может представлять собой, например, набор (блок) буферных элементов, аналогичных буферному элементу 22. В таком блоке разрешающий вход Е0 буферных элементов соединен с управляющим У входом приемника 8 разовых команд, а их выходы образуют выход Д данных приемника 8. На входах буферных элементов, образующих приемник 8, при необходимости могут быть установлены ограничители уровня входных сигналов и тому подобные устройства, согласующие уровни сигналов на входах буферных элементов с необходимым уровнем сигналов.

Формирователь 9 разовых команд может представлять собой, например, регистр, информационные входы которого подключены к входу Д данных формирователя 9, входы записи соединены с его управляющим У входом, а выходы регистра образуют выходы формирователя 9. Кроме этого, на выходах регистра могут быть установлены усилители, обеспечивающие необходимый уровень напряжения и мощность выходного сигнала.

Остальные блоки предлагаемого устройства широко известны.

Обмен данными устройства ввода-вывода и вычислительной системы, использующей данное устройство, осуществляется по магистральному каналу информационного обмена в соответствии с ГОСТ 26765.52-87. При этом устройство ввода-вывода работает в режиме оконечного устройства.

Предлагаемое устройство ввода-вывода работает следующим образом.

По магистральному каналу информационного обмена на вход-выход 18 магистрального канала информационного обмена устройства ввода-вывода поступают команды и данные, которые через приемопередатчик 1 магистрального канала информационного обмена поступают в контроллер 2 магистрального канала информационного обмена, который преобразует их из последовательного в параллельный код и передает по внутренней магистрали 10 информационного обмена в микроЭВМ 3. Контроллер 2 магистрального канала информационного обмена реализует протокол обмена по магистральному каналу информационного обмена в режиме оконечного устройства.

Вывод аналоговых сигналов производится следующим образом.

МикроЭВМ 3 в соответствии с полученными командами передает полученные данные по последовательному каналу в многоканальный цифроаналоговый преобразователь 7. Далее микроЭВМ 3 выставляет на внутренней магистрали 10 информационного обмена адрес, соответствующий многоканальному цифроаналоговому преобразователю 7, и дешифратор 19 через свой первый выход выдает управляющий сигнал на многоканальный цифроаналоговый преобразователь 7. При получении этого сигнала на свой управляющий вход (У) многоканальный цифроаналоговый преобразователь 7 изменяет сигналы на своих выходах в соответствии с загруженными в него по последовательному интерфейсу данными. Эти сигналы через выходы 161,...,16М с первого по М-й аналоговых сигналов поступают во внешние устройства.

Ввод аналоговых сигналов производится следующим образом.

МикроЭВМ 3 выставляет на линиях адреса внутренней магистрали 10 информационного обмена адрес, соответствующий мультиплексору 6, и выставляет на линиях данных внутренней магистрали 10 информационного обмена номер канала. Дешифратор 19 выдает через шестой выход управляющий сигнал на мультиплексор 6. Номер канала с внутренней магистрали 10 записывается в мультиплексор 6, который подключает ко входу аналого-цифрового преобразователя 5 один из входов 131, . ..,13N с первого по N-й аналоговых сигналов. Далее микроЭВМ 3 выставляет на внутренней магистрали 10 информационного обмена адрес, соответствующий входу запуска (З) аналого-цифрового преобразователя 5. Дешифратор 19 через свой седьмой выход выдает сигнал на вход запуска аналого-цифрового преобразователя 5, который начинает преобразование. Сигнал с седьмого выхода дешифратора 19 также поступает на вход сброса (R) второго триггера 21 и сбрасывает его в нулевое состояние. По окончании преобразования аналого-цифровой преобразователь 5 выдает сигнал готовности, который с выхода сигнала готовности (гот) цифроаналогового преобразователя 5 поступает на вход синхронизации (С) второго триггера 21. Во второй триггер 21 записывается значение единицы. МикроЭВМ 3 контролирует состояние второго триггера 21. Для этого микроЭВМ 3 выставляет на внутренней магистрали 10 такой адрес, при котором дешифратор 19 выдает сигнал на свой восьмой выход, который поступает на разрешающий вход (Е0) буферного элемента 22. Данные из второго триггера 21 через буферный элемент 22 выдаются в пятнадцатый разряд данных (D15) внутренней магистрали 10. По окончании преобразования микроЭВМ 3 производит чтение данных из аналого-цифрового преобразователя 5. Для этого микроЭВМ 3 выставляет на внутреннюю магистраль 10 информационного обмена сигналы адреса, соответствующие регистру данных аналого-цифрового преобразователя 5, и дешифратор 19 через свой восьмой выход выдает сигнал на управляющий вход (У) аналого-цифрового преобразователя 5. По этому сигналу результаты преобразования из аналого-цифрового преобразователя 5 поступают по внутренней магистрали 10 информационного обмена в микроЭВМ 3, далее в контроллер 2 магистрального канала информационного обмена и при помощи приемопередатчика 1 мультиплексного канала информационного обмена через вход-выход 18 магистрального канала информационного обмена выдаются в магистральный канал информационного обмена.

Ввод разовых команд (дискретных сигналов) производится следующим образом. Разовые команды поступают через входы 141,...,14К с первого по К-й разовых команд на входы приемника 8 разовых команд. МикроЭВМ 3 выставляет на внутреннюю магистраль 10 информационного обмена адрес, соответствующий приемнику 8 разовых команд, и дешифратор 19 через свой пятый выход выдает сигнал на управляющий вход (У) приемника 8 разовых команд. По этому сигналу принятые данные из приемника 8 разовых команд поступают по внутренней магистрали 10 информационного обмена в микроЭВМ 3, далее в контроллер 2 магистрального канала информационного обмена и при помощи приемопередатчика 1 через вход-выход 18 магистрального канала информационного обмена выдаются в магистральный канал информационного обмена.

Вывод разовых команд (дискретных сигналов) производится следующим образом.

МикроЭВМ 3 в соответствии с полученными командами выставляет на внутреннюю магистраль 10 информационного обмена данные для формирователя 9 разовых команд и адрес, соответствующий формирователю 9 разовых команд. Дешифратор 19 через свой четвертый выход выдает сигнал на управляющий вход (У) формирователя 9 разовых команд, который по этому сигналу принимает данные с внутренней магистрали 10 информационного обмена и далее выдает разовые команды на свои выходы и на соответствующие выходы 151,...,15J с первого по J-й разовых команд.

В случае, если на вход разрешения счета (рс) трехканального таймера 11 с третьего выхода устройства 4 управления подается соответствующий сигнал, в каждом из каналов трехканального таймера 11 производится обратный отсчет. По прошествии заданного промежутка времени выдаются сигналы на первый, второй и третий выходы трехканального таймера, которые поступают на соответствующие входы мажоритарной схемы 12. Мажоритарная схема 12 выдает соответствующий сигнал на свой выход и, соответственно, на выход 17 сигнала таймера устройства ввода-вывода при условии наличия сигналов на, как минимум, двух ее входах. Трехканальный таймер 11 может быть переведен в исходное состояние путем подачи соответствующего сигнала на его вход сигнала сброса (сб). Для этого микроЭВМ 3 выставляет на внутренней магистрали 10 информационного обмена адрес, соответствующий трехканальному таймеру 11. Дешифратор 19 выдает соответствующий сигнал через свой второй выход. Для управления сигналом разрешения счета (рс) микроЭВМ 3 выставляет на внутренней магистрали 10 адрес, при котором дешифратор 19 выдает сигнал на свой третий выход, также микроЭВМ 3 в нулевом разряде данных (D0) внутренней магистрали 10 - признак разрешения счета. Сигнал с третьего выхода дешифратора 19 поступает на сход синхронизации (С) первого триггера 20. Признак разрешения счета из нулевого разряда данных (D0) внутренней магистрали 19 записывается в первый триггер 20 и с его выхода поступает на вход разрешения счета (рс) трехканального таймера 11.

Таким образом, предлагаемое устройство обеспечивает ввод-вывод аналоговых сигналов и сигналов разовых команд (дискретных сигналов) и надежное формирование команды через заданный интервал (интервалы) времени.

Представленные чертеж и описание предлагаемого изобретения позволяют, используя существующую элементную базу, изготовить ее промышленным способом и использовать в системах сбора и обработки информации, а также в системах управления для сопряжения различных вычислительных систем с исполнительными устройствами и датчиками, что характеризует предлагаемое изобретение как промышленно применимое.

Источники информации

1. А.С. СССР 1532937, кл. G 06 F 13/00, 1990.

2. А.С. СССР 1564606, кл. G 06 F 3/00, 1990.

3. Свидет. РФ 18002, кл. G 06 F 3/00, 2001.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2012 |

|

RU2524852C2 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО ВВОДА-ВЫВОДА | 2023 |

|

RU2816245C1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| НАВИГАЦИОННЫЙ КОМПЛЕКС ЛЕТАТЕЛЬНОГО АППАРАТА | 2000 |

|

RU2170409C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

Изобретение относится к области обработки аналоговых и дискретных сигналов и может быть использовано для сопряжения различных вычислительных систем с исполнительными устройствами и датчиками, использующими как аналоговые сигналы, так и разовые команды. Техническим результатом является создание устройства ввода-вывода, обеспечивающего наряду с вводом-выводом аналоговых сигналов ввод-вывод сигналов разовых команд и надежное формирование команды через заданный интервал (интервалы) времени. Для этого устройство ввода-вывода содержит приемопередатчик магистрального канала информационного обмена, контроллер магистрального канала информационного обмена, микроЭВМ, дешифратор, первый триггер, второй триггер, буферный элемент, аналого-цифровой преобразователь, мультиплексор, многоканальный цифроаналоговый преобразователь, приемник разовых команд, формирователь разовых команд, внутреннюю магистраль информационного обмена, трехканальный таймер и мажоритарную схему, объединенные соответствующими связями. 1 ил.

Устройство ввода-вывода, характеризующееся тем, что оно содержит приемопередатчик магистрального канала информационного обмена, контроллер магистрального канала информационного обмена, микроЭВМ, дешифратор, первый триггер, второй триггер, буферный элемент, аналого-цифровой преобразователь, мультиплексор, многоканальный цифроаналоговый преобразователь, приемник разовых команд, формирователь разовых команд, внутреннюю магистраль информационного обмена, трехканальный таймер, мажоритарную схему, при этом вход-выход приемопередатчика магистрального канала информационного обмена является входом-выходом магистрального канала информационного обмена устройства ввода-вывода, контроллер магистрального канала информационного обмена соединен с приемопередатчиком магистрального канала информационного обмена, интерфейсный вход-выход контроллера магистрального канала информационного обмена, интерфейсный вход-выход микроЭВМ, выход данных аналого-цифрового преобразователя, вход кода номера канала мультиплексора, выход данных приемника разовых команд, вход данных формирователя разовых команд соединены между собой при помощи внутренней магистрали информационного обмена, разряды адреса с нулевого по второй внутренней магистрали информационного обмена соединены с соответствующими входами дешифратора, нулевой разряд данных внутренней магистрали информационного обмена соединен с входом данных первого триггера, выход буферного элемента соединен с пятнадцатым разрядом данных внутренней магистрали информационного обмена, сигнал чтения внутренней магистрали информационного обмена соединен с первым разрешающим входом дешифратора, сигнал записи внутренней магистрали информационного обмена соединен с нулевым разрешающим выходом дешифратора, выход последовательного интерфейса микроЭВМ соединен со входом многоканального цифроаналогового преобразователя, выходы которого являются выходами аналоговых сигналов устройства ввода-вывода, первый выход дешифратора соединен с управляющим входом многоканального цифроаналогового преобразователя, второй выход дешифратора соединен со входом сигнала сброса трехканального таймера, третий выход дешифратора соединен со входом синхронизации первого триггера, выход первого триггера соединен с входом синхронизации первого триггера, выход первого триггера соединен с входом сигнала разрешения счета трехканального таймера, четвертый выход дешифратора соединен с управляющим входом формирователя разовых команд, пятый выход дешифратора соединен с управляющим входом приемника разовых команд, шестой выход дешифратора соединен управляющим входом мультиплексора, седьмой выход дешифратора соединен со входом сигнала запуска аналого-цифрового преобразователя, восьмой выход дешифратора соединен с управляющим входом аналого-цифрового преобразователя, выход мультиплексора соединен со входом аналогового сигнала аналого-цифрового преобразователя, первый, второй, третий выходы трехканального таймера соединены соответственно с первым, вторым, третьим входами мажоритарной схемы, выход которой является выходом сигнала таймера устройства ввод-вывода, выход сигнала готовности аналого-цифрового преобразователя соединен со входом синхронизации второго триггера, входы мультиплексора являются входами аналоговых сигналов устройства ввода-вывода, входы приемника разовых команд являются входами разовых команд устройства ввода-вывода, выходы формирователя разовых команд являются выходами разовых команд устройства ввода-вывода, седьмой выход дешифратора соединен со входом сброса второго триггера, вход данных которого подключен к источнику сигнала логической единицы, восьмой выход дешифратора соединен с разрешающим входом буферного элемента, выход второго триггера соединен со входом данных буферного элемента.

| Машина для фарширования овощей | 1928 |

|

SU18002A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| УСТРОЙСТВО ДЛЯ СБОРА, РЕГИСТРАЦИИ И СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1996 |

|

RU2115163C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2017203C1 |

| US 5099444 А, 25.08.1992 | |||

| US 5072375 А, 10.12.1991. | |||

Авторы

Даты

2004-01-10—Публикация

2002-05-24—Подача