Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем.

Наиболее близким известным аналогом, принятым в качестве прототипа предлагаемого изобретения, является адаптер мультиплексных каналов информационного обмена [1, стр. 242-243, рис. 6.17,б], содержащий первый контроллер мультиплексных каналов информационного обмена (адаптер канала), первый приемопередатчик мультиплексного канала информационного обмена (образованный формирователем трансформаторной линии и оконечным усилителем), первый трансформатор гальванической развязки, при этом вход-выход (образованный выходами сигналов DO0, DO1 и входами сигналов MR, DI0, DI1) первого контроллера мультиплексных каналов информационного обмена соединены с первым входом-выходом (образованного входами сигналов DO0, DO1 и выходами сигналов MR, DI0, DI1) первого приемопередатчика мультиплексного канала информационного обмена, второй вход-выход первого приемопередатчика мультиплексного канала информационного обмена соединен с входом-выходом первого трансформатора гальванической развязки, выход которого является выходом первого мультиплексного канала информационного обмена адаптера мультиплексных каналов информационного обмена.

Недостатком прототипа является снижение производительности вычислительной системы, использующей данный адаптер из-за необходимости программно реализовывать протокол обмена по мультиплексным каналам информационного обмена, а также невозможность определения состояния исправности адаптера.

Задачей изобретения является повышение производительности вычислительной системы, использующей адаптер мультиплексных каналов информационного обмена, а также повышение ее отказоустойчивости.

Сущность изобретения заключается в том, что адаптер мультиплексных каналов информационного обмена содержит первый контроллер мультиплексных каналов информационного обмена, первый приемопередатчик мультиплексного канала информационного обмена, первый трансформатор гальванической развязки, второй приемопередатчик мультиплексного канала информационного обмена, второй трансформатор гальванической развязки, первый микропроцессор, первое оперативное запоминающее устройство, первое постоянное запоминающее устройство, первый контроллер внешней интерфейсной магистрали информационного обмена, первый формирователь выходных разовых команд, первый приемник входных разовых команд, второй контроллер мультиплексных каналов информационного обмена, третий приемопередатчик мультиплексного канала информационного обмена, третий трансформатор гальванической развязки, четвертый приемопередатчик мультиплексного канала информационного обмена, четвертый трансформатор гальванической развязки, второй микропроцессор, второе оперативное запоминающее устройство, второе постоянное запоминающее устройство, второй контроллер внешней интерфейсной магистрали информационного обмена, второй формирователь выходных разовых команд, второй приемник входных разовых команд, формирователь сигнала сброса, формирователь сигнала исправности, буферный формирователь, первую внутреннюю интерфейсную магистраль информационного обмена, вторую внутреннюю интерфейсную магистраль информационного обмена, устройство ввода сигнала ручного сброса с соответствующими связями.

Кроме этого, в предлагаемом адаптере мультиплексных каналов информационного обмена:

первый и второй контроллеры мультиплексных каналов информационного обмена выполнены с использованием микросхемы программируемой логики;

первое и второе постоянные запоминающие устройства каналов выполнены с использованием элементов электроперепрограммируемой энергонезависимой памяти;

первый и второй контроллеры внешней интерфейсной магистрали информационного обмена выполнены с использованием микросхемы программируемой логики.

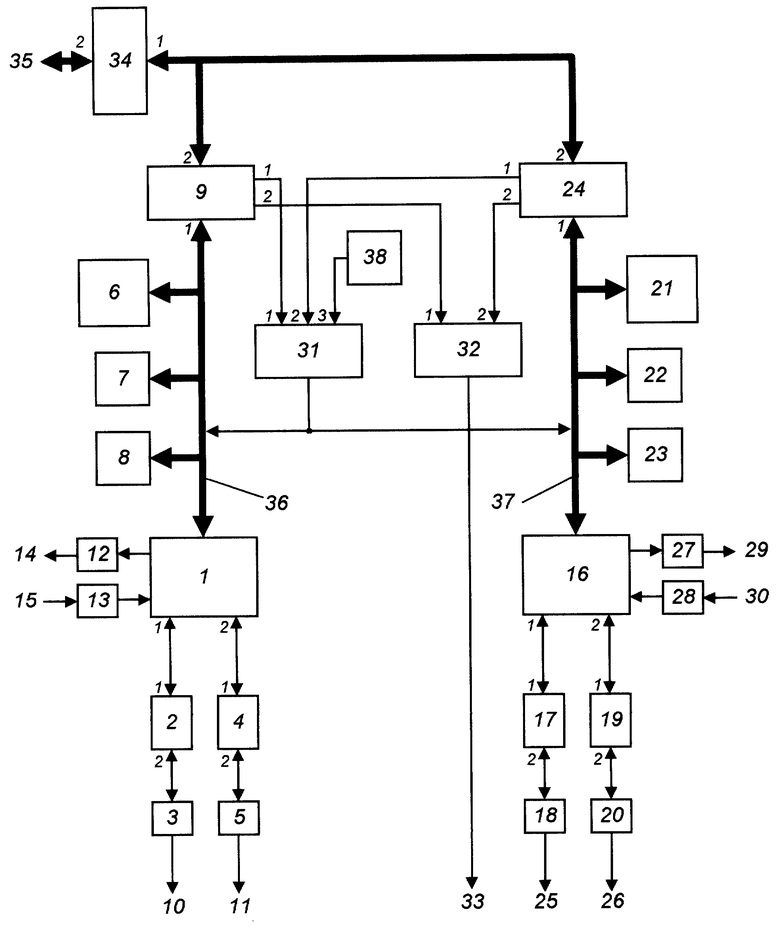

Сущность изобретения поясняется чертежом, на котором обозначены:

1 - первый контроллер мультиплексных каналов информационного обмена;

2 - первый приемопередатчик мультиплексного канала информационного обмена;

3 - первый трансформатор гальванической развязки;

4 - второй приемопередатчик мультиплексного канала информационного обмена;

5 - второй трансформатор гальванической развязки;

6 - первый микропроцессор;

7 - первое оперативное запоминающее устройство;

8 - первое постоянное запоминающее устройство;

9 - первый контроллер внешней интерфейсной магистрали информационного обмена;

10 - вход-выход первого мультиплексного канала информационного обмена;

11 - вход-выход второго мультиплексного канала информационного обмена;

12 - первый формирователь выходных разовых команд;

13 - первый приемник входных разовых команд;

14 - первый выход разовых команд;

15 - первый вход разовых команд;

16 - второй контроллер мультиплексных каналов информационного обмена;

17 - третий приемопередатчик мультиплексного канала информационного обмена;

18 - третий трансформатор гальванической развязки;

19 - четвертый приемопередатчик мультиплексного канала информационного обмена;

20 - четвертый трансформатор гальванической развязки;

21 - второй микропроцессор;

22 - второе оперативное запоминающее устройство;

23 - второе постоянное запоминающее устройство;

24 - второй контроллер внешней интерфейсной магистрали информационного обмена;

25 - вход-выход третьего мультиплексного канала информационного обмена;

26 - вход-выход четвертого мультиплексного канала информационного обмена;

27 - второй формирователь выходных разовых команд;

28 - второй приемник входных разовых команд;

29 - второй выход разовых команд;

30 - второй вход разовых команд;

31 - формирователь сигнала сброса;

32 - формирователь сигнала исправности;

33 - выход сигнала исправности;

34 - буферный формирователь;

35 - вход-выход внешней интерфейсной магистрали информационного обмена;

36 - первая внутренняя интерфейсная магистраль информационного обмена;

37 - вторая внутренняя интерфейсная магистраль информационного обмена;

38 - устройство ввода сигнала ручного сброса.

В предлагаемом адаптере мультиплексных каналов информационного обмена первый вход-выход первого контроллера 1 мультиплексных каналов информационного обмена соединен с первым входом-выходом первого приемопередатчика 2 мультиплексного канала информационного обмена, второй вход-выход первого контроллера 1 мультиплексных каналов информационного обмена соединен с первым входом-выходом второго приемопередатчика 4 мультиплексного канала информационного обмена, вторые входы-выходы первого и второго приемопередатчиков 2 и 4 мультиплексных каналов информационного обмена соединены соответственно с первым и вторым трансформаторами 3 и 5 гальванической развязки, выходы которых являются соответственно выходами 10 и 11 первого и второго мультиплексных каналов информационного обмена адаптера мультиплексных каналов информационного обмена.

Интерфейсные входы-выходы первого контроллера 1 мультиплексных каналов информационного обмена, первого микропроцессора 6, первого оперативного запоминающего устройства 7, первого постоянного запоминающего устройства 8, а также первый интерфейсный вход-выход первого контроллера 9 внешней интерфейсной магистрали информационного обмена соединены между собой при помощи первой внутренней интерфейсной магистрали 36 информационного обмена.

Выход разовых команд первого контроллера 1 мультиплексных каналов информационного обмена соединен с входом первого формирователя 12 выходных разовых команд, выход которого является первым выходом 14 разовых команд адаптера мультиплексных каналов информационного обмена, вход разовых команд первого контроллера 1 мультиплексных каналов информационного обмена соединен с выходом первого приемника 13 входных разовых команд, вход которого является первым входом 15 разовых команд адаптера мультиплексных каналов информационного обмена.

Второй интерфейсный вход-выход первого контроллера 9 внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя 34, второй вход-выход которого является входом-выходом 35 внешней интерфейсной магистрали информационного обмена адаптера мультиплексных каналов информационного обмена. При помощи входа-выхода 35 внешней интерфейсной магистрали информационного обмена адаптер мультиплексных каналов информационного обмена подключается к интерфейсной магистрали информационного обмена вычислительной системы, в составе которой используется адаптер мультиплексных каналов информационного обмена.

Первый вход-выход второго контроллера 16 мультиплексных каналов информационного обмена соединен с первым входом-выходом третьего приемопередатчика 17 мультиплексного канала информационного обмена, второй вход-выход второго контроллера 16 мультиплексных каналов информационного обмена соединен с первым входом-выходом четвертого приемопередатчика 19 мультиплексного канала информационного обмена, вторые входы-выходы третьего и четвертого приемопередатчиков 17 и 19 мультиплексных каналов информационного обмена соединены соответственно с третьим и четвертым трансформаторами 18 и 20 гальванической развязки, выходы которых являются соответственно выходами 25 и 26 третьего и четвертого мультиплексных каналов информационного обмена адаптера мультиплексных каналов информационного обмена.

Интерфейсные входы-выходы второго контроллера 16 мультиплексных каналов информационного обмена, второго микропроцессора 21, второго оперативного запоминающего устройства 22, второго постоянного запоминающего устройства 23, а также первый интерфейсный вход-выход второго контроллера 24 внешней интерфейсной магистрали информационного обмена соединены между собой при помощи второй внутренней интерфейсной магистрали 37 информационного обмена.

Выход разовых команд второго контроллера 16 мультиплексных каналов информационного обмена соединен со входом второго формирователя 27 выходных разовых команд, выход которого является вторым выходом 29 разовых команд адаптера мультиплексных каналов информационного обмена, вход разовых команд второго контроллера 16 мультиплексных каналов информационного обмена соединен с выходом второго приемника 28 входных разовых команд, вход которого является вторым входом 30 разовых команд адаптера мультиплексных каналов информационного обмена.

Второй интерфейсный вход-выход второго контроллера 24 внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя 34.

Первый выход первого контроллера 9 внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя 31 сигнала сброса, первый выход второго контроллера 24 внешней интерфейсной магистрали информационного обмена соединен со вторым входом формирователя 31 сигнала сброса, выход устройства 38 ввода сигнала ручного сброса соединен с третьим входом формирователя 31 сигнала сброса, выход формирователя 31 сигнала сброса соединен с первой и второй внутренними интерфейсными магистралями 36 и 37 информационного обмена.

Второй выход первого контроллера 9 внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя 32 сигнала исправности, второй выход второго контроллера 24 внешней интерфейсной магистрали информационного обмена соединен со вторым входом формирователя 32 сигнала исправности, выход формирователя 32 сигнала исправности является выходом 33 сигнала исправности адаптера мультиплексных каналов информационного обмена.

Первый контроллер 1 мультиплексных каналов информационного обмена обеспечивает со стороны первого и второго мультиплексных каналов информационного обмена прием слов в формате, соответствующем ГОСТ 26765.52-87 с контролем фазы синхросигнала и бита четности, формирование соответствующих признаков и предварительную дешифрацию командных слов мультиплексных каналов информационного обмена, выдачу слов в формате, соответствующем ГОСТ 26765.52-87 с формированием соответствующего синхросигнала и бита четности, формирование сигналов управления передатчиками мультиплексных каналов информационного обмена, а также со стороны первой внутренней интерфейсной магистрали 36 информационного обмена считывание принятых по мультиплексному каналу информационного обмена данных и признаков дешифрации, запись и хранение адреса оконечного устройства мультиплексных каналов информационного обмена, запись командных слов и слов данных для выдачи в первый и второй мультиплексные каналы информационного обмена.

Второй контроллер 16 мультиплексных каналов информационного обмена обеспечивает со стороны третьего и четвертого мультиплексных каналов информационного обмена прием слов в формате, соответствующем ГОСТ 26765.52-87 с контролем фазы синхросигнала и бита четности, формирование соответствующих признаков и предварительную дешифрацию командных слов мультиплексных каналов информационного обмена, выдачу слов в формате, соответствующем ГОСТ 26765.52-87 с формированием соответствующего синхросигнала и бита четности, формирование сигналов управления передатчиками мультиплексных каналов информационного обмена, а также со стороны второй внутренней интерфейсной магистрали 37 информационного обмена считывание принятых по мультиплексному каналу информационного обмена данных и признаков дешифрации, запись и хранение адреса оконечного устройства мультиплексных каналов информационного обмена, запись командных слов и слов данных для выдачи в третий и четвертый мультиплексные каналы информационного обмена.

Первый контроллер 1 мультиплексных каналов информационного обмена дополнительно содержит регистр для хранения 8-ми выходных разовых команд, а также содержит вход входных разовых команд данных с 8-разрядного приемника входных разовых команд.

Схемы приема первого, второго, третьего и четвертого приемопередатчиков 2, 4, 17 и 19 мультиплексных каналов информационного обмена подключены к отдельным обмоткам соответственно первого, второго, третьего и четвертого трансформаторов 3, 5, 18 и 20 гальванической развязки и выполнены на сдвоенном компараторе с использованием низкочастотного фильтра.

Первый и второй приемники 13 и 28 входных разовых команд выполнены на компараторах и обеспечивают прием разовых команд поступающих в виде сигнала "ключ на корпус/разрыв". Входная цепь каждого разряда входных разовых команд содержит резистор привязки к напряжению питания адаптера мультиплексных каналов информационного обмена и защитный диод, обеспечивающий прием входных сигналов напряжением до 27 В. С выхода компараторов сигналы разовых команд через соответственно первый и второй контроллеры 1 и 16 мультиплексных каналов информационного обмена считываются соответственно первым и вторым микропроцессорами 6 и 21 и доступны по чтению через соответствующий порт ввода-вывода внешней интерфейсной магистрали информационного обмена при помощи первого и второго контроллеров 9 и 24 внешней интерфейсной магистрали информационного обмена.

Первый микропроцессор 6 исполняет для первого и второго мультиплексных каналов информационного обмена программу контроллера канала или оконечного устройства, расположенную в первом постоянном запоминающем устройстве 8. Первое оперативное запоминающее устройство 7 используется в процессе исполнения этой программы для хранения данных и взаимодействия по внешней интерфейсной магистрали информационного обмена. Логическое сопряжение первой внутренней интерфейсной магистрали 36 информационного обмена с внешней интерфейсной магистралью информационного обмена обеспечивает первый контроллер 9 внешней интерфейсной магистрали информационного обмена. Первый контроллер 9 внешней интерфейсной магистрали информационного обмена обеспечивает доступ по внешней интерфейсной магистрали информационного обмена к первому оперативному запоминающему устройству 7 в режиме прямого доступа к памяти.

Второй микропроцессор 21 исполняет для третьего и четвертого мультиплексных каналов информационного обмена программу контроллера канала или оконечного устройства, расположенную во втором постоянном запоминающем устройстве 23. Второе оперативное запоминающее устройство 22 используется в процессе исполнения этой программы для хранения данных и взаимодействия по внешней интерфейсной магистрали информационного обмена. Логическое сопряжение второй внутренней интерфейсной магистрали 37 информационного обмена с внешней интерфейсной магистралью информационного обмена обеспечивает второй контроллер 24 внешней интерфейсной магистрали информационного обмена. Второй контроллер 24 внешней интерфейсной магистрали информационного обмена обеспечивает доступ по внешней интерфейсной магистрали информационного обмена ко второму оперативному запоминающему устройству 22 в режиме прямого доступа к памяти.

Выходные разовые команды, выдаваемые через первый и второй выходы 14 и 29 разовых команд, формируются записью в соответствующий порт ввода-вывода по внешней интерфейсной магистрали информационного обмена и сохраняются в регистре выходных разовых команд соответственно первого и второго контроллеров 1 и 16 мультиплексных каналов информационного обмена. Каждый выход регистров разовых команд первого и второго контроллеров 1 и 16 мультиплексных каналов информационного обмена подключен к схеме формирования выходных разовых команд соответственно первого и второго формирователей 12 и 27 выходных разовых команд.

Схемы формирования выходных разовых команд первого и второго формирователей 12 и 27 выходных разовых команд выполнены на транзисторах с открытым истоком. Выходные разовые команды выдаются в виде сигнала "ключ на корпус/разрыв цепи". В качестве защитного элемента в каждую схему формирования выходных разовых команд установлен резистор.

Формирователь 31 сигнала сброса выдает сигнал сброса на первую и вторую внутренние интерфейсные магистрали 36 и 37 информационного обмена при достижении напряжениями питания рабочих значений или при поступлении сигнала программного сброса с первых выходов первого и второго контроллеров 9 и 24 внешней интерфейсной магистрали информационного обмена.

Формирователь 32 сигнала исправности выдает сигнал исправности через выход 33 сигнала исправности адаптера мультиплексных каналов информационного обмена, если со вторых выходов первого и второго контроллеров 9 и 24 внешней интерфейсной магистрали информационного обмена регулярно поступают программно формируемые сигналы. В случае отсутствия этих сигналов в течение определенного времени формирователь 32 сигнала исправности снимает сигнал исправности.

Буферный формирователь 34 служит для разделения шины 35 и вторых входов первого и второго контроллеров 9 и 24 внешней интерфейсной магистрали информационного обмена. Буферный формирователь 34 включает в себя блок магистральных усилителей, построенных по известным схемам.

Адаптер мультиплексных каналов информационного обмена работает следующим образом.

При достижении напряжениями питания рабочих значений, а также при программном сбросе со стороны устройств, подключенных к внешней интерфейсной магистрали информационного обмена или при ручном сбросе (при помощи устройства 38 ввода сигнала ручного сброса) формирователь 31 сигнала сброса обеспечивает установку всех устройств адаптера мультиплексных каналов информационного обмена в исходное состояние.

По окончании сброса производится программная инициализация адаптера мультиплексных каналов информационного обмена путем записи в соответствующие адреса первого и второго оперативных запоминающих устройств 7 и 22 признаков режима работы.

По каждому из мультиплексных каналов информационного обмена адаптер мультиплексных каналов информационного обмена может функционировать в двух режимах - режиме контроллера канала и режиме оконечного устройства.

В этих режимах устройство обеспечивает исполнение команд управления и обмена данными в соответствии с ГОСТ 26765.52-87.

В режиме контроллера канала адаптер работает следующим образом.

В первое (при работе с первым и вторым мультиплексными каналами информационного обмена) или второе (при работе с третьим и четвертым мультиплексными каналами информационного обмена) оперативное устройство 7 или 22 записываются команды контроллера и данные для передачи по мультиплексным каналам, а также информация о числе команд. Эта информация поступает по внешней интерфейсной магистрали информационного обмена. Получив задание, первый или второй микропроцессор 6 или 21 последовательно выполняет заданные команды контроллера канала и по завершению задания формирует сигнал запроса прерывания на внешней интерфейсной магистрали информационного обмена. Количество команд, исполняемых котроллером канала в одном задании, от 1 до 16.

В режиме оконечного устройства адаптер работает следующим образом.

При поступлении по мультиплексному каналу информационного обмена достоверной команды с адресом оконечного устройства, соответствующему адресу данного оконечного устройства или адресу групповой команды, первый (при работе с первым и вторым мультиплексными каналами информационного обмена) или второй (при работе с третьим и четвертым мультиплексными каналами информационного обмена) контроллер 1 или 16 мультиплексных каналов информационного обмена формирует прерывание соответственно первому или второму микропроцессору 6 или 21, который начинает выполнение этой команды, обеспечивая прием или выдачу данных и контроль формата сообщения в соответствии с ГОСТ 26765.52-87 и по окончании выполнения команд, связанных с обменом данными, формирует сигнал запроса прерывания на внешней интерфейсной магистрали информационного обмена.

Обмен с адаптером мультиплексных каналов информационного обмена по внешней интерфейсной магистрали информационного обмена осуществляется через первый (при работе с первым и вторым мультиплексными каналами информационного обмена) или второй (при работе с третьим и четвертым мультиплексными каналами информационного обмена) контроллер 9 или 24 внешней интерфейсной магистрали информационного обмена, которые обеспечивают прямой доступ соответственно к первому или второму оперативному запоминающем устройству 7 или 22. В адресном пространстве портов ввода-вывода внешней интерфейсной магистрали информационного обмена первому и второму контроллерам 9 и 24 внешней интерфейсной магистрали информационного обмена отведены области из четырех шестнадцатиразрядных портов.

Таким образом, предлагаемое изобретение позволяет повысить производительность вычислительной системы, использующей адаптер мультиплексных каналов информационного обмена путем введения в адаптер первого и второго микропроцессоров и передачи этим микропроцессорам функций, обеспечивающих реализацию протокола информационного обмена по мультиплексным каналам информационного обмена, а также повысить отказоустойчивость вычислительной системы за счет включения в адаптер мультиплексных каналов информационного обмена формирователя сигнала исправности, что позволяет определять состояние исправности адаптера.

Представленные чертежи и описание адаптера мультиплексных каналов информационного обмена позволяют, используя существенную элементную базу, изготовить его промышленным способом и использовать в вычислительных устройствах различного назначения, что характеризует предлагаемое изобретение как промышленно применимое.

Источники информации

1. Микропроцессоры и микроЭВМ в системах автоматического управления: Справочник/С.Т. Хвощ, Н.Н. Варлинский, Е.А. Попов; Под общ. ред. С.Т. Хвоща. - Л.: Машиностроение. Ленингр. отд-ние, 1987. - 640 с.: ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| АДАПТЕР РАДИАЛЬНЫХ КАНАЛОВ ИНФОРМАЦИОННОГО ОБМЕНА | 2000 |

|

RU2159954C1 |

| СПОСОБ ИСПРАВЛЕНИЯ ОШИБОК ПРИ ПЕРЕДАЧЕ ИНФОРМАЦИИ БИИМПУЛЬСНЫМ КОДОМ Манчестер-II И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2566336C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| МНОГОКАНАЛЬНЫЙ АДАПТЕР АНАЛОГОВОГО ВВОДА-ВЫВОДА | 2000 |

|

RU2183857C1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА КОРАБЕЛЬНОГО КОМПЛЕКСА РАДИОЭЛЕКТРОННОГО ПРОТИВОДЕЙСТВИЯ | 2001 |

|

RU2209463C2 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2012 |

|

RU2524852C2 |

| КОМАНДНО-СТРЕЛЬБОВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА БЕРЕГОВОГО БАЗИРОВАНИЯ | 2000 |

|

RU2176818C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ВНУТРИСИСТЕМНОЙ ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ С ВНЕШНИМ МАГИСТРАЛЬНЫМ ПАРАЛЛЕЛЬНЫМ ИНТЕРФЕЙСОМ | 2000 |

|

RU2165640C1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем. Техническим результатом является повышение производительности вычислительной системы, использующей адаптер мультиплексных каналов информационного обмена, а также повышение ее отказоустойчивости. Для этого адаптер мультиплексных каналов информационного обмена содержит контроллеры мультиплексных каналов информационного обмена, приемопередатчики мультиплексного канала информационного обмена, трансформаторы гальванической развязки, микропроцессоры, оперативные запоминающие устройства, постоянные запоминающие устройства, формирователи выходных разовых команд, приемники входных разовых команд, формирователь сигнала сброса, формирователь сигнала исправности, буферный формирователь, внутренние интерфейсные магистрали информационного обмена, устройство ввода сигнала ручного сброса. 1 ил.

Адаптер мультиплексных каналов информационного обмена, содержащий первый контроллер мультиплексных каналов информационного обмена, первый приемопередатчик мультиплексного канала информационного обмена, первый трансформатор гальванической развязки, отличающийся тем, что дополнительно содержит второй приемопередатчик мультиплексного канала информационного обмена, второй трансформатор гальванической развязки, первый микропроцессор, первое оперативное запоминающее устройство, первое постоянное запоминающее устройство, первый контроллер внешней интерфейсной магистрали информационного обмена, первый формирователь выходных разовых команд, первый приемник входных разовых команд, второй контроллер мультиплексных каналов информационного обмена, третий приемопередатчик мультиплексного канала информационного обмена, третий трансформатор гальванической развязки, четвертый приемопередатчик мультиплексного канала информационного обмена, четвертый трансформатор гальванической развязки, второй микропроцессор, второе оперативное запоминающее устройство, второе постоянное запоминающее устройство, второй контроллер внешней интерфейсной магистрали информационного обмена, второй формирователь выходных разовых команд, второй приемник входных разовых команд, формирователь сигнала сброса, формирователь сигнала исправности, буферный формирователь, первую внутреннюю интерфейсную магистраль информационного обмена, вторую внутреннюю интерфейсную магистраль информационного обмена, устройство ввода сигнала ручного сброса, при этом первый вход-выход первого контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом первого приемопередатчика мультиплексного канала информационного обмена, второй вход-выход первого контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом второго приемопередатчика мультиплексного канала информационного обмена, вторые входы-выходы первого и второго приемопередатчиков мультиплексных каналов информационного обмена соединены соответственно с первым и вторым трансформаторами гальванической развязки, выходы которых являются соответственно выходами первого и второго мультиплексных каналов информационного обмена адаптера мультиплексных каналов информационного обмена, интерфейсные входы-выходы первого контроллера мультиплексных каналов информационного обмена, первого микропроцессора, первого оперативного запоминающего устройства, первого постоянного запоминающего устройства, а также первый интерфейсный вход-выход первого контроллера внешней интерфейсной магистрали информационного обмена соединены между собой при помощи первой внутренней интерфейсной магистрали информационного обмена, выход разовых команд первого контроллера мультиплексных каналов информационного обмена соединен со входом первого формирователя выходных разовых команд, выход которого является первым выходом разовых команд адаптера мультиплексных каналов информационного обмена, вход разовых команд первого контроллера мультиплексных каналов информационного обмена соединен с выходом первого приемника входных разовых команд, вход которого является первым входом разовых команд адаптера мультиплексных каналов информационного обмена, второй интерфейсный вход-выход первого контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя, второй вход-выход которого является входом-выходом внешней интерфейсной магистрали информационного обмена адаптера мультиплексных каналов информационного обмена, первый вход-выход второго контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом третьего приемопередатчика мультиплексного канала информационного обмена, второй вход-выход второго контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом четвертого приемопередатчика мультиплексного канала информационного обмена, вторые входы-выходы третьего и четвертого приемопередатчиков мультиплексных каналов информационного обмена соединены соответственно с третьим и четвертым трансформаторами гальванической развязки, выходы которых являются соответственно выходами третьего и четвертого мультиплексных каналов информационного обмена адаптера мультиплексных каналов информационного обмена, интерфейсные входы-выходы второго контроллера мультиплексных каналов информационного обмена, второго микропроцессора, второго оперативного запоминающего устройства, второго постоянного запоминающего устройства, а также первый интерфейсный вход-выход второго контроллера внешней интерфейсной магистрали информационного обмена соединены между собой при помощи второй внутренней интерфейсной магистрали информационного обмена, выход разовых команд второго контроллера мультиплексных каналов информационного обмена соединен со входом второго формирователя выходных разовых команд, выход которого является вторым выходом разовых команд адаптера мультиплексных каналов информационного обмена, вход разовых команд второго контроллера мультиплексных каналов информационного обмена соединен с выходом второго приемника входных разовых команд, вход которого является вторым входом разовых команд адаптера мультиплексных каналов информационного обмена, второй интерфейсный вход-выход второго контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя, первый выход первого контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя сигнала сброса, первый выход второго контроллера внешней интерфейсной магистрали информационного обмена соединен со вторым входом формирователя сигнала сброса, выход устройства ввода сигнала ручного сброса соединен с третьим входом формирователя сигнала сброса, выход формирователя сигнала сброса соединен с первой и второй внутренними интерфейсными магистралями информационного обмена, второй выход первого контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя сигнала исправности, второй выход второго контроллера внешней интерфейсной магистрали информационного обмена соединен со вторым входом формирователя сигнала исправности, выход формирователя сигнала исправности является выходом сигнала исправности адаптера мультиплексных каналов информационного обмена.

| ХВОЩ С.Т | |||

| и др | |||

| Микропроцессоры и микроЭВМ в системах автоматического управления | |||

| Справочник | |||

| Под ред | |||

| С.Т | |||

| Хвоща | |||

| - Л.: Машиностроение, 1987, с.639-644, рис.6.17б | |||

| RU 94015004 A1, 27.02.1996 | |||

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 1995 |

|

RU2109334C1 |

| US 5321819 A, 14.06.1994 | |||

| Станок для гибки арматурных элементов | 1972 |

|

SU505781A1 |

Авторы

Даты

2001-02-27—Публикация

2000-02-29—Подача