Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем.

Известны различные устройства сопряжения электронно-вычислительных машин с каналами связи (см., например, [1]).

Наиболее близким известным аналогом, принятым в качестве прототипа предлагаемого устройства, является устройство для сопряжения ЭВМ с каналами связи [2] , выполняющее функцию адаптера радиальных каналов информационного обмена. Устройство-прототип содержит контроллер радиальных каналов информационного обмена, образованный арифметико-логическим блоком, блоком памяти микрокоманд, дешифратором микрокоманд, регистром режима и блоком квитирования обмена, передатчик радиальных каналов информационного обмена, выполненный в виде блока выходных усилителей (формирователей), контроллер внешней интерфейсной магистрали информационного обмена, образованный приемопередатчиком и блоком обмена и первый тактовый генератор.

Недостатком прототипа является снижение производительности вычислительной системы, использующей данный адаптер из-за необходимости участия вычислительных устройств, подключенных к внешней интерфейсной магистрали информационного обмена в каждом цикле обмена по радиальным каналам информационного обмена, а также невозможность определения состояния исправности адаптера.

Задачей изобретения является повышение производительности вычислительной системы, использующей адаптер радиальных каналов информационного обмена, а также повышение ее отказоустойчивости.

Сущность изобретения заключается в том, что в адаптер радиальных каналов информационного обмена, содержащий контроллер радиальных каналов информационного обмена, передатчик радиальных каналов информационного обмена, контроллер внешней интерфейсной магистрали информационного обмена, первый тактовый генератор, дополнительно введены приемник радиальных каналов информационного обмена, микропроцессор, оперативное запоминающее устройство, постоянное запоминающее устройство, второй тактовый генератор, формирователь выходных разовых команд, приемник входных разовых команд, формирователь сигнала сброса, устройство ввода сигнала ручного сброса, формирователь сигнала исправности, буферный формирователь, внутренняя интерфейсная магистраль информационного обмена с соответствующими связями.

Кроме того, в предлагаемом адаптере радиальных каналов информационного обмена:

контроллер радиальных каналов информационного обмена выполнен с использованием микросхемы программируемой логики;

постоянное запоминающее устройство выполнено с использованием элементов электроперепрограммируемой энергонезависимой памяти;

контроллер внешней интерфейсной магистрали информационного обмена выполнен с использованием микросхемы программируемой логики.

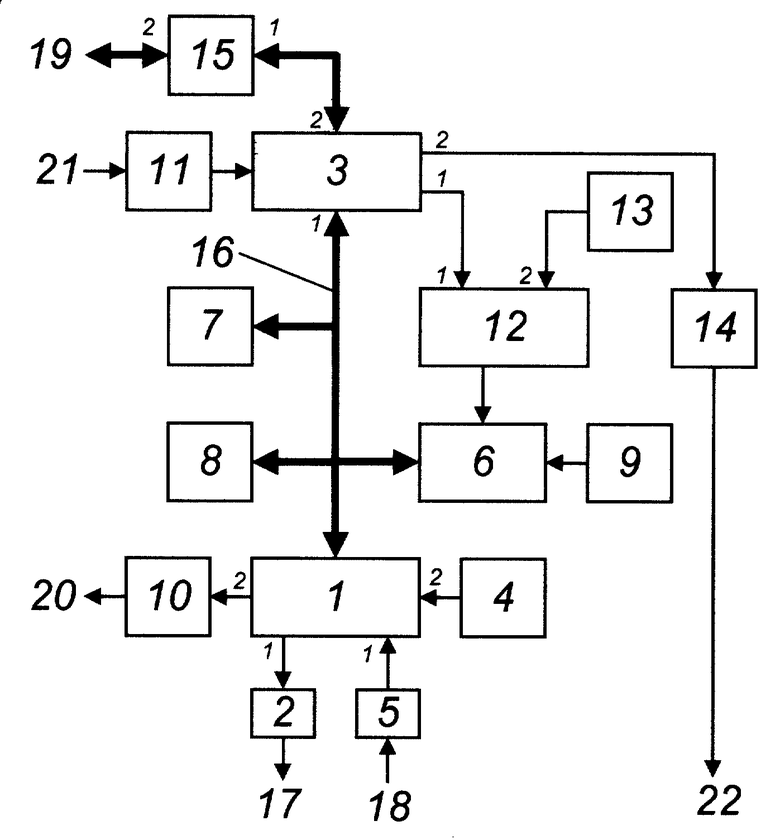

Сущность изобретения поясняется чертежом, на котором обозначены:

1 - контроллер радиальных каналов информационного обмена;

2 - передатчик радиальных каналов информационного обмена;

3 - контроллер внешней интерфейсной магистрали информационного обмена;

4 - первый тактовый генератор;

5 - приемник радиальных каналов информационного обмена;

6 - микропроцессор;

7 - оперативное запоминающее устройство;

8 - постоянное запоминающее устройство;

9 - второй тактовый генератор;

10 - формирователь выходных разовых команд;

11 - приемник входных разовых команд;

12 - формирователь сигнала сброса;

13 - устройство ввода сигнала ручного сброса;

14 - формирователь сигнала исправности;

15 - буферный формирователь;

16 - внутренняя интерфейсная магистраль информационного обмена;

17 - выход радиальных каналов информационного обмена;

18 - вход радиальных каналов информационного обмена;

19 - вход-выход внешней интерфейсной магистрали информационного обмена;

20 - выход разовых команд;

21 - вход разовых команд;

22 - выход сигнала исправности.

Выход радиальный каналов (выход 1) контроллера 1 радиальных каналов информационного обмена соединен с входом передатчика 2 радиальных каналов информационного обмена, выход которого является выходом 17 радиальных каналов информационного обмена адаптера.

Вход радиальный каналов (вход 1) контроллера 1 радиальных каналов информационного обмена соединен с выходом приемника 5 радиальных каналов информационного обмена, вход которого является входом 18 радиальных каналов информационного обмена адаптера.

Интерфейсные входы-выходы контроллера 1 радиальных каналов информационного обмена, микропроцессора 6, оперативного запоминающего устройства 7, постоянного запоминающего устройства 8, а также первый интерфейсный вход-выход контроллера 3 внешней интерфейсной магистрали информационного обмена соединены между собой при помощи внутренней интерфейсной магистрали 16 информационного обмена.

Выход разовых команд (выход 2) контроллера 1 радиальных каналов информационного обмена соединен с входом формирователя 10 разовых команд, выход которого является выходом 20 разовых команд адаптера.

Вход разовых команд контроллера 3 внешней интерфейсной магистрали информационного обмена соединен с выходом приемника 11 разовых команд, вход которого является входом 21 разовых команд адаптера радиальных каналов информационного обмена.

К входу синхронизации (входу 2) контроллера 1 радиальных каналов информационного обмена подключен выход первого тактового генератора 4.

К входу синхронизации микропроцессора 6 подключен выход второго тактового генератора 9.

Второй интерфейсный вход-выход контроллера 3 внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя 15, второй вход-выход которого является входом-выходом 19 внешней интерфейсной магистрали информационного обмена адаптера радиальных каналов информационного обмена. При помощи входа-выхода 19 внешней интерфейсной магистрали информационного обмена адаптер радиальных каналов информационного обмена подключается к интерфейсной магистрали информационного обмена вычислительной системы, в составе которой используется адаптер.

Первый выход контроллера 3 внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя 12 сигнала сброса, выход устройства 13 ввода сигнала ручного сброса соединен со вторым входом формирователя 12 сигнала сброса. Выход формирователя 12 сигнала сброса соединен с внутренней интерфейсной магистралью 16 информационного обмена.

Второй выход контроллера 3 внешней интерфейсной магистрали информационного обмена соединен с входом формирователя 14 сигнала исправности, выход которого является выходом 22 сигнала исправности адаптера.

Контроллер 1 радиальных каналов информационного обмена обеспечивает прием, контроль и преобразование последовательных кодов, поступающих с входа 18 радиальных каналов информационного обмена адаптера через приемник 5 радиальных каналов информационного обмена по шестнадцати входным каналам, и выдачу преобразованной информации на внутреннюю интерфейсную магистраль 16 информационного обмена по командам микропроцессора 6 для записи в оперативное запоминающее устройство 7, а также прием по командам микропроцессора 6 адаптера параллельной информации (по внутренней интерфейсной магистрали 16 информационного обмена), преобразование этой информации и выдачу в виде последовательных кодов по восьми выходным каналам через передатчик 2 радиальных каналов информационного обмена на выход 17 радиальных каналов информационного обмена адаптера.

Контроллер 1 радиальных каналов информационного обмена управляется командами от микропроцессора 6 по внутренней интерфейсной магистрали 16 информационного обмена. По командам микропроцессора 6 осуществляется запись и чтение данных в/из регистров контроллера 1 радиальных каналов информационного обмена и в/из его внутреннего оперативного запоминающего устройства. Контроллер 1 радиальных каналов информационного обмена формирует сигналы запроса прерывания микропроцессору 6 и передает вектор прерывания при запросе на выдачу на радиальные каналы очередного слова или приеме данных по каждому радиальному каналу.

Выходными данными контроллера 1 радиальных каналов информационного обмена являются для каждого выходного радиального канала синхросигнал и данные, а также сигналы сопровождения, передаваемые как выходные разовые команды.

Входными данными контроллера 1 радиальных каналов информационного обмена являются по каждому входному радиальному каналу сигналы с выхода приемника 5 радиальных каналов информационного обмена.

Работа контроллера 1 радиальных каналов информационного обмена синхронизирована первым тактовым генератором 4.

Передатчик 2 радиальных каналов информационного обмена содержит формирователи выходного биполярного последовательного кода для каждого радиального канала информационного обмена, которые обеспечивают преобразование униполярных последовательных кодов, поступающих с первого выхода контроллера 1 радиальных каналов информационного обмена, в биполярные последовательные коды с уровнями, соответствующими ГОСТ18977-79 и РТМ1495-75.

Каждый формирователь выходного биполярного последовательного кода содержит в цепи синхроимпульсов узел формирования формы выходного сигнала и выполнен на двух операционных усилителях и аналоговом переключающем элементе, управляемым выходным кодом.

Приемник 5 радиальных каналов информационного обмена содержит приемники входных биполярных последовательных кодов для каждого радиального канала информационного обмена, которые обеспечивают преобразование биполярных последовательных кодов, поступающих по радиальным каналам информационного обмена в униполярные последовательные коды для подачи на первый вход контроллера 1 радиальных каналов информационного обмена.

Каждый приемник входных биполярных последовательных кодов содержит входные резисторы, обеспечивающие высокое входное сопротивление, пороговую схему привязки и два компаратора, что обеспечивает подавление синфазных помех.

Контроллер 1 радиальных каналов информационного обмена дополнительно содержит регистр для хранения 8-ми выходных разовых команд.

Приемник 11 входных разовых команд выполнен на компараторах, и обеспечивает прием разовых команд, поступающих в виде сигнала "ключ на корпус/разрыв". Входная цепь каждого разряда входных разовых команд содержит резистор привязки к напряжению питания адаптера радиальных каналов информационного обмена и защитный диод, обеспечивающий прием входных сигналов напряжением до 27В.

Микропроцессор 6 управляет обменом по радиальным каналам информационного обмена в соответствии с программой, расположенной в постоянном запоминающем устройстве 8. Оперативное запоминающее устройство 7 используется в процессе исполнения этой программы для хранения данных и для взаимодействия по внешней интерфейсной магистрали информационного обмена. Логическое сопряжение внутренней интерфейсной магистрали 16 информационного обмена с внешней интерфейсной магистралью информационного обмена обеспечивает контроллер 3 внешней интерфейсной магистрали информационного обмена, который обеспечивает доступ по внешней интерфейсной магистрали информационного обмена к оперативному запоминающему устройству 7 в режиме прямого доступа к памяти.

Выходные разовые команды, выдаваемые через выход 20 разовых команд, формируются записью в соответствующий порт ввода-вывода по внешней интерфейсной магистрали информационного обмена и сохраняются в регистре выходных разовых команд контроллера 1 радиальных каналов информационного обмена. Выход каждого разряда регистра разовых команд контроллера 3 радиальных каналов информационного обмена подключен к схеме формирования выходных разовых команд формирователя 10 выходных разовых команд.

Схемы формирования выходных разовых команд формирователя 10 выходных разовых команд выполнены на транзисторах с открытым истоком. Выходные разовые команды выдаются в виде сигнала "ключ на корпус/разрыв цепи". В качестве защитного элемента в каждую схему формирования выходных разовых команд установлен резистор.

Формирователь 12 сигнала сброса выдает сигнал сброса на внутреннюю интерфейсную магистраль 16 информационного обмена при достижении напряжениями питания рабочих значений или при поступлении сигнала программного сброса с первого выхода контроллера 3 внешней интерфейсной магистрали информационного обмена, а также при поступлении соответствующего сигнала с выхода устройства 13 ввода сигнала ручного сброса.

Формирователь 14 сигнала исправности выдает сигнал исправности через выход 22 сигнала исправности адаптера при условии, если со второго выхода контроллера 3 внешней интерфейсной магистрали информационного обмена регулярно поступают программно формируемые сигналы. В случае отсутствия этих сигналов в течение определенного времени формирователь 14 сигнала исправности снимает сигнал исправности.

Буферный формирователь 15 служит для разделения внешней интерфейсной магистрали информационного обмена и выхода контроллера 3 внешней интерфейсной магистрали информационного обмена. Буферный формирователь 15 включает в себя блок магистральных усилителей, построенных по известным схемам.

Адаптер радиальных каналов информационного обмена работает следующим образом.

При достижении напряжениями питания рабочих значений, а также при программном сбросе со стороны устройств, подключенных к внешней интерфейсной магистрали информационного обмена, или при ручном сбросе (при помощи устройства 13 ввода сигнала ручного сброса) формирователь 12 сигнала сброса обеспечивает установку всех устройств адаптера радиальных каналов информационного обмена в исходное состояние.

Также адаптер может быть установлен в исходное состояние путем чтения со стороны внешней интерфейсной магистрали информационного обмена соответствующего порта ввода-вывода ("Порта инициализации") адаптера (программная инициализация).

Задание режимов работы осуществляется записью со стороны внешней интерфейсной магистрали информационного обмена в оперативное запоминающее устройство 7 блока информации управления, определяющей режимы работы каждого радиального канала. В соответствии с загруженной информацией, микропроцессор 6 производит настройку контроллера 1 радиальных каналов информационного обмена и сообщает по внешней интерфейсной магистрали информационного обмена о настройке адаптера на заданные режимы работы.

Выдача последовательного кода по радиальным каналам информационного обмена осуществляется следующим образом.

По завершении настройки контроллер 1 радиальных каналов информационного обмена начинает формировать сигналы готовности выходных каналов.

Микропроцессор 6 по запросам контроллера 1 радиальных каналов информационного обмена осуществляет загрузку из оперативного запоминающего устройства 7 очередного 32-разрядного слова из массивов данных, хранящихся в оперативном запоминающем устройстве 7 и подлежащих выводу через каждый выходной радиальный канал. Контроллер 1 радиальных каналов информационного обмена обеспечивает выдачу записанных в него данных на соответствующее выходные радиальные каналы. Одновременно с выдачей данных по радиальным каналам контроллер 1 радиальных каналов информационного обмена формирует очередные сигналы готовности выходных радиальных каналов.

Прием последовательного кода по радиальным каналам информационного обмена осуществляется следующим образом.

После настройки контроллер 1 радиальных каналов информационного осуществляет прием и контроль поступающих последовательных кодов по каждому из входных радиальных каналов информационного обмена.

При поступлении правильного последовательного кода по любому из каналов контроллер 1 радиальных каналов информационного обмена формирует сигнал готовности микропроцессору 6, который осуществляет чтение принятой информации из регистров контроллера 1 радиальных каналов информационного обмена и запись их в соответствующую данному каналу область оперативного запоминающего устройства 7. Правильным последовательным кодом считается тридцатидвухразрядный код с нечетным количеством информационных единиц при наличии паузы между словами не менее 3Т, где Т - период следования импульсов на заданной частоте. Адрес для записи в оперативное запоминающее устройство 7 формируется микропроцессором 6 в адресном или в файловом режиме приема информации. Режимы приема информации задаются со стороны внешней интерфейсной магистрали информационного обмена для каждого входного радиального канала информационного обмена индивидуально. В адресном режиме запись принятого последовательного кода осуществляется в заданную для данного канала область оперативного запоминающего устройства 7 по адресу, содержащемуся в соответствующих разрядах принятого последовательного кода ("Адресу параметра", 1. . .8 разряды принятого последовательного кода). В файловом режиме микропроцессор 6 осуществляет запись в оперативное запоминающее устройство 7 подряд заданного блока последовательных кодов, начиная со слова с заданным "Адресом параметра". По завершении приема блока последовательных кодов в файловом режиме микропроцессор 6 формирует сигнал прерывания на внешней интерфейсной магистрали информационного обмена.

Таким образом, предлагаемое изобретение позволяет повысить производительность вычислительной системы, использующей адаптер радиальных каналов информационного обмена путем ведения в адаптер микропроцессора и оперативного запоминающего устройства, что позволяет избавиться от необходимости участия вычислительных устройств, подключенных к внешней интерфейсной магистрали информационного обмена в каждом цикле обмена по радиальным каналам информационного обмена, а также повысить отказоустойчивость вычислительной системы за счет включения в адаптер радиальных каналов информационного обмена формирователя сигнала исправности, что позволяет определять состояние исправности адаптера.

Представленные чертежи и описание адаптера радиальных каналов информационного обмена позволяют, используя существующую элементную базу, изготовить его промышленным способом и использовать в вычислительных устройствах различного назначения, что характеризует предлагаемое изобретение как промышленно применимое.

Источники информации

1. Авт. св. СССР N 1264196, МПК G 06 F 13/14, опубл. в 1985 г.

2. Авт. св. СССР N 1532937, МПК G 06 F 13/00, опубл. в 1989 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТЕР МУЛЬТИПЛЕКСНЫХ КАНАЛОВ ИНФОРМАЦИОННОГО ОБМЕНА | 2000 |

|

RU2163728C1 |

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| СПОСОБ ИСПРАВЛЕНИЯ ОШИБОК ПРИ ПЕРЕДАЧЕ ИНФОРМАЦИИ БИИМПУЛЬСНЫМ КОДОМ Манчестер-II И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2566336C1 |

| МНОГОКАНАЛЬНЫЙ АДАПТЕР АНАЛОГОВОГО ВВОДА-ВЫВОДА | 2000 |

|

RU2183857C1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ВНУТРИСИСТЕМНОЙ ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ С ВНЕШНИМ МАГИСТРАЛЬНЫМ ПАРАЛЛЕЛЬНЫМ ИНТЕРФЕЙСОМ | 2000 |

|

RU2165640C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| НАВИГАЦИОННЫЙ КОМПЛЕКС ЛЕТАТЕЛЬНОГО АППАРАТА | 2000 |

|

RU2170409C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ С ИНТЕРФЕЙСОМ ПОСЛЕДОВАТЕЛЬНОГО КОДА | 2000 |

|

RU2201617C2 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем. Техническим результатом является повышение производительности вычислительной системы, использующей адаптер радиальных каналов информационного обмена, а также повышение ее отказоустойчивости. Сущность изобретения заключается в том, что в адаптер радиальных каналов информационного обмена, содержащий контроллер радиальных каналов информационного обмена, передатчик радиальных каналов информационного обмена, контроллер внешней интерфейсной магистрали информационного обмена, первый тактовый генератор, дополнительно введены приемник радиальных каналов информационного обмена, микропроцессор, оперативное запоминающее устройство, постоянное запоминающее устройство, второй тактовый генератор, формирователь выходных разовых команд, приемник входных разовых команд, формирователь сигнала сброса, устройство ввода сигнала ручного сброса, формирователь сигнала исправности, буферный формирователь, внутренняя интерфейсная магистраль информационного обмена с соответствующими связями. 3 з.п ф-лы, 1 ил.

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| SU 1206789 A, 23.01.1986 | |||

| Устройство для неразрушающего контроля объектов | 1987 |

|

SU1490612A2 |

| Устройство динамического приоритета | 1987 |

|

SU1495793A1 |

Авторы

Даты

2000-11-27—Публикация

2000-04-03—Подача