Микроконтроллеры нуждаются при применении для общих задач управления, в частности, в карточках с микросхемой, в энергонезависимых накопителях в качестве накопителей программ и накопителей данных. Прежде всего при применении в портативных носителях данных с батарейным питанием, как при мобильной передаче данных и обработке данных, или при беспроволочном подводе энергии, как в случае бесконтактных карточек с микросхемами, в частности, для накопителей данных приемлемыми являются способы программирования и стирания с малым потреблением мощности. Таким же образом и напряжения питания должны составлять менее 3 В. Так как контроллеры и карточки с микросхемой подвержены сильному давлению цен, для широкого применения важным является незначительная сложность процесса изготовления энергонезависимых накопителей.

Широко применяемые сегодня в карточках с микросхемой FLOTOX-EEPROM-ячейки (электронно-стираемые программируемые постоянные накопительные ячейки (ЭСППЗУ) на МОП-транзисторах с плавающим затвором и тонким слоем туннельного оксида), которые, например, известны из книги авторов Dietrich Rhein и Heinz Freitag "Mikroelektronische Speicher", издательство Springer, Вена, 1992, в частности, стр. 122, отличаются малым потреблением мощности, так как они программируются и стираются за счет туннельных токов Фаулера-Нордхайма. За счет этого программирующие напряжения могут просто получаться на микросхеме также из низких напряжений питания, которые могут быть меньше 3 В. Перепрограммирование в случае таких накопителей является возможным побайтово, так что FLOTOX-EEPROM-ячейки особенно пригодны для накопителей данных, которые перепрограммируются при эксплуатации. Эти FLOTOX-EEPROM-ячейки состоят из транзистора выборки и накопительного транзистора и поэтому требуют большой площади ячейки, так что на одном кристалле могут быть реализованы только небольшие накопители. Кроме того, за счет необходимого высокого программирующего напряжения 15 - 20 В реализация высоковольтных транзисторов, чтобы можно было включать эти программирующие напряжения, является сложной.

ЭСППЗУ с "быстрым стиранием" (Flash) реализованы в противоположность к ЭСППЗУ (EEPROM) с только одним транзистором на накопительную ячейку так, что здесь являются возможными значительно более сложные накопители, чем с FLOTOX-EEPROM-ячейками. Они, конечно, программируются горячими носителями заряда (channel hot electron: CHE). Этот вид программирования требует высоких программирующих токов, которые ограничивают минимальное напряжение питания до порядка 5 В. Они поэтому не применимы в качестве накопителей данных, которые должны перепрограммироваться при эксплуатации из малых напряжений питания или через бесконтактный подвод энергии. Обычная сегодня Split-Gate-Flash-EEPROM-ячейка ("Быстро стираемое" ЭСППЗУ с расщепленным затвором) описана и представлена также в книге "Mikroelektronische Speicher" на стр. 126.

Также и US-5,294,819 показывает однотранзисторную EEPROM-ячейку, которая образована только одним образованным переходом исток-канал-сток МОП-транзистором, при котором в полупроводниковой подложке первого типа проводимости выполнены области стока и истока второго типа проводимости с противоположной к первому типу проводимости полярностью. Ячейка содержит находящийся на плавающем потенциале электрод затвора, который электрически изолирован от области стока за счет туннельного оксида и от находящейся между областью стока и истока канальной области за счет оксида затвора и простирается в направлении исток-канал-сток, по меньшей мере, над частью канальной области и частью области стока, а также управляющий электрод, который электрически изолирован от электрода затвора за счет оксида связи.

Как стирание, так и программирование производятся посредством туннельных токов, правда используется только высокое положительное напряжение, которое прикладывают или к управляющему затвору, или выводу стока транзистора, чтобы внести электроны на управляющий затвор или снять их с него. Путем применения только высокого положительного напряжения оно должно иметь большую абсолютную величину порядка 18 В, за счет чего должны производиться большие затраты на изоляцию на полупроводниковой микросхеме.

Patent Abstracts of Japan, том 15, N 241 и JP-A-3074881 показывают также энергонезависимую накопительную ячейку с выше описанной конструкцией. Там к управляющему затвору прикладывают отрицательное напряжение и небольшое напряжение к электроду стока, чтобы удалить электроны с накопительного затвора. Однако при этом не раскрыто, каким образом электроны попадают на накопительный затвор.

Задача настоящего изобретения поэтому состоит в том, чтобы указать способ для эксплуатации электрически стираемой и программируемой энергонезависимой накопительной ячейки, который избегает недостатков уровня техники.

Эта задача решается способом с признаками пункта 1 формулы изобретения. Предпочтительные формы дальнейшего развития указаны в зависимых пунктах формулы изобретения.

Лежащая в основе изобретения накопительная ячейка состоит из только одного транзистора так, что потребность места по сравнению с обычными FLOTOX-EEPROM-ячейками является значительно меньшей. Однако она программируется и стирается таким же образом, что и такие FLOTOX-EEPROM-ячейки: путем туннельных токов Фаулера-Нордхайма.

За счет соответствующего изобретению применения отрицательных и положительных напряжений для программирования и стирания, абсолютная величина высоких напряжений может удерживаться относительно малой, так что невысоковольтные части схемы также должны быть менее электрически прочными и тем самым могут изготавливаться с меньшими технологическими затратами. Кроме того, необходимые для создания высокого напряжения встроенные в кристалл зарядные насосы могут иметь меньшие размеры.

Если первый тип проводимости является p-типом проводимости, то есть в случае образующего ячейку МОП-транзистора речь идет о n-канальном транзисторе, то ячейка программируется типично за счет того, что к ее управляющему затвору прикладывают напряжение -12 В, а к стоку +5 В, в то время как исток соединен с корпусом. За счет этого в области туннельного оксида, то есть в области, в которой находящийся на плавающем потенциале электрод затвора, так называемый плавающий затвор, перекрывается с областью стока, носители заряда туннелируют через туннельный оксид, так что плавающий затвор заряжается положительно. За счет этого пороговое напряжение этого МОП-транзистора сдвигается к более низким значениям. Для стирания таким образом программированной ячейки к управляющему электроду прикладывают типичным образом напряжение 12 В, а к электроду истока прикладывают типичным образом напряжение -6 В, в то время как электрод стока остается открытым. За счет этого носители заряда туннелируют между плавающим затвором и областью истока и также канальной областью так, что плавающий затвор снова разряжается и пороговое напряжение транзистора сдвигается к более высоким значениям. В случае программированной ячейки пороговые напряжения имеют значения порядка 1 В, а в случае непрограммированной ячейки порядка 5 В. Для считывания поэтому к управляющему затвору прикладывают напряжение порядка 3 В, в то время как к стоку приложено напряжение порядка 1 В, а к истоку напряжение 0 В. Только в случае программированной ячейки тогда будет течь ток, который может детектироваться, например, как логическая "1".

За счет соответствующего изобретению одновременного применения положительного и отрицательного напряжения для программирования и стирания соответствующей изобретению накопительной ячейки является возможным отказаться от дополнительного, требующего много места транзистора выборки и несмотря на это иметь возможность адресации каждой накопительной ячейки по отдельности. При обычном расположении накопительных ячеек в накопительной матрице, в которой выводы затворов накопительных ячеек соединены с шинами слов и выводы стоков с разрядными шинами, при приложении отрицательного напряжения к шине слов все накопительные ячейки, выводы затвора которых соединены с этой шиной слов, соединены неизбежно с этим отрицательным напряжением. Однако программируется только та накопительная ячейка, вывод стока которой соединен с положительным напряжением. Условие, чтобы оба напряжения одновременно были приложены только к одной единственной накопительной ячейке, может быть тем самым выполнено путем выбора только одной шины слов и только одной разрядной шины.

В случае соответствующей изобретению накопительной ячейки на выводе стока приложено максимально напряжение питания, так что также на разрядной шине, которая соединена с выводом стока и тем самым на схемах оценки приложено максимально напряжение питания и таким образом не должны приниматься никакие специальные меры предосторожности для защиты этих схем оценки.

Соответствующая изобретению накопительная ячейка вместе со стандартными КМОП-логическими схемами может быть преимущественным образом реализована на одной полупроводниковой подложке, то есть на одном кристалле микросхемы. Кроме того, является возможным одновременно реализовывать на той же самой полупроводниковой подложке также высоковольтные КМОП-схемные контуры для включения необходимых положительных и отрицательных напряжений. Как накопительные ячейки, так и высоковольтные схемы для этой цели располагают в глубоких ваннах с полярностью типа проводимости, которая противоположна полярности типа проводимости полупроводниковой подложки.

В первой форме выполнения соответствующей изобретению накопительной ячейки плавающий затвор простирается в направлении исток-канал-сток над всей канальной областью и еще над частью области стока. Эта область перекрытия плавающий затвор-сток определяет здесь туннельную область при программировании.

В особенно преимущественной форме выполнения изолирующий оксид, по меньшей мере, в части области перекрытия является тоньше, чем над канальной областью. За счет этой более тонкой области тогда определяется туннельная область. Чтобы избежать индуцированных полем затвора токов утечки стока при программировании, однако, является особенно предпочтительным, если оксид в области p-n-перехода от области стока к канальной области является толще, чем туннельный оксид.

В накопительных ячейках, в которых плавающий затвор перекрывает всю канальную область, при слишком продолжительном программировании пороговое напряжение ячейки становится отрицательным так, что препятствуется деселектирование таких программированных ячеек при считывании. Этому можно воспрепятствовать за счет предпочтительной формы выполнения так называемой ячейки с расщепленным затвором. При этом плавающий затвор простирается только над частью канальной области, в то время как управляющий электрод простирается над всей канальной областью и при этом в области, где больше нет плавающего затвора, осуществляет емкостную связь с каналом для его управления. Такой ячейкой с расщепленным затвором через образованный из управляющего электрода и оксида затвора последовательный транзистор ограничивается нижнее пороговое напряжение ячейки, даже если пороговое напряжение транзисторной части из плавающего затвора и оксида затвора становится отрицательным.

Изобретение поясняется ниже на примере выполнения с помощью фигур, на которых показано:

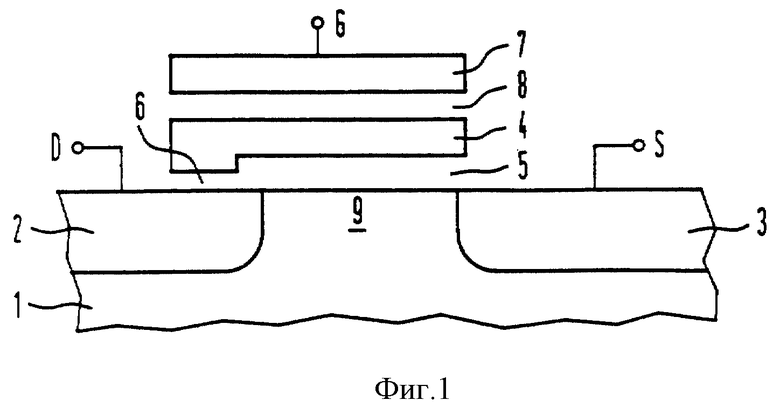

Фиг. 1 в схематическом представлении поперечное сечение через соответствующую изобретению накопительную ячейку,

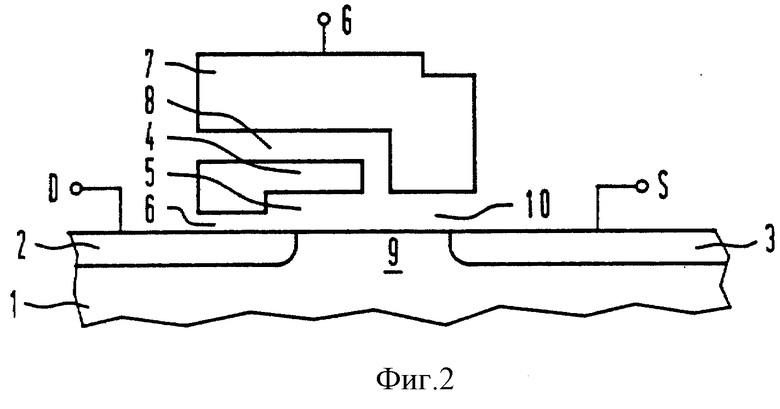

Фиг. 2 в схематическом представлении поперечное сечение через форму дальнейшего развития соответствующей изобретению накопительной ячейки,

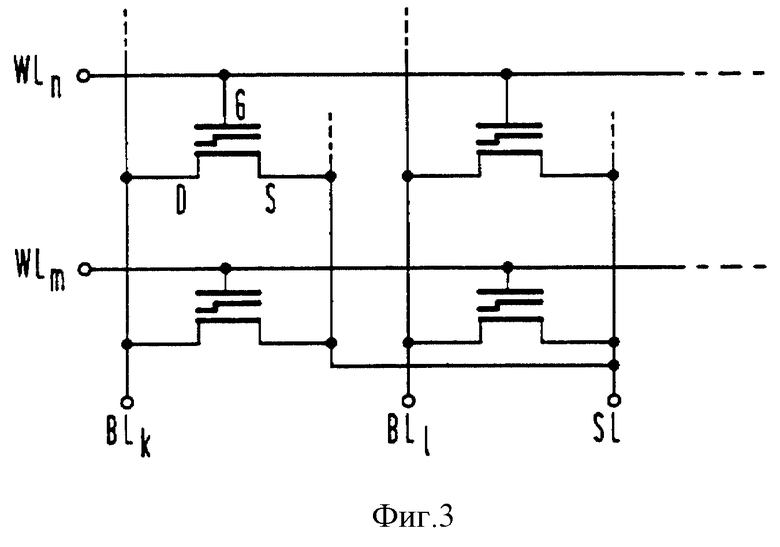

Фиг. 3 в схематическом представлении расположение таких накопительных ячеек в матрице накопительных ячеек и

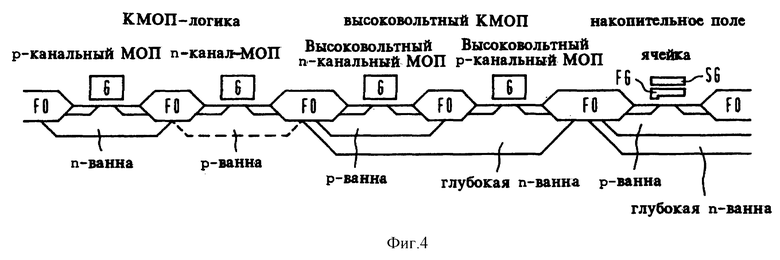

Фиг. 4 в схематической форме принципиальная реализация накопительного поля, стандартной КМОП-логики и высоковольтных КМОП-схем в полупроводниковой подложке.

Фиг. 1 показывает полупроводниковую подложку 1 первого типа проводимости, который, например, должен быть p-типом. В ней область стока 2 и область истока 3 имеют тип проводимости с полярностью, противоположной к типу проводимости полупроводниковой подложки 1, в настоящем примере то есть n-типа. Соответственно в случае транзистора этой накопительной ячейки речь идет о n-канальном транзисторе. Область стока 2 снабжена выводом стока D, а область истока выводом истока S. Над областью стока 2 и областью истока 3 и расположенной между этими областями канальной областью 9 выполнен оксидный слой в качестве электрического изолирующего слоя. Над этим оксидным слоем 5, 6 выполнен электрод затвора 4, который находится на электрически плавающем потенциале. Обычно его обозначают как плавающий затвор. Он простирается соответствующим изобретению образом в направлении исток-канал-сток МОП-транзистора над канальной областью и, по меньшей мере, частью области стока 2. Область оксидного слоя между плавающим затвором 4 и канальной областью обозначается как оксид затвора 5, а область оксидного слоя между плавающим затвором 4 и областью стока 2 обозначается как туннельный оксид 6. В представленной на фиг. 1 форме развития изобретения туннельный оксид 6 имеет меньшую толщину, чем оксид затвора 5. Особенно предпочтительно, если туннельный оксид 6, как представлено на фиг. 1, в области p-n-перехода от области стока 2 к канальной области 9 имеет такую же толщину, что и оксид затвора 5, за счет чего исключается или, по меньшей мере, уменьшается индуцированный полем затвора ток утечки на стоке. Для применений, при которых при программировании можно мириться с более высоким таким током утечки на стоке, устройство на фиг. 1 можно упростить таким образом, что толщины туннельного оксида 6 и оксида затвора 5 выбирают одинаковыми. Для такой упрощенной накопительной ячейки в способе изготовления отпадают некоторые технологические операции. Над электродом затвора или соответственно плавающим затвором 4 расположен электрически изолированный от плавающего затвора 4 оксидом связи управляющий электрод 7. Он соединен с выводом затвора G.

Фиг. 2 показывает форму дальнейшего развития накопительной ячейки согласно фиг. 1, причем одинаковые части имеют одинаковые ссылочные позиции. Представлена ячейка с расщепленным затвором. При этом плавающий затвор 4 простирается только над частью канальной области 9. За счет этого управляющий электрод 7 над частичной областью 10 оксида затвора может осуществлять емкостную связь с канальной областью 9 и управлять ею за счет этого. За счет этой меры компенсируется действие отрицательного порогового напряжения при "перепрограммировании".

Фиг. 3 показывает схематическое представление соответствующих изобретению накопительных ячеек в матрице накопительных ячеек. Матрица накопительных ячеек организована в шины слов ...WLn, WLm... и разрядные шины ... BLk, BLl... Накопительные ячейки соединены соответственно своим выводом затвора G с одной из шин слов ...WLn, WLm... и своим выводом стока D с одной из разрядных шин ...BLk, BLl.... Выводы истока S всех накопительных ячеек соединены с шиной истока SL. Естественно, что может также иметься множество шин истока, которые соединены тогда соответственно только с одной группой выводов истока S накопительных ячеек.

В образованной n-МОП-транзистором накопительной ячейке для программирования к управляющему электроду, то есть к выводу затвора G накопительной ячейки, должно прикладываться высокое отрицательное программирующее напряжение. Согласно фиг. 3 это означает, что это программирующее напряжение должно прикладываться к шине слов WLn. Это означает однако, что это программирующее напряжение одновременно приложено ко всем другим накопительным ячейкам, выводы затвора которых соединены с этой шиной слов.

Таким образом, чтобы в соответствующей изобретению накопительной ячейке, однако, действительно происходило программирование, одновременно с высоким отрицательным программирующим напряжением к выводу затвора G должно прикладываться положительное напряжение к выводу стока D. Как опять-таки следует из фиг. 3, это положительное напряжение должно прикладываться к разрядной шине BLk, за счет чего это положительное напряжение опять-таки приложено ко всем выводам стока D соединенных с этой разрядной шиной BLk накопительных ячеек. Программирование, однако, состоится только тогда, когда одновременно на выводе затвора приложены отрицательное программирующее напряжение и на выводе стока положительное напряжение. Если выбраны только одна шина слов и только одна разрядная шина, это условие выполнено только для одной единственной накопительной ячейки. Тем самым в случае выполненного с соответствующими изобретению накопительными ячейками накопителя каждая накопительная ячейка может адресоваться по отдельности. Естественно является возможным за счет адресования множества шин слов и/или множества разрядных шин одновременно программировать множество накопительных ячеек.

Для стирания к выводу затвора накопительной ячейки должно прикладываться высокое положительное напряжение, а к выводу истока отрицательное напряжение. Если все выводы истока соединены с шиной истока, при выборе только одной шины слов, к которой приложено высокое положительное напряжение, минимальное количество накопительных ячеек, которые могут быть стерты вместе, равно количеству накопительных ячеек, которые соединены с шиной слов. За счет этой меры процесс стирания значительно ускоряется.

При реализации выше описанного электрически стираемого и программируемого энергонезависимого накопителя вместе с КМОП-логикой, в частности, вследствие использования высоких положительных и отрицательных напряжений, должны приниматься особые меры предосторожности. Они представлены схематическим образом на фиг. 4. Исходя из p-проводящей полупроводниковой подложки, n- и p-канальные МОП-полевые транзисторы для логики изготавливают в p-подложке и в n-ванне. За счет этого КМОП-логика является совместимой по дизайну с стандартными КМОП-схемами. Для высоковольтных КМОП-транзисторов необходим более толстый оксид затвора, кроме того, n-канальные МОП-транзисторы для переключения отрицательных напряжений располагают изолированно от подложки в p-ванне внутри глубокой n-ванны. Высоковольтные p-канальные МОП-транзисторы расположены в n-ванне. При только низких требованиях к скорости переключения логики высоковольтные и логические транзисторы могут быть реализованы также с одинаковой толщиной оксидного слоя. Накопительные ячейки изготавливают изолированно от подложки в p-ванне внутри глубокой n-ванны. Таким образом является возможным прикладывать отрицательное напряжение к общей шине истока, не оказывая влияния на логическую часть.

За счет применения положительных и отрицательных напряжений абсолютная величина имеющихся программирующих напряжений ограничена до порядка 12 В, так что высоковольтные части должны рассчитываться только на эту величину. За счет применения изолированной p-ванны внутри глубокой n-ванны можно обрабатывать отрицательные напряжения без необходимости прибегать в высоковольтной части к инверторам напряжения или p-МОП-истоковым повторителям. В поле накопительных ячеек изолированная p-ванна имеет преимущество, что общая шина истока может прикладываться к отрицательному напряжению, не оказывая за счет этого воздействия на КМОП-логическую часть. Положительные и отрицательные программирующие напряжения вследствие малого потребления мощности программирования Фаулера-Нордхайма могут легко получаться на кристалле микросхемы за счет зарядных насосов.

Отдельные детали на фиг. 4 отделены друг от друга за счет областей полевого оксида. Хотя электроды затвора G КМОП-логики и высоковольтных КМОП-схем и представлены на фиг. 4 с одинаковым расстоянием относительно канальной области, однако на практике, если требуется быстрая КМОП-логика, толщины оксида под электродами затвора G выбирают различными. В случае представленной на фиг. 4 ячейки накопительного поля плавающий затвор FG и управляющий затвор SG показаны схематическим образом.

Использование: микроэлектроника. Сущность изобретения: электрически стираемая и программируемая энергонезависимая накопительная ячейка, которая образована только одним образованным переходом исток-канал-сток МОП-транзистором, в котором в полупроводниковой подложке (1) первого типа проводимости выполнены область стока (2) и область истока (3) второго типа проводимости с полярностью, противоположной первому типу проводимости, с находящимся на плавающем потенциале электродом затвора (4), который электрически изолирован от области стока (2) туннельным оксидом и от находящейся между областью стока и истока (2, 3) канальной области (9) оксидом затвора (5, 10) и протирается в направлении перехода исток-канал-сток по меньшей мере над частью канальной области (9) и частью области стока (2), и с управляющим электродом (7), который электрически изолирован оксидом связи (8) от электрода затвора (4). Для программирования накопительной ячейки к управляющему электроду (7) прикладывают высокое отрицательное напряжение, к электроду стока (D) - напряжения питания и к электроду истока (5) - нуль вольт. Для стирания накопительной ячейки к управляющему электроду (7) прикладывают высокое положительное напряжение и к электроду истока (s) - отрицательное напряжение, а электрод стока (D) оставляют неподключенным. Техническим результатом изобретения является снижение абсолютной величины высоких напряжений, что приводит к снижению затрат на изготовление частей схемы. 6 з.п.ф-лы, 4 ил.

| JP 3074881 A, 21.06.1991 | |||

| US 5294819 A, 16.03.1994 | |||

| Кулачковая сцепная муфта | 1974 |

|

SU618586A1 |

| Устройство для намотки и выдачи питающего кабеля | 1981 |

|

SU1056338A1 |

| RU 1105060 A1, 27.01.1995. | |||

Авторы

Даты

2001-05-27—Публикация

1996-07-08—Подача