При программировании или стирании энергонезависимой памяти, как например, электрически стираемой программируемой постоянной флэш-памяти с использованием эффекта Фоулера-Нордхайма образуется явное снижение потребления мощности по сравнению с записью с помощью горячих электронов. При использовании эффекта Фоулера-Нордхайма электроны могут за счет приложения положительного высокого напряжения на управляющий затвор ячейки памяти переходить за счет туннельной проводимости из соответствующей области стока на соответствующий плавающий затвор. За счет приложения отрицательного высокого напряжения к управляющему затвору и положительного напряжения к стоку ячейки памяти электроны могут проходить за счет туннельной проводимости с плавающего затвора обратно в область стока. Отрицательное высокое напряжение создают с помощью нагнетателей напряжения, которые работают по принципу емкостного умножения напряжения и имеют в каждой ступени накачивания один диод с МОП-структурой и один конденсатор. Под высоким напряжением в этом контексте понимается уже напряжение, равное, например, 10-30 В.

Особенно эффективное устройство для создания отрицательного высокого напряжения описано в публикации А. Умезава и др. "Электрически стираемая программируемая постоянная флэш-память с только рабочим напряжением 5 В и растром 0,6 мкм с рядной декодирующей схемой в трехкарманной структуре", IEEE Journal of Solid-State Circuits, том 27, N II (1992). При этом используют высоковольтные транзисторы с p-канальной МОП-структурой. Дополнительный усилительный транзистор накачивающей ступени повышает проводимость расположенного на выходе диода с МОП-структурой и таким образом снижает падение напряжения на этом диоде.

В высоковольтных транзисторах часто возникает усиленный эффект управления через подложку, из-за чего отдельные транзисторные ванны в устройстве для умножения напряжения подсоединяют раздельно. При создании отрицательного высокого напряжения до настоящего времени использовались высоковольтные транзисторы с p-канальной МОП-структурой. Однако высоковольтные транзисторы с p-канальной МОП-структурой имеют тот недостаток, что зарядка высоковольтных n-ванн до отрицательного высокого напряжения поляризует диод подложка-ванна в проводящем направлении и создает короткое замыкание по отношению к подложке.

Лежащая в основе изобретения задача состоит в том, чтобы создать устройство для создания отрицательного высокого напряжения, в котором возможно приложение отрицательного высокого напряжения к отдельно подключенным, образующим канал ваннам высоковольтных транзисторов без возникновения короткого замыкания по отношению к подложке.

Поставленная задача решается тем, что в устройстве для создания отрицательного высокого напряжения, содержащем, по меньшей мере, четыре накачивающих транзистора, представляющих собой высоковольтные транзисторы с МОП-структурой, согласно изобретению, по меньшей мере, четыре накачивающих транзистора включены последовательно, причем первый накачивающий транзистор соединен непосредственно со входом, а последний накачивающий транзистор соединен непосредственно или опосредованно с выходом устройства, при этом устройство содержит первые и вторые конденсаторы, причем затворы нечетных накачивающих транзисторов через первые конденсаторы соединены с первым входом тактовых сигналов, а затворы четных накачивающих транзисторов через другие первые конденсаторы соединены со вторым входом тактовых сигналов, причем нечетные соединительные узлы последовательной схемы через вторые конденсаторы соединены с третьим входом тактовых сигналов, а, четные соединительные узлы последовательной схемы через вторые конденсаторы соединены с четвертым входом тактовых сигналов, при этом накачивающие транзисторы представляют собой высоковольтные транзисторы с n-канальной МОП-структурой, соответствующая образующая канал ванна которых соединена с соответствующим соединительным узлом последовательной схемы.

Устройство согласно изобретению содержит усилительные транзисторы, причем затвор соответствующего накачивающего транзистора через соответствующий усилительный транзистор соединен с соответствующим соединительным узлом со стороны следующего накачивающего транзистора, а затвор соответствующего усилительного транзистора соединен с соответствующим соединительным узлом со стороны предыдущего накачивающего транзистора или со стороны входа устройства, при этом все усилительные транзисторы представляют собой высоковольтные транзисторы с n-канальной МОП-структурой, соответствующая образующая канал ванна которых соединена с соответствующим соединительным узлом последовательной схемы.

Устройство согласно изобретению содержит выходной диод, причем последний накачивающий транзистор соединен опосредованно через выходной диод с выходом устройства, при этом выходной диод представляет собой высоковольтный транзистор с n-канальной МОП- структурой, образующая канал ванна которого соединена с выходом устройства.

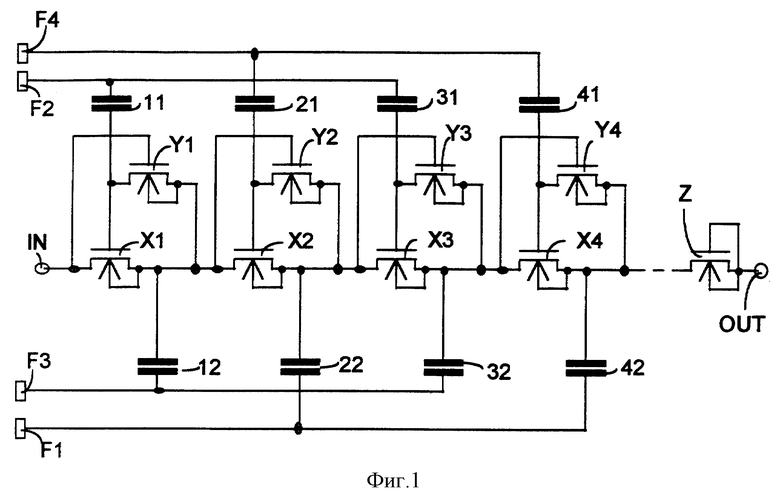

Изобретение поясняется ниже с помощью чертежей, на которых изображено:

фиг. 1 - схема устройства согласно изобретению;

фиг. 2 - временная диаграмма тактовых сигналов, прикладываемых при работе устройства согласно изобретению.

На фиг. 1 в качестве примера выполнения показано четырехступенчатое устройство согласно изобретению для создания отрицательного высокого напряжения, при этом первая ступень имеет транзистор X1 с n-канальной МОП-структурой и транзистор Y1 с n- канальной МОП-структурой, а также конденсатор 11 и конденсатор 12, вторая ступень имеет транзисторы Х2, Y2 с n-канальной МОП- структурой, а также конденсаторы 21, 22, третья ступень имеет транзисторы X3, Y3 с n-канальной МОП-структурой, а также конденсаторы 31, 32 и четвертая ступень имеет транзисторы X4, Y4 с n-канальной МОП-структурой, а также конденсаторы 41, 42. Вход IN устройства согласно изобретению соединен с вводом транзистора X1 и с затвором транзистора Y1 и представляет собой вход первой ступени. Затвор транзистора X1 соединен с вводом транзистора Y1 и через конденсатор 11 с тактовым входом F2. Выход первой ступени соединен со вторым вводом транзистора Y1 и вторым вводом транзистора X1, а также через конденсатор 12 с входом F3 тактовых сигналов. Вход второй ступени соединен с выходом первой ступени и выход второй ступени соединен со входом третьей ступени. Схема второй ступени соответствует схеме первой ступени, при этом, однако, конденсатор 21 не соединен как конденсатор 11 с входом F2 тактовых сигналов, а с входом F4 тактовых сигналов, а конденсатор 22 соединен не как конденсатор 12 с входом F3 тактовых сигналов, а с входом F1 тактовых сигналов. Ступени 3 и 4 соответствуют их схемой и подачей тактовых сигналов обеим первым ступеням и включены вслед за второй ступенью. На выходе четвертой ступени предусмотрен транзистор Z с n-канальной МОП-структурой, первый ввод которого соединен с выходом четвертой ступени и затвор которого и второй ввод соединены с выходом OUT устройства согласно изобретению, на котором создается высокое напряжение. При этом транзистор Z работает как подключенный в проводящем направлении диод.

Высоковольтные транзисторы X1, Y1... X4, Y4 с n-канальной МОП- структурой представляют собой так называемые трехкарманные транзисторы, которые показаны, например, в указанной выше публикации Умезава на фиг. 3а как транзистор с n-канальной МОП- структурой рядного декодера. При этом, как показано здесь на фиг. 1, p-ванна соответствующего транзистора с n-канальной МОП- структурой соединена со вторым вводом соответствующего транзистора с n-канальной МОП-структурой. При этом внешняя, общая n-ванна транзисторов с n-канальной МОП-структурой имеет потенциал 0 В. Таким образом, в этом устройстве не возникает диодного короткого замыкания.

Транзисторы X1. ..X4 действуют как накачивающие транзисторы для зарядки конденсаторов и транзисторы Y1. . . Y2 - как так называемые усилительные транзисторы для повышения уровня напряжения между затвором и стоком соответствующего накачивающего транзистора для повышения проводимости, соответственно, эффективности. Диод Z служит в качестве выходного диода. Выходной диод предотвращает выравнивание потенциалов между выходом OUT и выходом последней ступени в том случае, когда он имеет более высокий потенциал, чем выход OUT. Если выход OUT имеет более низкий потенциал, чем выход последней ступени, то выходной диод поляризован в проводящем направлении и может происходить выравнивание потенциалов.

За счет соответствующего последовательного включения k ступеней можно создать в целом высокое напряжение VOUT = VIN - (k*(F - VX)), где VOUT обозначает напряжение на выходе OUT, VIN обозначает напряжение на входе IN, k равно количеству ступеней, F обозначает тактовое напряжение и VX - падение напряжения на соответствующем накачивающем транзисторе X. При этом падение напряжения на соответствующем накачивающем транзисторе Х за счет применения соответствующего усилительного транзистора Y явно меньше, чем пороговое напряжение VT соответствующего транзистора X.

В показанном на фиг. 1 примере с числом ступеней k = 4, напряжением VIN = 0 В, тактовым напряжением F = 5 В выходное напряжение VOUT = 19,6 В.

Для k > 4 также необходимы только четыре тактовых сигнала, так как первые конденсаторы 11, 21. . . попеременно соединяются с входами F2 и F4 тактовых сигналов, а вторые конденсаторы попеременно соединяются с входами F1 и F3.

На фиг. 2 показаны друг под другом временные диаграммы тактовых сигналов на входах F1...F4 тактовых сигналов. В устройстве согласно изобретению, т.е. в нагнетателе отрицательного высокого напряжения с положительными входными тактами, цикл накачки происходит всегда тогда, когда такты накачки F1 и F2 являются логически низкими, в то время как усилительный цикл совершается при логически высоких F2 и F4 и может быть значительно короче, чем цикл накачки. Сигналы входов F1 и F2, соответственно, сигналы выходов F2 и F4 по времени сдвинуты относительно друг друга на, примерно, половину времени такта. Перекрытие во времени тактовых сигналов на входах F1 и F3 обеспечивает подзарядку накачивающих транзисторов X1...X4. Тактовые сигналы на входах F2 и F4 выбраны во времени так, что во время фазы пропускания соответствующего накачивающего транзистора соответствующий усилительный транзистор заперт и между затвором и стоком соответствующего усилительного транзистора находится повышенное напряжение, за счет чего повышается его проводимость.

Изобретение относится к устройству для создания отрицательного высокого напряжения, которое требуется, например, для программирования электрически стираемой программируемой постоянной флэш-памяти. Технический результат изобретения заключается в том, что уменьшается эффект управления через подложку. Образующие канал ванны соответствующих транзисторов выполнены с возможностью соединения с вводом соответствующего транзистора. При этом отрицательное высокое напряжение не поляризует диод подложка-ванна в прямом направлении и таким образом не возникает короткого замыкания по отношению к подложке. Устройство выполнено четырехступенчатым. Каждая ступень содержит по два МОП-транзистора с n-канальной структурой. На выходе четвертой ступени предусмотрен МОП-транзистор Z с n-канальной структурой. 2 з.п. ф-лы, 2 ил.

| IEEE JOURNAL OF SOLID STATE CIRCUITS, VOL.27, N 11, 1992, с.1540-1545 | |||

| Аналоговое перемножающее устройство | 1984 |

|

SU1218401A1 |

| US 5394365 A, 28.02.1995 | |||

| US 5077691 A, 31.01.1991 | |||

| US 5432738 A, 11.07.1995 | |||

| Умножитель напряжения | 1983 |

|

SU1164739A1 |

Авторы

Даты

2000-11-20—Публикация

1996-12-10—Подача