Изобретение относится к полупроводниковому запоминающему устройству согласно ограничительной части пункта 1 формулы изобретения.

Главной областью применения такого полупроводникового запоминающего устройства являются энергонезависимые, электрически стираемые, программируемые полупроводниковые запоминающие устройства, выполненные из запоминающих ячеек, которые могут как угодно часто программироваться и снова стираться путем приложения определенных напряжений. Запоминание информации при этом происходит за счет нанесения или, соответственно, удаления заряда на так называемом плавающем электроде затвора. Это происходит за счет приложения подходящих напряжений к линиям слов и разрядным линиям запоминающего устройства. При рабочих условиях считывания с низкими напряжениями обычно 5 вольт, никакие заряды не могут переодолеть потенциальный барьер изоляции так, что однажды накопленный заряд сохраняется. При программировании и стирании в противоположность этому между управляющим затвором и истоком/стоком/подложкой прикладывают более высокие напряжения обычно порядка 17 вольт. Эти напряжения обозначают в последующем как высокие напряжения, так как они превосходят по абсолютной величине напряжение питания. Вследствие высокой напряженности поля электроны могут туннелировать через потенциальный барьер изоляции (эффект Фоулера-Нордхайма) или возникшие вблизи стока горячие электроны могут преодолевать изоляцию (эффект каналирования горячих электронов). Так как напряжение питания запоминающей схемы обычно составляет порядка 5 вольт, должны предусматриваться схемы управления для подводимых извне или получаемых внутри программирующих и стирающих напряжений, которые могут селективно включать эти напряжения на запоминающие ячейки (или, соответственно, линию слов и разрядную линию). По схемно-техническим и технологическим сображениям является предпочтительным ограничивать диапазон напряжения по меньшей мере одной управляющей линии (разрядной линии или линии слов) до напряжения, равного или меньше значения напряжения питания, и применять высокие напряжения только на другой управляющей линии. Как следствие для программирования и стирания на линиях должны селективно включаться как положительные, так и отрицательные высокие напряжения.

Из Y. Yatsuda и др., IEEE J. Solid-State Circuits, Vol. sc-20. No. 1., стр. 144-151, 1985 известна высоковольтная схема управления для положительных напряжений, которая использует внешний такт (Clock). Выполненная на n-МОП транзисторах схема, однако, не в состоянии переключать отрицательные высокие напряжения. Кроме того, схема требует относительно большой емкости С, чтобы иметь возможность давать достаточно высокий зарядный ток, чтобы нагрузка могла заряжаться во время от 50 до 100 мкс.

Из ЕР 320916 В1 стала известна схема управления для энергонезависимого, электрически стираемого и программируемого полупроводникового запоминающего устройства, которое может переключать как положительные, так и отрицательные высокие напряжения и использует внешний такт. Эта схема базируется на принципе придания в соответствие каждой нагрузке собственного генератора высокого напряжения, который генерирует необходимое отрицательное высокое напряжение. Количество необходимых каскадов генератора, однако, увеличивается с абсолютной величиной высокого напряжения.

При более высоких значениях напряжения эта концепция требует большой занимаемой площади. В качестве дальнейшего недостатка известная схема в режиме стирания (отрицательное высокое напряжение) в неселектированном случае не дает чистого уровня нуль вольт. В фазе подготовки определенным значением напряжения на нагрузку наносится предварительный заряд. Во время собственно процесса стирания уровень ограничивается только через последовательное включение n-МОП-транзистора и нескольких, то есть двух или больше р-МОП-транзисторов. За счет этого известная схема подвержена также перекрестным помехам. В режиме считывания (напряжение +5 вольт) и в режиме записи (напряжение +15 вольт) уровни нуль вольт также не являются чистыми. Вместо этого выходное напряжение составляет величину запускающего напряжения р-МОП-транзистора. Предложение использовать транзистор с запускающим напряжением нуль вольт, смещает проблему в область более сложной и таким образом более невыгодной с точки зрения затрат технологии.

Из IEEE Journal of Solid-State Circuits, том 27, Nr. 11, 1 ноября 1992, стр. 1547-1553, ХР000320441, Toshi-katsu Jinbo и др. "A 5-V-only 16-MB Flash Memory with Sector Erase Mode" известно полупроводниковое запоминающее устройство согласно, ограничительной части пункта 1 формулы изобретения, в котором предусмотрена схема управления в качестве Row-Main-декодера со схемными блоками А и В. Схемный блок А, который также обозначается как обычный блок, подключен после n-МОП-транзистора с обеднением канала и является активным во время программного режима работы. Схемный блок В для включения отрицательного напряжения служит в первую очередь для того, чтобы преобразовывать положительный уровневый сигнал в отрицательный уровень напряжения режима работы стирания. Для этого на схемный блок В подают отрицательное высокое напряжение - 13 вольт из каскада накачки заряда и включают через управляющий сигнал ERA. Эта известная схема управления позволяет таким образом производить селекцию отдельной линии слов и управление отрицательным напряжением стирания, наряду с управлением 5 В или, соответственно, 0 В для режима считывания. Хотя функция известной схемы управления кажется сравнимой с функцией, соответствующей изобретению схемы, лежащие в основе обеих схем конструктивные концепции существенно отличаются друг от друга.

Следующая схема управления для запоминающих ячеек ЭСППЗУ известна из US-A-4823318. Также и эта схема управления отличается существенными конкретными признаками от соответствующей изобретению схемы управления.

Из. US-A-4742492 известна следующая схема управления, цель которой заключается в том, чтобы поставлять попеременно на конденсатор, включенный на стороне выхода, напряжения -Vgg, -Vpp и +Vpp, создаваемые тремя генераторами накачки заряда. Для этого в зависимости от приложенного на входной линии управляющего сигнала включают соответственно один из трех генераторов накачки заряда. Также и эта схема управления отличается от соответствующей изобретению схемы управления отдельными схемными признаками.

В основе настоящего изобретения поэтому лежит задача разработки устройства типа, приведенного в преамбуле описания, которое схемно-технически является более простым, требует меньшей площади, имеет в целом меньшее потребление мощности и по возможности малые поперечные токи, и при этом во всех рабочих состояниях обеспечивает сглаженные уровни напряжения, в частности, также сглаженный нулевой (без пульсаций) уровень напряжения.

Эта задача согласно изобретению решается устройством, согласно пункту 1 формулы изобретения.

Согласно изобретению предусмотрено, что для управления избирательной схемой сигнала селекции группы запоминающих ячеек для рабочих состояний стирание и сохранение содержания данных запоминающих ячеек предусмотрена соответствующая всем запоминающим ячейкам одной группы схема управления с одной единственной управляющей линией для связи со всеми запоминающими ячейками выбранной группы, причем на управляющей линии к выбранной группе запоминающих ячеек выборочно подключается стирающее или опорное напряжение.

Соответствующая изобретению концепция схемы решает названные во вводной части проблемы простым образом и предоставляет по сравнению с ранее известными решениями ряд преимуществ. За счет предусматривания приданной в соответствие совместно всем запоминающим ячейкам одной группы схемы управления с одной единственной управляющей линией для активного возбуждения или, соответственно, включения как стирающего напряжения (отрицательное высокое напряжение), так и опорного напряжения (например, с точно определенным уровнем нуль вольт) схемы генерации высокого напряжения схемно-технически могут быть выполнены развязанно от схемы управления в виде отдельных компонентов схемы. В отличие от известного уровня техники не требуется приводить в соответствие с каждой нагрузкой, причем в качестве нагрузки обозначается подлежащая возбуждению схемой управления линия и соответствующие схемные компоненты (например, линия слов), собственный генератор высокого напряжения, который генерирует необходимое стирающее напряжение (отрицательное высокое напряжение). С учетом необходимого числа генераторных каскадов, которое возрастает с абсолютной величиной высокого напряжения, известная ранее концепция при более высоких значениях напряжения является невыгодной с точки зрения занимаемой площади (т.е. является излишне материалоемкой). По сравнению с известными решениями настоящее изобретение позволяет централизованно обеспечивать группу запоминающих ячеек требуемыми значениями высокого напряжения, которое подводят к схеме управления либо снаружи, либо от изготовленной на той же самой полупроводниковой подложке схемы генерации высокого напряжения. Сама схема управления может быть выполнена схемно-технически более просто и состоять только из немногих конструктивных элементов. Так как схема управления по причинам максимальной экономии площади должна реализовываться, как правило, в ячеистом растре, преимущество возможно простого схемно-технического выполнения схемы управления является предпочтительным с точки зрения высокой плотности интеграции. Одновременно схема управления требует малой потребляемой мощности и в основном не имеет поперечных токов, которые могли бы способствовать потерям мощности. В частности, при реализации в n-карманной КМОП-технологии эти преимущества приобретают особенное значение за счет того, что все n-МОП-транзисторы имеют общий вывод подложки (массу), и таким образом для включения отрицательных напряжений могут применяться только р-МОП-транзисторы.

С соответствующей изобретению схемой управления удается селективно, например, в зависимости от соответствующего сигнала, прикладывать к запоминающим ячейкам, как стирающее напряжение (отрицательное высокое напряжение), так и опорное напряжение (уровень нуль вольт) в определенной форме и без потерь через одну единственную управляющую линию. Так как запоминающие ячейки образуют сравнительно большую емкостную нагрузку, выгодным является подключать напряжение активно, т. е. без существенных задержек во времени, что удается посредством соответствующей изобретению схемы управления, во всяком случае, с минимальными временными задержками.

Для различения, должна ли группа запоминающих ячеек стираться, или должны сохраняться содержащиеся в них данные согласно изобретению предусмотрено, что схема управления для выбора, подаваемого на управляющую линию стирающего напряжения и опорного напряжения является управляемой сигналом селекции, производимым включенной перед схемой управления схемой селекции. Целесообразно, чтобы схема сигнала селекции была подключена в большинстве случаев к и без того имеющемуся в полупроводниковом запоминающем устройстве адресному декодеру или выполнена интегрированной в полупроводниковом запоминающем устройстве. Это позволяет не только полностью стирать большие области полупроводникового запоминающего устройства, но и также внутри больших циклов стирания сохранять только содержания данных отдельных выбранных групп запоминающих ячеек, в результате чего можно уменьшить организационные затраты программ обработки информации. Другое преимущество получается за счет того, что поскольку опорное напряжение является по абсолютной величине меньше стирающего напряжения, схема управления требует меньше времени для включения опорного напряжения, чем для включения стирающего напряжения. За счет нацеленного выбора подлежащих стиранию запоминающих ячеек время, необходимое для процесса стирания может быть сокращено.

Далее согласно изобретения предусмотрено, что схема управления для активного включения стирающего напряжения и опорного напряжения на управляющей линии имеет действующую в зависимости от сигнала выбора или сигнала селекции схему накачки, которая по выбору включает стирающее напряжение и опорное напряжение без местной генерации этих напряжений.

В форме развития изобретения может быть дальше предусмотрено, что полупроводниковое запоминающее устройство может эксплуатироваться в третьем рабочем состоянии, которое по выбору может быть придано в соответствие программированию, считыванию или сохранению содержания данных запоминающих ячеек, причем полупроводниковое запоминающее устройство содержит связанную через переключающее устройство со схемой управления схему генерации программирующего напряжения для снабжения схемы управления имеющим противоположный знак относительно стирающего напряжения и превосходящим значение напряжения питания программирующим напряжением для программирования запоминающей ячейки, а приданное в соответствие схеме управления переключающее устройство для селективной выдачи подлежащего приложению к схеме управления программирующего напряжения, или подлежащего приложению к схеме управления считывающего напряжения, или подлежащего приложению к схеме управления опорного напряжения является управляемым посредством линии выбора состояния к выбранной группе запоминающих ячеек. За счет этого все напряжения, которые требуются для программирования, считывания, стирания и поддержания содержания данных запоминающих ячеек, могут прикладываться через одну единственную линию.

Для приложения напряжений, подведенных от схемы генерации программирующего напряжения, или меньших по абсолютной величине напряжений того же знака может быть предусмотрено, что перед переключающим устройством может быть включена приданная схеме генерации программирующего напряжения схема возбуждения, которая выдает на переключающее устройство напряжение, значения которого соответствуют третьему рабочему состоянию для программирования, считывания и сохранения содержания данных запоминающих ячеек. Это позволяет приложение в принципе любого количества напряжений со знаком, противоположным знаку стирающего напряжения. При этом стабильность этих уровней напряжения зависит в значительной степени от качества схемы возбуждения.

Для связи схемы возбуждения со схемой управления может быть предусмотрено, что схема управления содержит связанный с переключающим устройством первый вход напряжения, к которому в первом и втором рабочем состоянии приложены опорное напряжение, а в третьем рабочем состоянии приложены выдаваемые схемой возбуждения уровни напряжения.

Для связи схемы генерации стирающего напряжения со схемой управления может быть предусмотрено, что схема управления содержит связанный со схемой генерации стирающего напряжения второй вход напряжения, к которому в первом и втором рабочем состоянии приложены стирающее напряжение и в третьем рабочем состоянии стирающее напряжение или напряжение, которое по абсолютной величине меньше или равно программирующему напряжению.

Для подключения опорного напряжения и для связи схемы возбуждения со схемой управления может быть предусмотрено, что схема управления содержит подлежащую активированию через первый внутренний тактовый вход и включенную между первым входом напряжения и управляющей линией первую схему накачки, которая в первом рабочем состоянии служит блокировкой между первым входом напряжения и управляющей линией, во втором рабочем состоянии работает в качестве схемы накачки от первого входа напряжения к управляющей линии и в третьем рабочем состоянии работает в качестве схемы накачки между связанной с первым входом напряжения схемой возбуждения и управляющей линией. Первая схема накачки может производить по выбору две различные меры. Во-первых, может быть предусмотрено подключение опорного напряжения посредством механизма накачки, чтобы предотвратить провал опорного напряжения вследствие токов утечки или помех, которые обуславливают уменьшение однажды нанесенного заряда. Далее может быть предусмотрено, что первая схема накачки связывает напряжения, подведенные от схемы возбуждения и имеющие знак, противоположный стирающему напряжению, с управляющей линией.

Для активного включения стирающего напряжения может быть предусмотрено, что схема управления содержит подлежащую активированию через второй внутренний тактовый вход вторую схему накачки, включенную между вторым входом напряжения и управляющей линией, которая в первом рабочем состоянии работает в качестве схемы накачки от второго входа напряжения к управляющей линии и во втором и третьем рабочем состоянии в качестве схемы блокировки между вторым входом напряжения и управляющей линией. Вторая схема накачки обуславливает при этом активное проключение стирающего напряжения посредством механизма накачки, чтобы предотвратить провал стирающего напряжения вследствие токов утечки или помех, которые обуславливают уменьшение однажды нанесенного заряда, и вызывает, с другой стороны при активном проключении опорного напряжения или при связи подведенных от схемы возбуждения напряжений блокировку стирающего напряжения.

По причинам надежности эксплуатации может быть предусмотрено, что первая схема накачки содержит связанный с внешне управляемым входом сброса в исходное состояние переключатель сброса в исходное состояние, чтобы в первом рабочем состоянии схема накачки работала надежно в качестве схемы блокировки. Может быть предусмотрено управление входом сброса в исходное состояние при исходящей от адресного декодера смене адреса, чтобы первая схема накачки прежде всего надежно блокировала.

В качестве еще одной меры может быть предусмотрено, чтобы вторая схема накачки содержала управляемый через первый внутренний тактовый вход, деактивирующий переключатель, чтобы во втором и третьем рабочем состоянии вторая схема накачки работала надежно в качестве схемы блокировки. За счет этого дополнительно обеспечено, что при подключении опорного напряжения или при связи подведенных от схемы возбуждения напряжений стирающее напряжение блокируется.

Для схем генерации напряжения может быть предусмотрено, что полупроводниковое запоминающее устройство для по меньшей мере одной взаимосвязанной группы запоминающих ячеек одной линии слов или разрядной линии, расположенных на полупроводниковой подложке в виде матрицы в местах пересечения линий слов и разрядных линий запоминающих ячеек, содержит одну единственную схему генерации стирающего напряжения и одну единственную схему генерации программирующего напряжения, которые приданы в соответствие по меньшей мере одной схеме управления. Это позволяет применение глобально генерированных напряжений, которые могут генерироваться как на полупроводниковой подложке, так и подводиться извне. В обоих случаях это приводит к экономии площади монтажа по сравнению с известными ранее схемами.

Для активирования первой и второй схемы накачки может быть предусмотрено, что схеме управления придана в соответствие схема селекции, которая в зависимости от приложенного к входу селекции сигнала селекции придает в соответствие приложенный на внешнем тактовом входе внешний тактовый сигнал первому или второму внутреннему тактовому выходу. Для активирования схем накачки может быть предусмотрен тактовый сигнал, который селективно подводят к первой или второй схеме накачки.

При этом для активирования первой и второй схемы накачки, например, может быть предусмотрено, что схема селекции при логическом нуле на входе селекции прикладывает внешний тактовый сигнал противофазно на первый внутренний тактовый выход и устанавливает второй внутренний тактовый выход на логическую единицу, а при логической единице на входе селекции прикладывает внешний тактовый сигнал противофазно на второй внутренний тактовый выход и устанавливает первый внутренний тактовый выход на логический нуль.

Для связи схемы селекции со схемой управления может быть предусмотрено, что в первом и втором рабочем состоянии первый внутренний тактовый выход схемы селекции связан с первым внутренним тактовым входом и второй внутренний тактовый выход схемы селекции связан со вторым внутренним тактовым входом. Так как в первом и втором рабочем состоянии соответственно является активной одна из обоих схем накачки, в этих рабочих состояниях могут быть предусмотрены тактовые сигналы.

Для связи схемы возбуждения через схему управления с запоминающими ячейками может быть предусмотрено, что переключатели первой и второй схемы накачки и приданный в соответствие второй схеме накачки деактивирующий переключатель соответственно содержат МОП-полевые транзисторы с одним общим, внешне управляемым выводом подложки. За счет этого можно прикладывать на полупроводниковую подложку различные потенциалы, что позволяет связывание подведенных от схемы возбуждения напряжений, которые имеют знак, противоположный стирающему напряжению.

В особенно простой схемно-технической реализации схемы накачки может быть выгодным, что к первому внутреннему тактовому входу подключен первый конденсатор, а ко второму внутреннему тактовому входу подключен второй конденсатор.

Для выбора различных подводимых от схемы возбуждения уровней напряжения может быть предусмотрено, что схема возбуждения по выбору в первом режиме работы в зависимости от приложенного на входе селекции возбуждения сигнала селекции возбуждения выдает уровень напряжения для программирования или для сохранения содержания данных, а во втором режиме работы выдает уровень напряжения для считывания. Это позволяет исключительно в зависимости от сигналов, которые не должны иметь особой электрической мощности, прикладывать к одной единственной управляющей линии напряжения различного знака, причем напряжения обоих знаков могут превышать напряжение питания.

В последующей форме выполнения изобретения может быть предусмотрено, что на общем, внешне управляемом выводе подложки в первом и втором рабочем состоянии приложено опорное напряжение, в третьем рабочем состоянии и первом режиме работы приложено программирующее напряжение и в третьем рабочем состоянии и втором режиме работы приложено считывающее напряжение.

Чтобы сделать возможными быстрые времена переключения, может быть предусмотрено, что в третьем рабочем состоянии на первом внутреннем тактовом входе непосредственно после переключения в третье рабочее состояние приложен тактовый сигнал с заранее определенной временной длительностью. В третьем рабочем состоянии является достаточным прикладывать тактовый сигнал только в начальной фазе и после этого поддерживать его на уровне, который удерживает переключатель накачки первой схемы накачки открытым.

В дальнейшей предпочтительной форме выполнения может быть предусмотрено, что схема селекции содержит второй внешний тактовый вход для приложения отдельного от внешнего тактового сигнала второго внешнего тактового сигнала и приданную в соответствие второму внутреннему тактовому выходу и обоим тактовым входам схему амплитудного удвоителя, прикладывает при логическом нуле на входе селекции внешний тактовый сигнал противофазно на первый внутренний тактовый выход и устанавливает второй внутренний тактовый выход на логическую единицу, и при логической единице на входе селекции прикладывает внешний тактовый сигнал противофазно с увеличенной по сравнению с внешним тактовым сигналом амплитудой на второй внутренний тактовый выход и устанавливает первый внутренний тактовый выход на логический нуль. В дальнейшей форме выполнения, в частности, второй схемы накачки может быть предусмотрено прикладывать тактовые сигналы, которые превышают напряжение питания, чтобы надежно управлять переключателями контура накачки.

С учетом примененной технологии и физической конструкции запоминающих ячеек может быть предусмотрено, что опорное напряжение имеет значение нулевого напряжения, напряжение питания значение порядка +5 вольт, стирающее напряжение значение порядка - 12 вольт, а программирующее напряжение значение порядка +18 вольт.

Дальнейшие признаки, преимущества и целесообразные формы выполнения изобретения следуют из описания примеров выполнения с помощью чертежей, на которых показано:

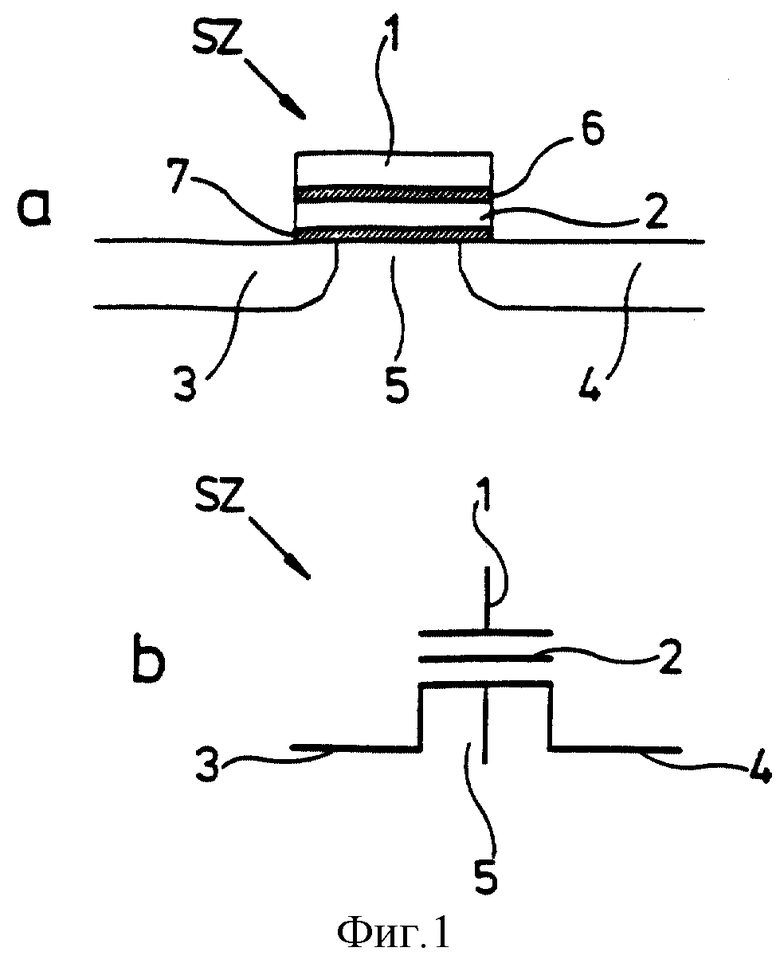

фиг. 1а и 1b - схематическая конструкция запоминающей ячейки энергонезависимого, электрически стираемого программируемого полупроводникового запоминающего устройства;

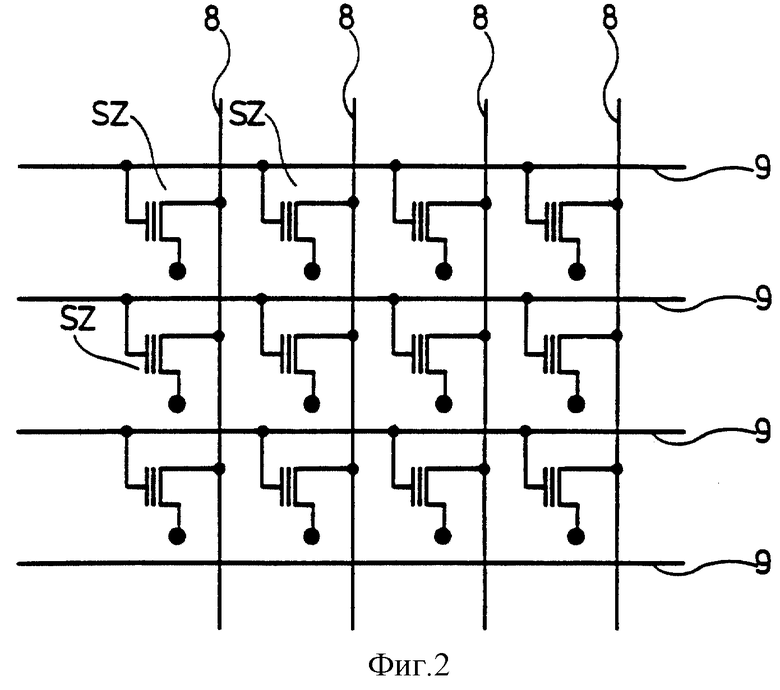

фиг. 2 - расположение запоминающих ячеек и их связь с разрядными линиями и линиями слов;

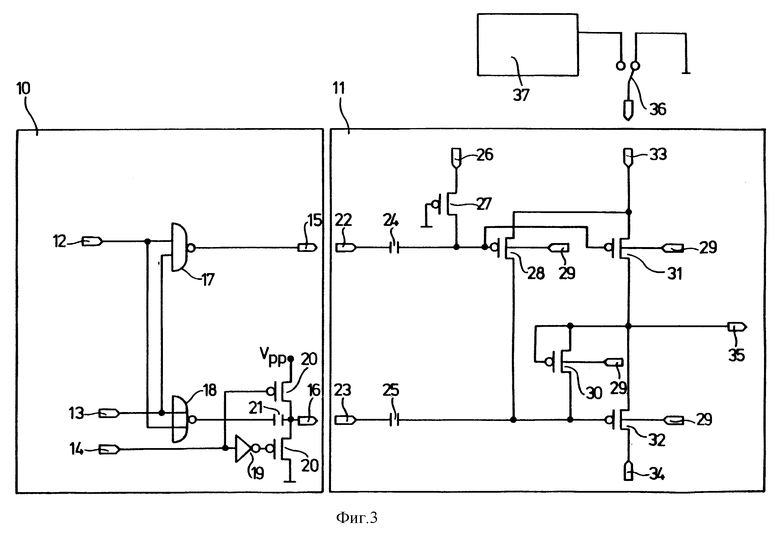

фиг. 3 - схематическое представление схемы соединений первого примера выполнения схемы управления со схемой селекции с амплитудным удвоителем;

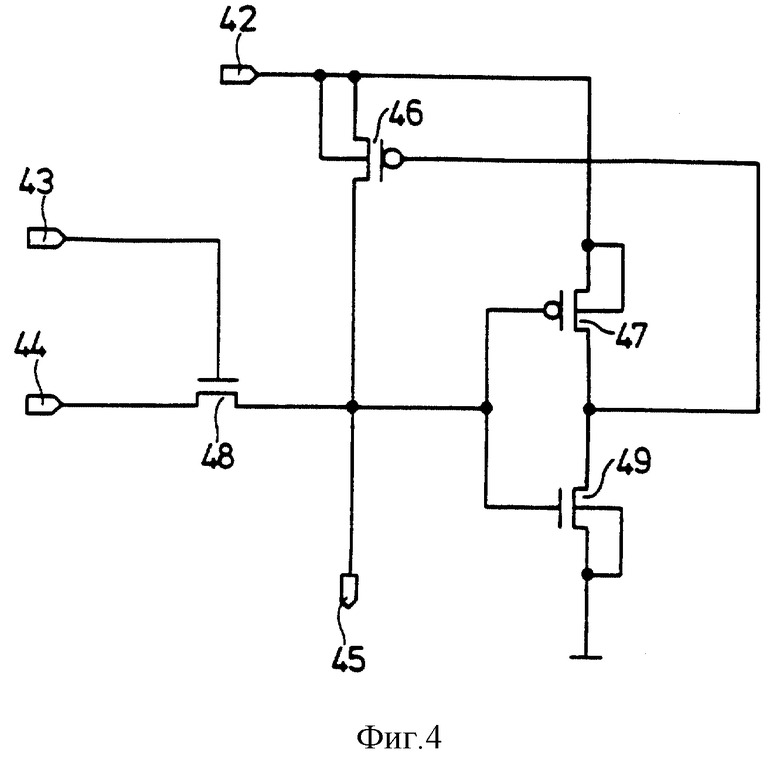

фиг. 4 - схематическое представление схемы соединений схемы возбуждения для положительных напряжений;

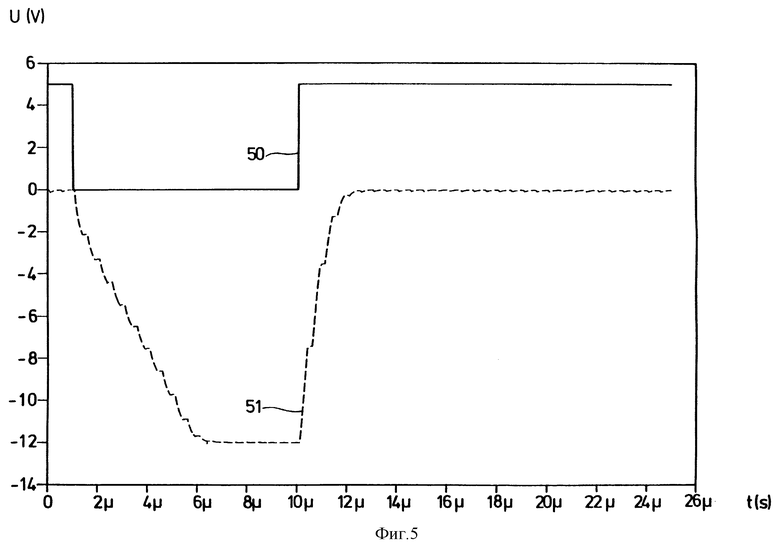

фиг. 5 - схематическое представление результата моделирования с напряжениями, приложенными на входе селекции и на линии управления, в качестве функций времени после приложения стирающего напряжения и опорного напряжения к линии слов;

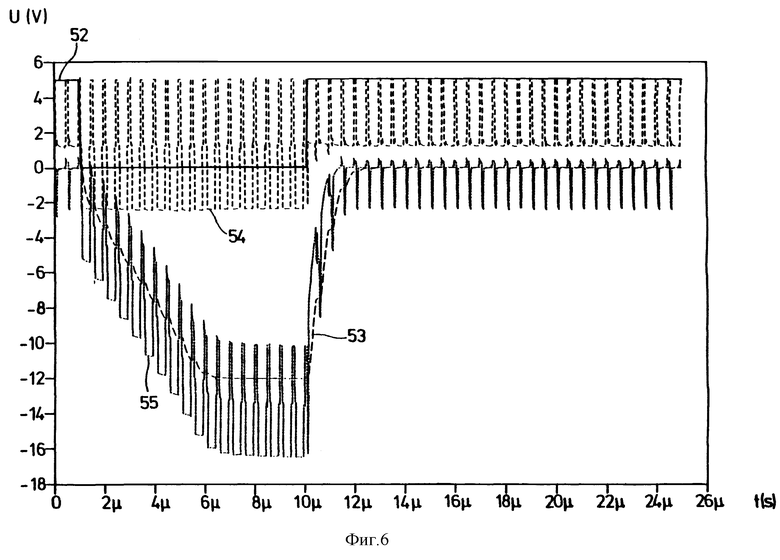

фиг. 6 - схематическое представление результата моделирования с напряжениями, приложенными на входе селекции, на линии управления, на втором внутреннем тактовом входе и на управляющем входе транзистора переключения накачки второй схемы накачки, в качестве функций времени после приложения стирающего напряжения и опорного напряжения к линии слов;

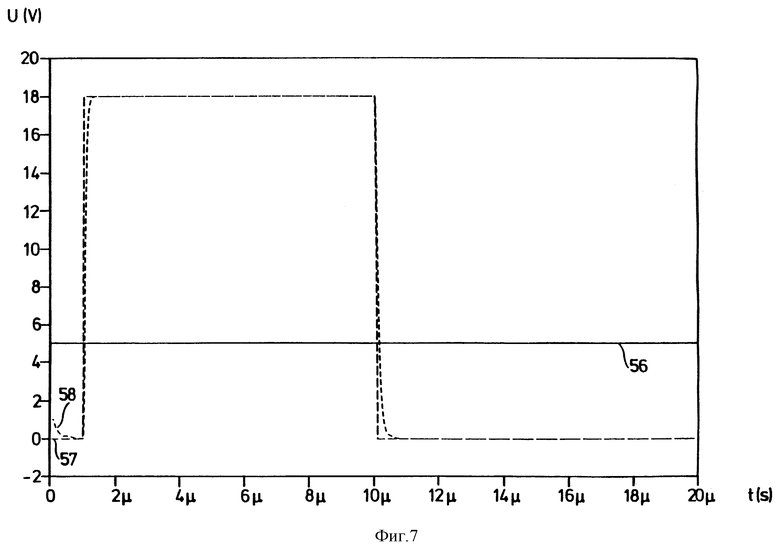

фиг. 7 - схематическое представление результата моделирования с напряжениями, приложенными на входе селекции, на выходе схемы возбуждения и на управляющей линии, в качестве функций времени после приложения программирующего напряжения и опорного напряжения к линии слов;

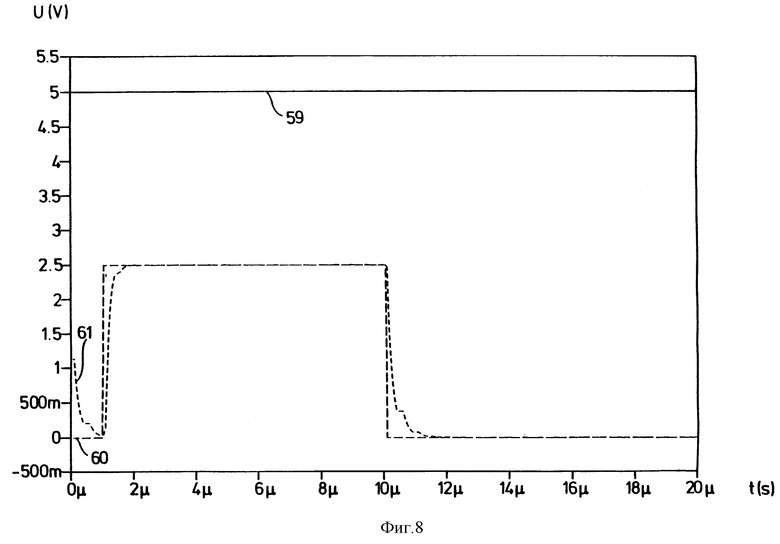

фиг. 8 - схематическое представление результата моделирования с приложенными на входе селекции, на выходе схемы возбуждения и на управляющей линии напряжениями в качестве функций времени при приложении считывающего напряжения и опорного напряжения к линии слов;

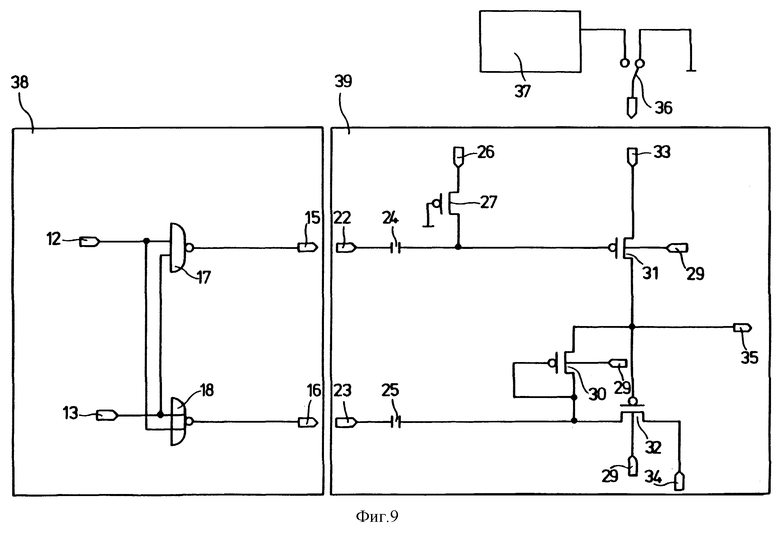

фиг. 9 - схематическое представление схемы соединений второго примера выполнения схемы управления со схемой селекции без амплитудного удвоителя; и

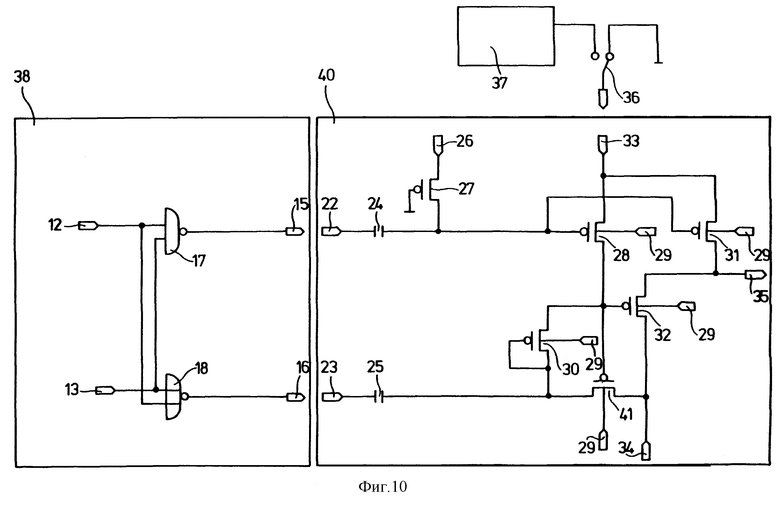

фиг. 10 - схематическое представление схемы соединений третьего примера выполнения схемы управления со схемой селекции без амплитудного удвоителя.

С помощью фиг. 1а и 1b должна вначале поясняться конструкция и принцип действия электрически программируемого и стираемого полупроводникового запоминающего устройства с множеством запоминающих ячеек SZ. Каждая запоминающая ячейка SZ состоит из управляющего электрода 1, потенциально развязанного электрода 2, области истока 3, области стока 4, области подложки 5 и изоляторов 6 и 7. Изолятор 6б расположен между управляющим электродом 1 и потенциально развязанным электродом 2, изолятор 7 расположен между потенциально развязанным электродом 2, с одной стороны, и областью истока 3, областью стока 4 и областью подложки 5, с другой стороны. Потенциально развязанный электрод 2, окруженный изоляторами 6 и 7, находится между управляющим электродом 1, областью истока 3 и областью стока 4. Запоминание информации соответствует нанесению и удалению зарядов на потенциально развязанном электроде 2. Это происходит за счет приложения подходящих напряжений между управляющим электродом 1 и областью стока 4. Для считывания к управляющему электроду 1 прикладывают положительное относительно области стока 4 напряжение, которое типичным образом составляет около +2,5 вольт и таким образом имеет порядок величины напряжения питания, и которое является не достаточным, чтобы электроны или дырки могли преодолеть изолятор. Для программирования к управляющему электроду 1 прикладывают положительное высокое напряжение, которое типичным образом составляет около +18 вольт и таким образом превышает напряжение питания, чтобы инжектировать электроны в потенциально развязанный электрод 2. Для стирания отрицательное высокое напряжение, которое типичным образом составляет около -12 вольт и таким образом по абсолютной величине превышает напряжение питания, прикладывают к управляющему электроду 1, чтобы инжектировать дырки в потенциально развязанный электрод 2. При программировании и стирании вследствие высоких напряженностей поля электроны или, соответственно, дырки могут туннелировать через потенциальный барьер изолятора 7 (эффект Фоулера-Нордхайма) или возникшие вблизи области стока 4 горячие электроны могут преодолевать изолятор 7 ("эффект каналирования горячих электронов").

В типичном запоминающем устройстве согласно фиг. 2 при считывании запомненных содержаний данных из запоминающих ячеек SZ разрядная линия 8 соединяется с выводом истока ячеек или остается отсоединенной. Предусмотрены (не представленные более подробно), приданные в соответствие разрядным линиям 8 усилители считывания, которые детектируют состояние ячейки путем обнаружения текущего через запоминающую ячейку SZ тока или путем обнаружения потенциального смещения на соответствующей разрядной линии 8. Ссылочные позиции 9 обозначают линии слов, которые для адресации запоминающих ячеек SZ соединены с (не представленной более подробно) схемой декодирования адреса. Подробности компоновки и принципа действия такого запоминающего устройства являются известными специалисту и не требуют здесь более подробного описания.

Фиг. 3 показывает первый пример выполнения соответствующего изобретению устройства со схемой селекции 10 и со схемой управления 11. Схема селекции 10 содержит вход селекции 12, первый внешний тактовый вход 13, второй внешний тактовый вход 14, первый внутренний тактовый выход 15 и второй внутренний тактовый выход 16. Далее схема селекции 10 состоит из логического элемента И с отрицанием 17 и логического элемента ИЛИ с отрицанием 18. Соответственно первые входы обоих логических элементов 17 и 18 связаны с входом селекции 12, а соответственно вторые входы обоих логических элементов 17 и 18 связаны с первым внешним тактовым входом 13. Выход логического элемента И с отрицанием 17 соответствует первому внутреннему тактовому выходу 15 схемы селекции 10. Выход логического элемента ИЛИ с отрицанием 18 соединен через конденсатор 21 со вторым внутренним тактовым выходом 16 схемы селекции 10. Точно также на втором внутреннем тактовом выходе 16 имеется, точка связи двух последовательно включенных транзисторов 20. К состоящей из двух транзисторов 20 последовательной схеме приложено напряжение питания Vpp. Управляющий вход одного из транзисторов 20 соединен непосредственно с тактовым входом 14, в то время как управляющий вход другого из двух транзисторов 20 соединен через логический элемент НЕ 19 со вторым внешним тактовым входом 14. К управляющим входам обоих транзисторов 20 за счет этого постоянно приложены взаимно инверсные цифровые сигналы. Конструктивные элементы 19-21 образуют схему амплитудного удвоителя. Схема управления 11 имеет пять входов 22, 23, 26, 33, 34 и один единственный выход 35. Входы 22 и 23 представляют собой связанные с внутренними тактовыми выходами 15, 16 схемы селекции 10 внутренние тактовые входы схемы управления 11. Вход 26 является внешне управляемым входом сброса в исходное состояние. Первый вход напряжения 33 в зависимости от переключающего устройства 36 в первом и втором рабочем состоянии связан с массой, которая во всех примерах выполнения представляет собой потенциал опорного напряжения, или в третьем рабочем состоянии связан с подводящей положительные напряжения схемой возбуждения 37. Второй вход напряжения 34 связан со схемой генерации стирающего напряжения, создающей отрицательное высокое напряжение. Через управляющую линию 35 и соответствующую линию слов 9 (см. фиг. 2) управляются управляющие электроды 1 запоминающих ячеек SZ. Первый внутренний тактовый вход 22 через конденсатор 24 соединен с управляющим входом работающего в качестве переключателя накачки транзистора 31. Между управляющим входом транзистора 31 и входом сброса в исходное состояние 26 промежуточно включен работающий в качестве переключателя сброса в исходное состояние транзистор 27, управляющий вход которого приложен к массе. Второй внутренний тактовый вход 23 через конденсатор 25 соединен с управляющим входом работащего в качестве переключателя накачки транзистора 32. Между первым входом напряжения 33 и управляющим входом транзистора 31 промежуточно включен работающий в качестве деактивирующего переключателя транзистор 28, который имеет совместно с транзистором 31 управляющий вход. Между управляющей линией 35 и управляющим входом транзистора 32 включен работащий в качестве переключателя обратной связи транзистор 30, управляющий вход которого также связан с управляющей линией 35. Транзисторы 28, 30, 31 и 32 имеют общий, управляемый снаружи вывод подложки 29. Во всех примерах выполнения предусмотрено, что к первому входу напряжения 33 в третьем рабочем состоянии прикладывают подведенное от схемы возбуждения 37 положительное напряжение и в первом и втором рабочем состоянии уровень нуль вольт. Точно также во всех примерах выполнения предусмотрено, что к входу 34 в первом и втором рабочем состоянии прикладывают подведенное от схемы генерации стирающего напряжения отрицательное высокое напряжение, а в третьем рабочем состоянии или подведенное от схемы генерации стирающего напряжения отрицательное высокое напряжение или напряжение, которое по абсолютной величине является меньшим или равным, чем программирующее напряжение. Эти напряжения подводят или от внешних или от находящихся на полупроводниковой подложке 5 схем генерации напряжения, которые на фигурах более подробно не представлены. При этом в принципе требуются только две генерирующие напряжение схемы, одна для положительного напряжения для считывания и положительного высокого напряжения для программирования и другая для отрицательного высокого напряжения для стирания.

С помощью представленного на фиг. 3 первого примера выполнения в последующем поясняется принцип действия. Схема управления 11 работает в трех названных рабочих состояниях. В первом и втором рабочем состоянии первый вход напряжения 33 подключен через переключающее устройство 36 к массе. Если на входе селекции 12 приложен сигнал, соответствующий первому рабочему состоянию, через управляющую линию 35 и приданную соответствующим запоминающим ячейкам SZ линию слов 9 к управляющим электродам 1 прикладывают имеющееся на втором входе напряжения 34 отрицательное высокое напряжение порядка -12 вольт, чтобы для стирания инжектировать дырки в потенциально развязанные электроды 2 запоминающих ячеек SZ. Если на входе селекции 12 приложен сигнал, соответствующий второму рабочему состоянию, через управляющую линию 35 и приданную соответствующим запоминающим ячейкам SZ линию слов 9 лежащий на первом входе напряжения 33 потенциал массы прикладывается к управляющим электродам 1 запоминающих ячеек SZ. В третьем рабочем состоянии приложенные на первом входе напряжения 33 подведенные от схемы возбуждения 37 через переключающее устройство 36 положительные напряжения подают на управляющую линию 35. В первом рабочем состоянии на входе селекции 12 приложено нулевое напряжение, за счет которого приложенный на первом внешнем тактовом входе 13 тактовый сигнал с двойной амплитудой U23,max подают на второй внутренний тактовый выход 16 и таким образом на второй внутренний тактовый вход 23. Выполненная из логического элемента НЕ 19, обоих транзисторов 20 и конденсатора 21 схема амплитудного удвоителя является необходимой для надежного управления транзистора 32. На втором внутреннем тактовом входе 23 для этого "требуется тактовый сигнал U23 с амплитудой U23,max, которая превосходит запускающее напряжение U32,min транзистора 32 на двойную величину. Для снабжения схемы амплитудного удвоителя 19, 20, 21 к обоим внешним тактовым входам 13, 14 приложены два отдельных тактовых сигнала с верхним уровнем напряжения 5 вольт и нижним уровнем напряжения 0 вольт. За счет приложенного на втором внутреннем тактовом входе 23 тактового сигнала U23 активизируется вторая схема накачки, состоящая из конденсатора 25 и транзистора 32, и пакетно подает приложенное на втором входе напряжения 34 отрицательное высокое напряжение. Приложенное на управляющем входе. транзистора 32 напряжение U32 составлено вначале из приложенного на управляющей линии напряжения U35 и абсолютной величины запускающего напряжения U32,min транзистора 32

U32=U35+/U32,min/

и при запуске тактового сигнала U23 с амплитудой U23,mах на втором внутреннем тактовом входе 23 уменьшается на разницу

dU=U23,max-2/U32,min/

между приложенной на втором внутреннем тактовом входе 23 тактовой амплитудой U23,max и двойной величиной абсолютной величины запускающего напряжения U32,min транзистора 32:

U35-U35-dU.

Вышеприведенные уравнения справедливы, конечно, только, если емкость С25 конденсатора 25 велика по сравнению c паразитными емкостями и емкостями С30, С32 транзисторов 30 и 32. Первый внутренний тактовый выход 15 и тем самым также первый внутренний тактовый вход 22 деактивизированы, что обуславливает то, что переключатель накачки 31 первой схемы накачки служит блокировкой между первым входом напряжения 33 и управляющей линией 35. Вход сброса в исходное состояние 26, кроме как при смене адреса, приложен постоянно к массе. При смене адреса на входе сброса в исходное состояние 26 кратковременно прикладывают напряжение питания, чтобы установить управляющие входы транзисторов 28 и 31 на не отрицательный потенциал. Управляющие входы транзисторов 28 и 31 могут иначе за счет связи выше критической попасть на отрицательный потенциал, в результате чего транзисторы 28 и 31 могли бы быть длительно открытыми. Во втором рабочем состоянии на входе селекции 12 приложен уровень пять вольт, за счет чего приложенный на первом внешнем тактовом входе 13 тактовый сигнал инверсно подключается на первый внутренний тактовый выход 15 и таким образом на первый внутренний тактовый вход 22. С помощью тактового сигнала состоящая из конденсатора 24 и транзистора 31 первая схема накачки активируется и переключает приложенный на первом входе 33 потенциал массы на управляющую линию 35. В противоположность этому второй внутренний тактовый выход 16 и таким образом также второй внутренний тактовый вход 23 является деактивированным, в результате чего переключатель накачки 32 второй схемы накачки служит блокировкой между вторым входом напряжения 34 и управляющей линией 35. В третьем рабочем состоянии на входе селекции 12 также приложен уровень пять вольт, за счет чего приложенный на первом внешнем тактовом входе 13 тактовый сигнал переключается на первый внутренний тактовый вход 22. За счет тактового сигнала активизируется состоящая из конденсатора 24 и транзистора 31 первая схема накачки и переключает на управляющую линию 35 приложенное на первом входе напряжения 33 положительное напряжение, подведенное от схемы возбуждения 37 через переключающее устройство 36. В зависимости от сигналов, приложенных на обоих входах селекции возбуждения 43, 44 схемой возбуждения 37 на первом входе напряжения 33 прикладываются программирующее напряжение, считывающее напряжение или нулевое напряжение. Точно также в третьем рабочем состоянии на внешне управляемых выводах подложки 29 схемой возбуждения 37 прикладываются те же напряжения, что и на первом входе напряжения 33. Для осуществления быстрых времен переключения может быть целесообразным включать такт только в начальной фазе и затем поддерживать его на более низком уровне. За счет этого управляющий вход транзистора 31 остается на отрицательном потенциале, в результате чего транзистор 31 остается открытым. Второй внутренний тактовый выход 16 и тем самым также второй внутренний вход 23 являются деактивированными, за счет чего переключатель накачки 32 второй схемы накачки служит блокировкой между вторым входом напряжения 34 и управляющей линией 35.

Фиг. 4 показывает подробности схемы возбуждения 37, которая подключена к схеме генерации программирующего напряжения, связана через переключающее устройство 36 со схемой управления 11, 39, 40 и вызывает подачу положительных напряжений к схеме управления 11, 39, 40. Схема возбуждения 37 содержит три входа 42, 43, 44 и один выход 45. Выход 45 предусмотрен для связи через переключающее устройство 36 с первым входом напряжения 33 схемы управления 11. Схема возбуждения 37 состоит из четырех транзисторов, двух р-канальных полевых транзисторов 46, 47 и двух n-канальных полевых транзисторов 48, 49. Вход 42 является входом напряжения для подключения к схеме генерации программирующего напряжения или, соответственно, для приложения положительного высокого напряжения, которое типичным образом составляет порядка +18 вольт. Входы 43 и 44 являются входами селекции возбуждения. В зависимости от сигналов, приложенных на входах селекции возбуждения 43 и 44 схема возбуждения 37 или включает приложенное на входе 42 положительное высокое напряжение для программирования, или включает типичным образом имеющее высоту +2,5 вольта частичное напряжение для считывания, или подают потенциал массы для сохранения содержания данных на выход 45 и тем самым на первый вход напряжения 33 схемы управления 11, 39, 40.

На фиг. 5-8 представлены временные характеристики напряжений, приложенных в различных выбранных точках представленной на фиг. 3 схемы.

Фиг. 5 показывает временную характеристику напряжения сигнала 50, приложенного на входе селекции 12, и сигнала 51, приложенного на управляющей линии 35. Путем управления входа селекции 12 происходит переключение между первым и вторым рабочим состоянием. Уровень нуль вольт на входе селекции 12 соответствует первому, а уровень пять вольт второму рабочему состоянию. Если на входе селекции 12 приложен уровень пять вольт, на управляющую линию 35 подают потенциал массы, приложенный на первом входе напряжения 33, который связан через переключающее устройство 36 с массой. При уровне нуль вольт на входе селекции 12 приложенное на втором входе напряжения 34 напряжение стирания, которое здесь составляет порядка -12 вольт, подают на управляющую линию. Процесс накачки длится порядка 5 мкс, пока будет достигнуто ранее определенное напряжение. После переключения на входе селекции в противоположность этому требуется только порядка 2 мкс, пока опорное напряжение будет приложено к управляющей линии.

Представленные на фиг. 6 характеристики напряжения 52, 53, 54, 55 передают тот же процесс, что и на фиг. 5. Представленные на фиг. 6 диаграммы 52 и 53 соответствуют диаграммам 50 или, соответственно, 51 на фиг. 5. Дополнительно на фиг. 6 представлена характеристика напряжения 54 на втором внутреннем тактовом входе 23 и характеристика напряжения 55 на втором переключателе накачки 32. В обоих точках напряжение осциллирует с частотой тактового сигнала. В первом рабочем состоянии амплитуда обоих сигналов 54, 55 составляет порядка 7 вольт, в то время как во втором рабочем состоянии амплитуда обоих сигналов составляет порядка 4 вольт. Приложенный на управляющем входе второго переключателя накачки 32 сигнал 55 соответствует приложенному к управляющей линии 35, амплитудно-модулированному сигналом 54 на втором тактовом входе 23 сигналу 53.

На фиг. 7 представлены диаграммы 56, 57, 58, которые представляют характеристику напряжения 56 на входе селекции 12, характеристику напряжения 57 на первом входе напряжения 33 и характеристику напряжения 58 на управляющей линии 35 в третьем рабочем состоянии. Вход селекции 12 лежит постоянно на 5 вольт, так как приложенные там сигналы 56 являются существенными только для первых двух рабочих состояний. Сравнение характеристики напряжения 57 на первом входе напряжения 33 и характеристики напряжения 58 на управляющей линии 35 показывает, что схема управления 11 переключает подведенное от схемы возбуждения 37 положительное высокое напряжение "приблизительно без задержки. Время задержки составляет меньше порядка 1 мкс.

На фиг. 8 аналогично фиг. 7 представлено переключение подведенного от схемы возбуждения 37 положительного напряжения, причем характеристика напряжения 59 на входе селекции 12, характеристика напряжения 60 на первом входе напряжения 33 и характеристика напряжения 61 на управляющей линии 35 представлена в третьем рабочем состоянии. Вместо программирующего напряжения, которое составляет порядка +18 вольт, прикладывают считывающее напряжение порядка +2,5 вольт. Также в этом случае времена задержки имеют примерно тот же порядок величины, что и при приложении программирующего напряжения, и лежат ниже порядка 1 мкс.

Представленный на фиг. 9 второй пример выполнения соответствующей изобретению схемы управления 39 в основном имеет подобную конструкцию, что и схема управления 11 первого примера выполнения. При этом схема селекции 38 представляет собой вариант схемы селекции 10, сокращенный на схему амплитудного удвоителя 19, 20, 21 и второй внешний тактовый вход 14. Схема селекции 38 состоит из входа селекции 12, первого внешнего тактового входа 13, логического элемента И с отрицанием 17, логического элемента ИЛИ с отрицанием 18 и внутренних тактовых выходов 15 и 16. Схема управления 39 второго примера выполнения также представляет собой сокращенный вариант соответствующей схемы 11 согласно первому примеру выполнения. В ней отсутствует работающий в качестве деактивирующего переключателя транзистор 28, а в транзисторе 32 по сравнению со схемой управления 11 управляющий вход взаимно заменен со связанным с управляющей линией 35 электродом. Транзисторы 30, 31 и 32 имеют общий, внешне управляемый вывод подложки 29.

Схема амплитудного удвоителя 19, 20, 21 для схемы управления 39 не требуется, так как для управления транзистора 32 является достаточным любой малый уровень напряжения U23, шах на втором внутреннем тактовом входе 23. При каждом периоде тактового сигнала U23,max. приложенного на втором внутреннем тактовом входе 23, накопленный на конденсаторе 25 заряд равномерно распределяется на конденсатор 25 и на действующие в качестве емкостной нагрузки CSZ запоминающие ячейки SZ, причем накопленный на конденсаторе 25 заряд является пропорциональным произведению из амплитуды U23, mах приложенного на втором внутреннем тактовом входе 23 тактового сигнала и емкости С25 конденсатора 25.

U32=U35-->U32=U35-(C25-->U23,mах)/(C25+Csz)

Для схемы управления 39, с одной стороны, являются достаточными тактовые сигналы с малой амплитудой U23, mах на втором внутреннем тактовом входе 23, с другой стороны, при невыгодном соотношении емкостей, при котором емкость С25 конденсатора 25 является малой по сравнению с емкостью Csz управляемых запоминающих ячеек SZ, по управляющей линии 35 течет только малый ток, что означает сравнительно долго длящийся процесс накачки. Этот недостаток может быть устранен только за счет конденсатора 25 с высокой емкостью С25 и связанной с этим большой занимаемой площадью на полупроводниковой подложке 5.

Представленный на фиг. 10 третий пример выполнения состоит из схемы управления 40 и из той же схемы селекции 38, что и во втором примере выполнения. Схема управления 40 является выполнением с элементами схем управления 11 и 39 из первых двух примеров выполнения. По сравнению со схемой управления 39 второго примера выполнения схема управления 40 третьего примера выполнения дополнительно содержит транзистор 32, который включен последовательно с транзистором 41 и имеет с ним общий управляющий вход. Точка связи обоих включенных друг за другом транзисторов 32 и 41 соединена со вторым входом напряжения 34. Обращенный от транзистора 32 электрод транзистора 41 связан с конденсатором 25. Работающий в качестве звена обратной связи транзистор 30 в отличие от схемы управления 39 из второго примера выполнения включен между общим управляющим выводом транзисторов 32 и 41 и точкой связи транзистора 41 с конденсатором 25. Транзисторы 28, 30, 31, 32 и 41 имеют общий, внешне управляемый вывод подложки 29.

В первом рабочем состоянии схема управления 40 работает по сравнению со схемами управления 11, 39 следующим образом. Как и в схеме управления 39 схема амплитудного удвоителя 19, 20, 21 не требуется также и в схеме управления 40, чтобы активировать вторую схему накачки 25, 32, 41. За счет обоих транзисторов 32 и 41 по сравнению со схемой управления 39 улучшается выходной коэффициент нагрузки. При каждом периоде приложенного на втором внутреннем тактовом входе 23 тактового сигнала U23 накопленный на конденсаторе 25 заряд распределяется равномерно на конденсатор 25 и действующие в качестве емкостной нагрузки С32, 41 управляющие входы транзисторов 32 и 41, что обуславливает для приложенного к управляющей линии 35 напряжения U35 следующий переход:

U35-->U35-(С25•U23,max)/(C25+C32,4l)≅U35-U23,max

Вследствие сравнительно малой емкости С32,41 связанных управляющих входов транзисторов 32 и 41 для конденсатора 25 не требуется слишком большой емкости C25 и тем самым не требуется слишком большой занимаемой площади на полупроводниковой подложке 5. С малым конденсатором 25 может быть достигнут быстрый процесс накачки. Во втором и третьем рабочем состоянии схема управления 40 работает также, как и схемы управления 11 и 39. В целом схема управления 40 представляет собой синтез схем управления 11 и 39.

Изобретение относится к полупроводниковым запоминающим устройствам. Техническим результатом является уменьшение потребления мощности, малые поперечные токи, чистота уровней напряжения. Устройство содержит множество запоминающих ячеек, схему селекции, схему управления, контур накачки. 19 з.п. ф-лы, 10 ил.

| IEEE Journal of Solid-State Circuits | |||

| Toshikatsu Jinbo et al | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Запоминающее устройство | 1983 |

|

SU1171849A1 |

| US 4823318 А, 18.04.1989 | |||

| US 4742492 А, 03.05.1988 | |||

| СПОСОБ ФОРМИРОВАНИЯ ЭЛЕКТРИЧЕСКИХ ИМПУЛЬСОВ ПЕРЕМЕННОЙ ЧАСТОТЫ СЛЕДОВАНИЯ КАК ФУНКЦИИ ВЕЛИЧИН ДВУХ ЗАДАЮЩИХ НАПРЯЖЕНИЙ ПОСТОЯННОГО ТОКА | 0 |

|

SU182192A1 |

| IEEE Journal of Solid-State Circuits | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

Авторы

Даты

2002-05-10—Публикация

1997-03-20—Подача