Изобретение относится к области радиосвязи и может использоваться для приема телеграфных сигналов и для повышения скорости обработки телеграфных сигналов.

Известны устройства приема телеграфных сигналов, содержащие последовательно соединенные усилитель-ограничитель, автокорреляционный демодулятор и фильтр нижних частот (патент США N 3656064, МКИ H 04 L 27/14, публ. 11.04.72; заявка Великобритании N 2144004, МКИ H 03 D 3/06, публ. 20.02.85; заявка Японии N 5737141, МКИ H 04 L 27/22, публ. 07.08.82), а также известно устройство, содержащее последовательно соединенные усилитель-ограничитель, смеситель частот, фильтр нижних частот, формирователь импульсов, автокорреляционный демодулятор, фильтр нижних частот и выходной триггер уровня, а также блок управления, выходы которого соединены с входами формирователя сигналов сетки частот и автокорреляционного демодулятора, выходы формирователя сигналов сетки частот соединены с вторым входом смесителя частот и вторым входом автокорреляционного демодулятора (авт.св. СССР N 760475, МКИ H 04 L 27/14, 27/22 от 28.11.77).

Наиболее близким по технической сущности является устройство обработки телеграфных сигналов, содержащее последовательно соединенные усилитель-ограничитель, демодулятор, фильтр нижних частот, формирователь уровня (прототип - описание изобретения к авт.св. 1510106 от 19.08.87). Однако известное устройство имеет низкую скорость обработки телеграфных сигналов.

Задачей, на решение которой направлено предлагаемое изобретение, является повышение скорости обработки телеграфных сигналов.

Решение задачи достигается тем, что в известное устройство приема телеграфных сигналов, содержащее последовательно соединенные демодулятор, интегратор отсчетов и формирователь уровня, выход которого является выходом устройства, а вход демодулятора является входом устройства, введен вычислитель сумм, вход которого соединен с выходом интегратора отсчетов, а выход с входом формирователя уровня.

Сопоставительный анализ с прототипом показывает, что введение существенных отличительных признаков составляет новизну и позволяет, как будет показано ниже, решить поставленную задачу.

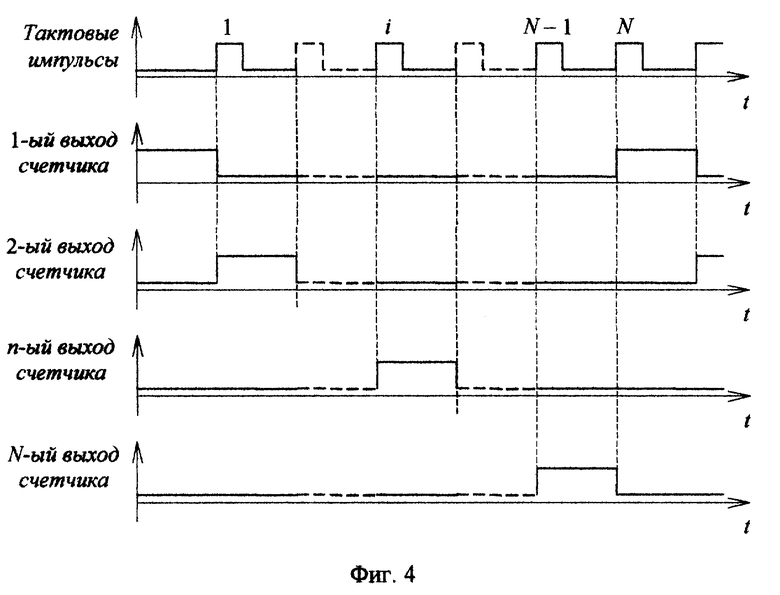

На фиг. 1 представлена структурная схема предлагаемого устройства.

Устройство содержит последовательно соединенные демодулятор 1, интегратор отсчетов 2, вычислитель сумм 3 и формирователь уровня 4, выход которого является выходом устройства, при этом вход демодулятора 1 является первым входом устройства, а тактовые входы демодулятоpa 1, интегратора отсчетов 2 и вычислителя сумм 3 образуют второй, тактовый вход устройства.

Прежде чем рассматривать работу устройства в целом, сделаем некоторые пояснения относительно исполнения и функционирования отдельных блоков.

Демодулятор 1, синхронизируемый тактовыми импульсами, осуществляет демодуляцию отсчетов телеграфного сигнала. При этом сигнал подается на первый вход демодулятора 1, а тактовые импульсы - на его тактовый вход.

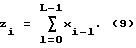

Интегратор отсчетов 2, синхронизируемый тактовыми импульсами, производит текущее суммирование значения N отсчетов сигнала, подаваемого на его первый вход, и может быть выполнен в виде последовательного регистра сдвига 8 и сумматора отсчетов 9, как это показано на фиг. 2.

В соответствии с фиг. 2 на вход 1 интегратора поступают отсчеты сигнала, а вход 2 является тактовым входом интегратора и объединяет тактовые входы регистра сдвига 8 и сумматора отсчетов 9. По каждому тактовому импульсу производится сдвиг отсчетов и запись нового отсчета в регистре сдвига 8 и суммирование всех записанных в регистре сдвига 8 отсчетов сумматором отсчетов 9. При этом число отводов регистра сдвига равно числу суммируемых отсчетов сигнала (для интегратора отсчетов 2 это число будет составлять N).

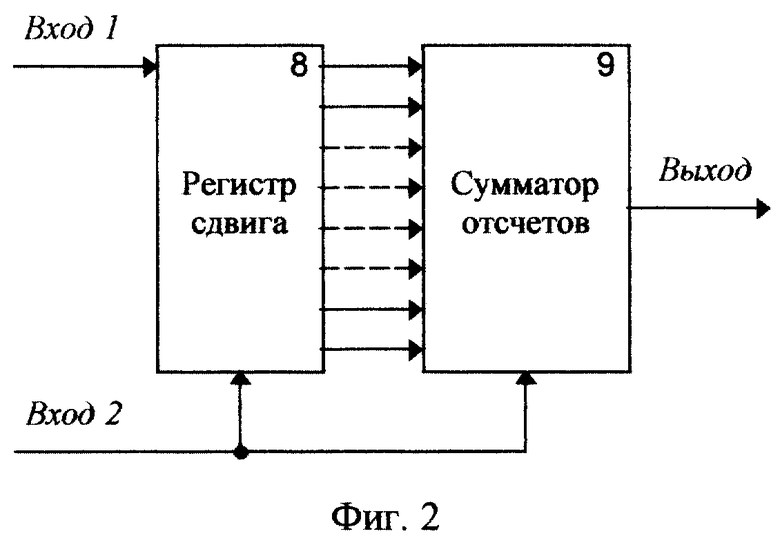

Вычислитель сумм 3 выполняется в соответствии с фиг. 3 и состоит из N парциальных ветвей, каждая из которых представляет собой последовательное соединение интегратора сумм 5 и коммутатора 6 и счетчика 7, при этом входы интеграторов сумм 5 объединены и образуют вход вычислителя сумм 3, выходы коммутаторов 6 объединены и образуют выход вычислителя сумм 3, причем каждый из N выходов счетчика 7 по порядку соединен параллельно с тактовым входом соответствующего интегратора сумм 5 и управляющим входом соответствующего коммутатора 6, а вход счетчика 7 является вторым, тактовым входом вычислителя сумм 3.

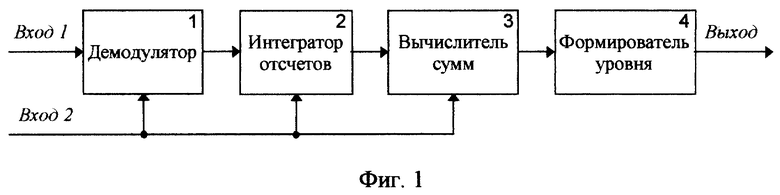

Счетчик 7 имеет коэффициент пересчета N и в каждый момент времени генерирует импульс только по одному из N выходов, как это показано на временных диаграммах фиг. 4. В исходном состоянии активным является 1-ый выход счетчика 7. Таким образом, с приходом на вход счетчика 7 i-го тактового импульса выходной импульс появится на выходе с номером

n = i - k • N + 1, (1)

где k = 0, 1, 2,...

Каждый интегратор сумм 6 при поступлении на его тактовый вход тактового импульса производит текущее суммирование значения М отсчетов сигнала, поступающих на его первый вход, и может быть выполнен в виде последовательного регистра сдвига 8 и сумматора отсчетов 9, как это показано на фиг. 2 и рассматривалось выше. При этом произведение

L = N • M (2)

будем считать количеством отсчетов сигнала, укладывающихся на длительности Т элементарной посылки.

Каждый коммутатор 6 при поступлении на его управляющий вход импульса соединяет выход соответствующего интегратора сумм 6 с выходом вычислителя сумм 3. В отсутствие импульса на управляющем входе коммутатор 6 указанную связь разрывает.

Таким образом, в текущий момент времени счетчик 7 активизирует только одну из N парциальных ветвей вычислителя сумм 3. Т.е. в соответствии с (1) для некоторого i-ого отсчета сигнала активной станет ветвь с номером n.

Рассмотрим работу устройства.

Сигнал, в виде отсчетов поступающий на первый вход устройства, демодулируется (1) и поступает на вход интегратора отсчетов 2. Выходной сигнал интегратора отсчетов 2 подается на вход вычислителя сумм 3 и затем на вход формирователя уровня 4. Формирователь уровня 4 преобразует входной сигнал в напряжение высокого или низкого уровня, которое подается на выход устройства. На второй вход устройства поступают тактовые импульсы, которые используются для синхронизации работы демодулятора 1, интегратора отсчетов 2 и вычислителя сумм 3.

Найдем величину сигнала на выходе интегратора отсчетов 2.

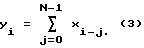

Пусть на выходе демодулятора 1 присутствует сигнал в виде последовательности {x}. Тогда для последовательности {y) на выходе интегратора отсчетов 2 в момент времени, соответствующий i-ому тактовому импульсу, имеем

В соответствии с (1) из всей последовательности {у} в качестве входных значений активный n-ый интегратор сумм 5 использует лишь те значения, чей индекс удовлетворяет условию

i = n + k • N - 1. (4)

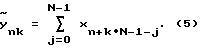

Следовательно, входной последовательностью отсчетов сигнала, воспринятых активным n-ым интегратором сумм 5, является некоторая последовательность

По аналогии c (3) сигнал на выходе данного интегратора сумм 5 можно описать последовательностью

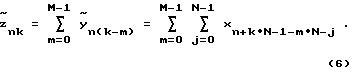

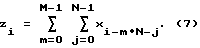

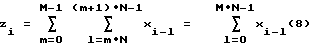

С учетом (1) выражение для последовательности {z} на выходе вычислителя сумм 3 примет вид

Выражение (7) описывает рабочий цикл (в расчете на один период следования тактовых импульсов) совокупности интегратора отсчетов 2 и вычислителя сумм 3.

Осуществим подстановку l = m • N + j

Учитывая (2), получим

Выражение (9) описывает рабочий цикл интегратора, который используется в устройстве-прототипе и предназначен для текущего суммирования L отсчетов сигнала, т. е. суммирования отсчетов сигнала на длительности Т элементарной посылки. Т. к. выражение (9) непосредственно выводится из (7), то этим доказывается, что совокупность интегратора отсчетов 2 и вычислителя сумм 3 в предлагаемом устройстве обеспечивает то же качество низкочастотной фильтрации, что и интегратор, использованный для этой же цели в устройстве-прототипе.

Однако, если учитывать количество Кдем операций, затраченных для демодуляции телеграфного сигнала, и количество Кфнч операций сложения для низкочастотной фильтрации (см. (2) и (9)), в устройстве-прототипе общее число операций рабочего цикла составит

K1 = Kдем + Kфнч = Kдем + L = Kдем + M • N. (10)

При тех же условиях для предлагаемого устройства общее число операций в соответствии с (7) может быть выражено как

K2 = Kдем + M + N. (11)

Сравнение (10) и (11) показывает, что при N > 2 и M > 2 предлагаемое устройство повышает скорость обработки, не ухудшая при этом ее качества. И с возрастанием N и M выигрыш в скорости обработки увеличивается.

Так, например, если допустить Кдем = 10 операций и L = 800 отсчетов и выбрать N = 20 и М = 40, то один рабочий цикл обработки телеграфного сигнала в предлагаемом устройстве потребует 70 операций, вместо 810 операций, необходимых для устройства-прототипа. Таким образом, с применением предлагаемого устройства можно в 11 раз увеличить значение тактовой частоты и, следовательно, скорость обработки телеграфного сигнала. Это, в свою очередь, позволяет при взятии отсчетов входного телеграфного сигнала использовать о нем более полную информацию с точки зрения фазы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2233552C2 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ РАЗНЕСЕННЫХ СИГНАЛОВ | 1990 |

|

RU2031543C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1997 |

|

RU2137313C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1992 |

|

RU2065255C1 |

| СПОСОБ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 2000 |

|

RU2222104C2 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО | 1991 |

|

RU2080739C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| СИСТЕМА ДУПЛЕКСНОЙ РАДИОСВЯЗИ | 2000 |

|

RU2190301C2 |

Изобретение относится к области радиосвязи и может использоваться для приема телеграфных сигналов и для повышения скорости обработки телеграфных сигналов. Техническим результатом является повышение скорости обработки телеграфных сигналов. В устройство для приема телеграфных сигналов, содержащее последовательно соединенные демодулятор, интегратор отсчетов, а также формирователь уровня, выход которого является выходом устройства, а вход демодулятора является входом устройства, введен вычислитель сумм, вход которого соединен с выходом интегратора отсчетов, а выход соединен с входом формирователя уровня, причем тактовые входы демодулятора, интегратора отсчетов и вычислителя сумм объединены и образуют второй, тактовый вход устройства. 4 ил.

Устройство для приема телеграфных сигналов, содержащее последовательно соединенные демодулятор, интегратор отсчетов, а также формирователь уровня, выход которого является выходом устройства, а вход демодулятора является входом устройства, отличающееся тем, что введен вычислитель сумм, вход которого соединен с выходом интегратора отсчетов, а выход соединен с входом формирователя уровня, причем тактовые входы демодулятора, интегратора отсчетов и вычислителя сумм объединены и образуют второй, тактовый вход устройства.

| Устройство для приема телеграфных сигналов | 1987 |

|

SU1510106A1 |

| US 3656064 A, 11.04.1972 | |||

| БИОРЕАКТОР С НЕПОДВИЖНЫМ СЛОЕМ, ЭЛЕМЕНТЫ-НОСИТЕЛИ ДЛЯ ТАКОГО РЕАКТОРА И СПОСОБЫ ИХ ИЗГОТОВЛЕНИЯ | 1994 |

|

RU2144004C1 |

| SU 760475 A, 03.09.1981 | |||

| JP 5737141 A, 07.08.1982. | |||

Авторы

Даты

2001-06-10—Публикация

2000-01-06—Подача