Изобретение относится к вычислительной технике и может быть использовано в радиотехнических системах для управления фазовращателями дискретно-коммутационных антенных решеток (АР).

Для управления дискретно-коммутационными АР используются различные управляющие устройства, с помощью которых фазовые соотношения для каждого фазовращателя во всех необходимых положениях луча АР либо определены заранее и хранятся в запоминающем блоке, либо вычисляются в процессе управления.

К управляющим устройствам вычислительного типа относятся известные устройства по авторским свидетельствам N 1150630, 1166131, кл. G 06 F 15/20. Указанные устройства содержат программный блок (блок управления), генератор импульсов, триггер отклонения знака луча, блоки совпадения и многоразрядные параллельные сумматоры по числу излучателей. Они реализуют так называемый принцип дельта-управления лучом АР, когда за каждый такт работы формируются сигналы управления фазовращателями, вызывающие отклонение луча АР на фиксированный угловой дискрет в ту или иную сторону, т.е. за p тактов работы устройства луч отклоняется на p дискретов.

Наиболее близким по техническому исполнению к предлагаемому является устройство для управления дискретно-коммутационной АР по авторскому свидетельству N 463977 (кл. G 06 F 15/20, 1972). Оно содержит генератор импульсов, программный блок (блок управления), триггер знака отклонения луча, блоки совпадения и многоразрядные параллельные накапливающие сумматоры, число которых равно числу излучателей.

Недостатком известных устройств является невозможность обеспечения управления АР в режиме автоматического сопровождения источника сигнала.

Заявленное устройство направлено на решение задачи управления АР в режиме автоматического сопровождения источника сигнала. Решение подобной задачи возможно в том случае, когда в устройстве для управления дискретно-коммутационной АР, состоящем из генератора импульсов, параллельных накапливающих сумматоров по числу излучателей, триггера знака отклонения луча, прямой и инверсный выходы которого соединены с первыми входами первого и второго блоков совпадения, вторые входы блоков совпадения подключены к выходу генератора импульсов, выходы блоков совпадения соединены со входами разрядов параллельных накапливающих сумматоров правой и левой относительно оси симметрии половин антенной решетки, при этом для правой относительно оси симметрии половины антенной решетки входы разрядов параллельных накапливающих сумматоров соединены таким образом, что через первый блок совпадения в них обеспечивается запись параллельных двоичных кодов, эквивалентных номерам n - излучателей, через второй блок совпадения - запись параллельных двоичных кодов, дополнительных к номерам n излучателей (дополнительный код соответствует числу (2m-n), где m - число разрядов параллельных накапливающих сумматоров), для левой относительно оси симметрии половины антенной решетки входы разрядов параллельных накапливающих сумматоров соединены с выходами первого и второго блоков совпадения таким образом, что через первый блок совпадения в них обеспечивается запись параллельных двоичных кодов, дополнительных к номерам n излучателей, через второй блок совпадения - запись параллельных двоичных кодов, эквивалентных номерам n излучателей, и блока управления, соединенного с синхронизирующим входом генератора импульсов, блок управления выполнен в виде однокристального микроконтроллера (МК) и подключенного к нему аналого-цифрового преобразователя (АЦП), первый вход введенного логического элемента ИЛИ подключен к выходу генератора импульсов, второй вход соединен с одним из портов микроконтроллера, а выход элемента ИЛИ - со счетным входом триггера знака отклонения луча, вход записи (нуля или единицы) триггера знака отклонения луча подключен к одному из портов однокристального микроконтроллера, причем аналоговый информационный вход блока управления является информационным входом аналого-цифрового преобразователя, запускающий вход аналого-цифрового преобразователя соединен с одним из портов микроконтроллера, а управляющий вход блока управления предназначен для обмена информацией между микроконтроллером и внешним устройством, например внешней ЭВМ.

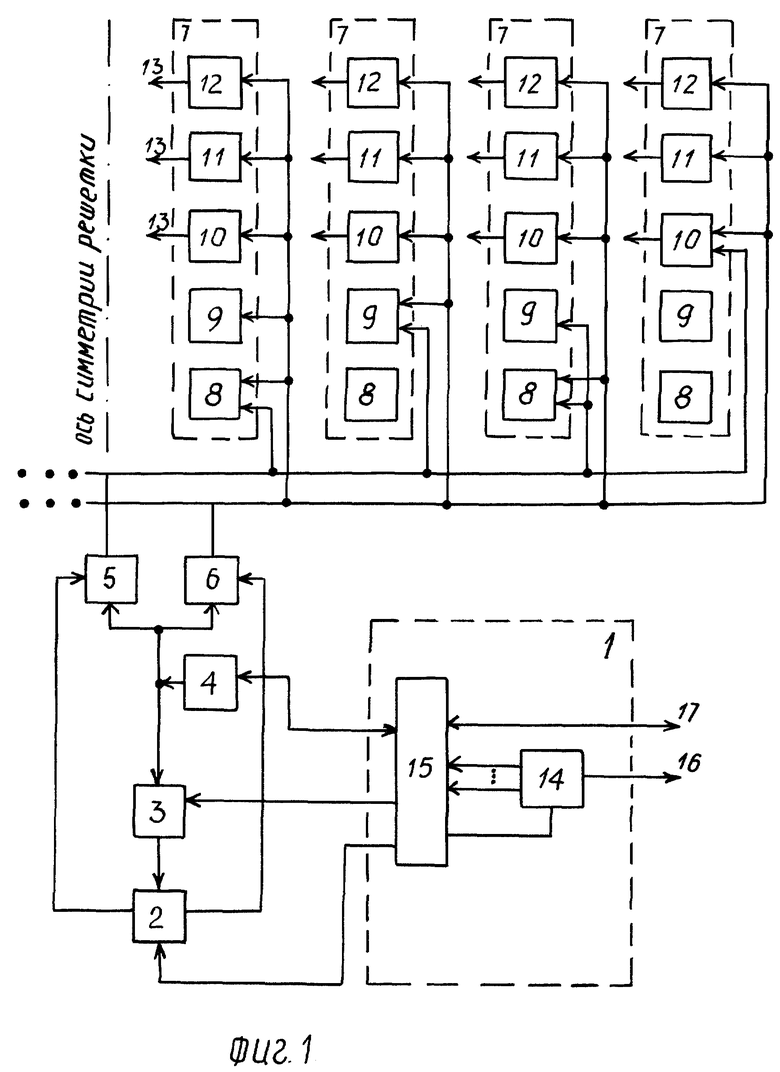

На фиг. 1 изображена структурная схема предлагаемого устройства применительно к правой половине девяти элементной линейки излучателей с трехсекционными фазовращателями 180, 90 и 45 градусов. Левая часть предлагаемого устройства, состоящая из аналогичных многоразрядных накапливающих сумматоров, по своему составу является зеркальным отражением правой и для упрощения схемы не показана. Фаза центрального излучателя линейки равна нулю и при перемещении луча не изменяется, поэтому в управляющем устройстве отсутствует накапливающий сумматор.

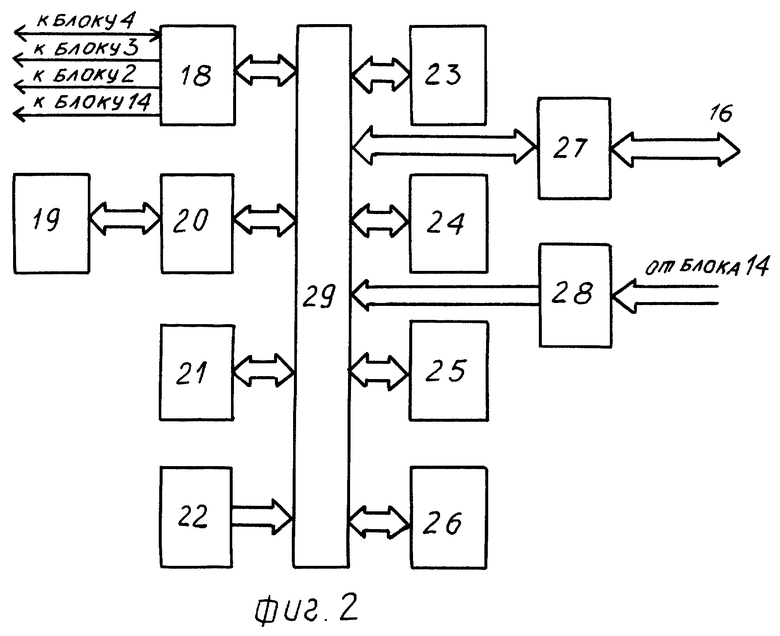

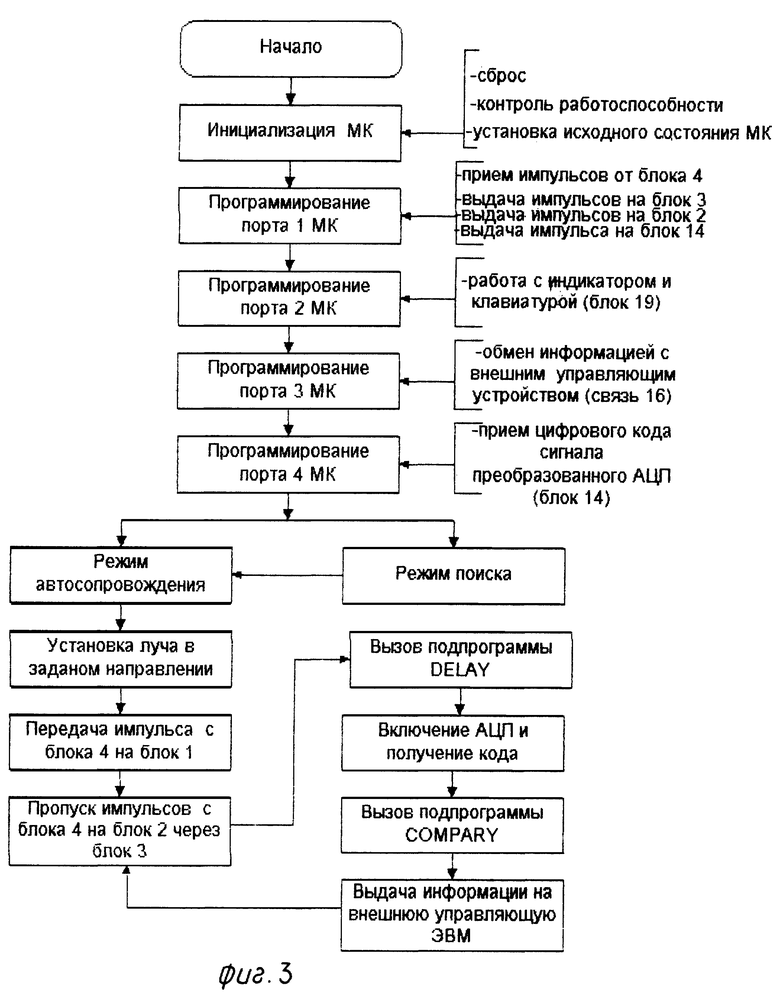

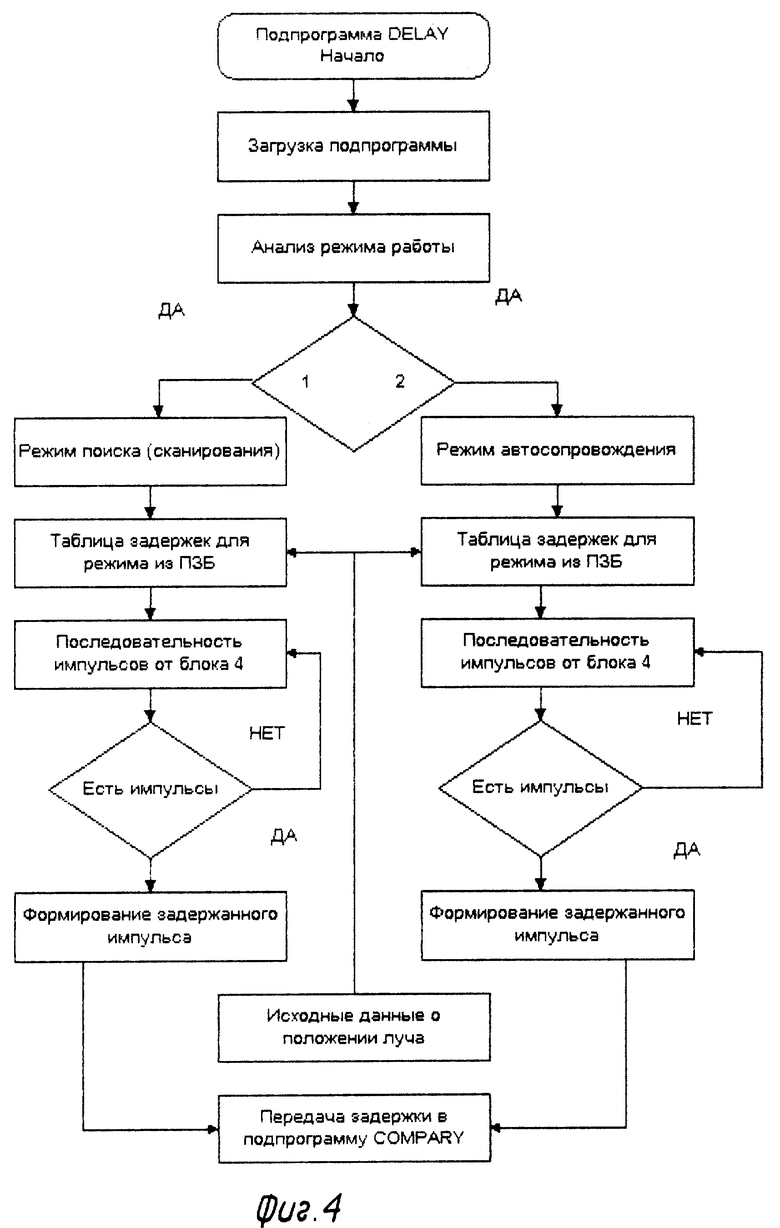

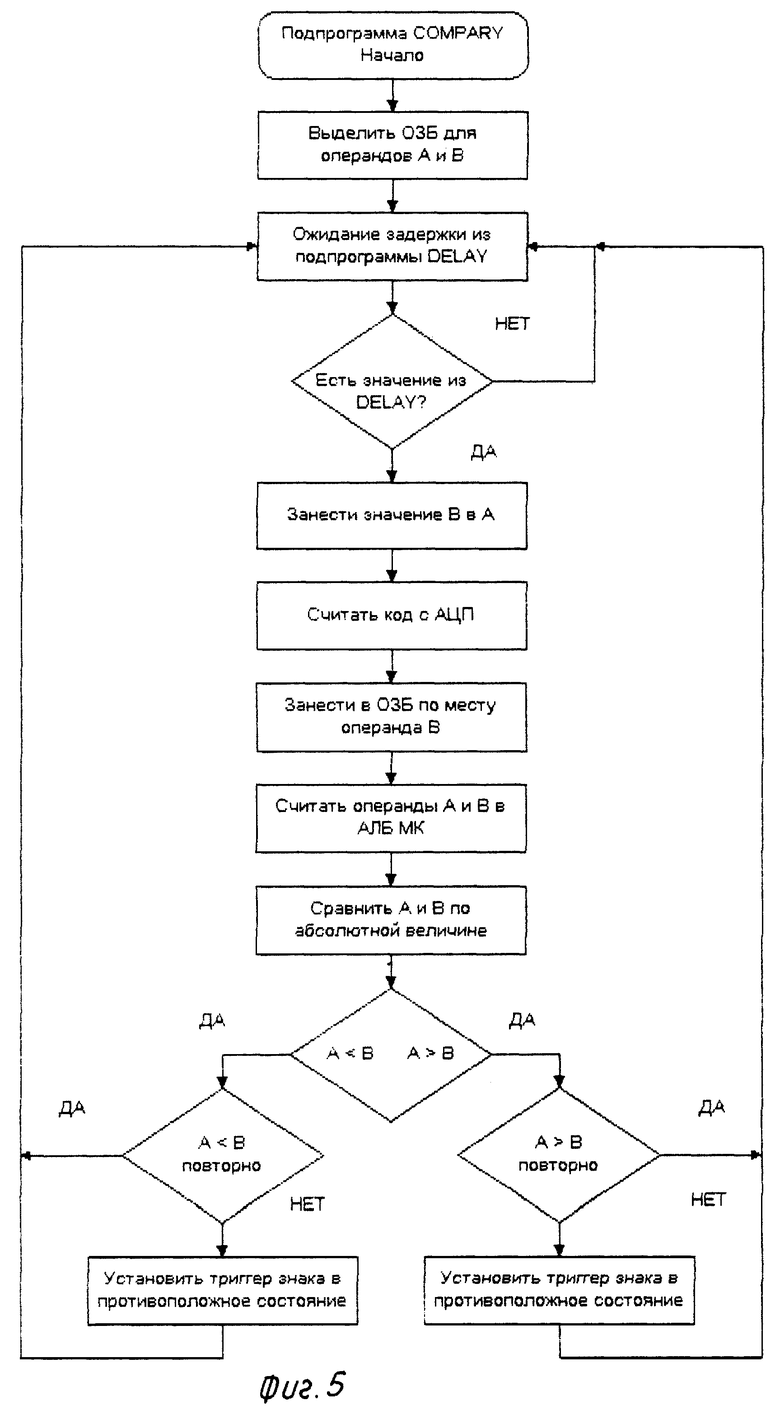

На фиг. 2 представлена структура однокристального микроконтроллера. На фиг. 3 показана блок-схема алгоритма работы микроконтроллера в составе устройства для управления дискретно-коммутационной АР, на фиг. 4 - блок-схема алгоритма, реализующего задержку импульсов, а на фиг. 5 - блок-схема алгоритма, обеспечивающего реализацию функции сравнения.

Предлагаемое устройство содержит блок 1 управления, триггер 2 знака отклонения луча, логический элемент 3 ИЛИ, генератор 4 импульсов. Прямой и инверсный выходы триггера знака отклонения луча соединены с первыми входами первого 5 и второго 6 блоков совпадения. Выход генератора импульсов соединен непосредственно со вторыми входами блоков совпадения, а через элемент ИЛИ - со счетным входом триггера знака отклонения луча. Выходы блоков совпадения 5 и 6 в определенном порядке соединены со входами разрядов 8-12 параллельных накапливающих сумматоров 7, при этом выход блока совпадения 5 соединен с накапливающими сумматорами 7 таким образом, что обеспечивается запись в них параллельных двоичных кодов, эквивалентных номерам n - излучателей, а именно, соединен со входом первого разряда 8 первого сумматора 7, со входом второго разряда 9 второго сумматора 7, со входом первого 8 и второго 9 разряда третьего сумматора 7 и со входом третьего 10 разряда четвертого сумматора 7. Выход блока совпадения 6 соединен с накапливающими сумматорами 7 таким образом, что обеспечивается запись в них параллельных двоичных кодов, дополнительных к номерам n излучателей (дополнительный код соответствует числу (2m-n), где m - число разрядов параллельных накапливающих сумматоров 7), а, именно, соединен со входами разрядов 8-12 первого сумматора 7, со входами разрядов 9-12 второго сумматора 7, со входами разрядов 8 и 10-12 третьего сумматора 7 и со входами разрядов 10-12 четвертого сумматора 7. Выходы 13 старших разрядов 10-12 сумматоров 7 соединяются со входами непоказанных на рисунке согласующих каскадов, управляющих секциями фазовращателей. Нумерация сумматоров 7 ведется по рисунку вправо от осевой линии решетки излучателей. Для левой (непоказанной на рисунке) части устройства для управления дискретно-коммутационной АР нумерация ведется влево от осевой линии, но излучатели имеют номера (-n) и для отклонения луча, например на один дискрет в положительном направлении, в накапливающие сумматоры 7 левой части должны быть записаны параллельные двоичные коды, эквивалентные номерам излучателей (-n), что достигается записью в них кодов, дополнительных к номерам излучателей n. Поэтому выходы блоков совпадения 5 и 6 соединены с накапливающими сумматорами 7 левой части устройства таким образом, что блок совпадения 5 обеспечивает запись в них параллельных двоичных кодов, дополнительных к номерам n излучателей, а блок совпадения 6 - параллельных двоичных кодов, эквивалентных номерам n излучателей.

Блок управления содержит аналого-цифровой преобразователь 14 и однокристальный микроконтроллер 15. Информационный вход АЦП является одновременно и аналоговым информационным входом 16 блока управления, а управляющий вход 17 предназначен для обмена информацией микроконтроллера с внешними устройства, например - с внешней ЭВМ.

Однокристальный микроконтроллер (см. фиг. 2) содержит блок 18 (порт 1 микроконтроллера), индикатор 19 с клавиатурой, блок 20 (порт 2), генератор 21, осуществляющий управление и синхронизацию микроконтроллера, постоянный запоминающий блок (ПЗБ) 22, оперативный запоминающий блок (ОЗБ) 23, блок специальных регистров 24, блок 25 прерываний с таймером, арифметический блок (АБ) 26, блок 27 (порт 3) и блок 28 (порт 4). Передача данных, адресов, команд, управление производятся через шину 29. Через порт 3 осуществляется обмен информацией между микроконтроллером и внешними устройствами (вход 17 блока управления 1). К блоку 28 (порту 4) подключены цифровые выходы АЦП 14. Синхронизация работы АЦП осуществляется от микроконтроллера. Через блок 18 (порт 1) производится синхронизация работы генератора 4, выдача импульсов на второй вход логического элемента ИЛИ и формирование импульсов, соответствующих нулю или единице и поступающих на вход записи триггера 2 знака отклонения луча.

Рассмотрим функционирование предлагаемого устройства. Через блок 19 МК (клавиатура и индикация) автономно или через вход 17 от внешнего устройства производится запуск однокристального микроконтроллера: инициализация, программирование портов 1-4 (блоков 18, 20, 27 и 28) и выбор режимов работы: поиск или автосопровождение. В зависимости от требуемого направления первоначальной установки луча АР через порт 1 (блок 18) МК на вход записи нуля или единицы триггера 2 знака отклонения луча поступает сигнал и устанавливает триггер 2 в состояние, соответствующее отклонению луча в положительном либо отрицательном направлении относительно нормали, в результате чего оказывается подготовленным к пропусканию импульсов блок совпадения 5 или 6, первый из которых используется для перемещения луча в положительном направлении, а второй - в отрицательном. Управляющий сигнал от МК 15 может поступать как через вход 17 от внешней управляющей ЭВМ, так и от пульта ручного управления (блок 19) устройства управления.

Пусть необходимо отклонить луч на один дискрет в положительном направлении. При этом триггер 2 знака отклонения луча находится в таком состоянии (положительном), что сигнал с его левого плеча открывает блок совпадения 5 и импульс от генератора 4 через блок совпадения 5 вводится в параллельные накапливающие сумматоры 7 параллельным двоичным кодом, эквивалентным номеру n излучателя. Этот код с выходов устройства 13 поступает через ключевые каскады на секции дискретно-коммутационных фазовращателей и устанавливает их в требуемые состояния. В результате на раскрыве АР создается амплитудно-фазовое распределение, обеспечивающее формирование диаграммы направленности с максимумом в заданном направлении.

При необходимости отклонить луч на один дискрет в отрицательном направлении триггер 2 знака отклонения луча перебрасывается в противоположное состояние и импульс от генератора 4 через открытый блок совпадения 6 вводится в параллельные накапливающие сумматоры 7 параллельным двоичным кодом, дополнительным к номеру n излучателя.

При отклонении луча на несколько дискретов, например p, в отрицательном направлении триггер 2 знака отклонения луча находится в неизменном состоянии столько времени, сколько необходимо на прохождение p импульсов от генератора импульсов 4, в результате чего в n-й сумматор вводятся в прямом коде числа, равные произведению номера положения луча (в данном случае p) на номер излучателя n, что обеспечивает отклонение луча на p-дискретов. Функционирование левой (не показанной на рисунке) части устройства осуществляется аналогичным образом.

Таким образом в режиме поиска (наведения) луча устройство функционирует в соответствии с ближайшим аналогом. Алгоритм работы блока управления 1 для режимов поиска и автосопровождения представлен в виде блок-схемы на фиг. 3. Откуда видно, что после начала работы блока осуществляется контроль работоспособности устройства управления на базе МК с АЦП, затем - программирование МК и переход в один из режимов работы (поиск, автосопровождение) по известным параметрам, полученным извне или из ПЗБ МК. Задержка, необходимая для сравнения кодовых последовательностей для приемной и передающей частей, и операция сравнения реализованы программно. Управление АЦП 14 и триггером знака отклонения луча 2 также осуществляется программно.

После выведения луча в заданном направлении с началом приема полезного сигнала устройство переходит в режим управления АР для автосопровождения источника сигнала. При этом сигналы на входах записи триггера знака отклонения луча 2 (от порта 1 МК 15) отсутствуют и управление триггером 2 осуществляется по счетному входу. Пусть по приходу первого импульса от генератора 4 триггер 2 знака отклонения луча устанавливается в положительное состояние, открывает блок совпадения 5 и обеспечивает отклонение луча на один дискрет в положительном направлении от равносигнального направления приема полезного сигнала. Этот же импульс от генератора 4, поступающий на блок 18 (порт 1) МК 15, вызывает срабатывание подпрограммы определения задержки DELEY, блок-схема алгоритма работы которой представлена на фиг. 4. Из блок-схемы алгоритма работы подпрограммы задержки следует, что параметры необходимых задержек представляют собой данные, занесенные по определенным адресам в блок ПЗБ 22 МК 15. Подпрограммой задержки формируется импульс, задержанный на время, необходимое для установки луча в заданное положение. Работа подпрограммы происходит в двух режимах: поиска и автосопровождения. В обоих режимах работы данные о задержке поступают в подпрограмму сравнения (COMPARY). Сформированный задержанный импульс запускает в работу АЦП 14, на аналоговый информационный вход 16 которого поступает сигнал из приемника со схемы быстродействующей автоматической регулировки усиления (БАРУ), несущий информацию об амплитуде принимаемого сигнала. По поступлению запускающего импульса, сформированного подпрограммой DELEY, в АЦП 14 происходит преобразование аналогового сигнала со входа 16 в цифровой код, который передается на МК 15 и обрабатывается подпрограммой сравнения (COMPARY). Подпрограмма COMPARY, блок-схема алгоритма которой представлена на фиг. 5, осуществляет сравнение кода сигнала, поступившего в текущем такте, с кодом сигнала, поступившим в предыдущем такте, и при превышении текущего кода над предыдущим формирует импульс для триггера 2 знака отклонения луча. На равенство кодов - текущего и предыдущего - подпрограмма не реагирует.

Рассмотрим случай равенства кодов. В этом случае подпрограмма COMPARY не формирует импульс управления триггером знака 2 отклонения луча и очередной импульс с выхода генератора 4 устанавливает триггер 2 знака отклонения луча в отрицательное состояние и через открытый блок совпадения 6 проходит на накапливающие сумматоры 7 и обеспечивает отклонение луча на один дискрет в отрицательном направлении от равносигнального. Следующий импульс генератора 4 вновь вернет триггер 2 знака отклонения луча в положительное состояние, и луч отклонится на один дискрет в положительном направлении. Таким образом при равенстве кодов на входе подпрограммы сравнения, что говорит о точном наведении луча на источник сигнала, устройство управления обеспечивает последовательное переключение луча на один дискрет в положительном и отрицательном направлении относительно равносигнального направления.

Пусть источник сигнала переместился в пространстве в положительном направлении от равносигнального направления. В этом случае при отклонении луча в положительном направлении код, соответствующий амплитуде принимаемого сигнала, на входе подпрограммы сравнения будет больше, чем в предыдущем такте, и подпрограмма сформирует одиночный импульс, который через логический элемент ИЛИ 3 пройдет на счетный вход триггера 2 знака отклонения луча и перебросит его в холостое, отрицательное состояние. Но так как при этом отсутствует импульс с выхода генератора 4, какого-либо изменения в состоянии накапливающих сумматоров 7 не происходит и соответственно не изменяется положение луча. Следующий приходящий с генератора 4 импульс вновь возвращает триггер 2 в рабочее (положительное) состояние и обеспечивает перемещение луча на один дискрет в положительном направлении и т.д. То есть луч АР будет догонять уходящий в положительном направлении источник сигнала.

При выравнивании кодов, когда равносигнальное направление "смотрит" на источник сигнала, устройство будет обеспечивать последовательное переключение луча на один дискрет вокруг равносигнального направления, о чем говорилось выше.

При перемещении источника сигнала в отрицательном направлении функционирование устройства осуществляется аналогично рассмотренному выше, но при этом рабочими являются отрицательные состояния триггера 2 знака отклонения луча, а холостыми - положительные состояния.

Таким образом, в процессе функционирования устройство обеспечит управление антенной решеткой с дискретно-коммутационными фазовращателями в режиме автосопровождения источника сигнала. При потере сигнала управление передается оператору или внешней ЭВМ, которые через блок 19 и соответственно через управляющий вход 17 устройства устанавливают триггер 2 знака отклонения луча в состояние, обеспечивающее вывод луча заданную точку ожидаемого появления сигнала, либо поиск его по заданной программе аналогично тому, как это осуществлено в ближайшем аналоге. При появлении сигнала устройство снова продолжает функционировать в режиме автосопровождения.

В качестве микроконтроллера возможно использование типового однокристального микроконтроллера из серии 1816 (/В.В.Сташин, А.В.Урусов, О.Ф.Мологонцева. Проектирование цифровых устройств на однокристальных микроконтроллерах. М., Энергоатомиздат. 1990 г./). Остальные компоненты структурной схемы устройства могут быть выполнены на элементах ТТЛШ серий 1533, 1554 аналогично предложенному в прототипе. Тип выбираемого АЦП будет определяться требованиями к временным параметрам, необходимым для обеспечения работоспособности устройства управления, а также заданными точностными характеристиками, определяемыми разрядностью преобразователя (Быстродействующие интегральные микросхемы ЦАП и АЦП и измерение их параметров / А.-Й.К. Марцинкявичус, Э.-А. К. Багданскис. Р.Л. Пошюнас и др. Под редакцией А.-Й.К. Марцинкявичуса, Э. -А.К. Багданскиса, - М.: Радио и связь, 1988, с. 20-29, 60-100).

Полученный технический эффект заключается в расширении функциональных возможностей устройства для управления дискретно-коммутационной АР в режиме автосопровождения или поиска цели, что достигается введением в ближайший аналог логического элемента ИЛИ, выполнением блока управления в виде однокристального микроконтроллера и подключенного к нему аналого-цифрового преобразователя, причем первый вход логического элемента ИЛИ подключен к генератору импульсов, второй вход - к одному из портов микроконтроллера, выход - к счетному входу триггера знака отклонения луча, вход записи (нуля или единицы) триггера знака отклонения луча подключен к одному из портов однокристального микроконтроллера, причем аналоговый информационный вход блока управления является информационным входом аналого-цифрового преобразователя, запускающий вход аналого-цифрового преобразователя соединен с одним из портов микроконтроллера, а управляющий вход блока управления предназначен для обмена информацией между микроконтроллером и внешним устройством, например внешней ЭВМ.

Изобретение относится к вычислительной технике и может быть использовано в радиотехнических системах для управления фазовращателями дискретно-коммутационных антенных решеток. Техническим результатом является расширение функциональных возможностей за счет обеспечения управления антенной решеткой в режиме автоматического сопровождения источника сигнала. Устройство содержит генератор импульсов, параллельные накапливающие сумматоры, триггер знака отклонения луча, блок управления и элемент ИЛИ. 5 ил.

Устройство для управления дискретно-коммутационной антенной решеткой, содержащее генератор импульсов, параллельные накапливающие сумматоры по числу излучателей, триггер знака отклонения луча, прямой и инверсный выходы которого соединены с первыми входами первого и второго блоков совпадения, вторые входы которых подключены к выходу генератора импульсов, выходы блоков совпадения соединены со входами разрядов параллельных накапливающих сумматоров правой и левой относительно оси симметрии половин антенной решетки, при этом для правой относительно оси симметрии половины антенной решетки входы разрядов параллельных накапливающих сумматоров соединены таким образом, что через первый блок совпадения в них обеспечивается запись параллельных двоичных кодов, эквивалентных номерам n излучателей, через второй блок совпадения - запись параллельных двоичных кодов, дополнительных к номерам n излучателей (дополнительный код соответствует числу (2m - n), где m - число разрядов параллельных накапливающих сумматоров), для левой относительно оси симметрии половины антенной решетки входы разрядов параллельных накапливающих сумматоров соединены с выходами первого и второго блоков совпадения таким образом, что через первый блок совпадения в них обеспечивается запись параллельных двоичных кодов, дополнительных к номерам n излучателей, через второй блок совпадения - запись параллельных двоичных кодов, эквивалентных номерам n излучателей, выходы старших разрядов параллельных накапливающих сумматоров являются выходами устройства, блок управления, соединенный с синхронизирующим входом генератора импульсов, отличающееся тем, что блок управления выполнен в виде однокристального микроконтроллера и подключенного к нему аналого-цифрового преобразователя, первый вход введенного логического элемента ИЛИ подключен к выходу генератора импульсов, второй вход соединен с одним из портов микроконтроллера, а выход логического элемента ИЛИ - со счетным входом триггера знака отклонения луча, вход записи (нуля или единицы) триггера знака отклонения луча подключен к одному из портов однокристального микроконтроллера, причем аналоговый информационный вход блока управления является информационным входом аналого-цифрового преобразователя, запускающий вход аналого-цифрового преобразователя соединен с одним из портов микроконтроллера, а управляющий вход блока управления предназначен для обмена информацией между микроконтроллером и внешним устройством, например внешней ЭВМ.

| Устройство для управления дискретно-коммутационной линейкой излучателей | 1972 |

|

SU463977A1 |

| Вычислительное устройство для управления решеткой излучателей | 1983 |

|

SU1150630A1 |

| Устройство для управления дискретно-коммутационной линейкой излучателей | 1983 |

|

SU1166131A1 |

| Релейный регулятор | 1989 |

|

SU1695263A1 |

| Самонаклад книжных блоков | 1956 |

|

SU108969A1 |

Авторы

Даты

2001-06-27—Публикация

1997-08-01—Подача