Настоящее изобретение относится к модулю с полупроводниковыми микросхемами и способу его изготовления, а более конкретно - к модулю с полупроводниковыми микросхемами, который имеет сравнительно короткий тракт передачи сигнала между полупроводниковыми микросхемами и который занимает на плате сравнительно мало места.

В связи с возрастающей тенденцией к применению более быстродействующих микросхем для процессоров допустимое время задержки сигнала доступа к микросхеме периферийной памяти становится все время короче и короче. Поэтому проектировщику необходимо найти способ укоротить тракт передачи сигнала между микросхемой процессора и микросхемой периферийной памяти. С другой стороны, в связи с растущей потребностью в увеличении емкости памяти возрастает число микросхем памяти на печатной плате. Однако площадь печатной платы ограничена. Таким образом, основной заботой проектировщиков стало решение проблемы размещения большого количества микросхем памяти с обеспечением при этом минимального отрицательного влияния на плату.

Известен модуль с полупроводниковыми микросхемами (патент JP 2-58793), содержащий первую полупроводниковую микросхему, имеющую монтажную поверхность с множеством расположенных на ней первых контактных площадок; диэлектрический ленточный слой, выполненный с множеством отверстий в местах расположения первых контактных площадок, и предназначенных для обнажения первых контактных площадок; множество электропроводных контактов и монтажную поверхность с множеством расположенных на ней вторых контактных площадок, которые соединены с электропроводными контактами с обеспечением электрического соединения с первыми контактными площадками.

Также известен способ изготовления модуля с полупроводниковыми микросхемами (патент JP 2-58793), включающий в себя выполнение диэлектрического ленточного слоя с множеством отверстий, предусмотренных в местах расположения первых контактных площадок, выполненных на монтажной поверхности первой полупроводниковой микросхемы и предназначенных для обнажения первых контактных площадок, соединение вторых контактных площадок, выполненных на другой монтажной поверхности, с электропроводными контактами с обеспечением электрического соединения с первыми контактными площадками.

Как видно из вышеописанного, модуль с полупроводниковыми микросхемами и способ его производства не решают проблемы размещения большого количества микросхем при одновременной экономии пространства, т.к. каждая микросхема должна быть размещена на печатной плате.

Основной целью настоящего изобретения является создание такого модуля с полупроводниковыми микросхемами и такого способа изготовления этого модуля с полупроводниковыми микросхемами, при применении которых тракт передачи сигнала может быть укорочен с тем, чтобы обеспечить минимальное время задержки.

Другая цель настоящего изобретения заключается в создании такого модуля с полупроводниковыми микросхемами и такого способа изготовления этого модуля с полупроводниковыми микросхемами, при применении которых на печатной плате может быть размещено большое количество микросхем памяти и при этом не будет существенного увеличения размера печатной платы.

В соответствии с одним аспектом настоящего изобретения модуль с полупроводниковыми микросхемами содержит первую полупроводниковую микросхему, имеющую монтажную поверхность с множеством расположенных на ней первых контактных площадок; диэлектрический ленточный слой, выполненный с множеством отверстий в местах расположения первых контактных площадок, и предназначенных для обнажения первых контактных площадок; множество электропроводных контактов и монтажную поверхность с множеством расположенных на ней вторых контактных площадок, которые соединены с электропроводными контактами с обеспечением электрического соединения с первыми контактными площадками, согласно изобретению, монтажная поверхность с множеством расположенных на ней вторых контактных площадок является монтажной поверхностью второй полупроводниковой микросхемы; диэлектрический ленточный слой имеет противоположные первую и вторую адгезионные поверхности; первая адгезионная поверхность сцеплена с монтажной поверхностью первой полупроводниковой микросхемы, при этом каждое из отверстий ограничено стенкой, которая совместно с соответствующей ему одной из первых контактных площадок образует приемное пространство под контакт; множество электропроводных контактов размещены соответственно в приемных пространствах под контакты; монтажная поверхность второй полупроводниковой микросхемы сцеплена со второй адгезионной поверхностью.

Желательно, чтобы вторая адгезионная поверхность была покрыта термоотверждаемым клеем, температура отверждения которого ниже, чем температура плавления электропроводных контактов.

Предпочтительно, модуль с полупроводниковыми микросхемами дополнительно содержит контактную рамку, на которой смонтирована вторая полупроводниковая микросхема.

Также модуль с полупроводниковыми микросхемами дополнительно содержит пластмассовый корпус, в который упакованы первая и вторая полупроводниковые микросхемы и контактная рамка.

Кроме того, модуль с полупроводниковыми микросхемами дополнительно содержит печатную плату, на которой смонтирована вторая полупроводниковая микросхема, причем печатная плата выполнена с расположенными на ней третьими контактными площадками, которые соединены электрически со второй полупроводниковой микросхемой, а также может дополнительно содержать пластмассовый корпус, в который упакованы первая и вторая полупроводниковые микросхемы.

Предпочтительно, первая полупроводниковая микросхема представляет собой микросхему памяти, а вторая полупроводниковая микросхема представляет собой микросхему процессора.

Также желательно, чтобы каждый из электропроводных контактов представлял собой оловянный шарик или был сформирован из электропроводной пасты или из электропроводного материала, который подвергнут химическому электролитическому осаждению до соединения со вторыми контактными площадками.

В соответствии с другим аспектом настоящего изобретения способ изготовления модуля с полупроводниковыми микросхемами включает в себя выполнение диэлектрического ленточного слоя с множеством отверстий, предусмотренных в местах расположения первых контактных площадок, выполненных на монтажной поверхности первой полупроводниковой микросхемы и предназначенных для обнажения первых контактных площадок, соединение вторых контактных площадок, выполненных на другой монтажной поверхности с электропроводными контактами с обеспечением электрического соединения с первыми контактными площадками, согласно изобретению перед соединением вторых контактных площадок, выполненных на другой монтажной поверхности, которая является монтажной поверхностью второй полупроводниковой микросхемы, с обеспечением электрического соединения с первыми контактными площадками, осуществляют сцепление первой адгезионной поверхности диэлектрического ленточного слоя с монтажной поверхностью первой полупроводниковой микросхемы, при этом каждое из отверстий ограничено стенкой, которая совместно с соответствующей ему первой контактной площадкой образует приемное пространство под контакт; размещение множества электропроводных контактов соответственно в приемных пространствах под контакты; сцепление монтажной поверхности второй полупроводниковой микросхемы со второй адгезионной поверхностью диэлектрического ленточного слоя, противоположной по отношению к первой адгезионной поверхности.

Желательно, чтобы вторая адгезионная поверхность была покрыта термоотверждаемым клеем, температура отверждения которого ниже чем температура плавления электропроводных контактов, а сцепление второй полупроводниковой микросхемы с диэлектрическим ленточным слоем и соединение вторых контактных площадок с электропроводными контактами осуществлялось одновременно путем операции термоотверждения таким образом, чтобы монтажная поверхность второй полупроводниковой микросхемы была уже сцеплена со второй адгезионной поверхностью до расплавления электропроводных контактов.

Кроме того, сцепление диэлектрического ленточного слоя с первой полупроводниковой микросхемой осуществляют посредством термоотверждения клея, применяемого для нанесения на первую адгезионную поверхность.

Cпособ дополнительно содержит операцию монтажа второй полупроводниковой микросхемы на контактной рамке.

Также дополнительно осуществляют операцию формовки пластмассового корпуса и упаковки первой и второй полупроводниковых микросхем контактной рамки, а также операции монтажа второй полупроводниковой микросхемы на печатной плате и соединения второй полупроводниковой микросхемы проводниками с третьими контактными площадками, выполненными на печатной плате.

Кроме того, способ дополнительно содержит операцию формовки пластмассового корпуса, упаковки первой и второй полупроводниковых микросхем.

И предпочтительно, первая полупроводниковая микросхема представляет собой микросхему памяти, а вторая полупроводниковая микросхема представляет собой микросхему процессора.

Также желательно, чтобы каждый из электропроводных контактов представлял собой оловянный шарик.

А также, предпочтительно, каждый из электропроводных контактов формируют из электропроводной пасты или из электропроводного материала, который подвергают химическому и электролитическому осаждению до соединения со вторыми контактами.

Другие признаки и преимущества настоящего изобретения станут очевидны из следующего подробного описания предпочтительных вариантов его осуществления, которое ведется со ссылками на чертежи, на которых:

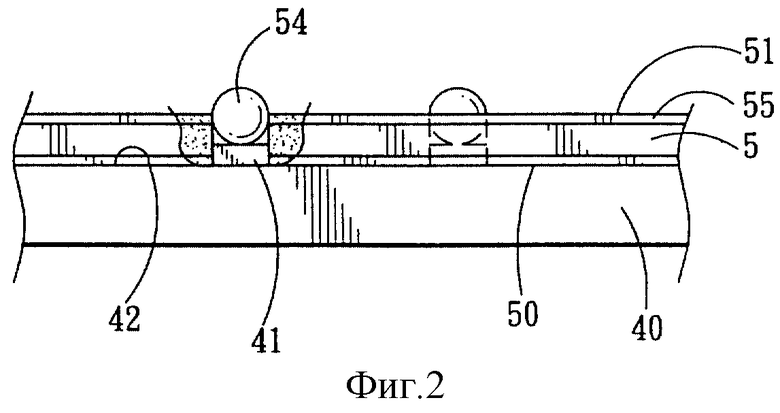

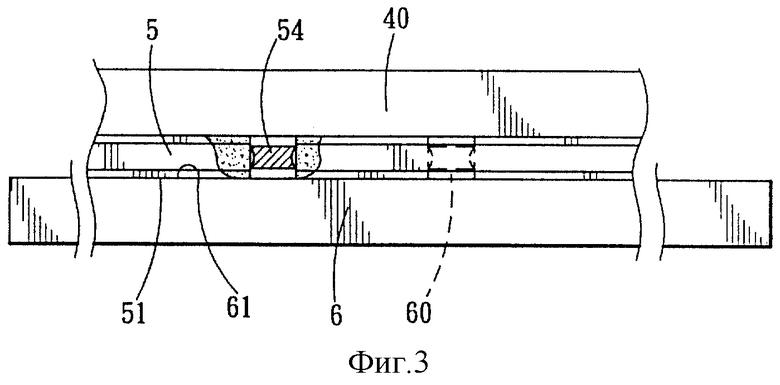

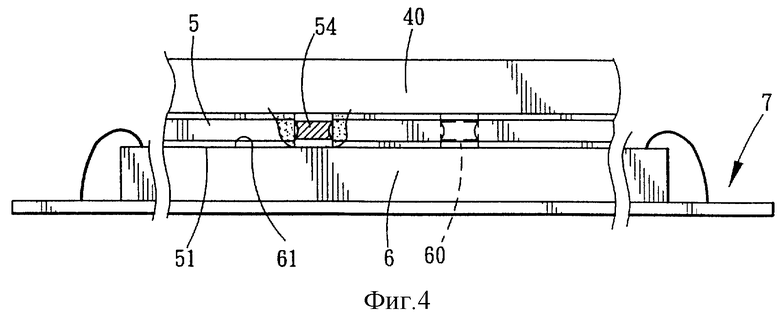

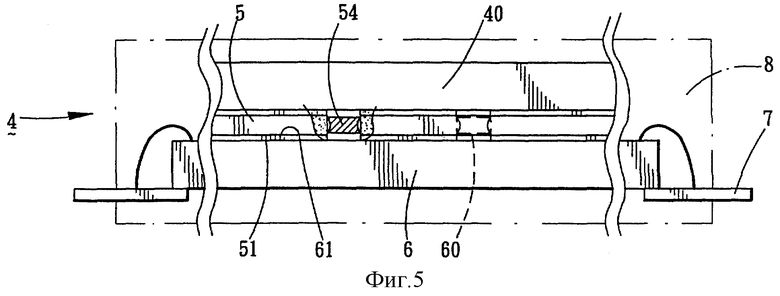

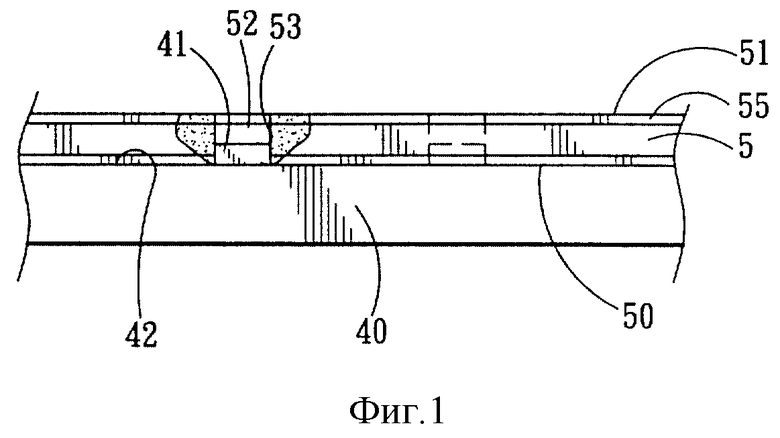

фиг. 1 - 5 изображают схематически виды, иллюстрирующие отдельные операции первого предпочтительного варианта выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением;

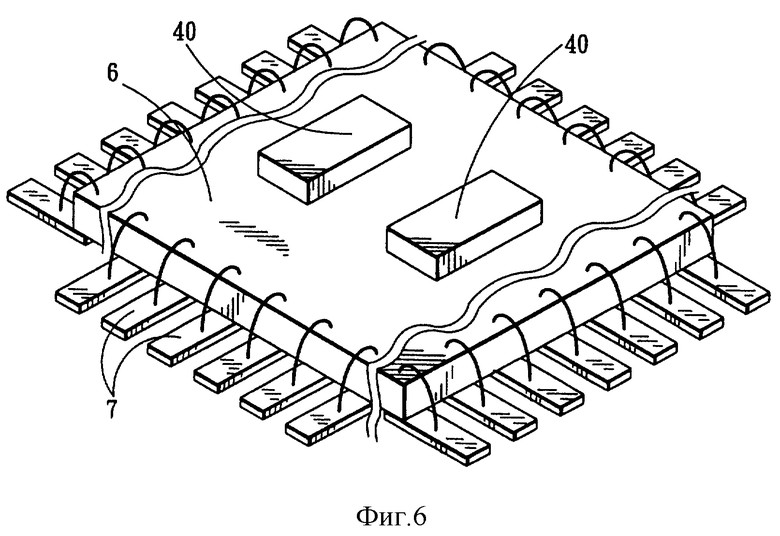

фиг. 6 - в перспективе вид второго предпочтительного варианта выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением;

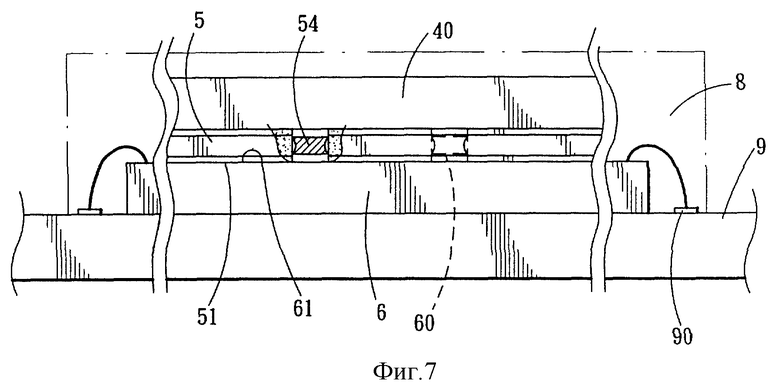

фиг. 7 - схематически вид третьего предпочтительного варианта выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением;

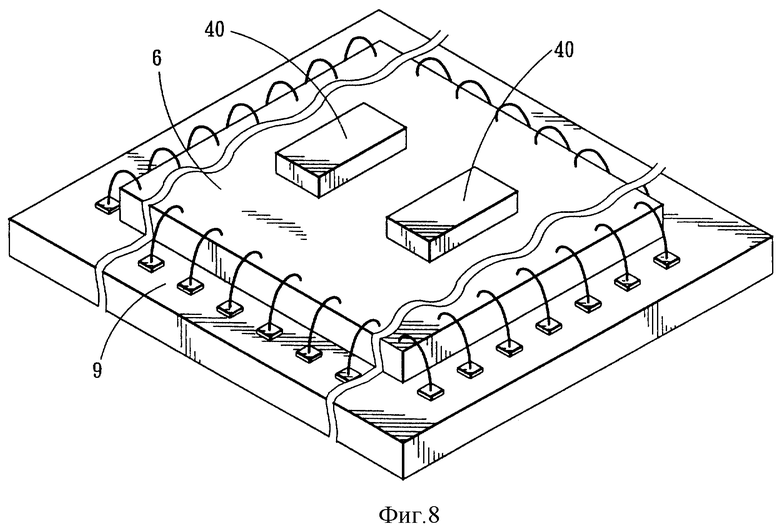

фиг. 8 - в перспективе вид четвертого предпочтительного варианта выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением;

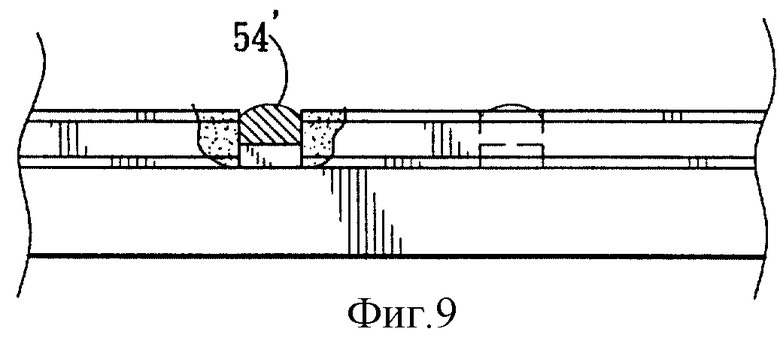

фиг. 9 - схематически вид пятого предпочтительного варианта осуществления модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением на одной из промежуточных операций его изготовления;

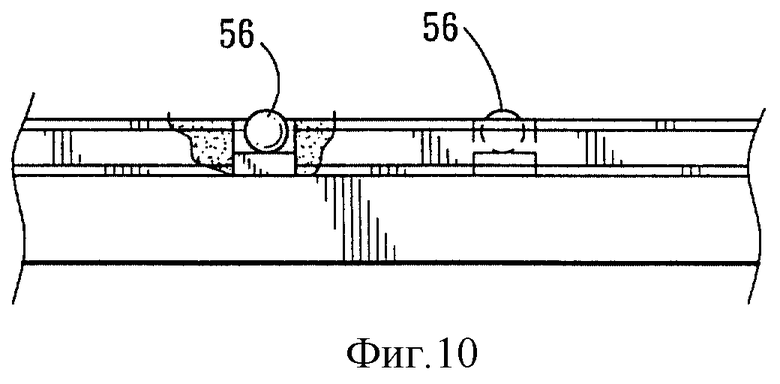

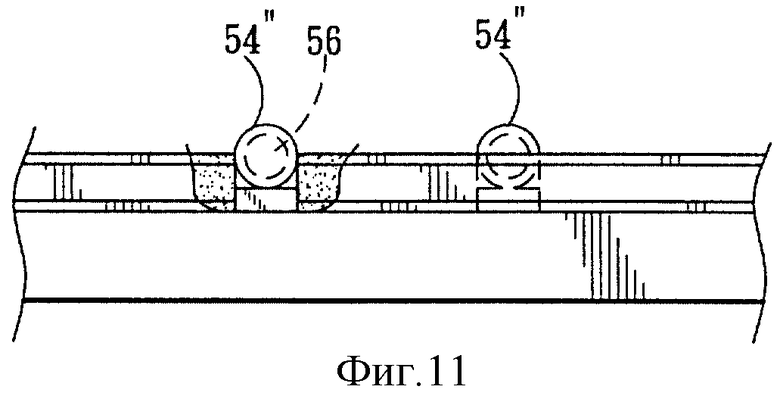

фиг. 10 и 11 - схематически виды, иллюстрирующие некоторые операции шестого предпочтительного варианта выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением.

Прежде чем приступить к более подробному изложению настоящего изобретения следует отметить, что одинаковые элементы на чертежах обозначены одними и теми же позициями.

Как видно из фиг. 1-5, первый предпочтительный вариант выполнения модуля 4 с полупроводниковыми микросхемами в соответствии с настоящим изобретением содержит первую полупроводниковую микросхему 40, диэлектрический ленточный слой 5 и вторую полупроводниковую микросхему 6.

Первая полупроводниковая микросхема 40 имеет монтажную поверхность 42 под контактные площадки с множеством расположенных на ней первых контактных площадок 41. В этом варианте осуществления изобретения первая полупроводниковая микросхема 40 представляет собой микросхему памяти. Диэлектрический ленточный слой 5 имеет противоположные первую и вторую адгезионные поверхности 50, 51. Предусматривается применение термоотверждаемого клея 55 для нанесения на первую адгезионную поверхность 50, благодаря чему поверхность 50 может быть сцеплена - приклеена к монтажной поверхности 42 под контактные площадки на первой полупроводниковой микросхеме 40 во время выполнения операции термоотверждения. Предусматривается применение обычной технологии лазерной резки для выполнения множества отверстий 52 в диэлектрическом ленточном слое 5 в местах расположения первых контактных площадок 41 для того, чтобы обнажить последние.

Каждое из отверстий 52 ограничено стенкой 53, которая соответственно с соответствующей отверстию 52 одной из первых контактных площадок 41 образуют приемное пространство под контакт. Предусматривается размещение множества электропроводных контактов 54 соответственно в приемных пространствах под контакты. В данном варианте осуществления изобретения в каждое приемное пространство под контакт вложен оловянный шарик, который и служит в качестве электропроводного контакта 54.

Вторая полупроводниковая микросхема 6 имеет монтажную поверхность 61 для монтажа микросхемы, выполненную с множеством расположенных на ней вторых контактных площадок 60, которые должны быть совмещены с электропроводными контактами 54 и соединены с ними. В этом варианте осуществления изобретения вторая полупроводниковая микросхема 6 представляет собой микросхему процессора, такого как процессор видеоданных, графический процессор, либо контроллер интегральной схемы для специальных применений. Проводится операция термоотверждения, чтобы соединить электропроводные контакты 54 со вторыми контактными площадками 60, а также, чтобы сцепить, в данном случае приклеить поверхность 61 для монтажа микросхемы ко второй адгезионной поверхности 51 на диэлектрическом ленточном слое 5. Предпочтительно, чтобы вторая поверхность 51 была покрыта термоотверждаемым клеем 55, температура отверждения которого ниже, чем температура плавления электропроводных контактов 54. Таким образом, монтажная поверхность 61 для монтажа микросхемы будет уже сцеплена со второй адгезионной поверхностью 51 еще до расплавления электропроводных контактов 54, благодаря чему будет обеспечена герметизация приемных пространств под контакты, в результате чего расплав электропроводного контакта 54 будет предохранен от вытекания из соответствующего приемного пространства под этот контакт, что позволит избежать образования нежелательных соединений с соседними электропроводными контактами 54.

Затем вторая полупроводниковая микросхема 6 монтируется в контактной рамке 7 обычным способом. После этого с использованием известных технологических приемов осуществляют формовку пластмассового корпуса 8, в который упаковывают первую и вторую полупроводниковые микросхемы 40, 6 и контактную рамку 7, что и является завершающей операцией при изготовлении модуля 4 с полупроводниковыми микросхемами.

Как видно из фиг. 6, на которой показан второй предпочтительный вариант выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением, может быть осуществлен монтаж двух или более первых полупроводниковых микросхем 40 на второй полупроводниковой микросхеме 6 с использованием при этом способа, аналогичного примененному при изготовлении первого предпочтительного варианта выполнения.

Как видно из фиг. 7, третий предпочтительный вариант выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением показан, как, по существу, аналогичный первому варианту его выполнения. Однако в этом варианте осуществления изобретения вместо того, чтобы быть смонтированной на контактной рамке, вторая полупроводниковая микросхема 6 смонтирована на печатной плате 9, при этом вторая полупроводниковая микросхема 6 соединена электрически с третьими контактными площадками 90, расположенными на печатной плате 9. После этого при использовании известных технологических приемов осуществляют формовку пластмассового корпуса 8, в который упаковывают первую и вторую полупроводниковые микросхемы 40, 6.

Как видно из фиг. 8, на которой показан четвертый предпочтительный вариант выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением, третий предпочтительный вариант его выполнения может быть модифицирован таким образом, чтобы был осуществлен монтаж двух или более первых полупроводниковых микросхем 40 на второй полупроводниковой микросхеме 6.

Как видно из фиг. 9, в пятом предпочтительном варианте выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением вместо того, чтобы в качестве электропроводных контактов использовать оловянные шарики, для формирования каждого контакта 54' применена электропроводная паста, к примеру, такая как электропроводная серебряная паста.

Как видно из фиг. 10 и 11, в шестом предпочтительном варианте выполнения модуля с полупроводниковыми микросхемами в соответствии с настоящим изобретением каждый контакт 54'' сформирован путем размещения электропроводного металлического материала 56, к примеру, такого как золотой или алюминиевый шарик, в каждом приемном пространстве под контакт. После этого осуществлен химический процесс электролитического осаждения, завершающий формирование каждого контакта 54'' до соединения с вторыми контактными площадками на второй полупроводниковой микросхеме (не показана).

Следует отметить, что тракт передачи сигнала между первой и второй полупроводниковыми микросхемами 40 и 6 становится существенно короче в модуле 4 с полупроводниковыми микросхемами, выполненном в соответствии с данным изобретением. Кроме того, поскольку первая полупроводниковая микросхема 40 не занимает места на печатной плате, площадь печатной платы может использоваться более эффективно, когда не ней устанавливается модуль 4 с полупроводниковыми микросхемами. Таким образом, достигаются цели, поставленные при создании настоящего изобретения.

Настоящее изобретение было описано в связи с теми вариантами его осуществления, которые считаются наиболее практичными и предпочтительными, однако, это отнюдь не означает, что данное изобретение ограничивается лишь раскрытыми здесь вариантами его осуществления, при этом подразумевается, что оно охватывает также различные его изменения, которые не выходят за пределы существа и объема в самой широкой их интерпретации с тем, чтобы заключать в себе все такие модификации и соответствующие изменения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1999 |

|

RU2168798C2 |

| КОМПЬЮТЕР В ВИДЕ АВТОРУЧКИ | 1999 |

|

RU2187145C2 |

| МИКРОКОНТАКТ ДЛЯ ПОВЕРХНОСТНОГО МОНТАЖА И МАССИВ МИКРОКОНТАКТОВ | 2018 |

|

RU2713908C2 |

| СПОСОБ ВСТРАИВАНИЯ КОМПОНЕНТА В ОСНОВАНИЕ | 2003 |

|

RU2327311C2 |

| УСТРОЙСТВО ИНТЕГРАЛЬНОЙ СХЕМЫ И СПОСОБ ИЗГОТОВЛЕНИЯ УСТРОЙСТВА ИНТЕГРАЛЬНОЙ СХЕМЫ | 2007 |

|

RU2419179C2 |

| МОДУЛЬ РАСПОЗНАВАНИЯ ОТПЕЧАТКОВ ПАЛЬЦЕВ И ЭЛЕКТРОННОЕ УСТРОЙСТВО | 2020 |

|

RU2810232C2 |

| МНОГОКРИСТАЛЬНАЯ МИКРОСХЕМА | 2017 |

|

RU2653183C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНЫХ ПЕЧАТНЫХ ПЛАТ | 2014 |

|

RU2574290C1 |

| СПОСОБ ВСТРАИВАНИЯ КОМПОНЕНТА В ОСНОВАНИЕ И ФОРМИРОВАНИЯ ЭЛЕКТРИЧЕСКОГО КОНТАКТА С КОМПОНЕНТОМ | 2003 |

|

RU2297736C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ОПТОЭЛЕКТРОННОЙ МИКРОСБОРКИ | 2008 |

|

RU2373605C1 |

Настоящее изобретение относится к модулю с полупроводниковыми микросхемами и способу его изготовления. Технический результат - создание модуля с полупроводниковыми микросхемами и способа изготовления данного модуля, при применении которых тракт передачи сигнала может быть укорочен для того, чтобы обеспечить минимальное время задержки. Также при применении вышеуказанных модуля с полупроводниковыми микросхемами и способа его изготовления на печатной плате может быть размещено больше количество микросхем памяти, при этом не требуется существенного увеличения размера печатной платы. Модуль (4) с полупроводниковыми микросхемами включает в себя первую и вторую полупроводниковые микросхемы (40, 6) и диэлектрический ленточный слой (5). Первая полупроводниковая микросхема (40) имеет монтажную поверхность под контактные площадки с расположенными на ней первыми контактными площадками. Диэлектрический ленточный слой (5) имеет противоположные первую и вторую адгезионные поверхности (51). Первая адгезионная поверхность сцеплена с монтажной поверхностью под контактные площадки на первой полупроводниковой микросхеме (40). Диэлектрический ленточный слой (5) выполнен с отверстиями, предусмотренными в местах расположения первых контактных площадок и предназначенными для обнажения последних. Каждое отверстие ограничено стенкой, которая совместно с соответствующей отверстию контактной площадкой образует приемное пространство под контакт. Предусматривается размещение электропроводных контактов (54) соответственно в приемных пространствах под контакты. Вторая полупроводниковая микросхема (6) имеет монтажную поверхность (61) для монтажа микросхемы, сцепленную с второй адгезионной поверхностью (51) диэлектрического ленточного слоя (5), с расположенными на этой поверхности контактными площадками (60), которые соединены с электропроводными контактами (54) обеспечением электрического соединения с первыми контактными площадками. Раскрывается также способ изготовления модуля (4) с полупроводниковыми микросхемами. 2 c и 19 з.п. ф-лы, 11 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| МНОГОСЛОЙНАЯ КОММУТАЦИОННАЯ ПЛАТА (ВАРИАНТЫ) | 1998 |

|

RU2133081C1 |

| УСТРОЙСТВО НА ИНТЕГРАЛЬНЫХ СХЕМАХ | 1992 |

|

RU2032964C1 |

| SU 227421 A, 29.01.1969 | |||

| МНОГОСЛОЙНАЯ НЕЧАТНАЯ ПЛАТА | 0 |

|

SU270029A1 |

| МНОГОСЛОЙНАЯ НЕЧАТНАЯ ПЛАТА | 0 |

|

SU270029A1 |

| Способ изготовления многослойных печатных плат | 1982 |

|

SU1019682A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| US 4585528 A, 29.04.1986 | |||

| US 3683105 A, 08.08.1972 | |||

| DE 4326104 А1, 09.02.1995. | |||

Авторы

Даты

2001-06-27—Публикация

1999-07-13—Подача