Изобретение относится к технике цифровой связи, а именно к устройствам для выделения компонентных потоков (каналов) в цифровых системах передачи информации с временным уплотнением.

Известно устройство для выделения цифровых потоков [1], содержащее генераторное оборудование, канальный распределитель, l-q блоки синхронного сопряжения, соединенные определенным образом.

Данное устройство распределяет многоканальный сигнал между соответствующими блоками синхронного сопряжения и восстанавливает первоначальную скорость компонентных потоков. Недостатком этого устройства является невозможность одним и тем же устройством осуществлять демультиплексирование различных передач плезиохронной цифровой иерархии как соответствующих рекомендациям Международного консультативного комитета по телеграфии и телефонии (МККТТ), так и большого количества нестандартизированных цифровых передач.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа многоканальное устройство приема дискретной информации [2], содержащее преобразователь кода, приемник синхросигнала, генераторный блок; клавиатурный блок, N канальных блоков, каждый из которых состоит из двух шифраторов, двух блоков сравнения, счетчика, элемента ИЛИ, блока синхронного сопряжения, блока исключения сигнала, состоящего из шифратора, элемента задержки, элемента И. В этом многоканальном устройстве для приема дискретной информации канальные блоки представляют собой устройство для демультиплексирования, которое выделяет компонентные потоки в системах с временным уплотнением.

Недостатками данного устройства являются:

- невозможность одним и тем же устройством осуществлять демультиплексирование различных передач плезиохронной цифровой иерархии как соответствующих рекомендациям МККТТ, так и большого количества нестандартизированных цифровых передач;

- отсутствие в устройстве блока дестаффингования, что при демультиплексировании цифровых потоков со стаффингом приводит к нарушению временной структуры выделяемых компонент (каналов) и, следовательно, невозможности дальнейшей их синхронизации;

- реализация канальных блоков требует достаточно больших аппаратных затрат, что приводит к усложнению устройства.

Технической задачей изобретения является расширение функциональных возможностей за счет обеспечения демультиплексирования одним устройством различных цифровых передач и сокращение оборудования.

Указанная задача решается тем, что в известное устройство, содержащее k канальных блоков, каждый из которых состоит из выделителя компонентных позиций, блока обработки стаффинга и информационного триггера, причем информационный И и тактовый T входы устройства для демультиплексирования соединены с информационным И и тактовым Т входами выделителей компонентных позиций и блоков обработки стаффинга соответствующих канальных блоков, вход сигнала конца цикла КЦ устройства для демультиплексирования соединен с соответствующим входом блоков обработки стаффинга, выходы сигналов наличия стаффинга СТ которых соединены с соответствующими входами выделителей компонентных позиций, а информационные выходы И последних соединены с соответствующими входами D информационных триггеров, информационный выход И информационного триггера соответствующего канального блока соединен с соответствующим информационным выходом И1, . . . ,Иk устройства для демультиплексирования, согласно изобретению введены устройство настройки и управления, а в каждый канальный блок - оперативное запоминающее устройство и формирователь тактов, причем адресные входы 1,..,N устройства для демультиплексирования соединены с адресными входами 1,..,N устройства настройки и управления, управляющие входы устройства для демультиплексирования соединены с управляющими входами устройства настройки и управления, тактовый вход Т устройства для демультиплексирования соединен с тактовыми входами Т формирователей тактов, адресные выходы 1,..,N устройства настройки и управления соединены с соответствующими адресными входами оперативных запоминающих устройств, выходы сигналов выбора микросхем CE1,...,CEk устройства настройки и управления соединены с входами сигналов выбора микросхемы СЕ оперативных запоминающих устройств соответствующих канальных блоков, выходы сигналов чтения ОЕ и сигналов записи WE устройства настройки и управления соединены соответственно с входами сигналов чтения ОЕ и сигналов записи WE оперативных запоминающих устройств, выходы сигналов параметров настройки Q1, Q2, Q3, Q4 устройства настройки и управления соединены соответственно с входами/выходами разрядов сигналов позиций выделяемой компоненты ПК, сигналов позиций управления стаффингом ПУ, позиции стаффинга ПС и сигналов позиций тактовой подставки ПТ оперативных запоминающих устройств, задающие режим работы формирователей тактов выходы 1, 2, 3 устройства настройки и управления соединены с соответствующими входами формирователей тактов, задающий мажоритарность работы блока обработки стаффинга выход 4 устройства настройки и управления соединен с входом КР блока обработки стаффинга, в каждом канальном блоке вход сигналов позиций выделяемой компоненты ПК и выход сигналов позиций стаффинга ПС выделителя компонентных позиций соединены с соответствующими выходами оперативного запоминающего устройства, выход сигналов позиций управления стаффингом ПУ оперативного запоминающего устройства соединен с входом разрешения записи ЕС блока обработки стаффинга, выход сигналов позиций тактовой подставки ПТ оперативного запоминающего устройства соединен с соответствующим входом формирователя тактов, выход сигналов позиций выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ выделителя компонентных позиций соединен с соответствующим входом формирователя тактов, тактовый выход Т которого соединен с тактовым входом К информационного триггера и является тактовым выходом T1,...,Tk соответствующего канального блока устройства для демультиплексирования.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: устройства настройки и управления, ОЗУ и формирователя тактов.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежной областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для демультиплексирования с указанными связями придает ему новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют расширить функциональные возможности и обеспечить простыми средствами формирование длительности тактовых сигналов выделяемых компонент при одновременном сокращении оборудования.

Таким образом, изобретение соответствует критерию "Изобретательский уровень", так как оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи с временным уплотнением цифровых потоков.

Таким образом, изобретение соответствует критерию "Промышленная применимость".

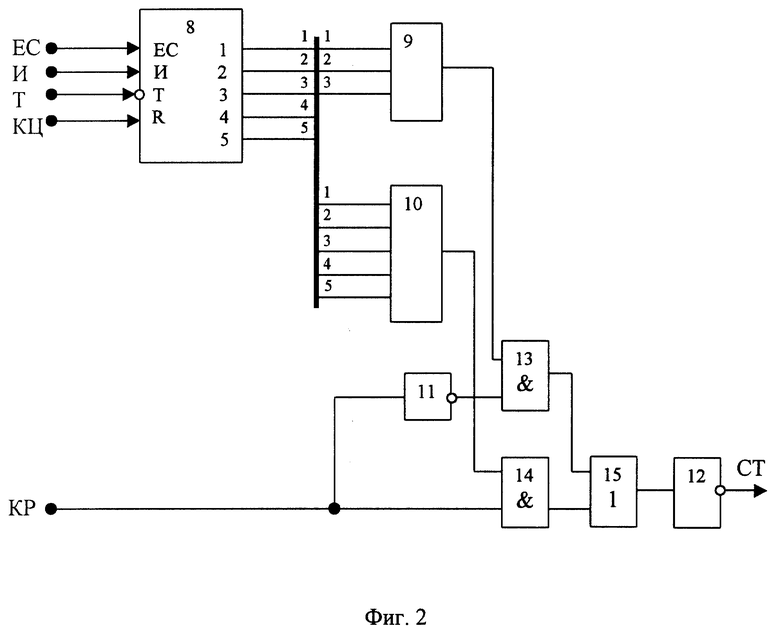

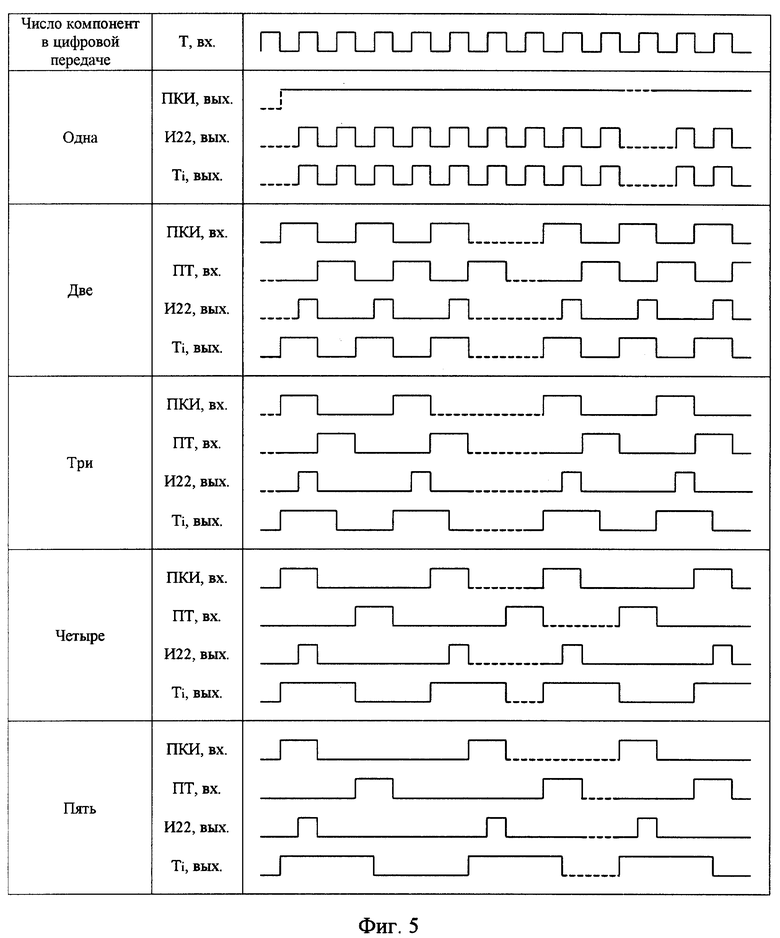

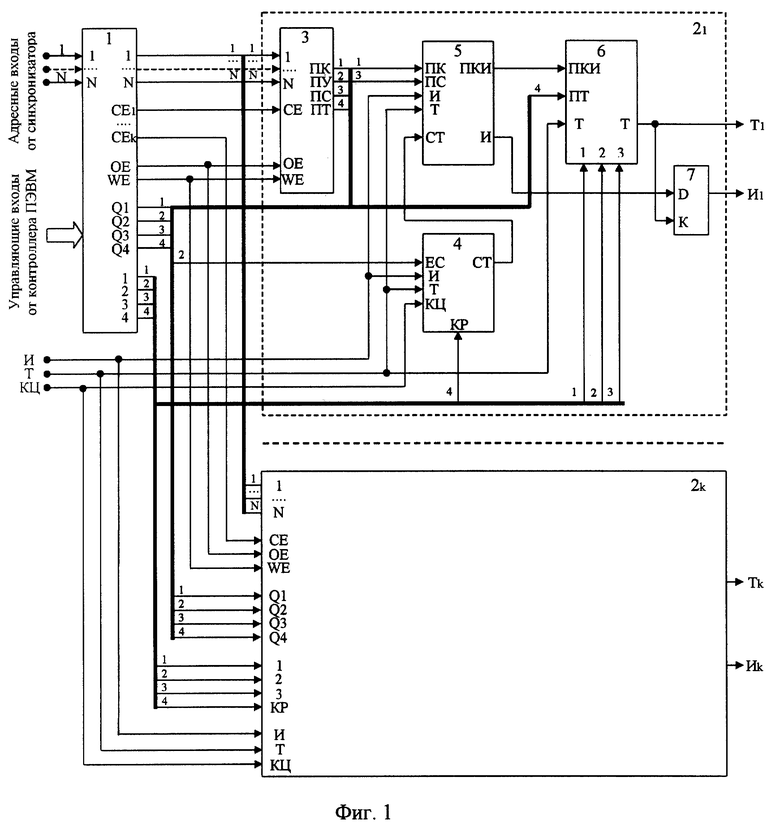

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства для демультиплексирования, на фиг. 2 - структурная электрическая схема блока обработки стаффинга, на фиг. 3 - принципиальная электрическая схема выделителя компонентных позиций, на фиг. 4 - принципиальная электрическая схема формирователя тактов, на фиг. 5 - временная диаграмма работы формирователя тактов при различном количестве компонент в цифровой передаче.

Устройство для демультиплексирования (фиг. 1) содержит устройство настройки и управления 1, канальные блоки 21,...,2k, каждый из которых состоит из оперативного запоминающего устройства 3, блока обработки стаффинга 4, выделителя компонентных позиций 5, формирователя тактов 6, информационного триггера 7, причем адресные 1,...,N и управляющие входы устройства для демультиплексирования соединены соответственно с адресными 1,...,N и управляющими входами устройства настройки и управления 1, информационный вход И устройства для демультиплексирования соединен с соответствующими входами блоков обработки стаффинга 4 и выделителей компонентных позиций 5 канальных блоков 21, ...,2k, тактовый вход Т устройства для демультиплексирования соединен с соответствующими входами блоков обработки стаффинга 4, выделителей компонентных позиций 5 и формирователей тактов 6 канальных блоков 21,...,2k, вход сигнала конца цикла КЦ устройства для демультиплексирования соединен с соответствующими входами блоков обработки стаффинга 4 канальных блоков 21,.. . ,2k, адресные выходы 1,...,N устройства настройки и управления 1 соединены с адресными входами 1,...,N оперативных запоминающих устройств 3 канальных блоков 21,...,2k, выходы сигналов выбора микросхемы CE1...CEk устройства настройки и управления 1 соединены с входами выбора микросхем CE оперативных запоминающих устройств 3 соответствующих канальных блоков 21,...,2k, выходы сигналов чтения ОЕ и сигналов записи WE устройства настройки и управления 1 соединены с соответствующими входами оперативных запоминающих устройств 3 канальных блоков 21,...,2k, выходы сигналов параметров настройки Q1, Q2, Q3, Q4 устройства настройки и управления 1 соединены соответственно с входами/выходами сигналов позиций выделяемой компоненты ПК, сигналов позиций управления стаффингом ПУ, сигналов позиции стаффинга ПС и сигналов позиции тактовой подставки ПТ оперативных запоминающих устройств 3 канальных блоков 21, . ..,2k, задающие режим работы формирователей тактов выходы сигналов 1, 2, 3 устройства настройки и управления 1 соединены с соответствующими входами формирователей тактов 6 канальных блоков 21,...,2k, задающий мажоритарность работы блока обработки стаффинга выход 4 устройства настройки и управления 1 соединен с входами сигнала критерия мажоритарности КР блоков обработки стаффинга 4 канальных блоков 21,...,2k, в каждом канальном блоке 21,...,2k выходы сигналов позиций выделяемой компоненты ПК и сигналов позиций стаффингов оперативного запоминающего устройства 3 соединены с соответствующими входами выделителя компонентных позиций 5, выход сигналов позиций управления стаффингом ПУ оперативного запоминающего устройства 3 соединен с входом разрешения записи ЕС блока обработки стаффинга 4, выход сигналов тактовой подставки ПТ оперативного запоминающего устройства 3 соединен с соответствующим входом формирователя тактов 6, выход сигнала наличия стаффинга СТ блока обработки стаффинга 4 соединен с соответствующим входом выделителя компонентных позиций 5, выход сигналов позиции выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ которого соединен с соответствующим входом формирователя тактов 6, а информационный выход И - с входом D информационного триггера 7, тактовый выход Т формирователя тактов 6 соединен с тактовым входом К информационного триггера 7 и является тактовым выходом T1,...,Tk соответствующего канального блока 21,...,2k устройства для демультиплексирования, а выход И информационного триггера 7 является информационным выходом И1,...,Иk соответствующего канального блока 21,...,2k устройства для демультиплексирования.

Блок обработки стаффинга 4 (фиг. 2) содержит регистр 8, элементы мажоритарности 9 и 10, инверторы 11 и 12, элементы И 13, 14, элемент ИЛИ 15, причем входы разрешения записи ЕС, информационный И, тактовый Т, сигнала конца цикла КЦ регистра 8 соединены с соответствующими входами блока обработки стаффинга 4, а информационные выходы 1, 2, 3, 4, 5 - с входами 1, 2, 3 элемента мажоритарности 9 и входами 1, 2, 3, 4, 5 элемента мажоритарности 10, вход сигнала критерия мажоритарности КР блока обработки стаффинга 4 соединен с входом инвертора 11 и вторым входом элемента И 14, первый вход которого соединен с выходом элемента мажоритарности 10, выход инвертора 11 соединен с вторым входом элемента И 13, первый вход которого соединен с выходом элемента мажоритарности 9, выходы элементов И 13 и И 14 соединены с входами элемента ИЛИ 15, выход которого соединен с входом инвертора 12, выход инвертора 12 соединен с выходом сигнала наличия стаффинга СТ блока обработки стаффинга 4.

Выделитель компонентных позиций 5 (фиг. 3) содержит триггеры 16, 17 и 18, элементы ИЛИ 19, 20, элемент И 21, причем вход сигнала выделяемой компоненты ПК выделителя компонентных позиций 5 соединен с входом D триггера 16 и первым входом элемента ИЛИ 19, вход сигнала позиции стаффинга ПС выделителя компонентных позиций 5 соединен с входом D триггера 17 и вторым входом элемента ИЛИ 19, выход которого соединен с входом разрешения записи ЕС триггера 18, вход сигнала наличия стаффинга СТ выделителя компонентных позиций 5 соединен с первым входом элемента И 21, второй вход которого соединен с выходом триггера 17, информационный вход И выделителя компонентных позиций 5 соединен с входом D триггера 18, а тактовый Т - с входами К триггеров 16, 17 и 18, выход триггера 16 соединен с первым входом элемента ИЛИ 20, второй вход которого соединен с выходом элемента И 21, а выход - с выходом сигналов позиций выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ выделителя компонентных позиций 5, выход триггера 18 соединен с информационным выходом И выделителя компонентных позиций 5.

Формирователь тактов 6 (фиг. 4) содержит элементы И 22, 23, 24, 25, 26, триггеры 27, 28 и 29, элемент ИЛИ 30, причем вход сигналов позиций выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ формирователя тактов 6 соединен с тактовыми входами К триггеров 28, 29 и с первым входом элемента И 22, вход сигналов позиций тактовой подставки ПТ формирователя тактов 6 соединен с входом D триггера 27, тактовый вход Т формирователя тактов 6 соединен с входом К триггера 27 и вторыми входами элементов И 22 и И 23, задающие режим работы формирователя тактов 6 входы 1, 2, 3 формирователя тактов 6 соединены с вторыми входами соответственно элементов И 24, И 25, И 26, выход триггера 27 соединен с входом установки в ноль R триггера 28 и первым входом элемента И 23, выход которого соединен с входом установки в ноль R триггера 29, первые входы элементов И 24, 25, 26 соединены соответственно с выходами элемента И 22, триггера 28 и триггера 29, выходы элементов И 24, 25, 26 соединены с входами элемента ИЛИ 30, выход которого соединен с тактовым выходом Т формирователя тактов 6, входы D триггеров 28 и 29 соединены с шиной питания.

Устройство для демультиплексирования работает следующим образом.

Перед началом работы осуществляется его настройка на параметры определенной цифровой передачи. При этом в оперативные запоминающие устройства 3 канальных блоков 21,...,2k для соответствующих выделяемых компонент по определенным адресам записываются единичные биты, соответствующие наличию позиций выделяемой компоненты (разряд ПК), позиций сигналов управления стаффингом (разряд ПУ), позиций бит стаффинга (разряд ПС) и позиций тактовой подставки (разряд ПТ). Выбор настраиваемого оперативного запоминающего устройства 3 осуществляется с помощью сигнала нулевой полярности, подаваемого на вход выбора микросхемы СЕ. Порядок настройки выбранного оперативного запоминающего устройства 3 следующий. Сигналом чтения ОЕ единичного уровня, поступающим с выхода устройства настройки и управления 1 на вход чтения ОЕ оперативного запоминающего устройства 3, последнее устанавливается в режим записи. Адресные сигналы, поступающие от контроллера персональной электронной вычислительной машины (ПЭВМ) на управляющие входы устройства настройки и управления 1, коммутируются последним на адресные входы 1,...,N оперативного запоминающего устройства 3. Сигналы параметров настройки, поступающие от контроллера ПЭВМ на входы устройства настройки и управления 1, с выходов сигналов параметров настройки Q1, Q2, Q3, Q4 последнего поступают соответственно на входы сигналов позиций выделяемой компоненты ПК, сигналов позиции управления стаффингом ПУ, сигналов позиции стаффинга ПС, сигналов позиций тактовой подставки ПТ оперативного запоминающего устройства 3. Далее по сигналу записи WE, поступающему от контроллера ПЭВМ, через устройство настройки и управления 1, на входы записи WE оперативных запоминающих устройств 3, в выбранном устройстве осуществляется запоминание задаваемых параметров. Затем изменяются адресные сигналы и параметры настройки вновь записываются в выбранное оперативное запоминающее устройство 3. Как было описано выше, параметры настройки последовательно записываются в оперативные запоминающие устройства 3 канальных блоков 21,...,2k. Также при настройке в устройстве настройки и управления 1 запоминаются параметры, определяющие режим работы формирователя тактов 6 - выходы 1, 2, 3 устройства настройки и правления 1, а также значение критерия мажоритарности - выход 4 устройства настройки и управления 1. Режимы работы формирователя тактов будут описаны ниже.

После настройки устройство для демультиплексирования переходит в режим работы. При этом по сигналу, поступившему от контроллера ПЭВМ в устройство настройки и управления 1, последнее подключает адресные входы оперативных запоминающих устройств 3 к адресным выходам устройства для цикловой синхронизации, на входы выбора микросхемы СЕ сигнала чтения ОЕ оперативных запоминающих устройств 3 подается разрешающий сигнал нулевой полярности, на входы сигнала записи WE - сигнал единичной полярности, переводящие оперативные запоминающие устройства 3 в режим чтения. При этом считывание данных из этих устройств осуществляется при смене адресных сигналов на их адресных входах 1,...,N.

В рабочем режиме устройство для демультиплексирования осуществляет выделение компонентных позиций с учетом наличия стаффингования, а также осуществляет формирование тактовых сигналов в зависимости от количества компонент в цифровой передаче.

Стаффингование предназначено для согласования скоростей источников информации и объединяющей их системы передачи. Как правило, информационная скорость системы передачи выше, чем суммарная скорость составляющих компонент, поэтому в основном применяется положительное стаффингование. При этом в объединяющей системе передачи для каждой компоненты выделяется специальная позиция, на которой может передаваться или информационный бит, или незначащий (бит стаффинга). Для определения наличия бита стаффинга для каждой компоненты выделяются три или пять, в зависимости от вида передачи, позиций управления стаффингом. Если передается бит стаффинга, то на этих позициях передаются единичные биты. С учетом искажения бит цифрового потока помехами решение о наличии бита стаффинга принимается по большинству единичных бит, передаваемых на позициях управления стаффингом. Таким образом, используются критерии мажоритарности "2 из 3" в одном случае или "3 из 5" - в другом. Предлагаемое изобретение реализовано с учетом положительного стаффингования.

Демультиплексирование входного цифрового потока происходит следующим образом. С выхода устройства для цикловой синхронизации на информационный И, тактовый Т, адресные 1,...,N и вход сигнала конца цикла КЦ устройства для демультиплексирования поступают соответственно информационные, тактовые, адресные сигналы и сигнал конца цикла. Наличие бита стаффинга определяется блоком обработки стаффинга 4 (фиг. 2). При этом сигналом на входе критерия мажоритарности КР блока обработки стаффинга 4 задается соответствующий передаче критерий мажоритарности. Нулевой уровень сигнала на входе критерия мажоритарности КР соответствует критерию "2 из 3", а единичный - "3 из 5". При критерии мажоритарности "2 из 3" через инвертор 11 открывается по одному входу элемент И 13, на другой вход которого поступает сигнал с выхода элемента мажоритарности 9. При критерии мажоритарности "3 из 5" открывается по одному входу элемент И 14, на другой вход которого поступает сигнал с выхода элемента мажоритарности 10. На входы И, Т и R регистра 8 поступают соответственно сигналы с информационного И, тактового Т и конца цикла КЦ устройства для демультиплексирования. Разрешение записи информации в регистр 8 блока обработки стаффинга 4 осуществляется сигналом, поступившим с выхода сигналов позиций управления стаффингом ПУ оперативного запоминающего устройства 3 на вход разрешения записи ЕС регистра. Таким образом, в регистр записываются биты, находящиеся на позициях управления стаффингом. С выходов 1, 2, 3, 4, 5 разрядов регистра 8 данные поступают на входы соответственно 1, 2, 3 элемента мажоритарности 9 и входы 1, 2, 3, 4, 5 элемента мажоритарности 10. Элемент мажоритарности 9 формирует положительный отклик при выполнении критерия мажоритарности "2 из 3", а элемент 10 - "3 из 5". С выхода открытого элемента И 13 или И 14 сигнал о наличии бита стаффинга через элементы ИЛИ 15 и инвертор 12 поступает на выход сигнала наличия стаффинга СТ блока обработки стаффинга 4 и далее на соответствующий вход выделителя компонентных позиций 5.

Выделитель компонентных позиций 5 (фиг. 3) работает следующим образом. На его информационный И и тактовый Т входы поступают соответственно информационные и тактовые сигналы с входов И и Т устройства для демультиплексирования, на входы сигналов позиций выделяемой компоненты ПК и сигналов позиции стаффинга ПС поступают сигналы с соответствующих выходов оперативного запоминающего устройства 3, а на вход сигнала наличия стаффинга СТ - с соответствующего выхода блока обработки стаффинга 4. Триггеры 16, 17, 18 предназначены для согласования по времени входных сигналов выделителя компонентных позиций 5. Триггер 18 осуществляет запись битов, находящихся на информационных позициях и позициях стаффинга выделяемой компоненты. Работа триггера 18 разрешается сигналами позиций выделяемой компоненты или сигналом позиции стаффинга, поступающими соответственно с входов ПК и ПС выделителя компонентных позиций 5, через элемент ИЛИ 19 на разрешающий вход ЕС триггера 18. Сигналы с триггера 18 через информационный выход И выделителя компонентных позиций 5 поступают на вход D информационного триггера 7 соответствующего канального блока. Наличие или отсутствие информационного бита на позиции стаффинга определяется сигналом, поступившим с выхода сигнала наличия стаффинга СТ блока обработки стаффинга 4 на соответствующий вход выделителя компонентных позиций 5, при этом нулевой уровень указанного сигнала соответствует наличию бита стаффинга, а единичный - информационному биту. Если передается бит стаффинга, то нулевой уровень сигнала наличия стаффинга СТ по второму входу закрывает элемент И 21, запрещая прохождение через него сигнала с выхода триггера 17. В этом случае на выход сигналов позиции выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ выделителя компонентных позиций 5 через элемент ИЛИ 20 поступают сигналы только с триггера 16, соответствующие информационным позициям выделяемой компоненты. Если же на позиции стаффинга передается информационный бит выделяемой компоненты, то единичный уровень сигнала наличия стаффинга СТ открывает по второму входу элемент И 21, разрешая прохождение на выход ПКИ через элементы И 21 и ИЛИ 20 сигнала с выхода триггера 17, то есть на выход ПКИ выделителя компонентных позиций 5 будут поступать как сигналы, соответствующие информационным позициям, так и сигналы, соответствующие позициям стаффинга. Сигнал с выхода ПКИ выделителя компонентных позиций 5 поступает на соответствующий вход формирователя тактов 6.

Формирователь тактов 6 (фиг. 4) предназначен для выравнивания длительностей полупериодов тактовых импульсов выделяемых компонент. Временная диаграмма работы формирователя тактов 6 при различном числе компонент в цифровой передаче представлена на фиг. 5. Для примера на временной диаграмме показана работа формирователя тактов 6 для цифровых передач, объединяющих одну, две, три, четыре или пять компонент. На временной диаграмме сигналы на выходе элемента И 22 является невыравненными тактовыми импульсами выделенной компоненты. При этом если количество компонент в цифровой передаче больше двух, то длительность положительного полупериода невыравненного тактового сигнала выделенной компоненты тем меньше длительности отрицательного полупериода, чем больше в передаче компонент, то есть скважность тактовых импульсов уменьшается при увеличении числа компонент. Так как выделенные компоненты цифровых передач высшего уровня поступают на дальнейшую обработку в системы низшего уровня, то малое значение скважности тактового сигнала приводит к более жестким требованиям по скорости к применяемой в этих системах элементной базе. Введенный в устройство для демультиплексирования формирователь тактов 6 позволяет формировать тактовый сигнал выделяемой компоненты со скважностью, близкой к 1.

Формирователь тактов 6 (фиг. 4) работает следующим образом. На его тактовый вход Т поступает сигнал с соответствующего входа устройства для демультиплексирования, на вход ПТ поступает сигнал позиции тактовой подставки с соответствующего выхода оперативного запоминающего устройства 3, на вход сигналов позиций выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ поступает сигнал с соответствующего выхода ПКИ выделителя компонентных позиций 5. На входы 1, 2, 3 формирователя тактов поступают сигналы, задающие режим его работы, с соответствующих выходов устройства настройки и управления 1. Формирователь тактов 6 может работать в трех режимах.

В первом режиме осуществляется формирование тактового сигнала при демультиплексировании цифровой передачи, состоящей из одной компоненты и служебных позиций, называемой радиоциклом. В этом случае сигнал единичной полярности с входа 1 поступает на второй вход элемента И 24, разрешая его работу. Элементы И 25 и И 26 закрыты сигналами нулевой полярности, поступающими с входов 2 и 3 формирователя тактов 6. При наличии информационных бит выделяемой компоненты сигналом ПКИ, поступающим с входа ПКИ на первый вход элемента И 22, последний открывается, тем самым разрешая прохождение тактового сигнала с входа Т через открытые элементы И 22, И 24 и через элемент ИЛИ 30 на тактовый выход Т формирователя тактов 6.

Во втором режиме осуществляется формирование тактового сигнала при демультиплексировании цифровой передачи, состоящей из четного количества компонент. В этом случае сигнал единичной полярности с входа 2 поступает на второй вход элемента И 25, разрешая его работу. Элементы И 24 и И 26 закрыты сигналами нулевой полярности, поступающими с входов 1 и 3 формирователя тактов 6. Положительным фронтом сигнала ПКИ, поступившего на тактовый вход К триггера 28, последний устанавливается в единичное состояние. После этого сигнал позиций тактовой подставки ПТ поступает на вход D триггера 27, который по заднему фронту тактового импульса устанавливается в единичное состояние. Триггер 27 предназначен для согласования по времени входного сигнала позиции тактовой подставки ПТ формирователя тактов 6. Сигналом с триггера 27, поступившим на вход установки в ноль R триггера 28, последний устанавливается в нулевое состояние. Сформированный тактовый сигнал с выхода триггера 28 через открытый элемент И 25 и элемент ИЛИ 30 поступает на тактовый выход Т формирователя тактов 6.

В третьем режиме осуществляется формирование тактового сигнала при демультиплексировании цифровой передачи, состоящей из нечетного количества компонент, начиная с трех. В этом случае сигнал единичной полярности с входа 3 формирователя тактов 6 поступает на второй вход элемента И 26, разрешая его работу. Элементы И 24 и И 25 закрыты сигналами нулевой полярности, поступающими с входов 1 и 2 формирователя тактов 6. Положительным фронтом сигнала ПКИ, поступившего на вход К триггера 29, последний устанавливается в единичное состояние. После этого сигнал позиции тактовой подставки ПТ поступает на вход D триггера 27, который по заднему фронту тактового импульса устанавливается в единичное состояние, разрешая по первому входу работу элемента И 23, на второй вход которого поступает тактовый импульс. Сигналом, поступившим с выхода элемента И 23 на вход установки в ноль R триггера 29, последний устанавливается в нулевое состояние. Сформированный тактовый сигнал с выхода триггера 29 через открытый элемент И 26 и элемент ИЛИ 30 поступает на тактовый выход Т формирователя тактов 6. Таким образом, для цифровых передач с числом компонент две и более передний фронт тактового импульса формируется с помощью сигнала ПКИ наличия информационного бита, а задний - с помощью сигнала ПТ позиции тактовой подставки.

С выхода Т формирователя тактов 6 тактовый сигнал поступает на вход К информационного триггера 7 и на соответствующий тактовый выход устройства для демультиплексирования. С выхода И информационного триггера сигнал поступает на соответствующий информационный выход устройства для демультиплексирования.

Для технической реализации устройства для демультиплексирования используются статические ОЗУ и программируемые пользователем логические интегральные схемы (ППЛИС).

Предлагаемое изобретение позволяет осуществить демультиплексирование различных цифровых передач плезиохронной цифровой иерархии как соответствующих рекомендациям МККТТ, так и большого количества нестандартизированных цифровых передач, при значительном сокращении оборудования.

Источники информации

1. Левин Л. С., Плоткин М.А. Цифровые системы передачи информации. М.: Радио и связь.- С. 87. Рис. 3.24.

2. Авторское свидетельство СССР N 1292200, H 04 L 25/40.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2003 |

|

RU2242842C1 |

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2005 |

|

RU2296431C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА ПРИЕМА, ДЕМОДУЛЯЦИИ И ОБРАБОТКИ СИГНАЛОВ I-IV УРОВНЕЙ ИЕРАРХИЧЕСКОГО УПЛОТНЕНИЯ | 2001 |

|

RU2224375C2 |

| УСТРОЙСТВО ДЕСКРЕМБЛИРОВАНИЯ | 2006 |

|

RU2310991C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| САМОСИНХРОНИЗИРУЕМОЕ УСТРОЙСТВО ДЕСКРЕМБЛИРОВАНИЯ | 2001 |

|

RU2203522C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

Изобретение относится к технике цифровой связи, а именно к устройствам для демультиплексирования цифровых систем передачи информации с временным уплотнением. Технический результат - расширение функциональных возможностей за счет обеспечения демультиплексирования одним устройством различных цифровых передач. Устройство для демультиплексирования содержит устройство настройки и управления 1, канальные блоки 21...2k, оперативное запоминающее устройство 3, блок обработки стаффинга 4, выделитель компонентных позиций 5, формирователь тактов 6 и информационный триггер 7. Устройство для демультиплексирования позволяет осуществить разуплотнение различных цифровых передач плезиохронной цифровой иерархии как соответствующих рекомендаций МККТТ, так и большого количества нестандартизированных цифровых передач. 5 ил.

Устройство для демультиплексирования, содержащее к канальных блоков, каждый из которых состоит из выделителя компонентных позиций, блока обработки стаффинга и информационного триггера, причем информационный И и тактовый Т входы устройства для демультиплексирования соединены с информационным И и тактовым Т входами выделителей компонентных позиций и блоков обработки стаффинга соответствующих канальных блоков, вход сигнала конца цикла КЦ устройства для демультиплексирования соединен с соответствующим входом блоков обработки стаффинга, выходы сигналов наличия стаффинга СТ которых соединены с соответствующими входами выделителей компонентных позиций, а информационные выходы И последних соединены с соответствующими входами D информационных триггеров, информационный выход И информационного триггера соответствующего канального блока соединен с соответствующим информационным выходом И1, . ..,Ик устройства для демультиплексирования, отличающееся тем, что введены устройство настройки и управления, а в каждый канальный блок - оперативное запоминающее устройство и формирователь тактов, причем адресные входы 1, . ...,N устройства для демультиплексирования соединены с адресными входами 1, . . .....,N устройства настройки и управления, управляющие входы устройства для демультиплексирования соединены с управляющими входами устройства настройки и управления, тактовый Т вход устройства для демультиплексирования соединен с тактовыми входами Т формирователей тактов, адресные выходы 1,...,N устройства настройки и управления соединены с соответствующими адресными входами оперативных запоминающих устройств, выходы сигналов выбора микросхем СЕ1, .....,СЕк устройства настройки и управления соединены с входами сигналов выбора микросхемы СЕ оперативных запоминающих устройств соответствующих канальных блоков, выходы сигналов чтения ОЕ и сигналов записи WE устройства настройки и управления соединены соответственно с входами сигналов чтения ОЕ и сигналов записи WE оперативных запоминающих устройств, выходы сигналов параметров настройки Q1, Q2, Q3, Q4 устройства настройки и управления соединены соответственно с входами/выходами разрядов сигналов позиций выделяемой компоненты ПК, сигналов позиций управления стаффингом ПУ, позиции стаффинга ПС и сигналов позиций тактовой подставки ПТ оперативных запоминающих устройств, задающие режим работы формирователей тактов выходы 1,2,3 устройства настройки и управления соединены с соответствующими входами формирователей тактов, задающий мажоритарность работы блока обработки стаффинга выход 4 устройства настройки и управления соединен с входом критерия мажоритарности КР блока обработки стаффинга, в каждом канальном блоке вход сигналов позиций выделяемой компоненты ПК и выход сигналов позиций стаффинга ПС выделителя компонентных позиций соединены с соответствующими выходами оперативного запоминающего устройства, выход сигналов позиций управления стаффингом ПУ оперативного запоминающего устройства соединен с входом разрешения записи ЕС блока обработки стаффинга, выход сигналов позиций тактовой подставки ПТ оперативного запоминающего устройства соединен с соответствующим входом формирователя тактов, выход сигналов позиций выделяемой компоненты и позиции стаффинга этой компоненты при его отсутствии ПКИ выделителя компонентных позиций соединен с соответствующим входом формирователя тактов, тактовый выход Т которого соединен с тактовым входом К информационного триггера и является тактовым выходом Т1,....,Тк соответствующего канального блока устройства для демультиплексирования.

| Многоканальное устройство для приема дискретной информации | 1985 |

|

SU1292200A1 |

| ЛЕВИН Л.С., ПЛОТКИН М.А | |||

| ЦИФРОВЫЕ СИСТЕМЫ ПЕРЕДАЧИ ИНФОРМАЦИИ | |||

| - М.: РАДИО И СВЯЗЬ, с.87, рис.3.24 | |||

| DE 3046636 А1, 22.07.1982 | |||

| DE 3046658 А1, 15.07.1982 | |||

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

Авторы

Даты

2001-08-27—Публикация

2000-04-27—Подача