Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением.

Известны устройства для цикловой синхронизации [1, 2, 3], содержащие регистр сдвига, опознаватель циклового синхросигнала, анализатор совпадения синхросигнала, блок удержания и поиска синхронизма, генераторное оборудование, входы и выходы устройства, соединенные определенным образом.

Недостатком данных устройств является:

- невозможность одним и тем же устройством осуществить синхронизацию различных передач информации с асинхронным объединением цифровых потоков первого - четвертого уровней;

- значительные аппаратные затраты, т.к. при распределении позиций синхрокомбинации на большой длине цикла (несколько тысяч бит) необходим регистр сдвига с такой же разрядностью.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации [4], содержащее оперативное запоминающее устройство, устройство настройки и диагностики, устройство хранения критериев входа в синхронизм и устройство хранения критериев выхода из синхронизма, дешифратор синхрокомбинации, фазирующее устройство, генераторное оборудование.

Недостатком данного устройства является:

- невозможность синхронизации цифровых передач с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

Технической задачей изобретения является расширение функциональных возможностей за счет обеспечения одним устройством цикловой синхронизации передач информации с асинхронным объединением цифровых потоков первого - четвертого уровней с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

Указанная задача решается тем, что в устройство для цикловой синхронизации, содержащее первое оперативное запоминающее устройство, устройство настройки и диагностики, дешифратор синхрокомбинации, фазирующее устройство, генераторное оборудование, причем тактовый вход устройства для цикловой синхронизации соединен с соответствующими входами дешифратора синхрокомбинации и генераторного оборудования, адресные выходы которого соединены с соответствующими входами первого оперативного запоминающего устройства и являются адресными выходами устройства для цикловой синхронизации, выход чтения, выход записи и первый выход выбора устройства настройки и диагностики соединены с соответствующими входами первого оперативного запоминающего устройства, вход/выход конца сверхцикла которого соединен с соответствующим входом генераторного оборудования, с соответствующим входом/выходом устройства настройки и диагностики и является выходом конца сверхцикла устройства для цикловой синхронизации, вход/выход конца синхрокомбинации первого оперативного запоминающего устройства соединен с соответствующими входами дешифратора синхрокомбинации, фазирующего устройства и входом/выходом устройства настройки и диагностики, входы/выходы позиции синхрокомбинации и значения синхрокомбинации первого оперативного запоминающего устройства соединены с соответствующими входами/выходами устройства настройки и диагностики и соответствующими входами дешифратора синхрокомбинации, выход отклика которого соединен с соответствующим входом фазирующего устройства, выход нулевого состояния которого соединен с соответствующим входом генераторного оборудования, входы тактов настройки и установки в ноль которого соединены с соответствующими выходами устройства настройки и диагностики, информационные входы/выходы, входы выбора режима, нового адреса, установки в ноль, записи, чтения, выбора настраиваемого оперативного запоминающего устройства, выбора настройки оперативных запоминающих устройств или регистра устройства настройки и диагностики являются соответствующими входами устройства для цикловой синхронизации, выход наличия синхронизации фазирующего устройства является соответствующим выходом устройства для цикловой синхронизации, вход выбора режима генераторного оборудования соединен с соответствующим входом устройства для цикловой синхронизации, согласно изобретению введены от второго до К-го оперативные запоминающие устройства, перестроитель сигналов, счетчик и дешифратор, причем адресные входы введенных оперативных запоминающих устройств соединены с соответствующими выходами генераторного оборудования, выходы позиций синхрокомбинации и выходы значений синхрокомбинации для соответствующих позиций введенных оперативных запоминающих устройств соединены с соответствующими входами/выходами устройства настройки и диагностики и с соответствующими входами дешифратора синхрокомбинации, информационные входы которого и информационные выходы устройства для цикловой синхронизации соединены с соответствующими выходами перестроителя сигналов, тактовый вход которого и тактовый вход счетчика соединены с соответствующим входом устройства для цикловой синхронизации, информационные входы перестроителя сигналов соединены с соответствующими входами устройства для цикловой синхронизации, выходы устройства настройки и диагностики, определяющие количество информационных входов устройства для цикловой синхронизации, соединены с соответствующими входами дешифратора, входы разрядов которого соединены с соответствующими выходами разрядов счетчика, вход конца перестроения которого и аналогичный вход генераторного оборудования соединены с соответствующим выходом дешифратора, управляющие выходы которого соединены с соответствующими входами перестроителя сигналов, выход нулевого состояния фазирующего устройства соединен с соответствующим входом счетчика, вход конца синхрокомбинации которого соединен с соответствующим выходом первого оперативного запоминающего устройства, входы чтения и входы записи введенных оперативных запоминающих устройств соединены с соответствующими выходами устройства настройки и диагностики, выходы выбора которого соединены с входами выбора введенных соответствующих оперативных запоминающих устройств.

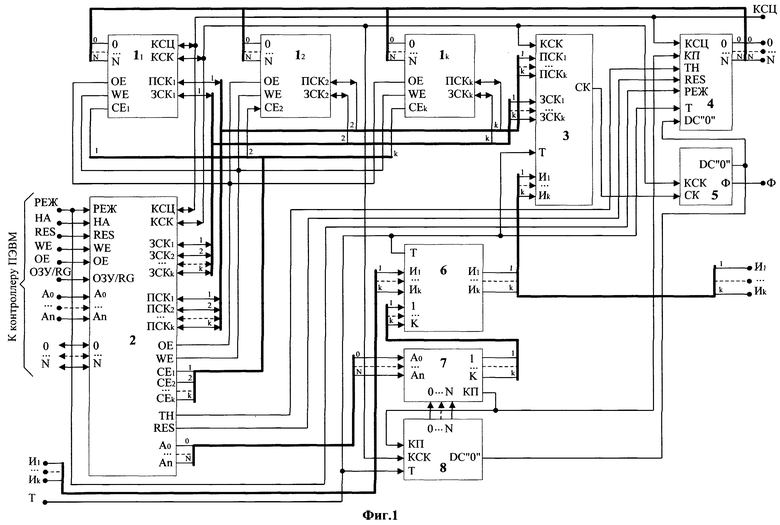

Перестроитель сигналов содержит с первого по К-1 триггеры, где К равно количеству информационных входов, и К групп вентилей, при этом каждая группа вентилей содержит К вентилей, причем информационные входы от второго до К-го перестроителя сигналов соединены с информационными входами соответственно триггеров с первого по (К-1)-й, первый информационный вход перестроителя сигналов соединен с входами от первого до К-го вентилей первой группы вентилей, второй информационный вход перестроителя сигналов соединен с входами от второго до К-го вентилей второй группы вентилей, третий информационный вход перестроителя сигналов соединен с входами от третьего до К-го вентилей третьей группы вентилей, (К-1)-й информационный вход перестроителя сигналов соединен с входами (К-1)-го и К-го вентилей (К-1)-й группы вентилей, К-й информационный вход перестроителя сигналов соединен с входом К-го вентиля К-й группы вентилей, информационные входы между третьим и (К-1)-м входами перестроителя сигналов соединены с входами вентилей групп, расположенных между третьей и (К-1)-й группами вентилей, в соответствии с порядком соединений, описанном выше, выход первого триггера соединен с входом первого вентиля второй группы вентилей, выход второго триггера соединен с входами первого и второго вентилей третьей группы вентилей, выход (К-2)-го триггера соединен с входами от первого до (К-2)-го вентилей (К-1)-й группы вентилей, выход (К-1)-го триггера соединен с входами от первого до (К-1)-го вентилей К-й группы вентилей, информационные выходы триггеров, расположенных между вторым и (К-2)-м триггерами, соединены с входами вентилей групп, расположенных между третьей и (К-1)-й группами вентилей, в соответствии с порядком соединений, описанном выше, управляющий вход 1 перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей соответствует порядковому номеру группы вентилей, управляющий вход 2 перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей от первой до (К-1)-й определяется порядковым номером группы вентилей, увеличенным на число 1, а в К-й группе вентилей - порядковым номером группы вентилей, уменьшенным на число К-1, управляющий вход 3 перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей от первой до (К-2)-й определяется порядковым номером группы вентилей, увеличенным на число 2, а в К-й и в (К-1)-й группах вентилей - порядковым номером группы вентилей, уменьшенным на число К-2, управляющий вход К-1 перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в первой и второй группах вентилей определяется порядковым номером группы вентилей, увеличенным на число К-2, а в группах вентилей от третьей до К-й - порядковым номером группы вентилей, уменьшенным на число 2, управляющий вход К перестроителя сигналов соединен с управляющим входом К-го вентиля первой группы вентилей и с управляющими входами вентилей от второй до К-й группы вентилей, в которых порядковый номер вентилей определяется порядковым номером группы вентилей, уменьшенным на число 1, управляющие входы, расположенные между третьим и (К-1)-м управляющими входами перестроителя сигналов, соединены с управляющими входами вентилей в соответствии с порядком соединения, описанном выше, одноименные выходы вентилей от первой до К-й группы вентилей соединены между собой и с соответствующими информационными выходами перестроителя сигналов, тактовый вход перестроителя сигналов соединен с тактовыми входами от первого до (К-1)-го триггеров.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: 12,..., 1k оперативных запоминающих устройств, перестроителя сигналов, счетчика и дешифратора.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежной областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для цикловой синхронизации с указанными связями придает ему новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют расширить его функциональные возможности за счет обеспечения одним устройством цикловой синхронизации широкого класса передач информации с асинхронным объединением цифровых потоков первого - четвертого уровней с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

Таким образом, изобретение соответствует критерию "изобретательский уровень", так как оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи информации с асинхронным объединением цифровых потоков.

Таким образом, изобретение соответствует критерию "промышленная применимость".

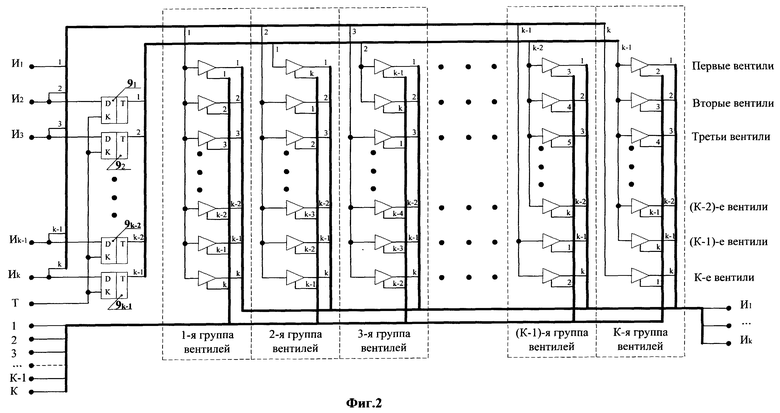

На фиг.1 представлена структурная схема предлагаемого устройства для цикловой синхронизации, на фиг.2 - принципиальная электрическая схема перестроителя сигналов.

Устройство для цикловой синхронизации (фиг.1) содержит оперативные запоминающие устройства 11,..., 1k, устройство настройки и диагностики 2, дешифратор синхрокомбинации 3, генераторное оборудование 4, фазирующее устройство 5, перестроитель сигналов 6, дешифратор 7 и счетчик 8, причем тактовый Т вход устройства для цикловой синхронизации соединен с соответствующими входами дешифратора синхрокомбинации 3 и генераторного оборудования 4, адресные 0,..., N выходы которого соединены с соответствующими входами оперативного запоминающего устройства 11 и являются адресными 0,..., N выходами устройства для цикловой синхронизации, выход чтения ОЕ, выход записи WE и первый выход выбора CE1 устройства настройки и диагностики 2 соединены с соответствующими входами первого оперативного запоминающего устройства 11, вход/выход конца сверхцикла КСЦ которого соединен с соответствующим входом генераторного оборудования 5, с соответствующим входом/выходом устройства настройки и диагностики 2 и является выходом конца сверхцикла КСЦ устройства для цикловой синхронизации, вход/выход конца синхрокомбинации КСК первого оперативного запоминающего устройства 11 соединен с соответствующими входами дешифратора синхрокомбинации 3, фазирующего устройства 5 и входом/выходом устройства настройки и диагностики 2, входы/выходы позиции синхрокомбинации ПСК1 и значения синхрокомбинации ЗCК1 первого оперативного запоминающего устройства 11 соединены с соответствующими входами/выходами устройства настройки и диагностики 2 и соответствующими входами дешифратора синхрокомбинации 3, выход отклика СК которого соединен с соответствующим входом фазирующего устройства 5, выход нулевого состояния ДС"0" которого соединен с соответствующим входом генераторного оборудования 4, входы тактов настройки ТН и установки в ноль RES которого соединены с соответствующими выходами устройства настройки и диагностики 2, информационные 0,..., N входы/выходы, входы выбора режима РЕЖ, нового адреса НА, установки в ноль RES, записи WE, чтения ОЕ, выбора настраиваемого оперативного запоминающего устройства А0,..., Аn, выбора настройки оперативных запоминающих устройств или регистра ОЗУ/RG устройства настройки и диагностики являются соответствующими входами устройства для цикловой синхронизации, выход наличия синхронизации Ф фазирующего устройства 5 является соответствующим выходом устройства для цикловой синхронизации, вход выбора режима РЕЖ генераторного оборудования 4 соединен с соответствующим входом устройства для цикловой синхронизации, адресные 0,..., N входы оперативных запоминающих устройств 12,..., 1k соединены с соответствующими выходами генераторного оборудования 4, ПСК2,...,ПСКk выходы позиций синхрокомбинации и ЗCK2,..., ЗCKk выходы значений синхрокомбинации для соответствующих позиций оперативных запоминающих устройств 12,..., 1k соединены с соответствующими входами/выходами устройства настройки и диагностики 2 и с соответствующими входами дешифратора синхрокомбинации 3, информационные И1,..., Иk входы которого и информационные И1,..., Иk выходы устройства для цикловой синхронизации соединены с соответствующими выходами перестроителя сигналов 6, тактовый Т вход которого и тактовый Т вход счетчика 8 соединены с соответствующим входом устройства для цикловой синхронизации, информационные И1,..., Иk входы перестроителя сигналов 6 соединены с соответствующими входами устройства для цикловой синхронизации, выходы А0,..., An устройства настройки и диагностики, определяющие количество информационных И1,..., Иk входов устройства для цикловой синхронизации, соединены с соответствующими входами дешифратора 7, входы разрядов 0,...,N которого соединены с соответствующими выходами разрядов счетчика 8, КП вход конца перестроения которого и аналогичный вход генераторного оборудования соединены с соответствующим выходом дешифратора 7, управляющие 1,..., К выходы которого соединены с соответствующими входами перестроителя сигналов 6, выход нулевого состояния ДС"0" фазирующего устройства 5 соединен с соответствующим входом счетчика 8, КСК вход конца синхрокомбинации которого соединен с соответствующим выходом оперативного запоминающего устройства 11, входы чтения ОЕ и входы записи WE оперативных запоминающих устройств 12,..., 1k соединены с соответствующими выходами устройства настройки и диагностики 2, выходы выбора CE2,...,CEk которого соединены соответственно с входами выбора CE2,...,CEk оперативных запоминающих устройств 12,..., 1k.

Перестроитель сигналов (фиг.2) содержит триггеры 91,..., 9k-1, где к равно количеству информационных входов, и К групп вентилей, при этом каждая группа вентилей содержит К вентилей, причем информационные И2,..., Иk входы перестроителя сигналов 6 соединены с соответствующими информационными входами триггеров 91,..., 9k-1, информационный H1 вход перестроителя сигналов 6 соединен с входами от первого до К-го вентилей первой группы вентилей, информационный И1 вход перестроителя сигналов 6 соединен с входами от второго до К-го вентилей второй группы вентилей, информационный Иk-1 вход перестроителя сигналов 6 соединен с входами от третьего до К-го вентилей третьей группы вентилей, информационный И2 вход перестроителя сигналов 6 соединен с входами (K-1)-го и К-го вентилей (К-1)-й группы вентилей, информационный Иk вход перестроителя сигналов 6 соединен с входом К-го вентиля К-й группы вентилей, информационные входы между информационными И3 и Иk-1 входами перестроителя сигналов 6 соединены с входами вентилей групп, расположенных между третьей и (К-1)-й группами вентилей, в соответствии с порядком соединений, описанном выше, выход триггера 91 соединен с входом первого вентиля второй группы вентилей, выход триггера 92 соединен с входами первого и второго вентилей третьей группы вентилей, выход триггера 9k-2 соединен с входами от первого до (К-2)-го вентилей (К-1)-й группы вентилей, выход триггера 9k-1 соединен с входами от первого до (K-1)-го вентилей К-й группы вентилей, информационные выходы триггеров, расположенных между триггерами 92 и 9k-2 соединены с входами вентилей групп, расположенных между третьей и (К-1)-й группами вентилей, в соответствии с порядком соединений, описанном выше, управляющий 1 вход перестроителя сигналов 6 соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей соответствует порядковому номеру группы вентилей, управляющий 2 вход перестроителя сигналов 6 соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей от первой до (К-1)-й определяется порядковым номером группы вентилей, увеличенным на число 1, а в К-й группе вентилей - порядковым номером группы вентилей, уменьшенным на число К-1, управляющий 3 вход перестроителя сигналов 6 соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей от первой до (К-2)-й определяется порядковым номером группы вентилей, увеличенным на число 2, а в К-й и в (К-1)-й группах вентилей - порядковым номером группы вентилей, уменьшенным на число К-2, управляющий К-1 вход перестроителя сигналов 6 соединен с управляющими входами вентилей, порядковый номер которых в первой и второй группах вентилей определяется порядковым номером группы вентилей, увеличенным на число К-2, а в группах вентилей от третьей до К-й - порядковым номером группы вентилей, уменьшенным на число 2, управляющий К вход перестроителя сигналов 6 соединен с управляющим входом К-го вентиля первой группы вентилей и с управляющими входами вентилей от второй до К-й группы вентилей, в которых порядковый номер вентилей определяется порядковым номером группы вентилей, уменьшенным на число 1, управляющие входы, расположенные между управляющими 3 и К-1 входами перестроителя сигналов 6, соединены с управляющими входами вентилей в соответствии с порядком соединения, описанном выше, одноименные выходы вентилей от первой до К-й группы вентилей соединены между собой и с соответствующими информационными И1,..., иk выходами перестроителя сигналов 6, тактовый Т вход перестроителя сигналов 6 соединен с тактовыми входами триггеров 91,..., 9k-1.

Устройство для цикловой синхронизации (фиг.1) работает следующим образом. Устройство для цикловой синхронизации (ЦС) имеет два режима работы. Первый - режим настройки и диагностики, второй - режим работы.

В первом режиме на входы устройства настройки и диагностики 2 (УНД) поступают сигналы с контроллера, работающего совместно с персональной электронно-вычислительной машиной (ПЭВМ). Режим настройки и диагностики разрешается сигналом Лог."0", который поступает на вход выбора режима (вход РЕЖ) УНД 2. Сигналом Лог."1", поступающим на вход выбора настройки оперативных запоминающих устройств или регистра (вход ОЗУ/RG) УНД 2, разрешается настройка оперативных запоминающих устройств (ОЗУ). Выбор настраиваемого ОЗУ осуществляется сигналами выбора настраиваемого ОЗУ, поступающими в двоичном коде на А0,..., Аn входы УНД 2. При настройки первого ОЗУ (ОЗУ11) на его вход выбора (вход CE1) с соответствующего выхода УНД 2 поступает сигнал Лог."0", разрешая работу ОЗУ11. При записи информации в ОЗУ11 с выхода чтения (выход ОЕ) УНД 2 на соответствующий вход ОЗУ11 поступает сигнал Лог."1". На вход установки в ноль (вход RES) УНД 2 поступает сигнал Лог."1". С выхода установки в ноль (выход RES) УНД 2 сигнал Лог."1" поступает на соответствующий вход генераторного оборудования 4 (ГО), устанавливая его в нулевое состояние. Адресные 0,..., N выходы ГО 4 соединены с соответствующими адресными входами ОЗУ11,..., ОЗУ1k. Далее по сигналу записи, поступающему с выхода записи (выход WE) УНД 2 на соответствующий вход ОЗУ11, в последнем по нулевому адресу в разрядах позиции конца сверхцикла (вход/выход КСЦ), позиции конца синхрокомбинации (вход/выход КСК), позиции синхрокомбинации (вход/выход ПСК1), позиции значения синхрокомбинации (вход/выход ЗCК1) осуществляется запись данных, поступающих с соответствующих входов/выходов УНД 2. После этого на вход нового адреса (вход НА) УНД 2 поступает сигнал, который, поступая с выхода тактов настройки (выход ТН) УНД 2 на соответствующий вход ГО 4, осуществляет смену адресов ОЗУ11.

Далее запись данных по новому адресу осуществляется так же, как было описано выше.

Для проверки правильности настройки озу11 сигналом установки в ноль, поступившим с выхода RES УНД 2 на соответствующий вход ГО 4, последнее устанавливается в нулевое состояние. После чего сигналом Лог."1″, поступившим на вход записи (вход WE) УНД 2 и далее с выхода WE УНД 2 на соответствующий вход ОЗУ11 последнее переводится в режим чтения. Затем сигналом Лог."0", поступившим на вход чтения (вход ОЕ) УНД 2 и далее с выхода ОЕ УНД 2 на соответствующий вход ОЗУ11, осуществляется считывание информации из ОЗУ11 по его нулевому адресу. При этом сигналы с входов/выходов КСЦ, КСК, ПСК1, ЗCК1 последнего поступают на соответствующие входы/выходы УНД 2 и далее в контроллер ПЭВМ для их сравнения с исходными. Затем по сигналу нового адреса осуществляется смена адреса ОЗУ11 и считывание данных по новому адресу так же, как было описано выше.

Аналогично осуществляется настройка и проверяется правильность настройки следующих ОЗУ. Номер настраиваемого ОЗУ задается сигналами, поступающими на А0,..., Аn входы УНД 2. Количество ОЗУ в устройстве для цикловой синхронизации определяется количеством его входов/выходов.

После настройки и проверки правильности настройки всех ОЗУ осуществляется настройка регистра запоминания, расположенного в УНД 2. Настройка регистра запоминания разрешается сигналом Лог."0", поступающим на ОЗУ/RG вход УНД 2. При этом порядок настройки и проверки ее правильности такой же, как для ОЗУ. С выходов регистра запоминания сигналы, задающие количество информационных входов устройства для цикловой синхронизации в двоичном коде поступают на А0,..., Аn выходы УНД 2 и далее на соответствующие входы дешифратора 7.

Перевод устройства для ЦС в режим работы осуществляется сигналом Лог."1", поступающим на вход РЕЖ УНД 2. При этом сигналами выбора, поступающими с CE1,...,CEk выходов УНД 2, разрешается работа ОЗУ1,..., ОЗУk, а сигналами Лог."1" и Лог."0", поступающими соответственно с выходов записи WE и чтения ОЕ УНД 2 на соответствующие входы ОЗУ, последние переводятся в режим считывания данных.

В режиме настройки на вход тактов настройки (вход ТН) счетчика позиций ГО 4 поступают тактовые импульсы с соответствующего выхода УНД 2, а в режиме работы на тактовый вход (вход Т) счетчика позиций ГО 4 поступают тактовые импульсы с тактового входа (вход Т) устройства для ЦС.

Работа устройства для ЦС осуществляется следующим образом. На адресные входы (входы 0,..., N) ОЗУ11,..., ОЗУ1k поступают сигналы с соответствующих выходов ГО 4, при этом на выходах конца сверхцикла, конца синхрокомбинации, позиции синхрокомбинации, значения синхрокомбинации соответствующих ОЗУ формируются соответствующие сигналы. По сигналу с выхода конца сверхцикла (выход КСЦ) озу11 в ГО 4 осуществляется синхронная установка в нулевое состояние счетчика тактовым импульсом, следующим за появлением данного сигнала. Длина сверхцикла определяется как наименьшее общее кратное между длиной цикла передачи и количеством информационных входов. Сигнал конца синхрокомбинации с выхода конца синхрокомбинации (выход КСК) ОЗУ11, сигналы позиций и значений синхрокомбинации с соответствующих выходов ОЗУ11,..., ОЗУ1k, информационные сигналы с соответствующих информационных выходов (выходы И1,..., Иk) перестроителя сигналов 6, а также тактовые сигналы с тактового входа (вход Т) устройства для ЦС поступают на соответствующие входы дешифратора синхрокомбинации 3 (ДС). ДС 3 осуществляет сравнение информационных сигналов с заданными в ОЗУ11,..., ОЗУ1k на позициях синхрокомбинации, также заданных в ОЗУ11,..., ОЗУ1k и формирование результата сравнения на его выходе отклика (выход СК). В случае положительного отклика на СК выходе ДС 3 формируется сигнал Лог."1", а в случае отрицательного отклика - сигнал Лог."0". Сигнал отклика с СК выхода ДС 3 и сигнал конца синхрокомбинации с КСК выхода ОЗУ11 поступают на соответствующие входы фазирующего устройства. До появления первого положительного отклика с СК выхода ДС 3 фазирующее устройство 5 (ФУ) находится в нулевом состоянии и сигналом Лог."1", поступающим с выхода нулевого состояния (выход ДС"0") ФУ 5 на соответствующие входы ГО 4 и счетчика 8, разрешается работа удалителя тактов ГО 4 и счетчика 8. Счетчик 8 увеличивает свое состояние на единицу при поступлении на его КСК вход сигнала с соответствующего выхода ОЗУ11 и затем тактового сигнала на его Т вход с соответствующего входа устройства для ЦС. Сигналы с выходов разрядов счетчика 8 (выходы 0,..., N) в двоичном коде поступают на соответствующие входы дешифратора 7, сигналы с управляющих выходов которого (выходы 1,..., К) поступают на соответствующие входы ПС 6. Наличие сигнала на одном из управляющих 1,..., К входов ПС 6 определяет порядок перестроения информационных сигналов, поступающих с информационных И1,..., Иk входов устройства для ЦС на соответствующие входы ПС. Количество управляющих входов ПС 6 определяется числом информационных входов устройства для ЦС. При отсутствии положительного отклика на СК выходе ДС 3 после появления сигнала на управляющем К выходе дешифратора 7 сигналом с выхода конца перестроения (выход КП) дешифратора 7 счетчик 8 устанавливается в нулевое состояние, а в ГО 4 осуществляется удаление (пропуск) одного такта. Сигнал конца перестроения формируется при совпадении сигналов, определяющих количество информационных входов устройства для ЦС, поступающих с выходов (выходы А0,..., An) УНД 2 на соответствующие входы дешифратора 7, и сигналов, поступающих с выходов (выходы 0,..., N) разрядов счетчика на соответствующие входы дешифратора 7. В описанном режиме устройство для ЦС работает до тех пор, пока не будет найдена первая синхрокомбинация. При этом на СК выходе ДС 3 появляется сигнал положительного отклика, который поступает на соответствующий вход ФУ 5. После поступления на соответствующие входы ФУ 5 сигнала положительного отклика и сигнала конца синхрокомбинации реверсивный счетчик последнего устанавливается в режим положительного счета и увеличивает свое состояние на единицу. При этом сигналом Лог."0", сформированном на ДС"0" выходе ФУ 5 запрещается работа удалителя такта ГО 4 и счетчика 8. Тем самым запрещается дальнейшее перестроение информационных сигналов, поступивших на входы ПС 6. Таким образом, при наличии сигнала положительного отклика на СК входе ФУ 5 реверсивный счетчик последнего увеличивает свое состояние на единицу, а при отсутствии - уменьшает на единицу. Когда разность количества сигналов положительного и отрицательного откликов достигает заданного в ФУ 5 значения, устройство для ЦС переходит в режим синхронизма, о чем свидетельствует сигнал Лог."1" на выходе (выход Ф) наличия синхронизации ФУ 5. В этом режиме устройство для ЦС находится до тех пор, пока разность количества сигналов отрицательного и положительного откликов достигает заданного в ФУ 5 значения. При этом ФУ 5 устанавливается в нулевое состояние, и устройство для ЦС переходит в режим поиска синхронизма, как было описано выше.

В режиме синхронизма с помощью перестроителя сигналов 6 и удалителя тактов ГО 4 информационные сигналы перестроены и поступают на выход в порядке, когда первый бит сверхцикла передачи расположен на первом информационном выходе.

Перестроитель сигналов (фиг.2) работает следующим образом. При наличии сигнала на первом управляющем входе (вход 1) перестроителя сигналов 6 (ПС) открываются вентили, номера которых в группах соответствуют номеру группы. При этом текущие значения информационных сигналов с информационных И1,..., Иk входов ПС 6 поступают через открытые вентили соответственно на информационные И1,..., Hk выходы ПС 6.

При наличии сигнала на втором управляющем входе (вход 2) ПС 6 открываются вентили, порядковый номер которых в группах вентилей от первой до (К-1)-й определяется порядковым номером группы вентилей, увеличенным на единицу, а в К-й группе вентилей - порядковым номером группы вентилей, уменьшенным на число К-1. При этом запомненный в триггере 9k-1 сигнал, поступивший с информационного Иk входа ПС 6 на D-вход триггера, с выхода последнего поступает на информационный И1 выход ПС 6, а текущие значения информационных сигналов с информационных И1,..., Иk-1 входов ПС 6 поступают соответственно на информационные И2,..., Иk выходы ПС 6.

При наличии сигнала на третьем управляющем входе (вход 3) ПС 6 открываются вентили, порядковый номер которых в группах вентилей от первой до (К-2)-й определяется порядковым номером группы вентилей, увеличенным на число 2, а в К-й и (К-1)-й группах вентилей - порядковым номером группы вентилей, уменьшенным на число К-2. При этом запомненные в триггерах 9k-2 и 9k-1 сигналы, поступившие с информационных Иk-1 и Иk входов ПС 6 на Д входы соответственно триггеров 9k-2 и 9k-1, с выходов последних поступают на информационные И1 и И2 выходы ПС 6, а текущие значения информационных сигналов с информационных И1,..., Иk-2 входов ПС 6 поступают соответственно на информационные И3,..., Иk выходы ПС 6.

При наличии сигнала на управляющем К-1 входе ПС 6 открываются вентили, порядковый номер которых в первой и второй группах вентилей определяется порядковым номером группы вентилей, увеличенным на число К-2, а в группах вентилей от третьей до К-й - порядковым номером группы вентилей, уменьшенным на число 2. При этом запомненные в триггерах 92,..., 9k-1 сигналы, поступившие с информационных И1,..., Иk входов ПС 6 на D-входы соответственно триггеров 92,..., 9k-1, с выходов последних поступают соответственно на информационные И1,..., Иk-2 выходы ПС 6, а текущие значения информационных сигналов с информационных И1 и И2 входов ПС 6 поступают соответственно на информационные Иk-1 и Иk выходы ПС 6.

При наличии сигнала на управляющем К входе ПС 6 открывается К-й вентиль первой группы вентилей, а в группах вентилей от второй до К-й открываются вентили, порядковый номер которых равен порядковому номеру группы вентилей, уменьшенному на единицу. При этом запомненные в триггерах 91,..., 9k-1 сигналы, поступившие с информационных И2,..., Иk входов ПС 6 на D-входы соответственно триггеров 91,..., 9k-1, с выходов последних поступают соответственно на информационные И1,..., Иk-1 выходы ПС 6, а текущее значение информационного сигнала с информационного И1 входа ПС 6 поступает соответственно на информационный Иk выход ПС 6.

При наличии сигнала на одном из управляющих от четвертого до (К-2)-го входов перестроитель сигналов работает в соответствии с порядком работы, описанном ранее.

Для технической реализации устройства для цикловой синхронизации использованы статические оперативные запоминающие устройства (ОЗУ) импортного производства типа KM68257CJ-15 фирмы SEC и программируемая пользователем логическая интегральная схема (ППЛИС) XC4020XLA фирмы XILINX.

Предлагаемое изобретение позволяет осуществить цикловую синхронизацию различных передач информации с асинхронным объединением цифровых потоков первого - четвертого уровней с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2005 |

|

RU2296431C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2003 |

|

RU2242842C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением. Технический результат – расширение функциональных возможностей за счет обеспечения передачи информации с асинхронным объединением цифровых потоков первого - четвертого уровней с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов. Устройство для цикловой синхронизации содержит оперативные запоминающие устройства, устройство настройки и диагностики, дешифратор синхрокомбинации, генераторное оборудование, фазирующее устройство, перестроитель сигналов, дешифратор, счетчик. 1 з.п.ф-лы, 2 ил.

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1992 |

|

RU2019046C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| ЛЕВИН Л.С., ПЛОТКИН М.А | |||

| Цифровые системы передачи информации | |||

| - Радио и связь, 1982, с.102 и 103, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| US 4517681 A, 14.05.1985 | |||

| US 4763324 A, 09.08.1988 | |||

| US 4727558 A, 23.02.1988. | |||

Авторы

Даты

2004-09-27—Публикация

2003-02-10—Подача