Изобретение относится к технике цифровой связи, а именно к устройствам для выделения компонентных потоков (каналов пользовательских данных) в цифровых системах передачи информации с временным уплотнением.

Известно многоканальное устройство приема дискретной информации [1], содержащее преобразователь кода, приемник синхросигнала, генераторный блок, N канальных блоков, соединенные определенным образом. В данном устройстве канальные блоки представляют собой устройство для демультиплексирования, которое выделяет компонентные потоки в системах с временным уплотнением.

Недостатком этого устройства является невозможность одним и тем же устройством осуществить демультиплексирование различных передач плезиохронной цифровой иерархии, как соответствующих рекомендациям ITU-T, так и большого количества нестандартизированных цифровых передач.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для демультиплексирования [2], содержащее устройство настройки и управления, К канальных блоков, каждый из которых состоит из оперативного запоминающего устройства, блока обработки стаффинга, выделителя компонентных позиций, формирователя тактов, информационного триггера. В этом устройстве для демультиплексирования канальные блоки представляют собой устройство, выделяющее компонентные потоки в системах с временным уплотнением.

Недостатком данного устройства является невозможность демультиплексирования нестандартизированных (не соответствующих рекомендациям ITU-T) передач, называемых радиоциклами, с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

Под радиоциклом понимается нестандартное с точки зрения стандартов ITU-T уплотнение цифровой информации для передачи в радиорелейных линиях связи. Структура радиоцикла определяется фирмой-разработчиком аппаратуры передачи данных. Обычно радиоцикл содержит синхрогруппу, служебные символы и один канал пользовательских данных (информация, передаваемая в канале, как правило, соответствует рекомендациям ITU-T).

Известным устройством возможно осуществить демультиплексирование конкретной передачи, если предварительно произвести преобразование сигнала из К-входового в одновходовой с одновременным увеличением тактовой частоты в К раз. Однако частотные и временные характеристики применяемой элементной базы, как правило, не позволяют обеспечить подобное преобразование и работоспособность устройства для демультиплексирования. С другой стороны, нестандартизированные передачи отличаются тактовой частотой, что не позволяет осуществить одним и тем же устройством подобное преобразование и, следовательно, не позволяет осуществить одним и тем же устройством для демультиплексирования демультиплексирование различных передач, называемых радиоциклами.

Технической задачей изобретения является расширение функциональных возможностей за счет обеспечения демультиплексирования одним устройством (для отдельного вида модуляции) различных нестандартизированных передач информации, называемых радиоциклами.

Указанная задача решается тем, что в известное устройство, содержащее устройство настройки и управления, оперативное запоминающее устройство, причем адресные входы и управляющие входы устройства для демультиплексирования соединены с соответствующими входами устройства настройки и управления, адресные выходы, выходы сигнала записи и сигнала чтения которого соединены с соответствующими входами оперативного запоминающего устройства, вход выбора микросхемы последнего соединен с земляной шиной, выходы сигналов позиций выделяемого канала пользовательских данных, сигналов позиций управления стаффингом, сигналов позиций стаффинга устройства настройки и управления соединены с соответствующими входами/выходами оперативного запоминающего устройства, согласно изобретению введены формирователь сигналов, перестроитель сигналов, преобразователь кода, сумматор по модулю К, устройство формирования канала данных, причем выход сигнала критерия стаффинга устройства настройки и управления соединен с соответствующим входом формирователя сигналов, информационные входы устройства для демультиплексирования соединены с соответствующими входами формирователя сигналов, входы сигналов позиций выделяемого канала пользовательских данных, сигналов позиций управления стаффингом, сигналов позиций стаффинга которого соединены с соответствующими выходами оперативного запоминающего устройства, информационные выходы формирователя сигналов соединены с соответствующими входами перестроителя сигналов, выходы формирователя сигналов, задающие пользовательский код сигналов для соответствующих его информационных выходов, соединены с соответствующими входами преобразователя кода и перестроителя сигналов, выходы преобразователя кода, преобразующие пользовательский код на его входах в двоичный, соединены с соответствующими входами сумматора по модулю К, выходы результата суммирования которого соединены с соответствующими его входами и входами устройства формирования канала данных, информационные выходы и выход разрешения перестроителя сигналов соединены с соответствующими входами устройства формирования канала данных, вход переноса которого соединен с соответствующим выходом сумматора по модулю К, информационные выходы и тактовый выход устройства формирования канала данных соединены с соответствующими выходами устройства для демультиплексирования, тактовый вход которого является тактовым входом для формирователя сигналов, перестроителя сигналов, преобразователя кода, сумматора по модулю К и устройства формирования канала данных.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: формирователя сигналов, перестроителя сигналов, преобразователя кода, сумматора по модулю К, и устройства формирования канала данных.

Таким образом, изобретение соответствует критерию "Новизна".

Анализ известных технических решений в исследуемой и смежной областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для демультиплексирования с указанными связями придает ему новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют расширить функциональные возможности, а именно обеспечить демультиплексирование одним устройством (для отдельного вида модуляции) различных нестандартизированных передач информации, называемых радиоциклами.

Таким образом, изобретение соответствует критерию "Изобретательский уровень", так как оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи с временным уплотнением цифровых потоков.

Таким образом, изобретение соответствует критерию "Промышленная применимость".

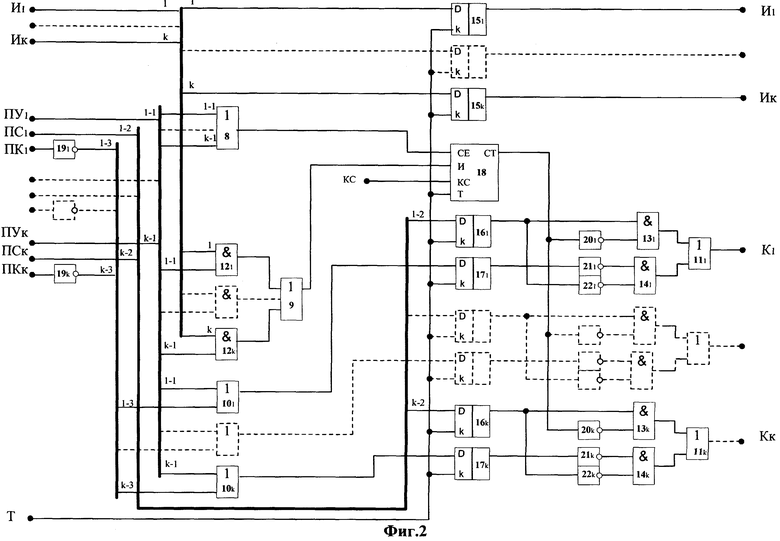

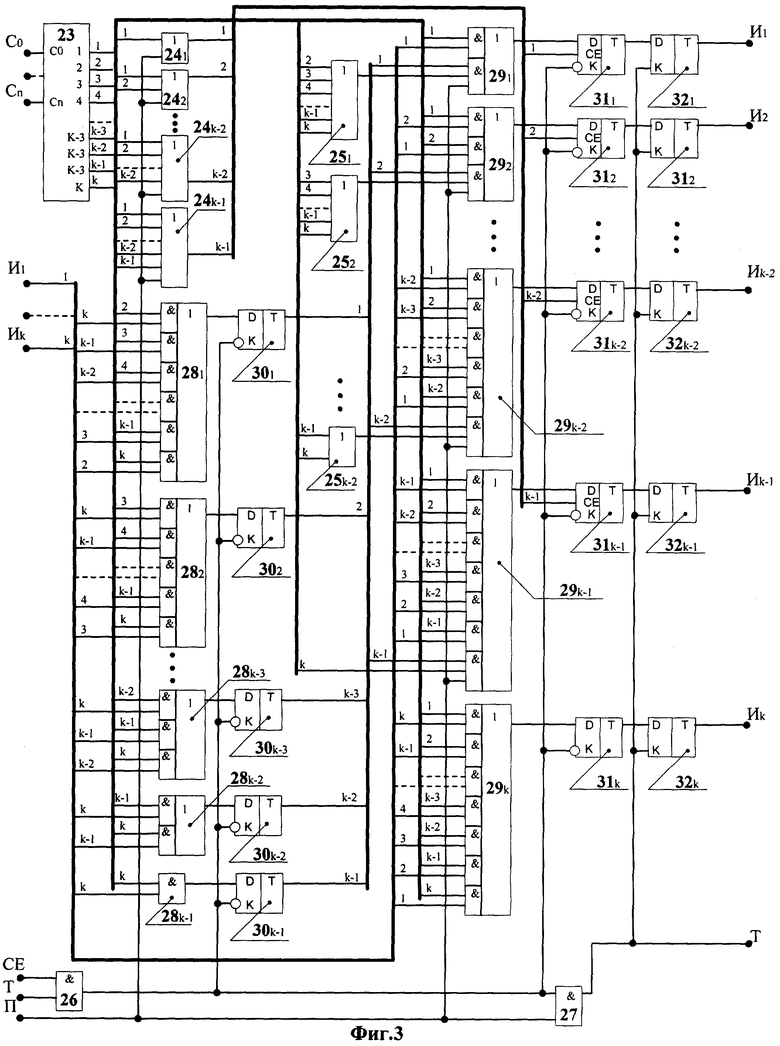

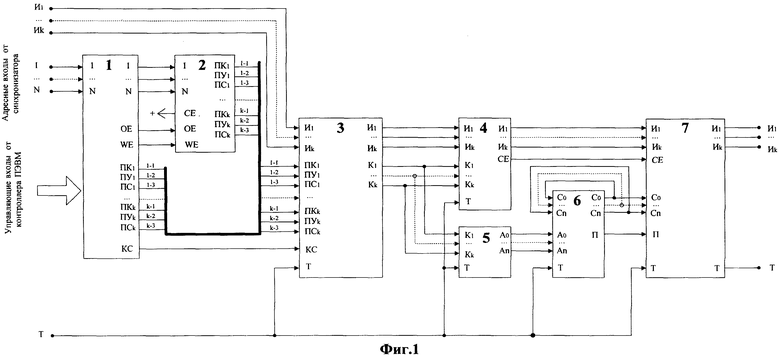

На фиг.1 представлена структурная электрическая схема предлагаемого устройства для демультиплексирования, на фиг.2 - принципиальная электрическая схема формирователя сигналов, на фиг.3 - структурная электрическая схема устройства формирования канала данных.

Устройство для демультиплексирования (фиг.1) содержит устройство настройки и управления 1, оперативное запоминающее устройство 2, формирователь сигналов 3, перестроитель сигналов 4, преобразователь кода 5, сумматор по модулю К 6, устройство формирования канала данных 7, причем адресные входы 1,...,N и управляющие входы устройства для демультиплексирования соединены с соответствующими входами устройства настройки и управления 1, адресные выходы 1,...,N, выходы сигнала записи WE и сигнала чтения ОБ которого соединены с соответствующими входами оперативного запоминающего устройства 2, вход выбора микросхемы СЕ последнего соединен с земляной шиной, выходы сигналов позиций выделяемого канала пользовательских данных ПК1,...,ПКk, сигналов позиций управления стаффингом ПУ1,...,ПУk, сигналов позиций стаффинга ПC1,...,ПCk устройства настройки и управления 1 соединены с соответствующими входами/выходами оперативного запоминающего устройства 2, выход сигнала критерия стаффинга КС устройства настройки и управления 1 соединен с соответствующим входом формирователя сигналов 3, информационные входы И1,...,Иk устройства для демультиплексирования соединены с соответствующими входами формирователя сигналов 3, входы сигналов позиций выделяемого канала пользовательских данных ПK1,...,ПKk, сигналов позиций управления стаффингом ПУ1,...,ПУk, сигналов позиций стаффинга ПC1,...,ПCk которого соединены с соответствующими выходами оперативного запоминающего устройства 2, информационные выходы И1,...,Иk формирователя сигналов 3 соединены с соответствующими входами перестроителя сигналов 4, выходы К1,...,Kk формирователя сигналов 3, задающие пользовательский код сигналов для соответствующих его информационных выходов И1,...,Иk, соединены с соответствующими входами преобразователя кода 5 и перестроителя сигналов 4, выходы A0,...,An преобразователя кода 5, преобразующие пользовательский код на его K1,...,Kk входах в двоичный, соединены с соответствующими входами сумматора по модулю К 6, выходы результата суммирования С0,...,Сn которого соединены с соответствующими его входами и входами устройства формирования канала данных 7, информационные выходы И1,...,Иk и выход разрешения СЕ перестроителя сигналов 4 соединены с соответствующими входами устройства формирования канала данных 7, вход переноса П которого соединен с соответствующим выходом сумматора по модулю К 6, информационные выходы И1,...,Иk и тактовый выход Т устройства формирования канала данных 7 соединены с соответствующими выходами устройства для демультиплексирования, тактовый вход Т которого является тактовым входом для формирователя сигналов 3, перестроителя сигналов 4, преобразователя кода 5, сумматора по модулю К 6 и устройства формирования канала данных 7.

Формирователь сигналов 3 (фиг.2) содержит элементы ИЛИ 8, 9, 101,...,10k, 111,...,11k, элементы И 121,...,12k, 131,...,13k, 141,...,14k, триггеры 151,...,15k, 161,..., 16k, 171,...,17k, блок обработки стаффинга 18, инверторы 191,...,19k, 201,...20k, 211,...21k, 221,...,22k, причем информационные входы И1,...Иk формирователя сигналов 3 соединены с первыми входами соответствующих элементов И 121,...,12k и с входами D соответствующих триггеров 151,...,15k, выходы которых соединены с соответствующими информационными выходами И1,...Иk формирователя сигналов 3, входы сигналов позиций управления стаффингом ПУ1,...,ПУk, формирователя сигналов 3 соединены с входами элемента ИЛИ 8, со вторыми входами соответствующих элементов И 121,...,12k и с первыми входами соответствующих элементов ИЛИ 101,..., 10k, выходы которых соединены с входами D соответствующих триггеров 171,...,17k, входы сигналов позиции стаффинга ПC1,...,ПCk формирователя сигналов 3 соединены с входами D соответствующих триггеров 161,...,16k, выходы которых соединены с первыми входами соответствующих элементов И 131,...,13k и с входами соответствующих инверторов 221,...,22k, входы сигналов позиций выделяемого канала пользовательских данных ПK1,...,ПKk формирователя сигналов 3 соединены с входами соответствующих инверторов 191,...,19k, выходы которых соединены со вторыми входами соответствующих элементов ИЛИ 101,..., 10k, выходы элементов И 121,...,12k соединены с входами элемента ИЛИ 9, выход которого соединен с информационным входом И блока обработки стаффинга 18, вход разрешения СЕ которого соединен с выходом элемента ИЛИ 8, выход сигнала наличия стаффинга СТ блока обработки стаффинга 18 соединен с входами инверторов 201,...20k, выходы которых соединены со вторыми входами соответствующих элементов И 131,...,13k, выходы триггеров 171,...,17k соединены с входами соответствующих инверторов 211,...,21k, выходы которых соединены с первыми входами соответствующих элементов И 141,...,14k, вторые входы которых соединены с выходами соответствующих инверторов 221,..., 22k, выходы элементов И 131,...,13k соединены с первыми входами соответственно элементов ИЛИ 111,..., 11k, вторые входы которых соединены с выходами соответственно элементов И 141,...,14k, выходы элементов ИЛИ 111,..., 11k соединены соответственно с выходами K1,...,Kk формирователя сигналов 3, тактовый вход Т которого соединен с тактовыми входами триггеров 151,...,15k, 161,..., 16k, 171,...,17k и тактовым входом Т блока обработки стаффинга 18, вход сигнала критерия стаффинга КС формирователя сигналов 3 соединен с соответствующим входом блока обработки стаффинга 18.

Устройство формирования канала данных (фиг.3) содержит дешифратор 23, элементы ИЛИ 241,...,24k-1, 251,...,25k-2, элементы И 26, 27, коммутаторы 281,...,28k-1, 291,...,29k, триггеры 301,...,30k-1, 311,...,31k, 321,...,32k, при этом коммутаторы 281,...28k-2 содержат элементы И и элемент ИЛИ, первые входы элементов И коммутаторов 281,...,28k-2 являются управляющими входами и соединены с соответствующими выходами дешифратора 23, вторые входы элементов И коммутаторов 281,...,28k-2 соединены с соответствующими информационными И2,...,Иk входами устройства формирования канала данных 7, в каждом из коммутаторов 281,...,28k-2 выходы элементов И соединены с входами элементов ИЛИ, коммутатор 28k-1 представляет собой элемент И, первый управляющий вход которого соединен с входом К дешифратора 23, а второй вход - с информационным входом Иk устройства формирования канала данных 7, коммутаторы 291,...,29k-1 содержат двухвходовые элементы И, один трехвходовой элемент И и элемент ИЛИ, коммутатор 29k содержит двухвходовые элементы И и элемент ИЛИ, первые управляющие входы двухвходовых элементов И коммутаторов 291,...,29k соединены с соответствующими выходами дешифратора 23, вторые входы элементов И коммутаторов 291,...,29k соединены с соответствующими информационными И1,...,Иk входами устройства формирования канала данных 7, первые входы трехвходовых элементов И коммутаторов 291,...,29k-1 соединены с выходами соответственно триггеров 301,...,30k-1, вторые входы трехвходовых элементов И коммутаторов 291,...,29k-2 соединены с выходами соответственно элементов ИЛИ 251,...,25k-2, второй вход трехвходового элемента И коммутатора 29k-1 соединен с К выходом дешифратора 23, выходы элементов И в каждом коммутаторе 291,...,29k соединены с входами элемента ИЛИ, входы результата суммирования С0,...,Сn устройства формирования канала данных 7 соединены с соответствующими входами дешифратора 23, первые входы элементов ИЛИ 241,...,24k-1 соединены с выходом 1 дешифратора 23, вторые входы элементов ИЛИ 242,...,24k-1 соединены с выходом 2 дешифратора 23, вход К-1 элемента ИЛИ 24k-1 соединен с выходом К-1 дешифратора 23, остальные входы соответствующих элементов ИЛИ 24 соединены с выходами дешифратора 23 по аналогии с порядком соединения, приведенным выше, первый вход элемента ИЛИ 251 соединен с выходом 2 дешифратора 23, второй вход элемента ИЛИ 251 и первый вход элемента ИЛИ 252 соединены с выходом 3 дешифратора 23, третий вход элемента ИЛИ 251 и второй вход элемента ИЛИ 252 соединены с выходом 4 дешифратора 23, входы К-1 и К элементов ИЛИ 251,...,25k-2 соединены соответственно с выходами К-1 и К дешифратора 23, остальные входы соответствующих элементов ИЛИ 25 соединены с выходами дешифратора 23 по аналогии с порядком соединения, приведенным выше, выходы коммутаторов 281,...,28k-1 соединены соответственно с информационными входами триггеров 301,...,30k-1, выходы коммутаторов 291,...,29k соединены соответственно с информационными входами Д триггеров 311,...,31k, выходы которых соединены соответственно с информационными входами Д триггеров 321,...,32k, выходы которых являются соответственно информационными выходами И1,...,Иk устройства формирования канала данных 7, выходы элементов ИЛИ 241,...,24k-1 соединены соответственно с разрешающими входами СЕ триггеров 311,...,31k-1, вход разрешения СЕ и тактовый вход Т устройства формирования канала данных 7 соединены соответственно с первым и вторым входами элемента И 26, выход которого соединен с тактовыми входами К триггеров 301,...,30k-1, с тактовыми входами К триггеров 311,...,31k и с первым входом элемента И 27, выход которого соединен с тактовыми входами К триггеров 321,..., 32k и является также тактовым выходом Т устройства формирования канала данных 7, вход переноса П устройства формирования канала данных 7 соединен с соответствующими входами элементов ИЛИ 241,...,24k-1, а также с соответствующими входами коммутаторов 291,...,29k-1 и со вторым входом элемента И 27.

Устройство для демультиплексирования работает следующим образом.

Перед началом работы осуществляется его настройка на параметры определенной цифровой передачи. При этом в оперативное запоминающее устройство 2 для каждого из К информационных входов устройства для демультиплексирования, по определенным адресам, записываются единичные биты, соответствующие наличию позиций выделяемого канала пользовательских данных (разряды ПК1,...,ПКk), позиций управления стаффингом (разряды ПУ1,...,ПУk), позиций бит стаффинга (разряды ПС1,...,ПCk). Так как в процессе работы устройства не возникает необходимости выбора оперативного запоминающего устройства 2, на вход выбора микросхемы СЕ последнего поступает сигнал нулевой полярности. Порядок настройки оперативного запоминающего устройства 2 следующий. Сигналом чтения ОЕ единичного уровня, поступающим с выхода устройства настройки и управления 1 на вход чтения ОЕ оперативного запоминающего устройства 2, последнее устанавливается в режим записи. Адресные сигналы, поступающие от контроллера персональной электронной вычислительной машины (ПЭВМ) на управляющие входы устройства настройки и управления 1, коммутируются последним на адресные входы 1,...,N оперативного запоминающего устройства 2. Сигналы параметров настройки, поступающие от контроллера ПЭВМ на входы устройства настройки и управления 1, с его выходов ПK1, ПУ1, ПС1,..., ПKk, ПУk, ПCk, поступают на соответствующие входы оперативного запоминающего устройства 2. Далее, по сигналу записи WE, поступающему от контроллера ПЭВМ через устройство настройки и управления 1 на вход записи WE оперативного запоминающего устройства 2, в нем осуществляется запоминание задаваемых параметров. Затем изменяются адресные сигналы, и параметры настройки вновь записываются в оперативное запоминающее устройство 2. Сигналом с выхода КС устройства настройки и управления 1 задаются параметры работы блока обработки стаффинга формирователя сигналов 3 (КС - выход сигнала критерия стаффинга). Сигналом "Лог.0" на выходе КС устройства настройки и управления 1 задается критерий обработки стаффинга, равный "2 из 3", а сигналом " Лог 1" - "3 из 5".

После настройки устройство для демультиплексирования переходит в режим работы.

В рабочем режиме устройство для демультиплексирования осуществляет разуплотнение нестандартного цифрового потока (радиоцикла) с учетом наличия стаффингования.

Демультиплексирование входного цифрового потока происходит следующим образом. С устройства для цикловой синхронизации на информационные И1,...,Иk, адресные 1,...,N и тактовый Т входы устройства для демультиплексирования поступают соответственно информационные, адресные и тактовый сигналы. Затем информационные И1,...,Иk и тактовый Т сигналы с входов устройства для демультиплексирования поступают на соответствующие входы формирователя сигналов 3. Формирователь сигналов 3 осуществляет распознавание бит канала пользовательских данных и служебных бит на каждом его И1,...,Иk информационных входах, то есть для каждого из его информационных выходов H1,...,Hk, на выходах K1,...,Kk формирователя сигналов 3 формируется сигнал пользовательского кода, единичный уровень которого означает наличие канала пользовательских данных на соответствующем информационном входе, а нулевой - наличие служебного бита, синхробита или незначащего бита.

Перестроитель сигнала 4 осуществляет перестроение информационных сигналов, поступающих на его информационные входы И1,...,Иk в зависимости от значения сигналов на его K1,...,Kk входах, поступающих с соответствующих выходов формирователя сигналов 3. Например, при наличии сигнала единичного уровня на входах К2, K5, K8 информационные сигналы, поступившие на входы И2, И5, И8 перестроителя сигналов 4, соответственно скоммутируются на информационные выходы И1, И2, И3 перестроителя сигналов 4.

Преобразователь кода 5 осуществляет преобразование количества сигналов, равных "Лог.1", на его K1,...,Kk входах в двоичный код, значение которого с выходов А0,...,An поступает на соответствующие входы сумматора по модулю К 6, где К - количество информационных входов устройства для демультиплексирования.

Сумматор по модулю К 6 осуществляет суммирование в двоичном коде предыдущего его значения с поступившим на входы А0,...,Аn. Результат суммирования в двоичном коде с выходов С0,...,Сn сумматора по модулю К 6 поступает на соответствующие входы устройства формирования канала данных 7. В случае если результат суммирования сумматора по модулю К 6 равен или превышает значение К, то на выходе переноса П сумматора по модулю К 6 формируется сигнал единичного уровня, а на его выходах С0,...,Сn формируются сигналы в двоичном коде, соответствующие разности между числом суммирования и числом К.

Устройство формирования канала данных 7 осуществляет коммутацию информационных сигналов в соответствии с порядком и временем их поступления и формирование информационных сигналов на его информационных выходах И1,...,Иk и тактового сигнала на его тактовом выходе Т при поступлении на его вход П сигнала переноса. Информационные И1,...,Иk и тактовый Т сигналы с выходов устройства формирования канала данных 7 поступают на соответствующие выходы устройства для демультиплексирования.

Формирователь сигналов 3 (фиг.2) работает следующим образом. На его информационные входы И1,...,Иk и тактовый вход Т поступают информационные И1,...,Иk и тактовый Т сигналы соответственно с информационных входов И1,...,Иk и тактового входа Т устройства для демультиплексирования. Для каждого информационного входа на входы сигналов позиций выделяемого канала пользовательских данных ПК1,...,ПКk, сигналов позиций управления стаффингом ПУ1,...,ПУk, сигналов позиций стаффинга ПC1,...,ПCk поступают сигналы с соответствующих выходов оперативного запоминающего устройства 2. На вход сигнала критерия стаффинга КС поступает сигнал с соответствующего выхода устройства настройки и управления 1. Триггеры 151,...,15k, 161,...,16k, 171,...,17k предназначены для согласования по времени сигналов, поступающих на их информационные входы.

Наличие позиций управления стаффингом, позиций стаффинга и позиций выделяемого канала пользовательских данных определяется сигналами "Лог.1", поступающими на соответствующие входы формирователя сигналов 3. При наличии на одном из входов сигнала позиции управления стаффингом, поступающего на первый вход соответствующего элемента ИЛИ 101,...,10k, или при отсутствии на соответствующем входе сигнала позиции выделяемого канала пользовательских данных, поступающего через соответствующий инвертор 191,...,19k на второй вход соответствующего элемента ИЛИ 101,...,10k, на выходе последнего формируется сигнал "Лог.1", который поступает на информационный вход соответствующего триггера 171,...,17k, и по положительному фронту тактового сигнала запоминается в нем. При отсутствии на одном из входов сигнала позиции управления стаффингом и при наличии на соответствующем входе сигнала позиции выделяемого канала пользовательских данных в соответствующем триггере 171,...,17k запоминается сигнал "Лог.0". Каждый из сигналов позиций управления стаффингом, через элемент ИЛИ 8 поступая на разрешающий вход СЕ блока обработки стаффинга 18, разрешает работу последнего.

Соответствующий сигнал позиции управления стаффингом, поступая на второй вход соответствующего элемента И121,...,12k, разрешает работу последнего и тем самым разрешает прохождение информационного сигнала с соответствующего информационного входа И1,...,Иk формирователя сигналов 3 через элемент ИЛИ 9 на информационный вход И блока обработки стаффинга 18, после чего по сигналу, поступившему на тактовый вход Т этого блока, в последнем записывается информация, поступившая на его информационный вход И. В случае наличия стаффинга на позициях управления стаффингом передаются информационные сигналы, равные "Лог.1". При отсутствии стаффинга на позициях управления стаффингом передаются информационные сигналы, равные "Лог.0". В зависимости от цифровой передачи количество позиций управления стаффингом в цикле может быть 3 или 5. В связи с тем что информация на позициях управления стаффингом может быть искажена помехами, решение о наличии стаффинга принимается по большинству сигналов "Лог.1" на этих позициях, т.е. "2 из 3" или "3 из 5". Критерии "2 из 3" или "3 из 5" задаются соответственно сигналом "Лог.0" или "Лог.1", поступающим с входа сигнала критерия стаффинга КС формирователя сигналов 3 на соответствующий вход блока обработки стаффинга 18. Сигнал "Лог.1" на выходе наличия стаффинга СТ блока обработки стаффинга 18 указывает на наличие незначащего бита на позиции стаффинга. Сигнал "Лог.0" на выходе наличия стаффинга СТ блока обработки стаффинга 18 указывает на наличие бита канала пользовательских данных на позиции стаффинга. Сигнал позиции стаффинга поступает на информационный вход Д соответствующего триггера 161,...,16k и сигналом, поступившим на его тактовый вход К, запоминается в последнем. При наличии сигнала позиции стаффинга, поступившего с выхода соответствующего триггера 161,...,16k на первый вход соответствующего элемента H 131,...,13k, и сигнала отсутствия стаффинга, поступившего с выхода СТ блока обработки стаффинга через соответствующий инвертор 201,...,20k на второй вход соответствующего элемента И 131,...,13k, на выходе последнего формируется сигнал "Лог.1", который через соответствующий элемент ИЛИ 111,...,11k поступает на соответствующий выход K1,...,Kk формирователя сигналов 3. При сигнале отсутствия позиции стаффинга, поступающего с выхода соответствующего триггера 161,...,16k через соответствующий инвертор 221,...,22k на второй вход соответствующего элемента И 141,...,14k, и при сигнале наличия позиции канала пользовательских данных и отсутствия позиции управления стаффингом, поступающего с выхода соответствующего триггера 171,...,17k через инверторы 211,...,21k на первый вход элемента И 141,...,14k, на выходе последнего формируется сигнал "Лог.1", который через соответствующий элемент ИЛИ 111,...,11k поступает на соответствующий выход K1,...,Kk формирователя сигналов 3. Наличие сигнала "Лог.1" на выходах K1,...,Kk указывает на наличие бит канала пользовательских данных на соответствующих информационных выходах И1,...,Иk формирователя сигналов 3.

Устройство формирования канала данных 7 работает следующим образом. Сигналы результата суммирования в двоичном коде с входов С0,...,Сn устройства формирования канала данных 7 поступают на соответствующие входы дешифратора 23. При наличии сигнала на выходе 1 дешифратора 23 сигналами с выходов элементов ИЛИ 241,...,24k-1, поступающими соответственно на разрешающие входы СЕ триггеров 311,...,31k-1, разрешается работа последних. Триггер 31k постоянно разрешен. Также сигналом с выхода 1 дешифратора 23 разрешается прохождение информационных сигналов с информационных входов И1,...,Иk устройства формирования канала данных 7 соответственно через коммутаторы 291,...,29k на информационные входы Д соответствующих триггеров 311,...,31k.

При наличии сигнала на выходе 2 дешифратора 23 сигналами с выходов элементов ИЛИ 242,...,24k-1, поступающими соответственно на разрешающие входы СЕ триггеров 312,...,31k-1, разрешается работа последних. Также сигналом с выхода 2 дешифратора 23 разрешается прохождение информационных сигналов с информационных входов И1,...Иk-1 устройства формирования канала данных 7 соответственно через коммутаторы 292,...,29k на информационные входы Д соответствующих триггеров 312,...,31k и разрешается прохождение информационного сигнала с информационного входа Иk устройства формирования канала данных 7 через коммутатор 281 на информационный вход Д триггера 301.

При наличии сигнала на выходе К-2 дешифратора 23 сигналами с выходов элементов ИЛИ 24k-2 и ИЛИ 24k-1, поступающими соответственно на разрешающие входы СЕ соответствующих триггеров 31k-2, 31k-1, разрешается работа последних. Также сигналом с выхода К-2 дешифратора 23 разрешается прохождение информационных сигналов с информационных входов И1,...,И3 устройства формирования канала данных 7 соответственно через коммутаторы 29k-2,...,29k на информационные входы Д соответствующих триггеров 31k-2,...,31k, а также разрешается прохождение информационных сигналов с информационных входов И4,...,Иk устройства формирования канала данных 7 соответственно через коммутаторы 281,...,28k-3 на информационные входы Д соответствующих триггеров 301,...,30k-3.

При наличии сигнала на выходе К-1 дешифратора 23 сигналом с выхода элемента ИЛИ 24k-1, поступающим на разрешающий вход СЕ триггера 31k-1, разрешается работа последнего. Также сигналом с выхода К-1 дешифратора 23 разрешается прохождение информационных сигналов с информационных входов И1,...И2 устройства формирования канала данных 7 соответственно через коммутаторы 29k-1,...,29k на информационные входы Д соответствующих триггеров 31k-1,...,31k, а также разрешается прохождение информационных сигналов с информационных входов И3,...,Иk устройства формирования канала данных 7 соответственно через коммутаторы 281,...,28k-2 на информационные входы Д соответствующих триггеров 301,...,30k-2.

При наличии сигнала на выходе К дешифратора 23 разрешается прохождение информационного сигнала с информационного входа И1 устройства формирования канала данных 7 через коммутатор 29k на информационный вход Д триггера 31k, а также разрешается прохождение информационных сигналов с информационных входов И2,...,Иk устройства формирования канала данных 7 соответственно через коммутаторы 281,...,28k-1 на информационные входы Д соответствующих триггеров 301,...,30k-1.

При наличии сигнала на одном из выходов между выходом 2 и выходом К-2 дешифратора 23 порядок работы устройства формирования канала данных 7 соответствует порядку работы, описанному выше.

Сигналы, поступившие на информационные входы триггеров 301,...,30k-1 и 311,...,31k, записываются в последние по заднему фронту тактового сигнала, поступившего с тактового входа Т устройства формирования канала данных 7 через элемент И 26 на тактовые входы К указанных выше триггеров. Элемент И 26 открыт сигналом, поступившим на его первый вход с разрешающего входа СЕ устройства формирования канала данных 7, в случае, если на информационные входы И1,...,Иk поступает хотя бы один сигнал канала пользовательских данных. Если на все информационные входы устройства формирования канала данных 7 поступают служебные сигналы, то сигналом, поступающим с разрешающего входа СЕ устройства формирования канала данных 7 на первый вход элемента И 26, запрещается работа последнего. Тем самым запрещается поступление тактового сигнала на тактовые входы триггеров 301,...,30k-1 и 311,...,31k и, следовательно, не осуществляется запись информационных сигналов в указанные триггеры.

Работа устройства формирования канала данных 7, описанная выше, приведена для случая отсутствия на его входе переноса П сигнала переноса.

При наличии сигнала переноса устройство формирования канала данных 7 работает следующим образом.

При поступлении сигнала переноса на входы элементов ИЛИ 241,...,24k-1 выходными сигналами последних разрешается работа соответствующих триггеров 311,...,31k-1.

При наличии сигнала на выходе 1 дешифратора 23 разрешается прохождение информационных сигналов с входов И1,...,Иk устройства формирования канала данных 7 соответственно через коммутаторы 291,...,29k на информационные входы соответствующих триггеров 311,...,31k, как было описано выше при отсутствии сигнала переноса.

При наличии сигнала на выходе 2 дешифратора 23, поступающего через элемент ИЛИ 251 на второй вход трехвходового элемента И и сигнала переноса, поступающего на третий вход трехвходового элемента И коммутатора 291, разрешается прохождение ранее записанного в триггер 301 сигнала на информационный вход Д триггера 311. На информационные входы Д остальных триггеров 31 сигналы поступают таким же образом, как было описано выше при отсутствии сигнала переноса.

При наличии сигнала на выходе 3 дешифратора 23, поступающего через элементы ИЛИ 251, 252 на вторые входы трехвходовых элементов И, и сигнала переноса, поступающего на третьи входы трехвходовых элементов И коммутаторов 291, 292, разрешается прохождение ранее записанных в триггерах 301 и 302 сигналов на информационные входы Д соответственно триггеров 311 и 312.

На информационные входы Д остальных триггеров 31 сигналы поступают таким же образом, как было описано выше при отсутствии сигнала переноса.

При наличии сигнала на одном из следующих выходов дешифратора 23 порядок работы устройства формирования канала данных 7 соответствует порядку работы, описанному выше.

Сигнал переноса открывает по второму входу элемент И 27, и передним фронтом тактового сигнала, поступившем с выхода элемента И 26 через открытый элемент И 27 на тактовые входы К триггеров 321,...,32k, в последних записываются сигналы, запомненные соответственно в триггерах 311,...,31k. После чего задним фронтом тактового сигнала в триггеры 311,...,31k записываются сигналы, поступившие на их информационные Д входы, как было описано ранее. Сигналы с выходов триггеров 321,...,32k поступают соответственно на информационные выходы H1,...,Hk устройства формирования канала данных 7, а сигнал с выхода элемента И 27 поступает на тактовый выход Т этого устройства.

Для технической реализации устройства для демультиплексирования использованы статические оперативные запоминающие устройства (ОЗУ) импортного производства типа KM68257CJ-15 - фирмы SEC и программируемая пользователем логическая интегральная схема (ППЛИС) XC4020XLA - фирмы XILINX.

Предлагаемое изобретение позволяет осуществить демультиплексирование различных нестандартизированных цифровых передач, называемых радиоциклами, с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

Источники информации

1. Авт. св. СССР № 1292200, кл. H 04 L 25/40.

2. Патент РФ № 2173029, кл. H 04 L 25/40.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2005 |

|

RU2296431C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2000 |

|

RU2173029C1 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

Изобретение относится к технике цифровой связи. Технический результат заключается в расширении функциональных возможностей за счет обеспечения демультиплексирования одним устройством различных нестандартизованных передач информации. Сущность изобретения заключается в том, что в известное устройство демультиплексирования, содержащее устройство настройки и управления и оперативное запоминающее устройство, дополнительно введены формирователь сигналов, перестроитель сигналов, преобразователь кода, сумматор по модулю К и устройство формирования канала данных. 3 ил.

Устройство для демультиплексирования, содержащее устройство настройки и управления, оперативное запоминающее устройство, причем адресные входы и управляющие входы устройства для демультиплексирования соединены с соответствующими входами устройства настройки и управления, адресные выходы, выходы сигнала записи и сигнала чтения которого соединены с соответствующими входами оперативного запоминающего устройства, вход выбора микросхем последнего соединен с земляной шиной, выходы сигналов позиций выделяемого канала пользовательских данных, сигналов позиций управления стаффингом, сигналов позиций стаффинга устройства настройки и управления соединены с соответствующими входами/выходами оперативного запоминающего устройства, отличающееся тем, что введены формирователь сигналов, перестроитель сигналов, преобразователь кода, сумматор по модулю К, устройство формирования канала данных, причем выход сигнала критерия стаффинга устройства настройки и управления соединен с соответствующим входом формирователя сигналов, информационные входы устройства для демультиплексирования соединены с соответствующими входами формирователя сигналов, входы сигналов позиций выделяемого канала пользовательских данных, сигналов позиций управления стаффингом, сигналов позиций стаффинга которого соединены с соответствующими выходами оперативного запоминающего устройства, информационные выходы формирователя сигналов соединены с соответствующими входами перестроителя сигналов, выходы формирователя сигналов, задающие пользовательский код сигналов для соответствующих его информационных выходов, соединены с соответствующими входами преобразователя кода и перестроителя сигналов, выходы преобразователя кода, преобразующие пользовательский код на его входах в двоичных, соединены с соответствующими входами сумматора по модулю К, выходы результата суммирования которого соединены с соответствующими его входами и входами устройства формирования канала данных, информационные выходы и выход разрешения перестроителя сигналов соединены с соответствующими входами устройства формирования канала данных, вход переноса которого соединен с соответствующим выходом сумматора по модулю К, информационные выходы и тактовый выход устройства формирования канала данных соединены с соответствующими выходами устройства для демультиплексирования, тактовый вход которого является тактовым входом для формирователя сигналов, перестроителя сигналов, преобразователя код, сумматора по модулю К и устройства формирования канала данных.

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2000 |

|

RU2173029C1 |

| Многоканальное устройство для приема дискретной информации | 1985 |

|

SU1292200A1 |

| DE 3046636 А1, 22.07.1982 | |||

| DE 3046658 A1, 15.07.1982 | |||

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

Авторы

Даты

2004-12-20—Публикация

2003-04-21—Подача