(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| Интерполятор третьей степени | 1988 |

|

SU1566369A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

Изобретение относится к вычисли тельной технике, в частности к устройствам для реализации функций, и может быть использовано для воспроизведения нелинейных зависимостей одной переменной. Цель изобретения - повышение точности интерполятора. С этой целью в интерполятор, содержащий накапливающий сумматор 8, умножитель 7, блок 6 памяти, коммутатор 4, преобразователь 3 в дополнительный код, счетчик 1 и регистр 2, введен блок 5 памяти. 1 ил., 1 табл.

4;

О СП

о ч

Изобретение относится к вычислительной технике, в частности к устройствам для реализации функций, и может быть использовано для воспроизведения нелинейных зависимостей одной переменной.

Цель изобретения - повышение точности интерполятора.

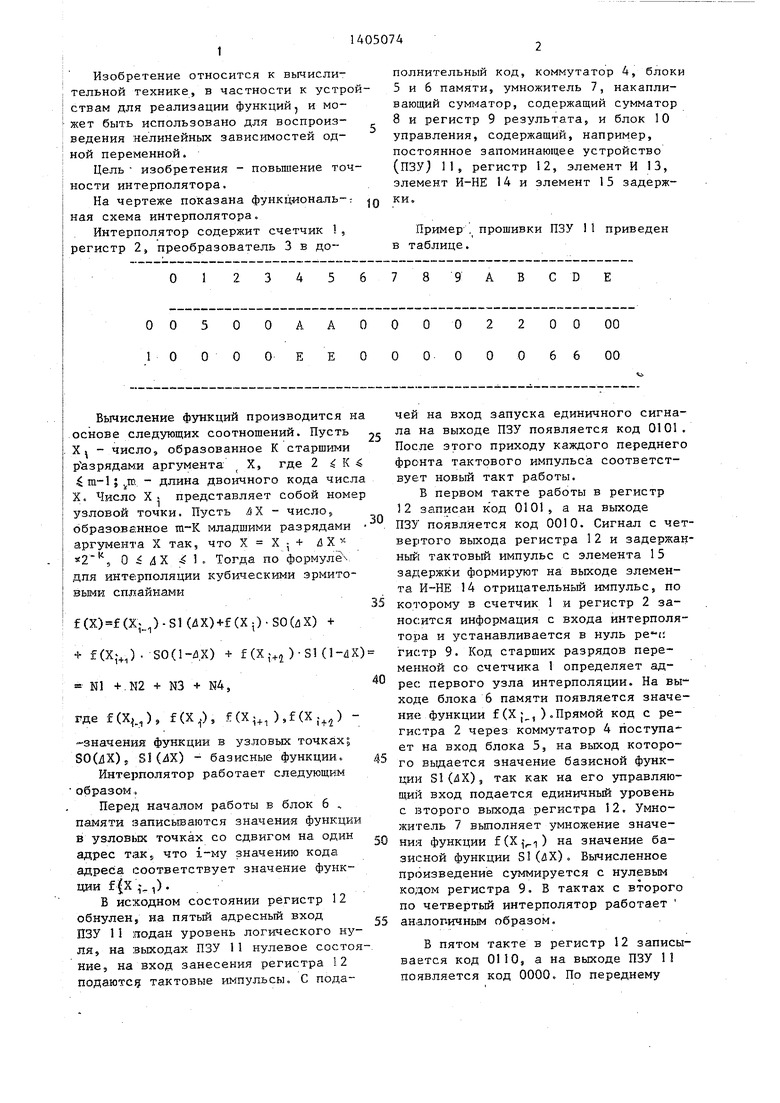

На чертеже показана функциональ-: ная схема интерполятора.

Интерполятор содержит счетчик , регистр 2, преобразователь 3 в доО

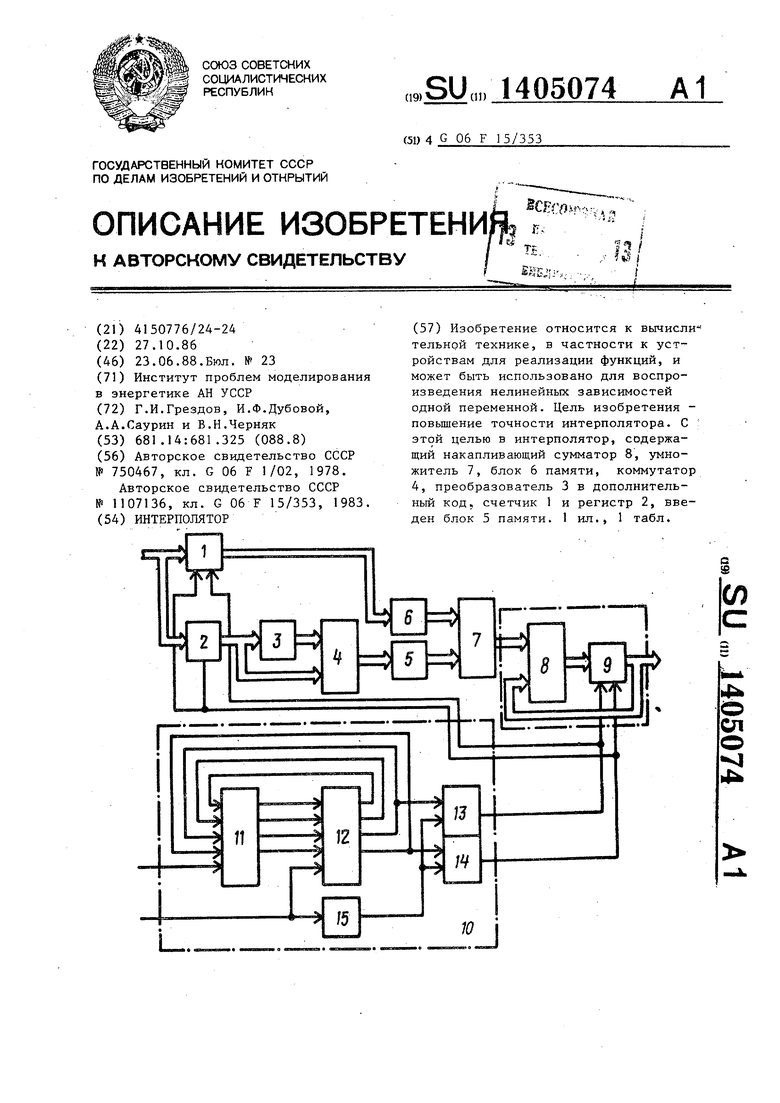

00500АА0000220000 10 00 ОЕ Е О О 00 О О 66 00

Вычисление функций производится на основе следующих соотношений. Пусть 25 - число, образованное К старшими р азрядами аргумента X, где 2 К 4 т-1; го, - длина двоичного кода числа . Число X. представляет собой номер узловой точки. Пусть .йХ - число,, образовенное т-К младшими разрядами аргумента X так, что X X + йХ 2, О 4Х . Тогда по формулё-v, пя интерполяции кубическими эрмитоыми сплайнами

35

(Х)(Х.)-8(йХ)+(Х;)-30(лХ) +

f(X,4,) -SOd-AX) f(X.+j)-S(l-dX) N1 +.N2 + N3 + N4,.

где f(X.,), f(X.), f(X.J,f(X;,) -значения функции в узловых точках; SO(4X)s SI(4Х) - базисные функции. 45

Интерполятор работает следующим образом,.

Перед началом работы в блок 6 , памяти записьгоаются значения функции в узловых точках со сдвигом на один CQ адрес так, что i-му значению кода адреса соответствует значение функции f |Х ;,).

Б исходном состоянии регистр 12 обнулен, на пятьш адресный вход ПЗУ 11 нодан уровень логического нуля, на выходах ПЗУ 11 нулевое состоя-. ние, на вход занесения регистра 12 подаются тактовые импульсы. С подаполнительный код, коммутатор 4, блок 5 и 6 памяти, умножитель 7, накапливающий сум-матор, содержащий сумматор 8 и регистр 9 результата, и блок 10 управления, содержащий, например, постоянное запоминающее устройство (ПЗУ; 11, регистр 12, элемент И 13, элемент И-НЕ 14 и элемент 15 задержки.

Пример . прошивки ПЗУ 1 1 приведен в таблице.

8 9

В

С D

чей на вход запуска единичного сигнала на выходе ПЗУ появляется код 0101. После этого приходу каждого переднего фронта тактового импульса соответствует новый такт работы.

В первом такте работы в регистр 12 записан к од 0101, а на выходе ПЗУ появляется код 0010. Сигнал с четвертого выхода регистра 12 и задержан ньй тактовый импульс с элемента 15 задержки формируют на выходе элемента И-НЕ 14 отрицательный импульс, по которому в счетчик 1 и регистр 2 заносится информация с входа интерполятора и устанавливается в нуль гистр 9. Код старших разрядов переменной со счетчика 1 определяет адрес первого узла интерполяции. На выходе блока 6 памяти появляется значение функции f (X ,) .Прямой код с регистра 2 через коммутатор 4 поступа- ет на вход блока 5, на выход которого вьщается значение базисной функции 3(ЛХ)5 так как на его управляющий вход подается единичньй уровень с второго выхода регистра 12. Умножитель 7 вьтолняет умножение значения функции f(X,VT) на значение базисной функции 51(йХ). Вычисленное произведение суммируется с нулевым кодом регистра 9. В тактах с второго по четвертый интерполятор работает аналогичным образом.

В пятом такте в регистр 12 записывается код 0110, а на выходе ПЗУ 11 появляется код 0000. По переднему

фронту импульса с элемента И 13 в регистр 9 записывается значение f(X).

Следующий тактовый импульс записывает в регистр 12 код 0000, возвращая устройство в исходное состояние.

Для функций, имеющих непрерывную третью производную на каждом интерва ле интерполяции, погрешность равна .3

5 т 96 мякс

(X) - h

Формула изобретения

Интерполятор, содержащий накапли-. вающий сумматор, умножитель, первьй блок памяти, коммутатор, преобразователь в дополнительный код, счетчик и. регистр, выход которого соединен с первым информационным входом коммутатора, причем выход первого разряда регистра соединен с управляющим входом коммутатора, второй информацион- ный вход которого соединен с вьгходом преобразователя в дополнительный код, вход которого соединен с выходом

10

15

20 25

регистра, информационный вход которого является входом младших разрядов аргумента интерполятора, вход старших разрядов которого соединен с входом установки начального значения счетчи1(а, выход которого соединен с адресным входом первого блока памяти, выход умножителя соединен с информационным входом накапливающего сумматора, выход которого является выхо- ; дом интерполятора, входы занесения данных счетчика и регистра и вход сброса накапливающего сумматора соединены с входом начальной установки интерполятора, счетный вход счетчика и вход синхронизации накапливающего сумматора соединены с входом тактирования интерполятора, о т л и- чающийся тем, что, с целью гговьппения точности интерполятора, в него введен второй блок памяти, выход которого соединен с входом первого сомножителя умножителя, вход второго сомножителя Которого соединен с выходом первого блока.памяти, а выход коммутатора соединен с адресным входом второго блока памяти.

| Цифровой генератор функций | 1978 |

|

SU750467A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-23—Публикация

1986-10-27—Подача