Изобретение относится к схемному устройству для питания электронной цепи нагрузки электрическим высоким напряжением, величина которого больше величины питающего схемное устройство напряжения, при этом схемное устройство имеет соединенную электрически с цепью нагрузки схему накачки, которая на основании внутреннего коммутационного сигнала с заданной частотой накачки таким образом выдает на цепь нагрузки высокое напряжение, что получаемая цепью нагрузки электрическая мощность накачки схемы накачки зависит, в основном, от величины питающего напряжения, а также от частоты накачки коммутационного сигнала схемы накачки.

Для электрически программируемых и стираемых полупроводниковых запоминающих устройств требуются для программирования и стирания напряжения, которые в большинстве случаев превышают по величине обычное питающее напряжение. Ячейки памяти электрически программируемых и стираемых полупроводниковых запоминающих устройств выполнены обычно из двух управляемых извне электродов и расположенного между ними, не связанного с потенциалом электрода. Программирование таких ячеек памяти производят нанесением зарядов на несвязанный с потенциалом электрод посредством приложения высокого напряжения между обоими управляемыми извне электродами, которое составляет обычно +18 В, стирание производят удалением зарядов с несвязанного с потенциалом электрода посредством приложения высокого напряжения, которое имеет по сравнению с напряжением программирования противоположный знак и составляет обычно - 12 В. Важными областями применения электрически программируемых и стираемых полупроводниковых запоминающих устройств наряду с электронными устройствами обработки данных, являются, в частности, электронные карточки, как например, карточки с памятью и карточки с микропроцессором. В этих случаях питающее напряжение подводят извне от так называемого терминала во время обмена данными между электронной карточкой и терминалом. В области технологии ТТЛ с выполненными из биполярных транзисторов интегрированными полупроводниковыми элементами питающее напряжение составляет обычно 5 В±10%, в то время как в области КМОП технологии с выполненными на полевых транзисторах интегрированными полупроводниковыми элементами типичным является напряжение 3 В±10%. Поэтому для указанных областей применения электрически программируемых и стираемых полупроводниковых запоминающих устройств желательно иметь в распоряжении схему создания высокого напряжения для напряжений обеих полярностей, которая работает как от питающего напряжения около 3 В, так и от питающего напряжения около 5 В.

В основе настоящего изобретения лежит задача создать схемное устройство указанного в начале типа, которое может работать с различными питающими напряжениями для выдачи постоянной мощности накачки на цепь нагрузки.

Эта задача решается с помощью схемного устройства согласно пункту 1 формулы изобретения.

Согласно изобретению предусмотрено, что схемное устройство имеет приданную схеме накачки, снабжаемую, по меньшей мере, производным от питающего напряжения схемы накачки напряжением электронную управляющую схему, которая в зависимости от зависящего от величины питающего напряжения управляющего сигнала выдает на схему накачки коммутационный сигнал, воздействующий на частоту накачки для создания выдаваемого схемой накачки высокого напряжения так, что величина частоты накачки коммутационного сигнала изменяется обратно пропорционально величине питающего напряжения. В основе изобретения лежит идея использовать зависимость отдаваемой на цепь нагрузки мощности накачки от произведения питающего напряжения и частоты накачки таким образом, что для выдачи по возможности постоянной мощности накачки даже при различных питающих напряжениях частотой накачки управляют так, что она увеличивается при уменьшении питающего напряжения. При этом схемные затраты являются относительно небольшими, так как необходим только один управляющий сигнал, соответствующий величине питающего напряжения, для управления частотой накачки. Таким образом, частотой накачки можно управлять исключительно в зависимости от величины питающего напряжения. Другие параметры, как например, выдаваемая мощность схемы накачки или потребление мощности цепью нагрузки не оказывают существенного влияния на частоту накачки, так что не требуются другие сигналы для управления частотой накачки, которые зависят от других параметров, кроме питающего напряжения.

В предпочтительном варианте выполнения схемного устройства согласно изобретению может быть предусмотрено, что схема накачки управляется с помощью управляющего сигнала схемы управления для выдачи, по меньшей мере, приблизительно постоянной мощности накачки на цепь нагрузки, при этом выдача мощности накачки схемы накачки управляется с помощью схемы управления, в основном, пропорционально произведению величины питающего напряжения и частоты накачки. Для поддержания мощности накачки схемы накачки на постоянном уровне может быть предусмотрено управление частотой накачки с помощью величины питающего напряжения таким образом, что компенсируется влияние питающего напряжения на мощность накачки.

С учетом пропорциональной связи между мощностью накачки, с одной стороны, и произведением питающего напряжения и частоты накачки, с другой стороны, можно, кроме того, предусмотреть, что выдача мощности накачки схемы накачки управляется с помощью схемы управления в зависимости от питающего напряжения так, что частота накачки является обратно пропорциональной величине питающего напряжения. В схеме накачки с мощностью накачки Р=c•U•f, где Р - мощность накачки, с - в идеальном случае постоянный фактор, U - питающее напряжение, f - частота накачки, в идеальном случае схема управления, которая управляет частотой накачки согласно зависимости f=d/U, где d - идеальная постоянная, удерживала бы мощность накачки на постоянной величине. Таким образом, для мощности накачки получаем зависимость Р=c•d. При таком управлении частотой накачки, которая обратно пропорциональна величине питающего напряжения, можно компенсировать зависимость мощности накачки от питающего напряжения и частоты накачки. В реальных схемах постоянные c и d зависят, например, от температуры и специфических параметров элементов схемы. Эту зависимость, если это считается необходимым, можно компенсировать с помощью подходящих схемных решений.

В другом предпочтительном варианте выполнения схемного устройства согласно изобретению может быть предусмотрено, что схема управления для создания и выдачи коммутационного сигнала имеет генераторный коммутационный контур, частота колебаний которого зависит от подаваемого на вход генераторного коммутационного контура управляющего сигнала. При применении создаваемого генераторным коммутационным контуром сигнала в качестве коммутационного сигнала для схемы накачки частота накачки пропорциональна частоте генератора, за счет чего происходит управление частотой накачки в зависимости от управляющего сигнала.

Для достижения обратно пропорциональной зависимости между величиной питающего напряжения и частотой накачки может быть далее предусмотрено, что подаваемый на вход генераторного коммутационного контура управляющий сигнал непосредственно выводится из величины питающего напряжения. За счет этого происходит непосредственное управление величиной частоты накачки посредством величины питающего напряжения.

В более подробном варианте выполнения схемного устройства согласно изобретению может быть предусмотрено, что генераторный коммутационный контур содержит коммутационный контур в виде триггера Шмитта. Частотой генераторного коммутационного контура с коммутационным контуром в виде триггера Шмитта можно простым способом управлять напряжением, за счет чего схемное устройство согласно изобретению можно выполнить с сравнительно небольшими схемными затратами.

Для дальнейшей отработки выдаваемых генераторным коммутационным контуром сигналов может быть предпочтительно предусмотрено, что приданная схеме накачки схема управления имеет включенный после генераторного коммутационного контура делитель частоты, который на оба входа накачки схемы накачки подает два антисимметричных по отношению друг к другу тактовых сигнала. Для правильного функционирования схемы накачки может быть предпочтительно предусмотрено поставлять два противоположных друг другу тактовых сигнала, высокий и низкий уровни которых имеют одинаковую длину во времени; такие тактовые сигналы могут относительно простым способом обеспечиваться с помощью делителя частоты схемного устройства согласно изобретению. Делитель частоты может быть, например, выполнен из простых вентильных схем, которые могут быть выполнены с помощью известных технологий ТТЛ или КМОП.

В другом предпочтительном варианте выполнения изобретения может быть предусмотрено, что схема накачки имеет каскадную цепь, выполненную из нескольких ступеней с конденсаторами и работающими как диоды транзисторами, при этом ступени каскадной цепи так включены последовательно между выходом высокого напряжения и питающим напряжением, что работающие как диоды транзисторы включены последовательно, и соединенные с точками соединения работающих как диоды транзисторов конденсаторы соединены попеременно стороной, обращенной от работающих как диоды транзисторов, с обоими входами накачки, и что схема накачки имеет другой работающий как диод транзистор с обратной связью, расположенный между питающим напряжением и составленной из транзисторов последовательной цепи, при этом управляющий вход подключен к питающему напряжению. За счет применения работающих как диоды транзисторов с обратной связью, в частности, выполненных с помощью КМОП технологии можно обойтись небольшой поверхностью на полупроводниковой подложке. Такую схему накачки можно реализовать с помощью широко применяемых полупроводниковых технологий, например ТТЛ или КМОП, что обеспечивает возможность полной интеграции на полупроводниковой подложке.

Для обеспечения по возможности более компактной конструкции может быть предпочтительно предусмотрено, что схемное устройство выполнено интегрально с цепью нагрузки на одной полупроводниковой подложке. Генераторный коммутационный контур, делитель частоты, а также каскадную цепь можно выполнить с помощью той же полупроводниковой технологии, так что возможно выполнение монолитных составляющих частей схемы на одной полупроводниковой подложке.

В особенно предпочтительном применении схемного устройства согласно изобретению может быть предусмотрено, что электронная цепь нагрузки содержит группу подлежащих программированию или стиранию ячеек памяти энергонезависимого электрически стираемого, программируемого полупроводникового запоминающего устройства. В этом случае может быть предпочтительно предусмотрено, что величина высокого напряжения составляет предпочтительно около +18 В или -12 В, а величина питающего напряжения находится предпочтительно между +3 В-10% и +5 В+10%.

Для уменьшения схемных затрат может быть, кроме того, предусмотрено, что величина управляющего сигнала соответствует непосредственно величине питающего напряжения. В противном случае схема трансформирования между питающим напряжением и управляющим сигналом могла бы приводить к нелинейности передающей функции между управляющим сигналом и питающим напряжением, что могло бы нарушать обратно пропорциональную зависимость между частотой накачки и питающим напряжением.

Дальнейшие признаки, преимущества и целесообразности изобретения следуют из последующего описания примера выполнения изобретения с помощью чертежей, на которых изображено:

фиг.1 - схематичное построение схемного устройства согласно изобретению;

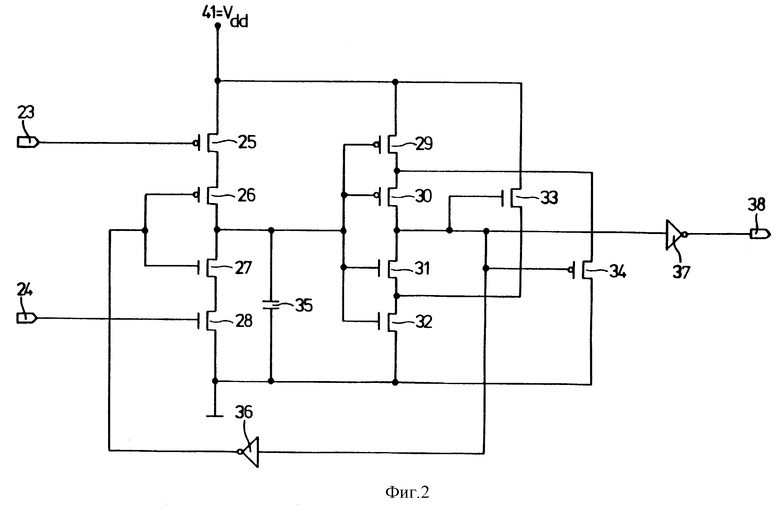

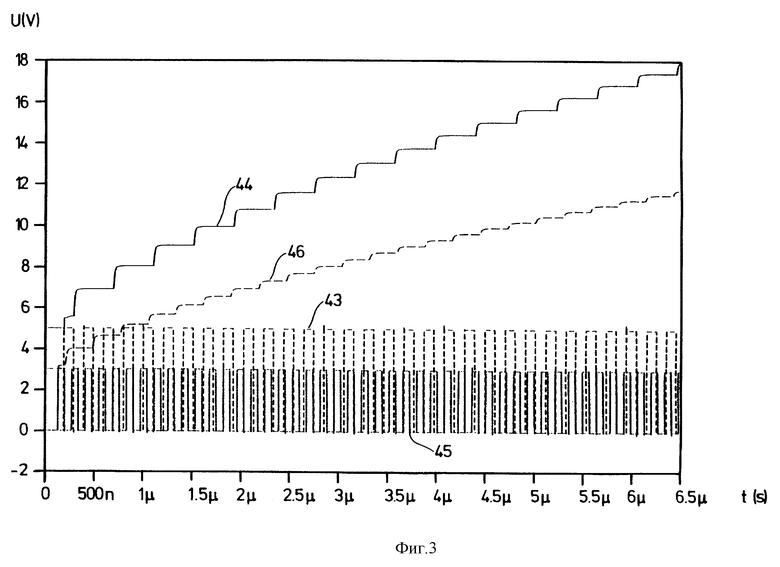

фиг. 2 - схематичное построение генераторного коммутационного контура в виде триггера Шмитта;

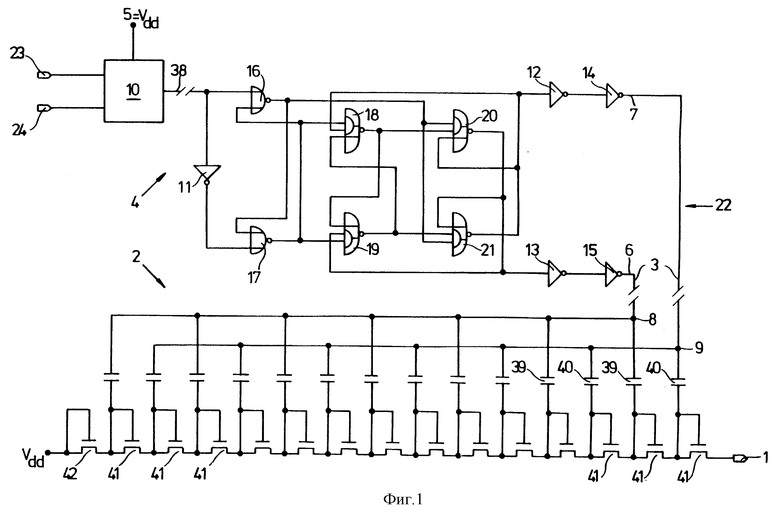

фиг. 3 - изменение во времени некоторых напряжений схемного устройства согласно изобретению.

На фиг. 1 показан пример выполнения схемного устройства согласно изобретению для питания подключенной к выходу 1 высокого напряжения, не изображенной на фиг. 1 цепи нагрузки электрическим высоким напряжением, абсолютная величина которого больше величины снабжающего схемное устройство питающего напряжения Vdd. Цепь нагрузки может представлять собой предпочтительно ячейки памяти предусмотренного в электронной карточке с памятью или в карточке с микропроцессором электрически программируемого и стираемого полупроводникового запоминающего устройства. Схемное устройство имеет соединенную с цепью нагрузки схему 2 накачки, которая на основе внутреннего коммутационного сигнала 3 с заданной частотой накачки выдает высокое напряжение, равное обычно + 18 В, через выход 1 высокого напряжения так, что получаемая схемой 2 накачки мощность накачки зависит, в основном, как от величины питающего напряжения Vdd, так и от величины частоты накачки коммутационного сигнала 3 схемы 2 накачки. Схемное устройство имеет приданную схеме 2 накачки, снабжаемую производным от питающего напряжения Vdd схемы накачки напряжением электронную схему 4 управления, которая в зависимости от зависящего от величины питающего напряжения Vdd управляющего сигнала 5 выдает на схему 2 накачки коммутационный сигнал 3, который воздействует на частоту накачки для создания выдаваемого схемой 2 накачки высокого напряжения так, что величина частоты накачки коммутационного сигнала 3 изменяется обратно пропорционально величине питающего напряжения Vdd. Схема 4 управления и схема 2 накачки соединены друг с другом через управляющие выходы 6, 7 схемы 4 управления и входы 8, 9 накачки схемы 2 накачки. В примере выполнения по фиг.1 управляющий сигнал 5 схемы 4 управления представляет собой непосредственно питающее напряжение Vdd схемного устройства. Схема 4 управления содержит генератор 10 в виде триггера Шмитта и включенный после генератора 10 в виде триггера Шмитта, выполненный из вентильных схем 11-21 делитель 22 частоты. Как показано на фиг.2, генераторный коммутационный контур 10 имеет первый вход 23 опорного напряжения и второй вход 24 опорного напряжения, на которые подают два постоянных опорных напряжения для юстирования схемного устройства. Кроме того, генераторный коммутационный контур 10 содержит последовательную цепь из четырех транзисторов 25 - 28, два р-канальных полевых транзистора 25, 26 и два n-канальных полевых транзистора 27, 28, которые включены между питающим напряжением Vdd и массой. Параллельно им включена вторая последовательная цепь из четырех транзисторов 29-32, двух р-канальных полевых транзистора 29, 30 и двух n-канальных полевых транзисторов 31, 32. Управляющий вход транзистора 25 подключен к первому входу 23 опорного напряжения и управляющий вход транзистора 28 подключен ко второму входу 24 опорного напряжения. Управляющие входы транзисторов 26, 27 соединены друг с другом. Управляющие входы транзисторов 29-32 соединены друг с другом и с точкой соединения обоих электродов транзисторов 26, 27. Кроме того, параллельно транзисторам 26, 27 включен конденсатор 35. Параллельно транзисторам 29-31 включен р-канальный полевой транзистор 33. Параллельно транзисторам 30-32 включен n-канальный полевой транзистор 34. Управляющие входы транзисторов 33, 34 соединены с точкой соединения электродов транзисторов 30, 31 и с входами двух вентилей НЕ 36, 37. Выход вентиля НЕ 36 соединен с общим управляющим входом транзисторов 26, 27. Выход вентиля НЕ 37 соответствует выходу 38 генераторного коммутационного контура 10. Генераторный коммутационный контур 10 через выход 38 соединен с делителем 22 частоты. Образованный из вентилей 11-21 делитель 22 частоты имеет пять вентилей НЕ 11-15, два отрицательных вентиля ИЛИ 16 и 17 и четыре с включенными перед ними соответствующими интегрированными вентилями И отрицательных вентиля ИЛИ 18-21, которые соединены указанным на фиг.1 образом. Первый и второй управляющие выходы 6, 7 схемы 4 управления соединены с первым, соответственно, со вторым входом 8, 9 накачки для подвода коммутационного сигнала 3 к схеме 2 накачки. Состоящая из четырнадцати конденсаторов 39, 40 и пятнадцати транзисторов 40, 41 схема 2 накачки представляет собой состоящую из четырнадцати ступеней, каждая из которых содержит один конденсатор 39, 40 и один работающий как диод транзистор 41, каскадную цепь, которая соединена согласно изображению на фиг.1. При этом ступени каскадной цепи соединены последовательно между выходом 1 высокого напряжения и питающим напряжением Vdd так, что работающие как диоды транзисторы 41 образуют последовательную цепь, которая соединяет подключенные к управляющим входам работающих как диоды транзисторов 41 конденсаторы 39, 40 попеременно обращенной от транзисторов стороной с обоими входами накачки 8, 9, при этом четные конденсаторы 39 соединены с входом накачки 8, а нечетные конденсаторы 40 - с входом накачки 9. Схема 2 накачки имеет другой работающий как диод транзистор 42 с обратной связью, который включен между питающим напряжением Vdd и состоящей из транзисторов 41 последовательной цепью и управляющий вход которого соединен с питающим напряжением Vdd. На фиг. 3 показаны четыре диаграммы 43-46, которые отображают изменение во времени некоторых напряжений показанного на фиг.1 и 2 схемного устройства. Кривая 43 изображает тактовый сигнал на выходе 38, создаваемый генераторным коммутационным контуром 10 при питающем напряжении Vdd=5 В, и вторая кривая 44 отображает находящееся на выходе 1 высокое напряжение. Аналогично этому кривые 45 и 46 отображают тактовый сигнал на выходе 38, соответственно, высокое напряжение на выходе 1 при питающем напряжении Vdd=3 В.

Принцип действия показанного на фиг.1 и 2 схемного устройства поясняется ниже подробнее с помощью показанных на фиг.3 изменений напряжений. Генератор 10 в виде триггера Шмитта образует на своем выходе 38 прямоугольный сигнал 45, 46, частота которого изменяется обратно пропорционально управляющему сигналу 5, который идентичен величине питающего напряжения Vdd схемного устройства. За счет подаваемых на входы 23, 24 опорных напряжений изображенная на фиг.2, образованная из транзисторов 25-28 последовательная цепь работает как источник тока, ток которой пропорционален питающему напряжению Vdd. Имеющая обратную связь через вентили НЕ 36 последовательная цепь транзисторов 29-31 и конденсатор 35 образуют колебательный контур и создают колебания, которые с помощью вентиля НЕ 37 преобразуются в прямоугольные сигналы и через выход 38 подаются на делитель 22 частоты. Сравнение кривых 43 и 45, которые изображают тактовые сигналы на выходе 38 генератора, показывает приблизительно обратно пропорциональную связь между питающим напряжением Vdd и тактовой частотой на выходе 38 генератора. Включенный за генератором 10 в виде триггера Шмитта делитель 22 частоты обрабатывает находящиеся на выходе 38 сигналы так, что коммутационный сигнал 3 состоит из двух находящихся на управляющих входах 6, 7 и тем самым на входах 8, 9 накачки, всегда противоположных друг другу прямоугольных сигналов. Схема 2 накачки перерабатывает поступающий на входы 8, 9 накачки коммутационный сигнал 3 в высокое напряжение на выходе 1 высокого напряжения. Кривые 44 и 46 иллюстрируют выполняемые схемой 2 накачки с половинной частотой находящегося на выходе 38 генератора соответствующего тактового сигнала пакетные повышения высокого напряжения на выходе 1, начальные значения которого соответствуют соответствующему питающему напряжению Vdd в 5 В и 3 В. В обоих случаях высокое напряжение на выходе 1 после 2 мкс повышается на примерно двойное значение соответствующего питающего напряжения Vdd и после следующих 2 мкс примерно на тройное значение соответствующего питающего напряжения Vdd, что означает почти независящую от питающего напряжения Vdd мощность накачки.

Схемное устройство для питания электронной цепи нагрузки электрическим высоким напряжением, абсолютная величина которого больше величины снабжающего схемное устройство питающего напряжения, которое имеет электрически соединенную с цепью нагрузки схему накачки, которая на основе внутреннего коммутационного сигнала с заданной частотой накачки выдает высокое напряжение на цепь нагрузки так, что получаемая цепью нагрузки электрическая мощность накачки схемы накачки зависит, в основном, как от величины питающего напряжения, так и от величины частоты накачки коммутационного сигнала схемы накачки. Схемное устройство имеет приданную схеме накачки, снабжаемую по меньшей мере производным от питающего напряжения схемы накачки напряжением электронную схему управления, которая в зависимости от зависящего от величины питающего напряжения управляющего сигнала выдает на схему накачки коммутационный сигнал, который воздействует на частоту накачки для создания выдаваемого схемой накачки высокого напряжения так, что величина частоты накачки коммутационного сигнала изменяется обратно пропорционально величине питающего напряжения. Технический результат - расширение диапазона питающих напряжений. 12 з.п.ф-лы, 3 ил.

| US 5414614 А, 09.05.1995 | |||

| Преобразователь постоянного напряжения | 1982 |

|

SU1073857A1 |

| US 4236199 А, 25.11.1980 | |||

| СПОСОБ ИЗМЕРЕНИЯ ДАВЛЕНИЯ НА РАЗНЫХ УРОВНЯХ ТРАХЕИ И КРУПНЫХ БРОНХОВ | 0 |

|

SU350462A1 |

Авторы

Даты

2002-05-20—Публикация

1997-03-27—Подача