Изобретение относится к схемному устройству согласно ограничительной части п.1 формулы изобретения.

После изготовления полупроводниковых схем с высокой степенью интеграции необходимо проверить их динамическую и статическую работоспособность, что означает для производителя необходимость выполнения в большинстве случаев дорогой процедуры тестирования. Вследствие большого количества всех возможных логических состояний как правило сложных схем проведение всеохватывающей проверки возможно только с высокими затратами. Так как стоимость тестирования, в частности, для полупроводниковых запоминающих устройств с высокой степенью интеграции составляет значительную часть стоимости производства, то желательно иметь способ тестирования и схемы тестирования, которые в течение короткого времени обеспечивают выявление возможно большего числа дефектов. Возможно раннее отсортирование дефектных схем из процесса производства обеспечивает уменьшение нагрузки на производственные установки и способствует тем самым экономии времени и средств. В настоящее время используют цикл проверки специально для электрически стираемого и программируемого полупроводникового запоминающего устройства следующим образом. Перед началом собственно цикла проверки стирают все ячейки памяти, а затем либо все ячейки памяти, либо выбранные по определенной системе ячейки памяти программируют на определенные логические значения. После этого может производиться так называемая усиленная нагрузка с повышенной температурой и/или повышенным напряжением стока. В последующем испытательном цикле проверяют ячейки памяти и схемные компоненты электрически стираемого и программируемого полупроводникового запоминающего устройства, например, посредством определения сдвига порогового напряжения ячеек памяти. После повторного стирания ячеек памяти проводят еще раз усиленную нагрузку ячеек памяти, при необходимости, с повышенным напряжением затвора и повторяют проверку функционирования с определением сдвига порогового напряжения ячеек памяти. Затем стирают информационное содержание электрически стираемого и программируемого полупроводникового запоминающего устройства. Д. Райн и X. Фрайтаг в публикации "Микроэлектронные запоминающие устройства", Вена, Нью-Йорк, издательство Шпрингер Ферлаг, с.117, описывают схемные решения для упрощения таких процессов проверки. В так называемом режиме группового программирования можно с помощью параллельного программирования двух или четырех байт сократить время программирования. В так называемом режиме нагрузки всей решетки одновременно прикладывают высокие нагрузочные напряжения на все пословные, соответственно, разрядные линии для воспроизведения дефектов в нормальном режиме в невыбранных ячейках. В так называемом пороговом режиме индивидуальной ячейки все считывающие схемы работают с нормальным напряжением, в то время как напряжение на пословных линиях может изменяться между 0 В и напряжением программирования (обычно, +18 В), за счет чего можно определить напряжение срабатывания ячеек. Во всех известных до настоящего времени тестах необходимо несколько раз программировать и затем стирать ячейку памяти. Однако это как раз для электрически стираемого и программируемого полупроводникового запоминающего устройства требует очень много времени и приводит к большой длительности испытания, так как для программирования, соответственно, стирания электрически стираемого и программируемого полупроводникового запоминающего устройства необходимо до 50 мс/байт. Другие известные по испытаниям динамического запоминающего устройства с произвольной выборкой алгоритмы (например, так называемый маршевый тест) нельзя использовать вследствие большого числа требуемых циклов программирования, в частности, для флэш-ППЗУ.

Из DE-A-43 12238 С2 известен способ освобождения полупроводникового запоминающего устройства от короткого замыкания между соседними линиями выбора ячеек памяти, в котором посторонний материал, который замыкает соседние линии выбора ячеек памяти, выжигают с помощью джоулевого тепла. Для этой цели к линиям выбора ячеек памяти прикладывают повышенное напряжение от электрического источника. Из публикации известен способ приложения к соседним линиям различных потенциалов и определения короткого замыкания за счет определения тока утечки.

Из ЕР-А-0 480752 известно схемное устройство согласно п. 1 формулы изобретения в виде монолитно интегрированной с постоянным запоминающим устройством испытательной схемы, которая выполнена в трех вариантах. В первом варианте, в котором тестируются пословные линии, на все нечетные пословные линии WL1, WL3 и т.д. подается высокий сигнал из испытательной схемы, в то время как все четные пословные линии WL0, WL2 и т.д. подключаются к низкому сигналу. В случае короткого замыкания между соседними пословными линиями на выходе испытательной схемы течет ток Itw, на основании которого можно распознать дефект в пословных линиях, однако не локализовать его. В другом варианте предусмотрена соответствующе работающая испытательная схема для разрядных линий. Четные разрядные линии подключают к высокому сигналу, нечетные разрядные линии - к низкому сигналу. За счет измерения тока Itb, протекающего по сигнальной линии для сигнального пути ТЕСТ 1, возможно определить наличие короткого замыкания между соседними разрядными линиями, однако снова без возможности локализации конкретной дефектной разрядной линии. В следующем варианте предусмотрена, наконец, комбинация испытательной схемы для пословных линий и испытательной схемы для разрядных линий. Однако все известные испытательные схемы позволяют производить только "глобальное" испытание пословных или разрядных линий; локализация дефектной сигнальной линии таким способом невозможна.

В основе настоящего изобретения лежит задача, создать схемное устройство указанного в начале типа, которое позволяет с возможно меньшими схемными дополнительными затратами получать быстрый и при этом достаточно информативный результат тестирования работоспособности схемного устройства.

Поставленная задача решается тем, что в схемном устройстве с испытательной схемой для проверки его работоспособности, содержащем заданное количество выполненных рядом друг с другом на полупроводниковой подложке в систематическом порядке групповых линий, с которыми соединено множество выполненных на полупроводниковой подложке и идентичных друг другу электронных элементарных схем, причем испытательная схема предусмотрена для проверки работоспособности электронных элементарных схем и/или групповых линий, выполнена интегрирование также на полупроводниковой подложке схемного устройства и имеет соответствущее групповым линиям коммутационное устройство, выполненное с возможностью подачи, по меньшей мере, на одну заданную групповую линию первого испытательного сигнала, а на другую групповую линию, расположенную непосредственно рядом с заданной групповой линией, второго испытательного сигнала, имеющего отличный от первого испытательного сигнала уровень, при этом предусмотрено соответствующее групповым линиям устройство обнаружения, регистрирующее выходной сигнал, снимаемый с групповых линий, на которые подан первый или второй испытательный сигнал, также предусмотрено соответствующее количеству групповых линий число переключателей, выполненных с возможностью управления сигналом выбора для последовательного включения или первого или второго испытательного сигнала на групповую линию, согласно изобретению устройство обнаружения имеет соответствующую четным групповым линиям первую линию обнаружения, соответствующую нечетным групповым линиям вторую линию обнаружения и соответствующие каждой групповой линии электрически соединенные со стороны управляющих входов с групповыми линиями переключатели обнаружения, причем переключатели обнаружения со стороны входов находятся на заданном постоянном опорном потенциале, а со стороны выходов в соответствии с принадлежностью к четной или нечетной групповой линии электрически присоединены к первой или, соответственно, второй линии обнаружения.

В основе изобретения заложена идея использования во многих случаях имеющейся пространственной симметрии, соответственно, регулярного расположения множества структурно одинаково расположенных элементарных схем для схемно просто выполненного и требующего немного времени тестирования целостности или разрыва групповых линий. Во многих случаях было установлено, что большое число обусловленных процессом производства дефектов можно выявить с помощью проверки целостности или разрыва групповых линий. За счет этого определяются, в частности, дефектные групповые линии, а также можно определять вызываемые элементарными схемами дефектные электрические соединения между самими групповыми линиями и между групповыми линиями и другими линиями. Проверку целостности или разрыва групповых линий можно проводить очень быстро по сравнению с проверкой работоспособности элементарных схем. Проводимые с помощью испытательной схемы согласно изобретению испытательные циклы в течение короткого времени обеспечивают высокую выявляемость дефектов, которая может быть положена в основу эффективного предварительного отбора дефектных деталей. Существенное преимущество изобретения состоит в том, что испытательная схема выполнена с помощью простых схемных решений и состоит только из небольшого числа дополнительных компонентов, которые необходимо предусмотреть на полупроводниковой подложке, так что испытательная схема как неотъемлемая составная часть полупроводниковой схемы интегрируется на той же полупроводниковой подложке. Во многих случаях можно использовать уже имеющиеся части подлежащей тестированию схемы одновременно в качестве определенных составляющих частей испытательной схемы, так что дополнительная площадь, необходимая для испытательной схемы на полупроводниковой подложке является небольшой.

При предпочтительном усовершенствовании изобретения в отношении короткой длительности испытаний может быть предусмотрено, что с помощью приданного групповым линиям коммутационного устройства на все четные групповые линии подается первый испытательный сигнал и на все нечетные групповые линии - второй испытательный сигнал, и приданное групповым линиям устройство обнаружения измеряет выходной сигнал, снимаемый с нагруженных первым, соответственно, вторым испытательным сигналом четных, соответственно, нечетных групповых линий. Это позволяет с помощью только одного теста, в котором на четные и нечетные групповые линии подаются только два испытательных сигнала, одновременно проверять множество проходящих рядом друг с другом групповых линий на целостность или разрыв и определять наличие коротких замыканий между соседними групповыми линиями.

При дальнейшем усовершенствовании схемного устройства согласно изобретению может быть предусмотрено, что поперек групповым линиям предусмотрено заданное количество выполненных на полупроводниковой подложке проходящими рядом друг с другом коллективных линий, при этом в каждом месте пересечения групповых и коллективных линий предусмотрена элементарная схема, связанная с групповой и коллективной линиями соответствующего места пересечения. Элементарные схемы расположены, предпочтительно, в виде матрицы и при этом каждой групповой, соответственно, коллективной линии придается одна строка или столбец матрицы. Это дает возможность посредством сравнения испытательных сигналов на групповых линиях с испытательными сигналами на связанных соответствующими элементарными схемами с групповыми линиями коллективных линиях проверять элементарные схемы на целостность и отсюда делать выводы о правильном функционировании элементарных схем.

В особенно простом по схеме варианте выполнения может быть предусмотрено соответствующее количеству групповых линий число переключателей, которые с помощью сигнала выбора подключают первый или второй испытательный сигнал к групповой линии, при этом все управляющие входы приданных четным групповым линиям переключателей соединены с первой линией выбора и приданных нечетным групповым линиям - со второй линией выбора. При этом линии выбора и соответствующие приданные каждой групповой линии переключатели являются единственными дополнительно выполненными на полупроводниковой подложке компонентами испытательной схемы. Все линии выбора, а также переключатели можно выполнить с помощью распространенных технологий (КМОП, ТТЛ и т.д.). Если для выполнения линий выбора и переключателей испытательной схемы используется та же полупроводниковая технология, что и для групповых линий и элементарных схем подлежащей тестированию схемы, то дополнительные затраты на разработку и изготовление схемного устройства являются небольшими.

Для идентификации отдельных дефектных групповых линий может быть предусмотрено, что коммутационное устройство подает испытательный сигнал на единственную заданную групповую линию, а на все остальные групповые линии подает второй испытательный сигнал. Этот тест позволяет наряду с определением короткого замыкания между двумя любыми групповыми линиями также однозначно идентифицировать дефектную групповую линию. Для идентификации необходимо столько испытательных циклов, сколько имеется групповых линий. В каждом испытательном цикле на одну групповую линию подают первый испытательный сигнал, а на все остальные - второй испытательный сигнал.

Для особенно быстрого обнаружения коротких замыканий между соседними групповыми линиями может быть предусмотрено, что коммутационное устройство имеет приданный каждой групповой линии, управляемый попеременно двумя линиями выбора и связанный с соответствующей групповой линией на выходе переключатель, при этом придаваемый определенной групповой линии переключатель со стороны входа подключен к первому входному сигналу и приданные другим групповым линиям переключатели со стороны входа подключены ко второму входному сигналу, и что устройство обнаружения имеет приданную четным групповым линиям первую линию обнаружения, приданную нечетным групповым линиями вторую линию обнаружения и приданные каждой групповой линии, электрически соединенные со стороны входа с групповыми линиями переключатели обнаружения, при этом переключатели со стороны входа подключены к заданному постоянному опорному потенциалу и со стороны выхода системы электрически соединены с четной или нечетной групповой линией, соответственно, с первой или второй линией обнаружения, при этом устройство обнаружения имеет соединенное с первой линией обнаружения первую схему распознавания токов и соединенную со второй линией обнаружения вторую схему распознавания токов. Если это устройство обнаружения регистрирует на четных, соответственно, нечетных групповых линиях другие испытательные сигналы, чем те, которые подает коммутационное устройство на четные, соответственно, нечетные групповые линии, то можно сделать, по меньшей мере, вывод о наличии короткого замыкания, по меньшей мере, между двумя соседними групповыми линиями или же дефектной линии обнаружения.

Для идентификации дефектных групповых линий может быть также предусмотрено, что устройство обнаружения имеет приданные каждой групповой линии, электрически связанные схемы распознавания сигналов. В большинстве случаев в полупроводниковых схемах указанного в начале типа уже имеются приданные каждой групповой линии схемы, которые можно использовать как схемы распознавания сигналов, так что не требуется дополнительных схемных затрат для устройства обнаружения.

Этот вариант выполнения можно усовершенствовать так, что устройство обнаружения имеет ряд приданных селектирующих переключателей в соответствии с числом групповых линий, которые включены между групповыми линиями и схемами распознавания сигналов и управляются через общую линию селекции. Это обеспечивает, например, возможность с помощью переключения селектирующего переключателя переключать находящуюся на определенном потенциале групповую линию в состояние запирания и проверять, не разряжаются ли групповые линии и тем самым являются действительно изолированными, или что они разряжаются, что означает нежелательное соединение с соседними групповыми линиями или с другими частями схемы.

При особенно простой по схеме реализации коммутационного устройства может быть предусмотрено, что переключатели для первого и второго испытательных сигналов представляют собой переключающие транзисторы или снабженные отключаемым соединением на массу инверторы. Эти элементы схемы могут быть изготовлены без дополнительных затрат на производство на полупроводниковой подложке для интеграции испытательной схемы согласно изобретению.

При особенно предпочтительном применении схемного устройства согласно изобретению может быть предусмотрено, что элементарные схемы в местах пересечения групповых и коллективных линий представляют собой ячейки памяти выполненного на полупроводниковой подложке запоминающего устройства. В особенности в полупроводниковых запоминающих устройствах испытания на целостность, разрыв или короткое замыкание групповых линий приводит к экономии времени. Программирование, стирание и считывание ячеек памяти полупроводникового запоминающего устройства требует много времени, в частности, если речь идет о электрически программируемом и стираемом полупроводниковом запоминающем устройстве. При этом соответствующий уровню техники способ проверки требует до 50 мс/байт, в то время как испытания согласно изобретению требуют обычно менее 50 мс/байт, что соответствует разнице величин в 106 раз.

Для всех типов полупроводниковых запоминающих устройств может быть предусмотрено, что групповые линии представляют собой пословные или разрядные линии, коллективные линии - разрядные или пословные линии, линии обнаружения - линии считывания, переключатели обнаружения - соединенные с линиями считывания переключатели, первая и вторая схемы распознавания токов соединенные с линиями считывания усилители считывания и схемы распознавания сигналов - соединенные с разрядными линиями усилители считывания, которые являются уже имеющимися в полупроводниковом запоминающем устройстве схемными составляющими и могут быть, предпочтительно, использованы для проведения испытаний с помощью схемы согласно изобретению. Это не требует дополнительных схемных затрат в полупроводниковом запоминающем устройстве для схемы обнаружения, для которой можно использовать исключительно уже имеющиеся схемные компоненты.

Транзисторы, приданные линии выбора и каждой пословной линии, можно, предпочтительно, включать перед приданными пословной линии, уже имеющимися в полупроводниковом запоминающем устройстве драйверами пословных линий. За счет этого можно использовать для существенной составной части схемного устройства, которое создает необходимые для испытательных сигналов напряжения, уже имеющиеся относительно сложные устройства.

Перед состоящим из транзисторов коммутационным устройством необходимо включить реверсирующее коммутационное устройство, которое соединяет линию выбора с отличным от нуля, предпочтительно, положительным напряжением или с нулевым напряжением. Для этого можно использовать в качестве нулевого напряжения уже имеющийся контакт массы, а в качестве положительного напряжения, например, питающее напряжение или другое имеющееся на полупроводниковой подложке напряжение.

В другом варианте выполнения может быть предусмотрено, что соединенное с разрядными линиями коммутационное устройство представляет собой имеющееся в полупроводниковом запоминающем устройстве устройство для подачи напряжения программирования на разрядные линии. В этом случае дополнительные схемные затраты на испытательную схему состоят только из двух линий выбора, соответственно, из линий селекции или разъединения для всей матрицы памяти, а также из одного транзистора, соответственно, инвертора для каждой групповой линии. Все другие составляющие части испытательной схемы, как например, драйверы пословных линий и генераторы напряжения программирования, а также усилители считывания и линии считывания для устройства обнаружения и без того имеются в полупроводниковом запоминающем устройстве.

При предпочтительном применении испытательной схемы согласно изобретению для проверки полупроводниковых запоминающих устройств, в частности, электрически программируемых и стираемых полупроводниковых запоминающих устройств предпочтительным образом используется то, что большая часть обусловленных процессом изготовления дефектов вызываются короткими замыканиями металлизации и поликристаллизации, а также короткими замыканиями оксида управляющего электрода. Испытательная схема согласно изобретению проверяет указанные выше статические линии без программирования ячеек памяти и обеспечивает тем самым в течение минимального времени высокую степень выявления дефектов.

Дальнейшие признаки, преимущества и целесообразности изобретения следуют из последующего описания примеров выполнения с помощью чертежей, на которых изображено:

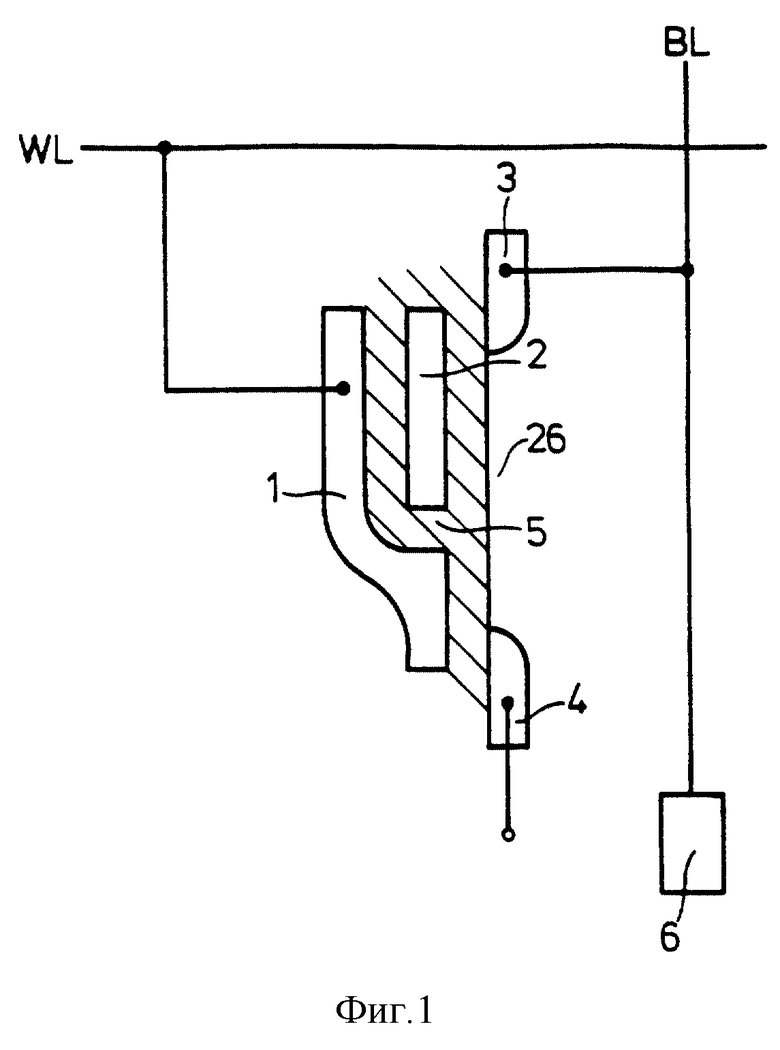

фиг. 1 - схематичный вид построения ячейки памяти электрически программируемого и стираемого полупроводникового запоминающего устройства с пословными и разрядными линиями;

фиг. 2 - схематичный вид схемного устройства с испытательной схемой для проверки пословных линий и проверки линий считывания электрически программируемого и стираемого полупроводникового запоминающего устройства согласно первому примеру выполнения;

фиг. 3А - схематичный вид схемного устройства с испытательной схемой для проверки пословных линий и проверки линий считывания электрически программируемого и стираемого полупроводникового запоминающего устройства согласно второму примеру выполнения;

фиг.3В - схематичный вид внутреннего построения инвертора, содержащегося в изображенном на фиг.3А схемном устройстве;

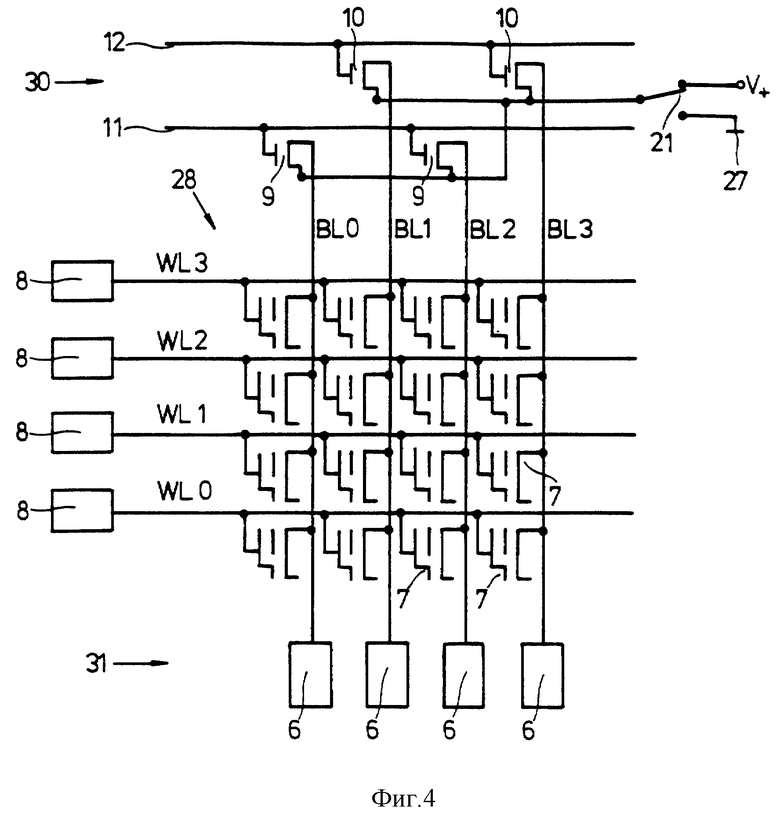

фиг. 4 - схематичный вид схемного устройства с испытательной схемой для проверки разрядных линий электрически программируемого и стираемого полупроводникового запоминающего устройства с усилителями напряжения считывания согласно третьему примеру выполнения;

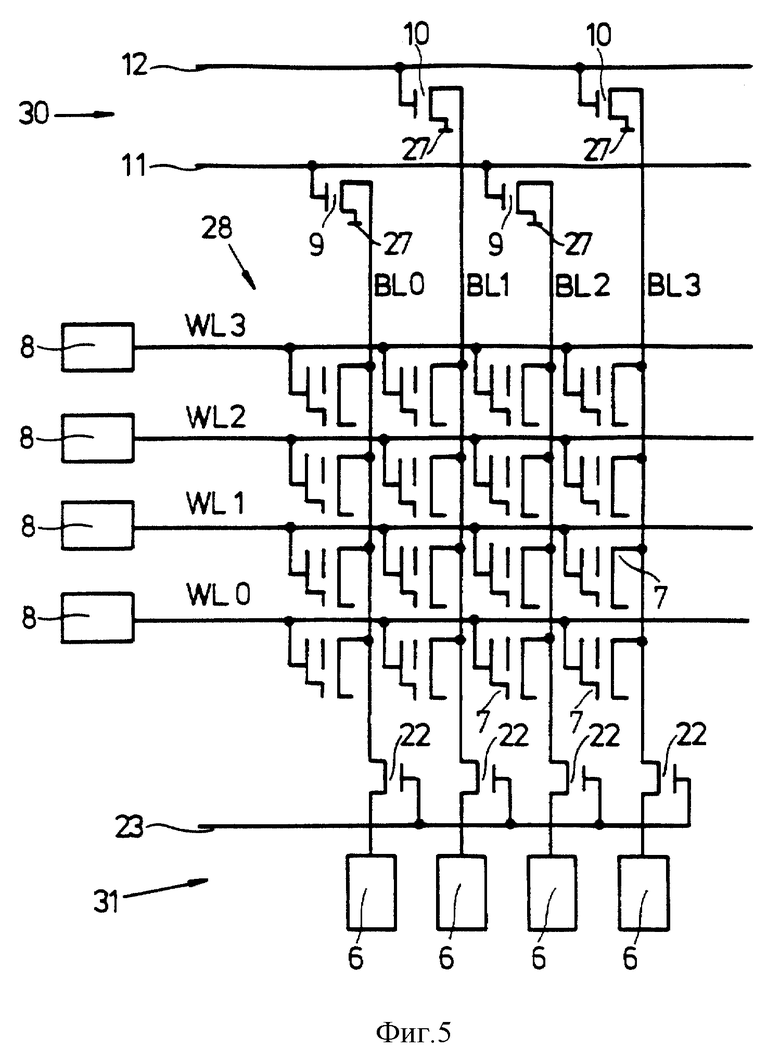

фиг. 5 - схематичный вид схемного устройства с испытательной схемой для проверки разрядных линий электрически программируемого и стираемого полупроводникового запоминающего устройства с усилителями тока считывания согласно третьему примеру выполнения;

фиг. 6 - схематичный вид схемного устройства с испытательной схемой для проверки разрядных линий электрически программируемого и стираемого полупроводникового запоминающего устройства с усилителями тока считывания.

Так как применение испытательной схемы согласно изобретению особенно предпочтительно для электрически программируемых и стираемых полупроводниковых запоминающих устройств, то все последующие поясняемые подробно примеры выполнения относятся к электрически программируемым и стираемым полупроводниковым запоминающим устройствам с единожды программируемыми или флэш-программируемыми (многократно программируемыми) ячейками памяти. На фиг.1 в схематичном виде показана одна ячейка памяти электрически программируемого и стираемого полупроводникового запоминающего устройства. Однако область применения схемы согласно изобретению не ограничивается программируемыми накопителями постоянных величин или другими энергонезависимыми накопителями, а распространяется также на любые другие типы накопителей и логических схем с регулярно расположенными элементарными схемами.

На фиг.1 в качестве примера элементарной схемы показана ячейка 7 памяти, состоящая из управляющего электрода 1, несвязанного с потенциалом электрода 2. электрода 3 стока и электрода 4 истока. Несвязанный с потенциалом электрод 2 окружен изолятором 5. Управляющий электрод 1 соединен с пословной линией WL, приданной вышестоящей для ячейки 7 памяти строке, электрод 3 стока электрически соединен с разрядной линией BL, приданной вышестоящему для ячейки памяти столбцу. Контакты истока 4 ячеек памяти соединены друг с другом и находятся на общем, заданном потенциале. Ячейка памяти работает самим по себе известным образом как описано ниже. Обоим состояниям ячейки 7 памяти соответствует заряженное или незаряженное состояние несвязанного с потенциалом электрода 2. Для программирования вводятся заряды в несвязанный с потенциалом электрод 2 тем, что на управляющий электрод 1 подают положительное высокое напряжение относительно электрода 3 стока. Величина положительного высокого напряжения составляет, обычно, около +18 В. Для стирания из несвязанного с потенциалом электрода 2 удаляют электроны, соответственно, инжектируют дырки в связанный с потенциалом электрод тем, что прикладывают отрицательное высокое напряжение к управляющему электроду 1 относительно электроду 3 стока, величина которого составляет, обычно, около - 12 В. Эти превышающие по абсолютной величине питающее напряжение напряжения необходимы для того, чтобы преодолеть создаваемые изолятором 5 потенциальные барьеры. На основании высокой силы электрического поля электроны могут преодолевать туннельные потенциальные барьеры изоляторов (эффект Фоулера-Нордхайма) или возникшие вблизи электрода стока горячие электроны могут преодолеть изолятор (эффект канализации горячих электронов). Для считывания прикладывают положительное напряжение около 5 В между управляющим электродом 1 и электродом 3 стока, которое однако недостаточно для изменения состояния зарядки несвязанного с потенциалом электрода 2.

На фиг. 2 показан первый пример выполнения схемного устройства согласно изобретению с заданным числом выполненных на полупроводниковой подложке 26 с равномерным шагом рядом друг с другом пословных линий WL0, WL1, WL2, WL3, которые в данном случае в общем виде обозначаются так же, как групповые линии, а также с заданным числом выполненных поперек пословным линиям на полупроводниковой подложке 26 рядом друг с другом разрядных линий BL0, BL1, BL2, BL3, которые в данном случае обозначаются как коллективные линии. С каждым местом пересечения пословных и разрядных линий связана обозначаемая как элементарная схема ячейка 7 памяти электрически программируемого и стираемого полупроводникового запоминающего устройства 28. Для управления пословными линиями WL0 - WL3 предусмотрены драйверы 8 пословных линий, которые известным образом соединены с (не изображенными) схемами декодирования адресов. Для считывания находящегося на разрядных линиях BL0 - BL3 информационного содержания из ячеек 7 памяти предусмотрены схемы 6 усилителей считывания, построение и принцип действия которых также известны специалисту. Пословные линии WL0-WL3 через линии 15 и 16 считывания и через транзисторы 13 и 14 линий считывания соединены с усилителями 29 считывания, при этом линии считывания 15 и 16 через делитель напряжения с сопротивлениями 17 соединены с питающим напряжением Vdd, за счет чего усилители 29 считывания работают как схемы распознавания тока. Драйверы 8 пословных линий, схемы 6 усилителей считывания, а также схемы 29 усилителей тока считывания являются известными для специалиста составляющими частями электрически программируемого и стираемого полупроводникового запоминающего устройства и поэтому не требуют подробного описания принципа их действия. В соответствии с изобретением предусмотрено коммутационное устройство 30, состоящее из переключающих транзисторов 9 и 10, а также линий 11 и 12 выбора, принцип действия которых поясняется подробнее ниже.

С помощью показанного на фиг.2 первого примера выполнения можно проводить следующий испытательный цикл. Четные пословные линии WL0, WL2 с помощью драйверов 8 пословных линий предварительно заряжаются на 0 В и отделяются с помощью переключающих транзисторов 9 коммутационного устройства 30. На нечетные пословные линии WL1, WL3 подается с драйверов 8 пословных линий через переключающие транзисторы 10 напряжение считывания. Только в одной из линий 15 или 16 считывания может течь ток. Если в обеих линиях 15 и 16 считывания с помощью усилителей 29 тока считывания регистрируется ток, то либо имеется короткое замыкание между соседними пословными линиями WL0,...,WL3, либо имеется дефект декодирования. Если ни в одной линии 15 и 16 не обнаруживается ток, то либо прервана линия 16 считывания, либо имеется дефект декодирования. Испытательный цикл повторяют с измененными ролями четных пословных линий WL0, WL2 и нечетных пословных линий WL1, WL3. Этот испытательный цикл позволяет также судить о возможных коротких замыканиях между соседними пословными линиями WL0, ...,WL3, разрывах линий 15, 16 считывания или дефектах декодирования. Короткие замыкания между соседними пословными линиями WL0,... , WL3 могут быть, например, короткими замыканиями металлизации или поликристаллизации, или вызываться примыкающими к электродам элементарных схем оксидными слоями. В этом испытательном цикле указанные выше соединения проверяют статически без программирования ячеек 7 памяти. За счет этого за короткое время достигается высокая степень обнаружения дефектов.

Показанный на фиг.3А второй пример выполнения схемного устройства согласно изобретению отличается от показанного на фиг.1 первого примера выполнения построением создающего испытательные сигналы коммутационного устройства 30. Вместо переключающих транзисторов 9, 10 и линий 11, 12 выбора это коммутационное устройство 30 имеет инверторы 18, приданные соответствующим пословным линиям WL0, ...,WL3, которые со стороны выхода соединены с пословными линиями WL0,...,WL3. Контакты массы клемм питающего напряжения инверторов 18 соединены друг с другом и через разделительную линию 19 и работающий как разделительный переключатель транзистор 20 соединены с массой 27. Эти инверторы 18 уже могут иметься в полупроводниковых запоминающих устройствах в виде драйверов 8 пословных линий. В качестве устройства 31 обнаружения используются как в первом примере выполнения приданные разрядным линиям BL0,..., BL3 усилители 6 считывания, линии 15, 16 считывания, транзисторы 13, 14 линий считывания и приданные соответствующим линиям считывания 15, 16, соединенные через сопротивление 17 с питающим напряжением Vdd, работающие как схемы распознавания тока усилители 29 считывания. На фиг. 3В показано внутреннее построение инвертора 18, который состоит из последовательно включенных между питающим напряжением и разделительной линией р-канального транзистора 32 и n-канального транзистора 33. Общий управляющий контакт транзисторов 32, 33 соответствует входу инвертора 18, а общая точка соединения электродов транзисторов 32, 33 - выходу инвертора 18.

С помощью изображенного на фиг.3А и 3В второго примера выполнения можно проводить следующий испытательный цикл. Приданный разделительной линии 19 разделительный переключатель 20 сперва является проводящим, за счет чего обе клеммы питающего напряжения инвертора 18 находятся между питающим напряжением Vdd и массой 27. Выбирают пословную линию WLn и с помощью приданного ей инвертора 18 подают на нее напряжение считывания. Другие пословные линии WLn' (n′ ≠ n) с помощью приданных им инверторов 18 активно переводятся на 0 В. Затем разделительный переключатель 20 запирается и за счет этого все приданные пословным линиям WLn и WLn' инверторы 18 отсоединяются от массы. За счет этого предварительно заряженные на 0 В пословные линии WLn' не являются связанными с потенциалом. Если имеется короткое замыкание между выбранной пословной линией WLn и соседней пословной линией WLn', при этом n'=n-1 или n'= n+1, то приданный пословной линии WLn инвертор 18 переводит соединенную через короткое замыкание соседнюю пословную линию WLn' на напряжение, которое находится между напряжением считывания и нулевым напряжением.

В этом случае в обеих линиях 15, 16 считывания течет ток, который обнаруживается усилителями 29 считывания. Ток в обеих линиях 15, 16 считывания может, кроме короткого замыкания между выбранной пословной линией WLn и соседней пословной линией WLn', сигнализировать также дефект декодирования. Если ни в одной из линий 15, 16 считывания не обнаруживается ток, то имеют разрыв выбранная пословная линия WLn или одна из линий 15 или 16 считывания, или имеет место дефект декодирования. В каждый испытательный цикл последовательно выбирается каждая пословная линия WL0,...,WL3 в качестве той пословной линии WLn, на которую подается напряжение считывания. Если уже имеющиеся на полупроводниковой подложке 26, приданные линиям 15, 16 считывания усилители 29 считывания выполнены не как усилители тока считывания и таким образом не обеспечивают соединение по току с питающим напряжением Vdd, то необходимо ввести, например, работающие в качестве нагрузки сопротивления или транзисторы, работающие в режиме нагрузки. Таким образом, можно использовать высокоомные усилители напряжения считывания в качестве схем 29 распознавания тока считывания.

На фиг. 4 показан третий пример выполнения схемного устройства согласно изобретению для проверки разрядных линий для идентификации дефектных разрядных линий BL0,...,BL3, которые в этом и последующих примерах выполнения означают групповые линии электрически программируемого и стираемого полупроводникового запоминающего устройства 28 с работающими как детекторы напряжения, соединенными с разрядными линиями BL0,...,BL3 усилителями 6 считывания, которые образуют устройство 31 обнаружения. В качестве создающего испытательные сигналы коммутационного устройства 30 служат приданные каждой разрядной линии BL0, ...,BL3 переключающие транзисторы 9, 10 между разрядными линиями BL0,...,BL3 и выполненным с возможностью переключения между заданным положительным напряжением V+ и массой 27 реверсирующим переключателем 21. Управляющие входы приданных четным разрядным линиям BL0,...,BL3 переключающих транзисторов 9 соединены друг с другом и связаны с первой линией 11 выбора. Управляющие входы приданных нечетным разрядным линиям BL0,..., BL3 переключающих транзисторов 10 соединены друг с другом и связаны со второй линией 12 выбора. Приданные каждой разрядной линии BL0,...,BL3, работающие как датчики напряжения усилители 6 считывания с высокоомным входом, которые образуют устройство 31 обнаружения, уже имеются в полупроводниковом запоминающем устройстве.

С помощью изображенного на фиг.4 третьего примера выполнения можно проводить следующий испытательный цикл. Общий контакт электродов 4 истока всех ячеек 7 памяти и все пословные линии WL0,...,WL3 во время всего испытательного цикла находятся на 0 В. Все разрядные линии BL0,...,BL3 с помощью управляемых линиями 11, 12 выбора транзисторов 9, 10 и подключенного к положительному напряжению V+ реверсирующего переключателя 21 предварительно заряжаются до положительного напряжения V+. Если при последующем считывании всех разрядных линий BL0,...,BL3 усилитель 6 считывания регистрирует нулевой уровень, то соответствующая разрядная линия BL0,...,BL3 имеет разрыв. Затем на 0 В переключаются все четные разрядные линии BL0, BL2 через проводящие транзисторы 9 и переключенный на массу 27 реверсирующий переключатель 21, в то время как нечетные разрядные линии BL1, BL3 с помощью запертых транзисторов 10 работают вхолостую. При последующем считывании всех разрядных линий BL0,...,BL3 на усилителях 6 считывания четных разрядных линий BL0, BL2 должен находиться уровень 0 В, а на усилителях 6 нечетных разрядных линий BL1, BL3 - положительное напряжение предварительной зарядки V+. Если на нечетной разрядной линии BL1, BL3 измеряется уровень 0 В, то имеется короткое замыкание между нечетной разрядной линией BL1, BL3 и соседней четной разрядной линией BL0, BL2 или соответствующая нечетная разрядная линия BL1, BL3 имеет разрыв и таким образом не получила предварительной зарядки до положительного напряжения V+. Испытательный цикл повторяют тем, что четные разрядные линии BL0, BL2 меняются ролями с нечетными разрядным линиям BL1, BL3.

На фиг.5 показан четвертый пример выполнения, который, по существу, является дальнейшим расширением показанного на фиг.4 третьего примера выполнения. Усилители 6 считывания работают в противоположность третьему примеру выполнения как датчики тока. В каждой разрядной линии BL0,...,BL3 между разрядным линиям BL0,...,BL3 и усилителями 6 считывания дополнительно включены работающие как селектирующие переключатели транзисторы 22. Управляющие входы селектирующих переключателей 22 соединены все вместе с селектирующей линией 23.

С помощью показанного на фиг.5 четвертого примера выполнения можно выполнять следующие четыре проверки. Все пословные линии WL0,...,WL3 и общий контакт электродов 4 истока ячеек 7 памяти во время всех четырех испытательных циклов находятся на уровне 0 В. В первом испытательном цикле селектирующие переключатели 22 сперва заперты с помощью селектирующей линии 23 и все разрядные линии BL0,...,BL3 отсоединены и считаны через усилители 6 считывания. Если в одном из усилителей 6 считывания обнаруживается ток, то в соответствующей разрядной линии BL0,...,BL3 имеется пробой туннельного оксидного сополидиэлектрика или вызванное, например, металлическими частицами прямое короткое замыкание с одной пословной линией WL0,...,WL3. Во втором проверочном цикле все разрядные линии BL0,...,BL3 посредством приложения питающего напряжения Vdd к линиям выбора 11, 12 переводятся на 0 В и считываются через усилитель 6 считывания. Если в одной из разрядных линий BL0,..., BL3 не обнаруживается ток, то соответствующая разрядная линия BL0,...,BL3 имеет разрыв. Третий проверочный цикл состоит в том, что четные разрядные линии BL0, BL2 переводят на 0 В, в то время как нечетные разрядные линии BL1, BL3 остаются несвязанными с потенциалом. Если затем считывать все разрядные линии BL0,...,BL3 через усилители 6 считывания, то приданные четным разрядным линиям BL0, BL2 усилители 6 считывания должны обнаруживать ток, а приданные нечетным разрядным линиям BL1, BL3 не должны обнаруживать ток. Если в нечетной разрядной линии BL1, BL3 течет ток, то существует низкоомное короткое замыкание между двумя разрядным линиям BL0,...,BL3. Предпосылкой для обнаружения является то, что транзисторы 9, 10 коммутационного устройства 30 могут переводить на 0 В более одного усилителя 6 считывания. Недостаток испытательного цикла состоит в том, что высокоомное короткое замыкание между двумя разрядным линиям BL0,...,BL3 при некоторых обстоятельствах не вызывает достаточного тока в неполучающей напряжение разрядной линии BL0, ...,BL3 и поэтому остается не распознанным. Третий испытательный цикл повторяют тем, что меняют ролями четные и нечетные разрядные линии BL0,...,BL3. В четвертом испытательном цикле работающие как селектирующие переключатели транзисторы 22 позволяют распознавать высокоомное короткое замыкание. Сперва все разрядные линии BL0,...,BL3 с помощью переключателей 9, 10 отделяют от массы 27 и затем через усилители 6 считывания переводят на положительный потенциал V+. Затем за счет запирания селектирующих переключателей 22 отсоединяют усилители 6 считывания, за счет чего сохраняется заряд в разрядных линиях BL0, ...,BL3. После этого в течение заданного времени за счет приложения питающего напряжения Vdd к первой линии 11 выбора активно переводят четные разрядные линии BL0, BL2 на 0 В, в то время как за счет приложения нулевого напряжения ко второй линии 12 выбора нечетные разрядные линии BL1, BL3 находятся в несвязанном с потенциалом состоянии на положительном уровне V+. В течение этого заданного времени может быть разряжена несвязанная с потенциалом разрядная линия BL1, BL3 через возможно имеющееся короткое замыкание между двумя разрядным линиям BL0,...,BL3. По истечении заданного времени считывают все разрядные линии BL0,...,BL3 с помощью открытых селектирующих переключателей 22 и в течение короткого времени снова отделяют от усилителей 6 считывания. Это необходимо потому, что иначе разряженная через высокоомное короткое замыкание разрядная линия BL0,...,BL3 в течение короткого времени снова зарядится до положительного уровня V+, и тем самым дефект останется нераспознанным. Результат проверки четных разрядных линий BL0, BL2 и нечетных разрядных линий BL1, BL3 должен соответствовать состояниям наличия тока или отсутствия тока. Если в нечетной разрядной линии BL0, . . . , BL3 обнаруживается ток, то существует короткое замыкание между двумя разрядным линиям BL0, . ..,BL3. Испытательный цикл повторяют с измененными ролями четных и нечетных разрядных линий BL0,...,BL3 тем, что на первую линию 11 выбора подают нулевое напряжение, а на вторую линию 12 выбора - питающее напряжение Vdd.

На фиг. 6 показан пятый пример выполнения, в котором создающее испытательные сигналы коммутационное устройство 30 находится на той же стороне матрицы памяти, что и устройство 31 обнаружения. При этом хотя и нельзя проводить испытания на целостность разрядных линий BL0,...,BL3, однако к разрядным линиям BL0, . ..,BL3 можно через пути программирования прикладывать напряжения, за счет чего нет необходимости в транзисторах. Каждая разрядная линия BL0,...,BL3 соединена через переключающий транзистор 9, 10 с фиксирующей схемой 24, 25. Усилители 6 считывания работают как драйверы и датчики тока и тем самым являются одновременно составной частью коммутационного устройства 30 и устройства 31 обнаружения. Точки соединения обращенных от фиксирующих схем 24, 25 электродов переключающих транзисторов 9, 10 на разрядных линиях BL0,...,BL3 находятся между селектирующими переключателями 22 и ячейками 7 памяти. Управляющие входы приданных четным разрядным линиям BL0, BL2 переключающих транзисторов 9 подключены совместно к первой линии 11 выбора. Управляющие входы приданных нечетным разрядным линиям BL1, BL3 переключающих транзисторов 10 соединены со второй линией 12 выбора.

С помощью показанного на фиг.6 пятого примера выполнения можно выполнять следующие четыре испытательных цикла. Во время всех четырех испытательных циклов все пословные линии WL0,...,WL3 и общий контакт электродов 4 истока ячеек 7 памяти находятся на уровне 0 В. В первом испытательном цикле сперва запирают переключатели 9, 10 через линии 11, 12 выбора и отделяют все разрядные линии BL0,...,BL3 и посредством запирания селектирующых переключателей 22 считывают через усилители 6 считывания. Если усилитель 6 считывания регистрирует ток, то в приданной этому усилителю 6 считывания разрядной линии BL0, ...,BL3 имеется пробой туннельного оксида сополидиэлектрика или вызванное, например, металлической частицей прямое короткое замыкание с одной пословной линией WL0,...,WL3. Во втором испытательном цикле за счет приложения нулевого напряжения к фиксирующим схемам 24, 25 и ко второй линии 12 выбора и за счет приложения питающего напряжения Vdd к первой линии 11 выбора все четные разрядные линии BL0, BL2 переключают на 0 В, в то время как нечетные разрядные линии BL1, BL3 становятся свободными от потенциала. При считывании всех разрядных линий BL0,...,BL3 через усилители 6 считывания приданные четным разрядным линиям BL0, BL2 усилители 6 считывания должны регистрировать ток, а приданные нечетным разрядным линиям BL1, BL3 усилители 6 считывания должны регистрировать отсутствие тока. Если в нечетной разрядной линии BL1, BL3 течет ток, то между двумя разрядным линиям BL0,...,BL3 существует низкоомное короткое замыкание. Предпосылкой для обнаружения является то, что транзисторы 9, 10 коммутационного устройства 30 могут переводить на 0 В более одного усилителя 6 считывания. Недостаток испытательного цикла состоит в том, что высокоомное короткое замыкание между двумя разрядным линиям BL0,... , BL3 при некоторых обстоятельствах не вызывает достаточного тока в не питаемой напряжением разрядной линии BL0,...,BL3 и поэтому остается не распознанным. Второй испытательный цикл повторяют тем, что меняют ролями четные и нечетные разрядные линии BL0,...,BL3. В третьем испытательном цикле работающий как селектирующий переключатель транзистор 22 позволяет распознавать высокоомное короткое замыкание. Сперва все фиксирующие схемы 24, 25 подключают к питающему напряжению Vdd и отделяют разрядные линии BL0,...,BL3 за счет запирания селектирующих переключателей 22 от усилителей 6 считывания. Затем все разрядные линии BL0,...,BL3 через выходы фиксирующих схем 24, 25 переводятся на питающее напряжение Vdd. За счет запирания переключателей 9, 10, 22 отсоединяют фиксирующие схемы 24, 25, при этом сохраняется заряд в разрядных линиях BL0,...,BL3. Все фиксирующие схемы 24, 25 подключают к нулевому напряжению. После этого в течение заданного времени активно переводят четные разрядные линии BL0, BL2 на 0 В, в то время как нечетные разрядные линии BL1, BL3 находятся в несвязанном с потенциалом состоянии на положительном уровне V+. В течение этого заданного времени может быть разряжена несвязанная с потенциалом разрядная линия BL1, BL3 через возможно имеющееся короткое замыкание между двумя разрядным линиям BL0,...,BL3. По истечении заданного времени считывают все разрядные линии BL0,...,BL3 с помощью открытых селектирующих переключателей 22 и в течение короткого времени подключаются к нулевому напряжению с помощью фиксирующих схем 24, 25. Это необходимо потому, что иначе разряженная через высокоомное короткое замыкание разрядная линия BL0,...,BL3 в течение короткого времени снова зарядится до положительного уровня V+, и тем самым дефект останется нераспознанным. Результат проверки четных разрядных линий BL0, BL2 и нечетных разрядных линий BL1, BL3 должен соответствовать состояниям наличия тока или отсутствия тока. Если в нечетной разрядной линии BL1, BL3 течет ток, то существует короткое замыкание между двумя разрядным линиям BL0,...,BL3. Испытательный цикл повторяют с измененными ролями четных и нечетных разрядных линий BL0,...,BL3 тем, что на первую линию 11 выбора подают нулевое напряжение, а на вторую линию 12 выбора - питающее напряжение Vdd.

Изобретение относится к устройствам тестирования электронных элементарных схем и групповых линий соединений. Техническим результатом является получение быстрого и информативного результата тестирования. Устройство содержит множество электронных элементарных схем и групповых линий, испытательную схему, устройство обнаружения. 14 з.п. ф-лы, 6 ил.

| Смазочно-охлаждающая среда для обработки резанием титана и его сплавов | 1974 |

|

SU480752A1 |

| RU 2002318 C1, 30.10.1993 | |||

| EP 0228283 A2, 08.07.1987 | |||

| Двумерная самонастраивающаяся следящая система для автоматического определения коэффициентов дифференциального уравнения | 1960 |

|

SU146975A1 |

| Устройство для разгрузки рельсовых транспортных средств | 1973 |

|

SU451595A1 |

| US 4720818 A, 19.01.1988 | |||

| US 5331274 A, 19.07.1994.. | |||

Авторы

Даты

2002-06-10—Публикация

1997-03-26—Подача