Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределенных систем программного управления технологическими процессами, роботами и робототехническими комплексами, а также подсистем логического управления многоуровневых иерархических АСУ и мультипроцессорных систем широкого класса.

Известна распределенная система для программного управления технологическими процессами, содержащая M•N каналов (модулей), каждый из которых включает блок памяти программ, коммутатор адреса, регистры адреса и команд, мультиплексор логических условий, блоки синхронизации и анализа, буферный запоминающий блок, два блока элементов И и элемент И (а.с. 1605212 CCCP, G 05 B 19/18; опубл. 07.11.90, БИ N 41).

Недостатком этой системы является узкая область применения, связанная с отсутствием средств синхронизации групп параллельных участков программ, закрепленных за различными модулями. Отсутствие средств синхронизации во многих случаях является недопустимым, поскольку обусловливает возможность одновременного выполнения несовместимых команд (участков).

Наиболее близкой к предлагаемой сети по технической сущности является дискретная микроконтроллерная сеть, содержащая M•N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, каждый модуль которой включает блок памяти программ, блок анализа, регистр-счетчик адреса, регистр команд, коммутатор адреса, мультиплексор логических условий, блок синхронизации, блок управления синхронизацией параллельных участков, триггер, с первого по четвертый блоки элементов И, с левого по седьмой элементы И, с первого по третий элементы ИЛИ (патент 2110827 РФ, G 05 B 19/18, G 06 F 9/28; опубл. 10.05.98, БИ N 13).

Недостатком известной сети является невысокая оперативность межмодульной передачи управления при запуске групп параллельных участков (микро)программ (алгоритмов управления), закрепленных за различными модулями, обусловленная необходимостью последовательного попарного межмодульного обмена специальными управляющими командами. Данный недостаток ведет к снижению общего быстродействия сети. Другой недостаток указанной сети состоит в значительной сложности образующих ее модулей.

Технической задачей, на решение которой направлено изобретение, является повышение оперативности межмодульной передачи управления в микроконтроллерной сети при запуске групп параллельных участков программ на основе организации параллельного запуска модулей, реализующих эти участки, при одновременном упрощении модулей сети.

Техническая задача решается тем, что в микроконтроллерную сеть, содержащую M•N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, при этом каждый модуль включает блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, причем вход кода операции модуля соединен с первым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом регистра команд, выход метки конца программы которого соединен с управляющими входами коммутатора адреса, выходы кода логического условия и модифицируемого разряда адреса регистра команд подключены к управляющему и первому информационному входам мультиплексора логических условий соответственно, второй информационный вход которого соединен с входом логических условий модуля, первый вход блока синхронизации соединен с входом пуска модуля, дополнительно введен блок элементов НЕ, а каждый модуль дополнительно включает регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, первую и вторую группы элементов И, группу элементов ИЛИ, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, причем выход немодифицируемой части адреса регистра команд в объединении с выходом мультиплексора логических условий подключены к первому входу блока элементов ИЛИ и к информационному входу буферного регистра, выход которого соединен со вторым входом блока элементов ИЛИ, выход которого соединен со вторым информационным входом коммутатора адреса, выход микроопераций регистра команд подключен к выходу микроопераций модуля, вход вектора соответствия модуля соединен с информационным входом регистра вектора соответствия, выходы с первого по n-й которого (где n - максимальное число вершин синхронизации в реализуемых программах) подключены к первым входам элементов ИЛИ группы с первого по n-й соответственно, первый выход номера вершины синхронизации регистра команд соединен с входом первого дешифратора номера вершины синхронизации, выходы с первого по n-й которого соединены со вторыми входами элементов ИЛИ группы с первого по n-й соответственно, выходы которых подключены к первым входам элементов И первой группы с первого по n-й соответственно, входы первой группы входов синхронизации модуля с первого по n-й соединены со вторыми входами элементов И первой группы с первого по n-й соответственно, выходы которых соединены с выходами группы выходов синхронизации модуля с первого по n-й соответственно, второй выход номера вершины синхронизации регистра команд соединен с входом второго дешифратора номера вершины синхронизации, выходы с первого по n-й которого подключены к первым входам элементов И второй группы с первого по n-й соответственно, входы второй группы входов синхронизации модуля с первого по n-й подключены к третьим входам элементов И первой группы с первого по n-й соответственно, выходы которых подключены к вторым входам элементов И второй группы с первого по n-й соответственно, выходы которых соединены с входами первого элемента ИЛИ с первого по n-й соответственно, выход которого соединен с входом синхронизации буферного регистра и с входом первого одновибратора, выход которого подключен к входу сброса регистра команд и ко второму входу блока синхронизации, первый выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к входу синхронизации регистра адреса, выход метки конца участка регистра команд соединен с входом второго одновибратора, выход которого соединен с третьим входом блока синхронизации, второй выход которого подключен к входу сброса буферного регистра и к первому входу третьего элемента ИЛИ, вход настройки модуля соединен со вторым входом второго элемента ИЛИ, с входом синхронизации регистра вектора соответствия, а также с входом элемента задержки, выход которого подключен ко второму входу третьего элемента ИЛИ, выход которого подключен к входу синхронизации регистра команд, группа выходов синхронизации (1.N)-го модуля соединена с входами блока элементов НЕ, выходы которого подключены к первой группе входов синхронизации (i.1)-го модуля,  и ко второй группе входов синхронизации (M. j)-го модуля,

и ко второй группе входов синхронизации (M. j)-го модуля,  группа выходов синхронизации (α,β)-го модуля,

группа выходов синхронизации (α,β)-го модуля,

подключена к первой группе входов синхронизации (α.β+1)-го модуля и ко второй группе входов синхронизации (α-l.β)-го модуля, группа выходов синхронизации (l.β)-го модуля соединена с первой группой входов синхронизации (l.β+l)-го модуля, группа выходов синхронизации (α,N)-го модуля соединена со второй группой входов синхронизации (α-l.N)-го модуля.

подключена к первой группе входов синхронизации (α.β+1)-го модуля и ко второй группе входов синхронизации (α-l.β)-го модуля, группа выходов синхронизации (l.β)-го модуля соединена с первой группой входов синхронизации (l.β+l)-го модуля, группа выходов синхронизации (α,N)-го модуля соединена со второй группой входов синхронизации (α-l.N)-го модуля.

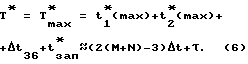

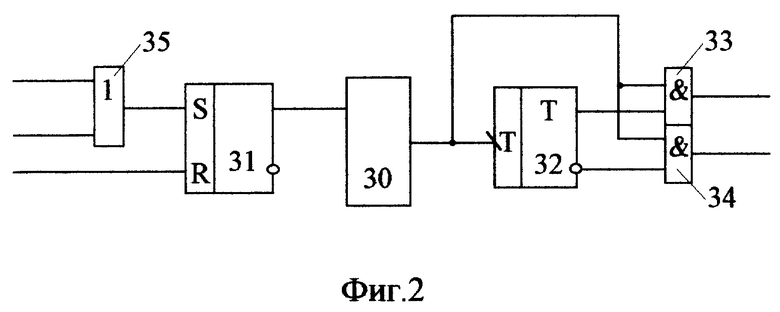

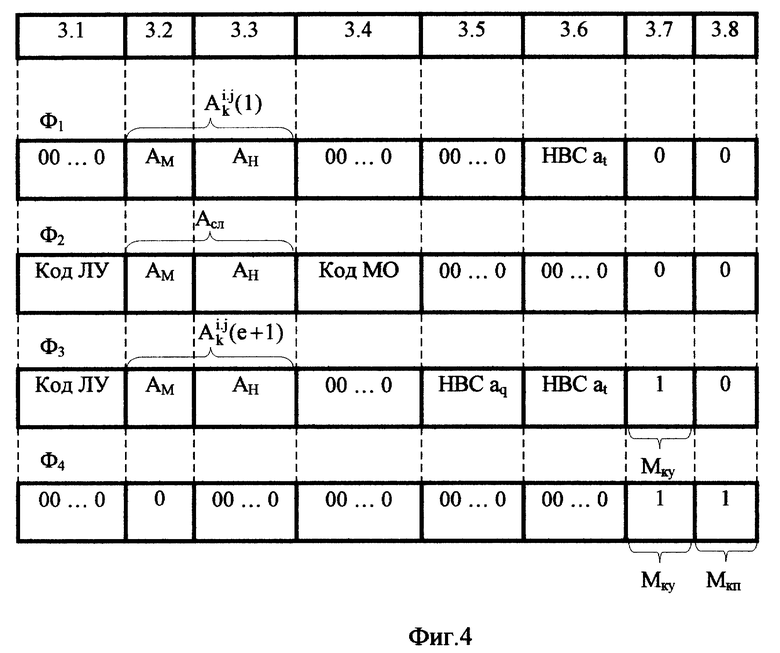

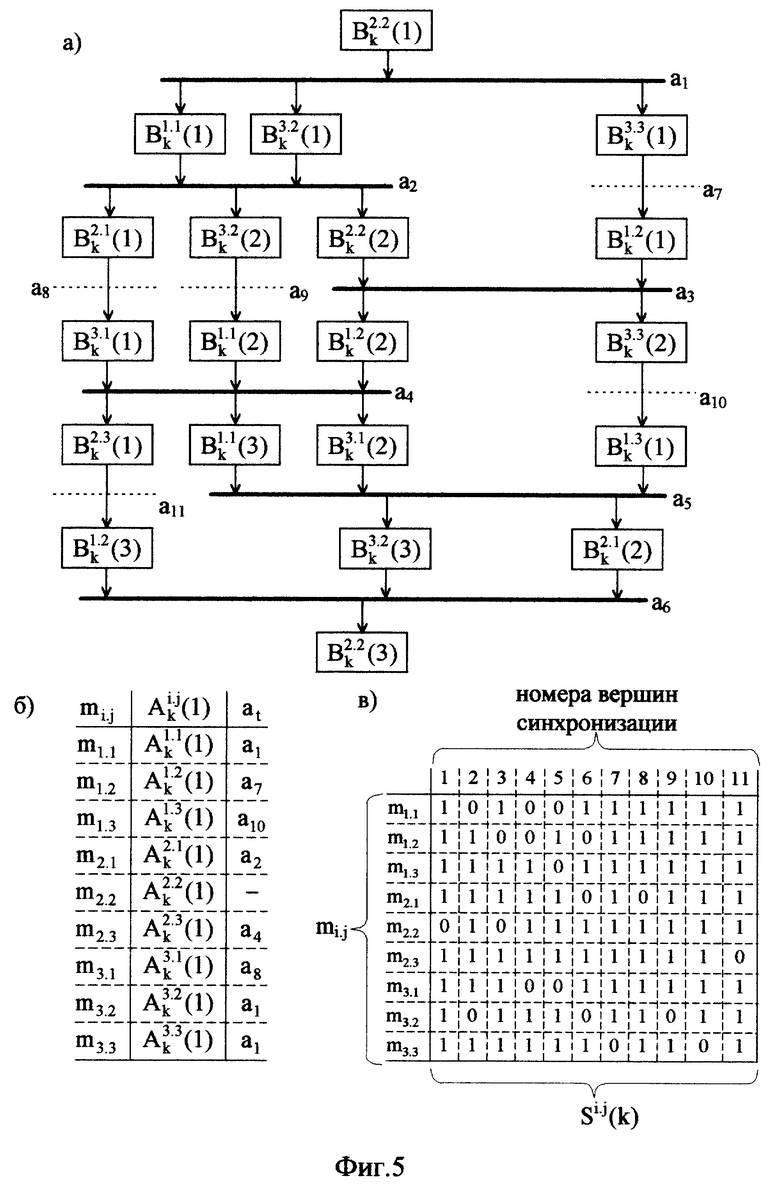

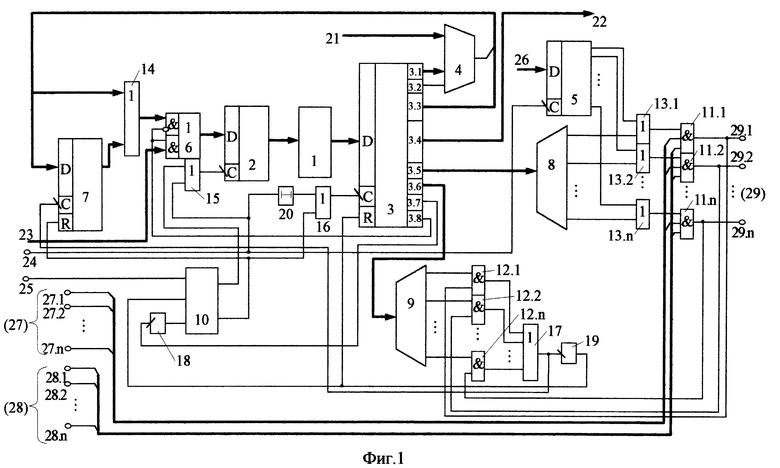

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема модуля микроконтроллерной сети, на фиг. 2 изображена функциональная схема блока синхронизации, на фиг. 3 дана структурная схема микроконтроллерной сети, на фиг. 4 приведены форматы (микро)команд, реализуемые модулем микроконтроллерной сети, на фиг. 5 представлен иллюстративный пример, поясняющий принципы реализации параллельных алгоритмов (программ) в микроконтроллерной сети.

Микроконтроллерная сеть (фиг. 3) содержит M•N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, а также дополнительно введенный блок элементов НЕ 36, причем группа 29 выходов синхронизации (1.N)-го модуля соединена с входами блока элементов НЕ 36, выходы которого подключены к группе 27 входов синхронизации (i.1)-го модуля,  и к группе 28 входов синхронизации (M. j)-го модуля,

и к группе 28 входов синхронизации (M. j)-го модуля,  группа 29 выходов синхронизации (α.β)-го модуля,

группа 29 выходов синхронизации (α.β)-го модуля,

подключена к группе 27 входов синхронизации (α.β+l) -го модуля и к группе 28 входов синхронизации (α-l.β)-го модуля, группа 29 выходов синхронизации (l.β)-го модуля соединена с группой 27 входов синхронизации (l.β+l)-го модуля, группа 29 выходов синхронизации (α.N)-го модуля соединена с группой 28 входов синхронизации (α-l.N)-го модуля.

подключена к группе 27 входов синхронизации (α.β+l) -го модуля и к группе 28 входов синхронизации (α-l.β)-го модуля, группа 29 выходов синхронизации (l.β)-го модуля соединена с группой 27 входов синхронизации (l.β+l)-го модуля, группа 29 выходов синхронизации (α.N)-го модуля соединена с группой 28 входов синхронизации (α-l.N)-го модуля.

Модуль микроконтроллерной сети (фиг. 1) включает блок 1 памяти программ, регистр 2 адреса, регистр 3 команд с выходами 3.1 кода логического условия, 3.2 модифицируемого разряда адреса; 3.3 немодифицируемой части адреса, 3.4 микроопераций, первым выходом 3.5 номера вершины синхронизации, вторым выходом 3.6 номера вершины синхронизации, выходом 3.7 метки конца участка и выходом 3.8 метки конца программы, мультиплексор 4 логических условий, коммутатор 6 адреса, блок 10 синхронизации, первый 17, второй 15 и третий 16 элементы ИЛИ, причем вход 23 кода операции модуля соединен с первым информационным входом коммутатора 6 адреса, выход которого подключен к информационному входу регистра 2 адреса, выход которого подключен к адресному входу блока 1 памяти программ, выход которого соединен с информационным входом регистра 3 команд, выход 3.8 метки конца программы которого соединен с управляющими входами коммутатора 6 адреса, выходы 3.1 кода логического условия и 3.2 модифицируемого разряда адреса регистра 3 команд подключены к управляющему и первому информационному входам мультиплексора 4 логических условий соответственно, второй информационный вход которого соединен с входом 21 логических условий модуля, первый вход блока 10 синхронизации соединен с входом 25 пуска модуля, а также дополнительно введенные регистр 5 вектора соответствия, буферный регистр 7, первый 8 и второй 9 дешифраторы номера вершины синхронизации, первую группу элементов И 11.1-11.n, вторую группу элементов И 12.1-12. n, группу элементов ИЛИ 13.1-13.n, блок элементов ИЛИ 14, первый 19 и второй 18 одновибраторы, элемент 20 задержки, причем выход 3.3 немодифицируемой части адреса регистра 3 команд в объединении с выходом мультиплексора 4 логических условий подключены к первому входу блока элементов ИЛИ 14 и к информационному входу буферного регистра 7, выход которого соединен со вторым входом блока элементов ИЛИ 14, выход которого соединен со вторым информационным входом коммутатора 6 адреса, выход 3.4 микроопераций регистра 3 команд подключен к выходу 22 микроопераций модуля, вход 26 вектора соответствия модуля соединен с информационным входом регистра 5 вектора соответствия, выходы с первого по n-й которого подключены к первым входам элементов ИЛИ 13.1-13.n соответственно, первый выход 3.5 номера вершины синхронизации регистра 3 команд соединен с входом дешифратора 8 номера вершины синхронизации, выходы с первого по n-й которого соединены со вторыми входами элементов ИЛИ 13.1-13.n соответственно, выходы которых подключены к первым входам элементов И 11.1-11. n соответственно, входы первой группы входов синхронизации модуля 27.1-27.n (27) соединены со вторыми входами элементов И 11.1-11.n соответственно, выходы которых соединены с выходами группы выходов синхронизации модуля 29.1-29.n (29) соответственно, второй выход 3.6 номера вершины синхронизации регистра 3 команд соединен с входом дешифратора 9 номера вершины синхронизации, выходы с первого по n-й которого подключены к первым входам элементов И 12.1-12. n соответственно, входы второй группы входов синхронизации модуля 28.1-28. n (28) подключены к третьим входам элементов И 11.1 -11.n соответственно, выходы которых подключены к вторым входам элементов И 12.1 -12.n соответственно, выходы которых соединены с входами элемента ИЛИ 17 с первого по n-й соответственно, выход которого соединен с входом синхронизации буферного регистра 7 и с входом одновибратора 19, выход которого подключен к входу сброса регистра 3 команд и ко второму входу блока 10 синхронизации, первый выход которого соединен с первым входом элемента ИЛИ 15, выход которого подключен к входу синхронизации регистра 2 адреса, выход 3.7 метки конца участка регистра 3 команд соединен с входом одновибратора 18, выход которого соединен с третьим входом блока 10 синхронизации, второй выход которого подключен к входу сброса буферного регистра 7 и к первому входу элемента ИЛИ 16, вход 24 настройки модуля соединен со вторым входом элемента ИЛИ 15, с входом синхронизации регистра 5 вектора соответствия, а также с входом элемента 20 задержки, выход которого подключен ко второму входу элемента ИЛИ 16, выход которого подключен к входу синхронизации регистра 3 команд.

Блок синхронизации (фиг. 2) содержит генератор 30 импульсов, триггер 31 управления, триггер 32, первый 33 и второй 34 элементы И, элемент ИЛИ 35, первый и второй входы которого являются первым и вторым входами блока соответственно, а выход соединен с входом установки триггера 31 управления, вход сброса которого является третьим входом блока, а прямой выход подключен к входу генератора 30 импульсов, выход которого соединен с первыми входами элементов И 33 и 34, а также со счетным входом триггера 32, прямой и инверсный выходы которого подключены ко вторым входам элементов И 33 и 34 соответственно, выходы которых являются первым и вторым выходами блока соответственно.

Общие особенности функциональной организации микроконтроллерной сети состоят в следующем.

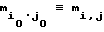

Микроконтроллерная сеть (МКС) формируется из множества однотипных модулей, объединенных в матричную структуру (фиг. 3). Каждый модуль МКС (микроконтроллер) выполняется в виде СБИС с внутренней перепрограммируемой памятью программ и имеет два входных и один выходной информационный каналы, предназначенные для подключения к другим аналогичным модулям и обмена управляющей информацией. Модули сети идентифицируются условными номерами вида i.j, где i и j имеют смысл соответственно номера строки и номера столбца матричной структуры, содержащих данный модуль, "." - символ конкатенации. (В дальнейшем модуль с номером i.j именуется так же, как (i.j)-й модуль или модуль mi.j).

МКС служит для управления сложными объектами, поведение которых описывается комплексом программ и предполагает параллельное протекание и взаимодействие множества процессов. Комплекс программ, реализуемый сетью, разбивается на множество параллельных и последовательных участков, которые распределяются между различными модулями. Каждый модуль реализует некоторое подмножество участков.

В процессе выполнения участков программ модули МКС обрабатывают команды двух типов: операционные и коммуникационные. Операционные команды (эти команды имеют формат Ф2 (фиг. 4)) обеспечивают выдачу управляющих воздействий на объект управления и инициируют исполнение требуемых микроопераций. Коммуникационные команды (формат Ф3 (фиг. 4)) служат для организации взаимодействия и координации различных модулей, включая запуск участков, закрепленных за другими модулями (межмодульную передачу управления), и синхронизацию параллельных участков программ.

Организация межмодульного взаимодействия в предлагаемой МКС принципиально отличается от прототипа. Если в прототипе явно предусматриваются процедуры межмодульной передачи управления и синхронизации параллельных участков, то в рассматриваемой МКС межмодульная передача управления в явном виде отсутствует; выполняется только процедура синхронизации. При этом запуск участков программ, реализуемых различными модулями, происходит при выполнении соответствующих условий синхронизации. Таким условием при запуске участков, непосредственно следующих за подмножеством других (параллельных) участков, является синхронизация (завершение) всех участков данного подмножества. При запуске участков, следующих за единственным участком, в качестве условия выступает завершение этого единственного участка.

Для задания момента активизации некоторого участка Bki.j (e) (где e - порядковый номер данного участка для (i.j)-го модуля, k - номер программы) этому участку ставится в соответствие номер непосредственно предшествующей ему вершины синхронизации at (если активизируемому участку непосредственно предшествует единственный участок программы, то вершина at считается фиктивной). Запуск участка Bki.j (e) происходит после выполнения вершины at, т.е. как только завершаются все непосредственно предшествующие ему участки программы.

В отличие от прототипа, где адреса запускаемых участков (адреса приема управления) передаются от модуля - инициатора запуска, в предлагаемой сети указанные адреса формируются непосредственно модулями, реализующими запускаемые участки (модулями - приемниками управления), в результате самонастройки. Адрес Aki.j (e+1) начала следующего ((e+1)-го) участка, выполняемого (i.j)-м модулем, указывается в заключительной команде предшествующего (e-го) участка программы. Для задания адресов начальных участков модулей {Aki.j(1)} используются команды настройки формата Ф1 (фиг. 4). За каждым модулем сети закрепляется Q таких команд, Q - число программ, реализуемых микроконтроллерной сетью (число программ в реализуемом комплексе). Каждая из Q команд настройки определяет адрес Aki.j(1) первой команды, выполняемой (i.j)-м модулем при реализации k-й программы, т.е. адрес начального участка (i.j)-го модуля. (Если (i. j)-й модуль не участвует в процессе выполнения k-й программы, то команда Ф1 содержит только нули.) Команды настройки Ф1 размещаются в блоке 1 памяти программ (фиг. 1) по начальным адресам от 1 до Q включительно. Команда настройки, а следовательно, и реализуемая программа однозначно задаются адресом при обращении к блоку 1.

Процесс синхронизации параллельных участков в предлагаемой МКС также принципиально отличается от аналогичного процесса в прототипе. В отличие от прототипа, где синхронизация обеспечивается путем подсчета одним из модулей числа сообщений - квитанций завершения параллельных участков, передаваемых другими модулями, в МКС синхронизация осуществляется на основе распространения и опроса отдельных сигналов завышения групп параллельных участков. Каждый такой сигнал распространяется в отдельном канале управления синхронизацией, который соответствует одной из вершин синхронизации (слияния) параллельных участков. Канал управления синхронизацией представляет собой совокупность элементов различных модулей МКС и соответствующих связей, обеспечивающих протекание процесса синхронизации определенной группы параллельных участков. Так, в q-й канал управления синхронизацией войдут элементы И 11.q модулей и q-й элемент блока элементов НЕ 36 с соответствующими им связями (фиг. 1, 3).

Для обеспечения синхронизации произвольных групп параллельных участков за каждым модулем МКС закрепляется вектор, задающий соответствие между множеством вершин синхронизации программы и данным модулем. (i.j)-му модулю сети,

в общем случае соответствует Q различных векторов, каждый из которых отвечает определенной программе. Вектор соответствия для (i.j)-го модуля и k-й программы имеет вид

в общем случае соответствует Q различных векторов, каждый из которых отвечает определенной программе. Вектор соответствия для (i.j)-го модуля и k-й программы имеет вид

Si.j(k)=(s1i.j,s2i.j,..., sni.j),

где

nk - число вершин синхронизации в k-й программе.

Значение компоненты вектора Si.j(k) определяется следующим образом:

sqi.j = 0, если за (i.j)-м модулем закреплен некоторый участок программы, завершающийся в q-й вершине синхронизации;

sqi.j = 1, если (i.j)-й модуль не реализует ни одного участка, завершающегося в q-й вершине синхронизации, или q-я вершина синхронизации отсутствует в k-й программе (что возможно при nk<q).

Синхронизация группы параллельных участков Bq = {B1q, B2q, ...,  }, завершающихся (сходящихся) в q-й вышине синхронизации, осуществляется на основе циклического распространения сигнала dq завершения группы участков в q-м канале управления синхронизацией МКС. Сигнал dq формируется (1.N)-м модулем сети (фиг. 3). В исходном состоянии dq=0 (параллельные участки не завершены) и, следовательно,

}, завершающихся (сходящихся) в q-й вышине синхронизации, осуществляется на основе циклического распространения сигнала dq завершения группы участков в q-м канале управления синхронизацией МКС. Сигнал dq формируется (1.N)-м модулем сети (фиг. 3). В исходном состоянии dq=0 (параллельные участки не завершены) и, следовательно,  = 1.

= 1.

Процесс синхронизации включает две фазы - формирование признака окончания синхронизируемых участков и передачу этого признака всем модулям МКС. Первая из указанных фаз начинается с подачи единичного сигнала  Данный сигнал одновременно подается модулям с номерами 1.1, 2.1, ..., М.1 и М.2, М. 3, . . . , M.N. Далее сигнал

Данный сигнал одновременно подается модулям с номерами 1.1, 2.1, ..., М.1 и М.2, М. 3, . . . , M.N. Далее сигнал  последовательно распространяется через все модули МКС в направлении от (М.1)-го модуля вверх и вправо (по схеме фиг. 3) и в конце концов появляется на выходе (1.N)-го модуля.

последовательно распространяется через все модули МКС в направлении от (М.1)-го модуля вверх и вправо (по схеме фиг. 3) и в конце концов появляется на выходе (1.N)-го модуля.

Распространение сигнала  через некоторый модуль mi.j происходит следующим образом. Если sqi.j = 1, то появление единичных сигналов

через некоторый модуль mi.j происходит следующим образом. Если sqi.j = 1, то появление единичных сигналов  на нижнем и левом входах (i.j)-го модуля обусловливает формирование единичного сигнала

на нижнем и левом входах (i.j)-го модуля обусловливает формирование единичного сигнала  на его выходе. Если sqi.j = 0, то формирование единичного сигнала

на его выходе. Если sqi.j = 0, то формирование единичного сигнала  на выходе (i.j)-го модуля происходит только при условии завершения участка Bfq, реализуемого (i.j)-м модулем.

на выходе (i.j)-го модуля происходит только при условии завершения участка Bfq, реализуемого (i.j)-м модулем.

Состояние участка Bfq определяется значением сигнала - признака gqi.j: gqi.j = 1, если участок Bfq завершен; gqi.j = 0 в противном случае. В случае, если участок Bfq не завершен, на выходе (i.j)-го модуля устанавливается нулевой сигнал. Данный сигнал формирует нулевые сигналы на выходах всех модулей, расположенных выше и/или правее (i.j)-го модуля. На выходе (1.N)-го модуля, соответственно, также будет нулевой сигнал dq = 0. Как только происходит завершение участка Вfq, единичный сигнал  передается на выход (i. j)-го модуля и поступает на (i-1.j)-й и (i.j+1)-й модули.

передается на выход (i. j)-го модуля и поступает на (i-1.j)-й и (i.j+1)-й модули.

После завершения всех параллельных участков группы Bq сигнал  пройдет на входы (1.N)-го модуля и на выходе (1.N)-го модуля, таким образом, будет сформирован сигнал dq = 1, сообщающий об окончании синхронизируемых параллельных участков. На этом первая фаза синхронизации завершается.

пройдет на входы (1.N)-го модуля и на выходе (1.N)-го модуля, таким образом, будет сформирован сигнал dq = 1, сообщающий об окончании синхронизируемых параллельных участков. На этом первая фаза синхронизации завершается.

Вторая фаза синхронизации начинается с инвертирования сигнала dq. Получаемый нулевой сигнал  подается на входы модулей с номерами 1.1, 2.1, ..., M.1 и М.2, М.3, ..., M.N и распространяется через все модули МКС до модуля с номером 1. N. В процессе распространения сигнала происходит запуск всех модулей, ожидающих завершение параллельных участков группы Bq. Признаком запуска модуля является переход сигнала

подается на входы модулей с номерами 1.1, 2.1, ..., M.1 и М.2, М.3, ..., M.N и распространяется через все модули МКС до модуля с номером 1. N. В процессе распространения сигнала происходит запуск всех модулей, ожидающих завершение параллельных участков группы Bq. Признаком запуска модуля является переход сигнала  из единицы в нуль (1 ---> 0). Вторая фаза и процесс синхронизации параллельных участков в целом завершаются после появления нулевого сигнала на выходе (1.N)-го модуля.

из единицы в нуль (1 ---> 0). Вторая фаза и процесс синхронизации параллельных участков в целом завершаются после появления нулевого сигнала на выходе (1.N)-го модуля.

Принципы организации межмодульной передачи управления и синхронизации параллельных участков в предлагаемой МКС поясняются примером реализации параллельного алгоритма управления, представленного на фиг. 5а. Алгоритм включает 20 параллельных и последовательных участков Вki.j(e), принадлежность которых определенному модулю задается верхним индексом i.j. В рассматриваемый алгоритм входят вершины синхронизации a1, a2, ..., a11; вершины a7, a8, a9, a10, a11 (показанные пунктиром) являются фиктивными, поскольку им соответствуют переходы между отдельными участками. МКС содержит 3х3 модулей.

Таблица настройки модулей, определяющая адреса начальных участков Aki.j(1), а также номера вершин синхронизации at, после достижения которых должен быть обеспечен запуск соответствующих модулей, представлена на фиг. 5б. В соответствии с данной таблицей запуск модулей m1.1, m3.2 и m3.3 происходит после выполнения вершины синхронизации a1, т.е. после завершения участка Bk2.2(1), запуск модуля m1.2 осуществляется после достижения вершины синхронизации a7, т.е. после завершения участка Bk3.3(1), и т.д. Модуль m2.2 активизируется непосредственно в момент запуска МКС независимо от состояния других модулей.

Таблица векторов соответствия для рассматриваемого алгоритма показана на фиг. 5в. Согласно данной таблице модуль m1.1 реализует участки, завершающиеся в вершинах синхронизации a2, a4 и a5 (s21.1 = s41.1 = s51.1 = 0), модуль m1.2 - участки, сходящиеся в вершинах a3, a4 и a6(s31.2 = s41.2 = s61.2 = 0) и т.д.

Более подробно процессы синхронизации и запуска параллельных участков описываются при рассмотрении соответствующих режимов функционирования модулей МКС.

Назначение элементов и блоков модуля микроконтроллерной сети (фиг. 1) заключается в следующем.

Блок 1 памяти программ служит для постоянного хранения команд, составляющих параллельные и последовательные участки программ, закрепленные за текущим модулем. Информация (команда) на выходе блока 1 появляется непосредственно после подачи на его адресный вход соответствующего адреса.

Регистр 2 адреса предназначен для временного хранения исполнительного адреса следующей команды.

Регистр 3 команд используется с целью фиксации очередной считываемой из блока 1 команды на время ее обработки.

Мультиплексор 4 логических условий служит для опроса значений логических условий на входе 21 модуля и модификации младшего (модифицируемого) разряда адреса следующей команды в точках ветвления программ.

Регистр 5 вектора соответствия введен с целью хранения вектора Si.j(k) в течение времени исполнения k-й программы.

Коммутатор 6 адреса обеспечивает выбор направления приема исполнительного адреса следующей команды.

Буферный регистр 7 предназначен для временной фиксации исполнительного адреса следующей команды в процессе запуска текущего модуля после завершения некоторой группы параллельных участков программы. Необходимость такой фиксации обусловлена исчезновением информации на выходах 3.2 и 3.3 регистра 3 (вследствие сброса регистра 3 в момент завершения группы параллельных участков) до момента фактической записи адреса следующей команды в регистр 2.

Дешифратор 8 служит для преобразования кода номера вершины синхронизации aq, соответствующей завершаемому участку программы, в унитарный код и формирования сигналов {gqi.j} - признаков состояния (завершения) участков программ.

Дешифратор 9 обеспечивает преобразование кода номера вершины синхронизации at, определяющей момент последующего запуска текущего модуля, в соответствующий унитарный код, а также блокировку/открытие элементов И 12.1 - 12.n.

Блок 10 синхронизации необходим для формирования двух сдвинутых друг относительно друга последовательностей импульсов t1 и t2, синхронизирующих работу различных узлов модуля.

Элементы И 11.1, 11.2, ..., 11.n введены с целью управления распространением сигналов d1, d2, ..., dn с входов 27.1, 28.1; 27.2, 28.2; ...; 27.n, 28. n на выходы 29.1, 29.2, ..., 29.n модуля, а также на входы элементов И 12.1, 12.2, ..., 12.n соответственно.

Элементы И 12.1, 12.2, . .., 12.n служат для управления прохождением сигналов d1, d2, ..., dn с выходов элементов 11.1, 11.2, ..., 11.n соответственно на входы элемента ИЛИ 17.

Элементы ИЛИ 13.1, 13.2, ..., 13.n предназначены для объединения сигналов с первых, вторых и т.д., n-х выходов регистра 5 и дешифратора 8 соответственно.

Блок элементов ИЛИ 14 обеспечивает объединение кодов (адресов) с выхода буферного регистра 7, а также с выхода 3.3 регистра 3 и выхода мультиплексора 4.

Элемент ИЛИ 15 служит для передачи импульсов с первого выхода блока 10 и с входа 24 настройки модуля на вход синхронизации регистра 2.

Элемент ИЛИ 16 обеспечивает передачу импульсов со второго выхода блока 10 и с выхода элемента 20 задержки на вход синхронизации регистра 3.

Элемент ИЛИ 17 используется для объединения сигналов с выходов элементов И 12.1-12.n.

Одновибратор 18 предназначен для формирования импульса, обеспечивающего выключение блока 10 синхронизации.

Одновибратор 19 служит для формирования импульса, обеспечивающего запуск модуля после окончания требуемых групп параллельных участков программ.

Элемент 20 обеспечивает задержку передачи импульса настройки с входа 24 модуля на второй вход элемента ИЛИ 16 на время считывания команды настройки из блока 1.

Блок элементов НЕ 36 (фиг. 3) предназначен для инвертирования сигналов d1, d2, ..., dn с выходов 29.1, 29.2, ..., 29.n (1.N)-го модуля МКС.

Рассмотрим процесс функционирования микроконтроллерной сети подробно.

Первоначально элементы памяти (регистры и триггеры) всех модулей MKC находятся в состоянии логического нуля. Исключение составляют триггеры 32 блоков 10 синхронизации (фиг. 2), а также разряды 3.8 регистров 3 (фиг. 1), установленные в единичное состояние. Исходя из указанного состояния элементов памяти, блоки 10 синхронизации модулей выключены, коммутаторы 6 настроены на прием информации с входов 23, а на всех выходах модулей находятся сигналы логического нуля. Нулевые сигналы с выходов 29.1-29.n (1.N)-го модуля MKC (фиг. 3) формируют единичные сигналы на выходах блока элементов НЕ 36.

Работа сети начинается с настройки модулей на выполнение требуемой программы. Предположим, что эта программа имеет номер k. Настройка (i.j)-го модуля на выполнение k-й программы сводится к установлению адреса Aki.j(1) (адреса первой команды), а также к определению номера вершины синхронизации at, после достижения которой должен осуществляться запуск (i.j)-го модуля.

Процесс настройки начинается с подачи на вход 23 (i.j)-го модуля (фиг. 1) кода операции. Код операции (КОП), представляющий собой код номера выполняемой программы (k), через коммутатор 6 передается на информационный вход регистра 2. Одновременно на вход 24 модуля подается импульс настройки. Указанный импульс через элемент ИЛИ 15 поступает на вход синхронизации регистра 2 и задним фронтом фиксирует КОП в данном регистре. Далее КОП с выхода регистра 2 подается на адресный вход блока 1 и формирует на его выходе команду настройки Ф1 (фиг. 4), соответствующую k-й программе.

В то же самое время импульс настройки через элемент 20 задержки и элемент ИЛИ 16 (фиг. 1) передается на вход синхронизации регистра 3 и задним фронтом производит запись считанной из блока 1 команды в регистр 3. После фиксации команды на выходах 3.2 и 3.3 регистра 3 образуется адрес Aki.j(1), а на выходе 3.6 формируется код номера (t) вершины синхронизации (НВС) at. На остальных выходах регистра 3 устанавливаются нулевые сигналы.

Нулевой сигнал с выхода 3.8 регистра 3 перенастраивает коммутатор 6 на прием информации с выхода блока элементов ИЛИ 14. Поскольку на выходе 3.1 регистра 3 присутствует нулевой код (проверка логических условий в ходе настройки не производится), адрес Aki.j(1) без изменений проходит через блок элементов ИЛИ 14. Далее этот адрес передается через коммутатор 6 и устанавливается на информационном входе регистра 2.

В то же время код номера вершины синхронизации at с выхода 3.6 регистра 3 подается на вход дешифратора 9. В результате на t-м выходе дешифратора 9 образуется единичный сигнал. Этот сигнал открывает элемент И 12.t и тем самым обеспечивает возможность опроса уровня сигнала на выходе элемента И 11. t. (Процесс формирования сигнала на выходе элемента 11.t детально описан ниже при рассмотрении работы МКС в режиме синхронизации параллельных участков. ) Для модуля МКС, который реализует начальный участок k-й программы, задание кода НВС не требуется, поскольку этот модуль активизируется непосредственно в момент запуска МКС независимо от условий синхронизации. На выходе 3.6 регистра 3 рассматриваемого модуля, соответственно, устанавливается нулевой код.

Одновременно с описанными выше действиями производится запись в регистр 5 модуля значения вектора Si.j(k) (устанавливается соответствие между (i. j)-м модулем и множеством вершин синхронизации k-й программы). Вектор Si.j(k) подается на вход 26 модуля и по заднему фронту импульса настройки с входа 24 модуля заносится в регистр 5. На этом процесс настройки (i.j)-го модуля завершается.

Аналогичным образом протекает процесс настройки остальных модулей МКС, причем настройка различных модулей выполняется одновременно. На входы 23 всех модулей подается один и тот же КОП; векторы соответствия для разных модулей в общем случае различны. В результате настройки для каждого модуля определяется момент его запуска при выполнении сетью k-й программы, задается соответствующий адрес (адрес первой команды) и, кроме того, устанавливается подмножество вершин синхронизации k-й программы, в которых завершаются участки, реализуемые модулем.

После завершения настройки осуществляется запуск МКС. Для запуска сети на вход 25 одного из ее модулей подается импульс пуска. Таким модулем является модуль, реализующий начальный участок k-й программы. Допустим, что указанный модуль имеет номер i.j (в примере на фиг. 5 это модуль m2.2). Импульс пуска с входа 25 (i.j)-го модуля передается на первый вход блока 10 синхронизации. Далее этот импульс проходит через элемент ИЛИ 35 (фиг. 2), воздействует на вход установки триггера 31 и переводит этот триггер в единичное состояние. Единичный сигнал с прямого выхода триггера 31 поступает на вход генератора 30 и разрешает формирование на его выходе последовательности импульсов.

Первый импульс с выхода генератора 30 проходит через элемент И 33 на первый выход блока синхронизации (элемент 33 открыт единичным сигналом с прямого выхода триггера 32). По заднему фронту этого же импульса триггер 32 переключается в нулевое состояние. В результате происходит блокировка элемента И 33 и открытие элемента И 34. Второй импульс с выхода генератора 30 через открытый элемент 34 проходит на второй выход блока синхронизации. Задний фронт данного импульса вновь возвращает триггер 32 в исходное (единичное) состояние. Третий импульс снова проходит на первый выход блока синхронизации, а четвертый импульс - на второй выход и т.д. Таким образом, на выходах блока 10 синхронизации начинается генерация двух сдвинутых друг относительно друга последовательностей импульсов синхронизации t1 и t2.

Первый импульс t1 с первого выхода блока 10 синхронизации (фиг. 1) через элемент ИЛИ 15 проходит на вход синхронизации регистра 2 и фиксирует в данном регистре адрес Aki.j(1), поступающий с выхода коммутатора 6. Адрес Aki.j(1) с выхода регистра 2 поступает на адресный вход блока 1 и формирует на его выходе первую команду k-й программы.

Первый импульс t2 со второго выхода блока 10 синхронизации проходит через элемент ИЛИ 16 и, поступая затем на вход синхронизации регистра 3, записывает в этот регистр считанную из блока 1

команду. Одновременно этот же импульс подается на вход сброса буферного регистра 7 и подтверждает его нулевое состояние. Таким образом, (i.j)-й модуль и микроконтроллерная сеть в целом начинают исполнение k-й программы.

Дальнейшее функционирование МКС будем рассматривать в предположении, что (i.j)-й модуль выполняет некоторый (в общем случае не начальный) участок k-й программы, например участок Bfq, завершающийся вершиной синхронизации aq. Кроме того, будем считать, что одновременно с (i.j)-м модулем могут функционировать и некоторые другие модули МКС (остальные модули находятся в пассивном состоянии или в состоянии ожидания).

В процессе выполнения участка Bfq (i.j)-й модуль может обрабатывать команды форматов Ф2, Ф3 или Ф4 (фиг. 4). Обработка команды формата Ф2 соответствует режиму собственно выполнения участка программы (режим A), команда Ф3 определяет режим завершения участка программы (режим B), а команда Ф4 задает режим завершения программы в целом (режим C). Рассмотрим работу модуля в каждом из названных режимов.

Режим A. Записанная в регистр 3 команда имеет формат Ф2 (фиг. 4). В этом случае на выходе 3.4 регистра 3 (фиг. 1) формируется код микроопераций (МО), на выходах 3.2 и 3.3 образуется адрес следующей команды Aсл (на выходе 3.3 - немодифицируемая часть, а на выходе 3.2 - модифицируемый разряд адреса следующей команды, изменяемый в точках ветвления программ), на выходе 3.1 устанавливается код опрашиваемого логического условия (ЛУ), а на выходах 3.5-3.8 появляются сигналы логического нуля.

Код МО с выхода 3.4 регистра 3 передается на выход 22 модуля и, поступая далее на вход объекта управления, инициирует выполнение требуемых микроопераций. Нулевые сигналы с выходов 3.5 и 3.6 регистра 3 воздействуют на входы дешифраторов 8 и 9 соответственно и формируют на всех их выходах нулевые сигналы. Нулевой сигнал с выхода 3.8 регистра 3 поступает на управляющие входы коммутатора 6 и настраивает его на прием адреса следующей команды с выхода блока элементов ИЛИ 14.

Одновременно с описанными действиями происходит формирование исполнительного адреса следующей команды. Указанный адрес образуется из адреса следующей команды Aсл путем замещения его модифицируемого (младшего) разряда значением опрашиваемого ЛУ. Новое значение младшего разряда формируется на выходе мультиплексора 4. Процесс формирования этого значения протекает следующим образом. Модифицируемый разряд (Aм) адреса Aсл с выхода 3.2 регистра 3 подается на первый информационный вход мультиплексора 4, а код ЛУ с выхода 3.1 поступает на управляющий вход мультиплексора 4. Если код ЛУ отличен от нулевого, то на выход мультиплексора 4 передается значение соответствующего ЛУ с входа 21 модуля. Если же код ЛУ нулевой, то на выход мультиплексора 4 поступает значение Ам с выхода 3.2 регистра 3. Значение с выхода мультиплексора 4 в объединении с немодифицируемой (старшей) частью адреса следующей команды (Aн) с выхода 3.3 регистра 3 образует исполнительный адрес следующей команды Aсл*.

Адрес Aсл* через блок элементов ИЛИ 14 и открытый коммутатор 6 проходит на информационный вход регистра 2. Очередной импульс синхронизации t1 с первого выхода блока 10 синхронизации фиксирует адрес Aсл* в регистре 2. Адрес Aсл* с выхода регистра 2 поступает на адресный вход блока 1 и обеспечивает считывание из блока 1 очередной команды k-й программы. Следующий импульс t2 со второго выхода блока 10 синхронизации через элемент ИЛИ 16 подается на вход синхронизации регистра 3 и записывает в этот регистр считанную команду.

На этом работа (i.j)-го модуля в режиме A заканчивается. Считанная команда снова может иметь формат Ф2 либо может быть командой формата Ф3 или Ф4.

Режим B. Записанная в регистр 3 команда имеет формат Ф3 (фиг. 4). В этом случае (i.j)-й модуль завершает выполнение некоторого участка Bfq, производит самонастройку на реализацию очередного участка k-й программы и переходит в состояние ожидания. В ходе самонастройки (i.j)-й модуль устанавливает адрес Aki.j(e+1) начала очередного ((e+1)-го) участка Bht (здесь e - порядковый номер участка Bfq для (i.j)-го модуля) и фиксирует номер (t) вершины синхронизации at (после достижения которой должен осуществляться запуск (i. j)-го модуля).

На выходе 3.7 регистра 3 появляется единичная метка конца участка программы (Mку), индицирующая формат считанной команды, на выходах 3.2 и 3.3 регистра 3 формируется адрес Aki.j(e+1), на выходе 3.1 образуется код ЛУ, а на выходах 3.4 и 3.8 устанавливаются сигналы логического нуля. В то же время на выходах 3.5 и 3.6 регистра 3 формируются номера (коды номеров) вершин синхронизации: на выходе 3.5 - номер (q) вершины синхронизации aq, завершающей выполненный модулем участок Bfq; на выходе 3.6 - номер (t) вершины синхронизации at, определяющей момент очередного запуска (i.j)-го модуля (допустимым является случай, когда t=q).

В примере на фиг. 5 после выполнения участка Bk2.2(1) на выходе 3,5 регистра 3 модуля m2.2 будет сформирован номер вершины a1, на выходе 3.6 будет установлен номер вершины a2, за которой следует очередной участок Bk2.2(2), выполняемый модулем m2.2. Адрес начала этого участка Ak2.2(2) будет зафиксирован на выходах 3.2 и 3.3 регистра 3. После завершения участка Bk2.2(2) на выходе 3.5 регистра 3 модуля m2.2 будет установлен НВС a3, а на выходе 3.6 - НВС a6, за которой следует очередной участок модуля m2.2 - участок Bki.j(3).

Аналогичным образом происходит самонастройка других модулей.

Код номера вершины синхронизации aq с выхода 3.5 регистра 3 поступает на вход дешифратора 8 и возбуждает единичный сигнал gqi.j - признак завершения участка Bfq - на его q-м выходе. Единичный сигнал gqi.j проходит через элемент ИЛИ 13.q (на первом входе элемента 13.q присутствует сигнал sqi.j = 0 с q-го выхода регистра 5). Далее сигнал gqi.j поступает на первый вход элемента И 11.q и тем самым индицирует окончание участка Bfq. В свою очередь, код НВС at с выхода 3.6 регистра 3 подается на вход дешифратора 9 и возбуждает сигнал логической единицы на его t-м выходе. Единичный сигнал с t-го выхода дешифратора 9 открывает элемент И 12.t, обеспечивая возможность последующего запуска (i.j)-го модуля при завершении участков, сходящихся в вершине синхронизации at.

В то же время нулевой сигнал с выхода 3.8 регистра 3 настраивает коммутатор 6 на прием информации с выхода блока элементов ИЛИ 14. Положительный перепад уровня сигнала (0 ---> 1), возникающий на выходе 3.7 регистра 3, воздействует на одновибратор 18 и формирует на его выходе импульс. Данный импульс поступает на третий вход блока 10 синхронизации и, проходя затем на вход сброса триггера 31 (фиг.2), переключает этот триггер в состояние логического нуля. Нулевой сигнал с прямого выхода триггера 31 выключает генератор 30 и тем самым приостанавливает процесс формирования импульсов синхронизации t1 и t2 на выходах блока 10 синхронизации. Таким образом, процесс считывания команд из блока 1 временно прекращается (модуль переходит в состояние ожидания).

Одновременно с описанными действиями происходит формирование исполнительного адреса следующей команды (адреса, с которого произойдет фактический запуск (i.j)-го модуля после достижения t-й вершины синхронизации). Указанный адрес образуется из адреса Aki.j(e+1) путем модификации его младшего разряда (Aм) значением логического условия с входа 21 модуля (фиг. 1). Процесс формирования исполнительного адреса протекает так же, как и при работе модуля в режиме A (см. выше). Полученный исполнительный адрес (обозначим его как Aki.j(e+1)*) поступает на информационный вход буферного регистра 7, а также через блок элементов ИЛИ 14 и коммутатор 6 проходит на информационный вход регистра 2.

На этом работа модуля в режиме В заканчивается. Аналогичным образом происходит завершение других участков k-й программы, в том числе и участков {Вzq}, z≠f, сходящихся в q-й вершине синхронизации.

Рассмотрим работу МКС в режиме синхронизации группы параллельных участков, а также процесс запуска модулей при синхронизации. Для определенности будем рассматривать конкретную группу участков, например группу участков Вq = {В1q, В2q, ...,  }, сходящихся в вершине синхронизации aq. Будем считать, что участки В1q, В2q, ...,

}, сходящихся в вершине синхронизации aq. Будем считать, что участки В1q, В2q, ...,  распределены между модулями МКС произвольным образом.

распределены между модулями МКС произвольным образом.

Процесс синхронизации параллельных участков в МКС происходит циклически. Очередной цикл синхронизации начинается с момента появления нулевого сигнала dq (признака завершения группы параллельных участков Bq) на выходе 29.q (1. N)-го модуля. (В исходном состоянии, т.е. до начала выполнения k-й программы, все сигналы d1, d2, ...,  будут нулевыми, поскольку в каждой группе В1, В2, . . .,

будут нулевыми, поскольку в каждой группе В1, В2, . . .,  имеется хотя бы один незавершенный участок. Уровень сигналов dz, z = nk+1, nk+2, ..., n, при выполнении k-й программы несуществен. ) Сигнал dq поступает на q-й вход блока элементов НЕ 36 (фиг. 3) и формирует на q-м выходе этого блока сигнал логической единицы

имеется хотя бы один незавершенный участок. Уровень сигналов dz, z = nk+1, nk+2, ..., n, при выполнении k-й программы несуществен. ) Сигнал dq поступает на q-й вход блока элементов НЕ 36 (фиг. 3) и формирует на q-м выходе этого блока сигнал логической единицы  С появлением сигнала

С появлением сигнала  начинается первая фаза синхронизации - формирование признака окончания участков группы Bq.

начинается первая фаза синхронизации - формирование признака окончания участков группы Bq.

Единичный сигнал с q-го выхода блока элементов НЕ 36 одновременно подается на входы 27.q модулей МКС с (1.1)-го по (M.1)-й (модулей первого столбца) и на входы 28.q модулей МКС с (M.1)-го по (M.N)-й (модулей M-й строки). Единичные сигналы с входов 27.q модулей с (1.1)-го по (M.1)-й поступают на вторые входы элементов И 11.q (фиг. 1, 3), а единичные сигналы с входов 28.q модулей с (M.1)-го по (M.N)-й передаются на третьи входы элементов И 11.q. Поскольку на входах 28.q модулей с (1.1)-го по (M-1.1)-й и на входах 27.q модулей с (M.2)-го по (M.N)-й первоначально присутствуют сигналы логического нуля (обусловленные нулевым уровнем сигнала на выходе 29.q (M.1)-го модуля), на выходах их элементов 11.q также сохраняются нулевые сигналы независимо от уровня сигнала на выходах элементов ИЛИ 13.q. В то же время, поскольку на входах 27.q и 28.q (M.1)-го модуля устанавливаются единичные сигналы, элемент И 11.q этого модуля открывается и уровень сигнала на его выходе определяется только сигналом с выхода элемента ИЛИ 13.q. Последний, в свою очередь, зависит от сигнала sqM.1 с q-го выхода регистра 5 и сигнала gqM.1 с q-го выхода дешифратора 8.

Если sqM.1 = 1, т.е. (M.1)-й модуль не реализует участков из группы синхронизируемых участков Bq (и, соответственно, не должен оказывать влияние на процесс синхронизации), то на выходе элемента ИЛИ 13.q образуется единичный сигнал. Этот сигнал поступает на первый вход элемента И 11.q и, так как на других входах данного элемента также находятся единичные сигналы, формирует единичный сигнал на его выходе (т.е. фактически ретранслирует сигналы  с входов 27.q и 28.q на выход элемента 11.q).

с входов 27.q и 28.q на выход элемента 11.q).

Если sqM.1 = 0, т.е. за (M.1)-м модулем закреплен некоторый участок Вwq группы Bq, то сигнал на выходе элемента 13.q определяется сигналом gqM.1 с q-го выхода дешифратора 8 (формирование сигнала gqM.1 описано выше на примере (i. j)-го модуля). Если участок Вwq завершен, то gqM.1 = 1 и на выходе элемента 13.q появляется единичный сигнал. Соответственно, единичный сигнал будет и на выходе элемента 11.q (сигналы  ретранслируются на выход элемента 11.q). Однако в случае если участок Вwq не завершен, то gqM.1 = 0 и на выходе элемента 13.q образуется нулевой сигнал. Этот сигнал блокирует элемент И 11.q и формирует на его выходе нулевой сигнал (передача сигналов

ретранслируются на выход элемента 11.q). Однако в случае если участок Вwq не завершен, то gqM.1 = 0 и на выходе элемента 13.q образуется нулевой сигнал. Этот сигнал блокирует элемент И 11.q и формирует на его выходе нулевой сигнал (передача сигналов  на выход элемента 11.q заблокирована). Нулевой сигнал на выходе элемента 11. q сохраняется до тех пор, пока не будет завершен участок Вwq.

на выход элемента 11.q заблокирована). Нулевой сигнал на выходе элемента 11. q сохраняется до тех пор, пока не будет завершен участок Вwq.

Сигнал с выхода элемента 11.q поступает на выход 29.q (M.1)-го модуля и далее распространяется на вход 27.q (М.2)-го модуля (вправо, фиг. 3) и на вход 28.q (М-1.1)-го модуля (вверх). Если данный сигнал нулевой, то он блокирует элементы И 11. q (М.2)-го и (М-1.1)-го модулей (фиг. 1, 3) и подтверждает тем самым нулевой уровень сигнала на выходах 29.q этих модулей. Нулевые сигналы с выходов 29.q (М.2)-го и (M-1.1)-го модулей, в свою очередь, обусловливают образование сигналов логического нуля на выходах 29.q (М-1.2)-го, (M. 3)-го и (М-2.1)-го модулей. Нулевые сигналы с выходов 29.q (М-1.2)-го, (М.3)-го и (М-2.1)-го модулей формируют нулевые сигналы на выходах 29.q (М-2.2)-го, (М-1.3)-го, (М.4)-го и (М-3.1)-го модулей и т.д. И, наконец, нулевые сигналы с выходов 29.q (1.N-1)-го и (2.N)-го модулей подтверждают нулевой сигнал dq на выходе 29.q (1.N)-го модуля.

Если сигнал на выходе 29.q (М.1)-го модуля единичный, то на втором и третьем входах элементов И 11.q (М.2)-го и (М-1.1)-го модулей происходит совпадение единиц (на второй вход элемента 11.q (М- 1.1)-го модуля и на третий вход элемента 11. q (М.2)-го модуля подается единичный сигнал  с q-го выхода блока элементов НЕ 36). Теперь уровень сигнала на выходах указанных элементов определяется сигналами с выходов элементов ИЛИ 13.q. Формирование сигнала на выходах элементов 13.q (М.2)-го и (М-1.1)-го модулей происходит так же, как и в случае (М.1)-го модуля. Если sqM.2 = 1 или sqM.2 = 0 и gqM.2 = 1, sqM-1.1 = 1 или sqM-1.1 = 0 и gqM-1.1 = 1, то эти сигналы единичные. Если же sqM.2 = 0 и gqM.2 = 0, sqM-1.1 = 0 и gqM-1.1 = 0, то указанные сигналы нулевые.

с q-го выхода блока элементов НЕ 36). Теперь уровень сигнала на выходах указанных элементов определяется сигналами с выходов элементов ИЛИ 13.q. Формирование сигнала на выходах элементов 13.q (М.2)-го и (М-1.1)-го модулей происходит так же, как и в случае (М.1)-го модуля. Если sqM.2 = 1 или sqM.2 = 0 и gqM.2 = 1, sqM-1.1 = 1 или sqM-1.1 = 0 и gqM-1.1 = 1, то эти сигналы единичные. Если же sqM.2 = 0 и gqM.2 = 0, sqM-1.1 = 0 и gqM-1.1 = 0, то указанные сигналы нулевые.

Сигналы с выходов элементов 11.q (М-1.1)-го и (М.2)-го модулей поступают на выходы 29. q этих модулей и далее распространяются на входы 28.q (М-2.1)-го, 27.q (М-1.2)-го модулей и на входы 28.q (М- 1.2)-го, 27.q (М.3)-го модулей соответственно.

Аналогичным образом происходит формирование сигналов на выходах 29,q (М-2.1)-го, (М-1.2)-го и (М.3)-го модулей, затем точно так же формируются сигналы на выходах 29.q (М-1.3)-го, (М-2.2)-го, (М-3.1)-го и (М.4)-го модулей и т.д. В конце концов образуется сигнал dq на выходе 29.q (1.N)-го модуля. Как следует из вышесказанного, значение этого сигнала будет оставаться нулевым до тех пор, пока хотя бы один из оставшихся модулей, например (i. j)-й модуль, имеет нулевой сигнал на выходе 29.q, либо sq1.N = 0 и gq1.N = 0, т.е. пока в группе Bq имеется по меньшей мере один незавершенный участок. Нулевой сигнал с выхода 29.q (i.j)-го модуля будет блокировать все остальные модули, расположенные выше и/или правее него (по схеме фиг. 3). На выходах 29. q этих модулей будет нулевой уровень сигнала независимо от сигналов на выходах их элементов 13.q. Как только все участки группы Bq будут завершены, на выходах 29. q всех модулей сети появятся единичные сигналы. Соответственно, единичное значение примет и сигнал dq на выходе 29.q (1.N)-го модуля.

В ходе реализации первой фазы синхронизации наряду с распространением сигнала  обеспечивается подготовка модулей к последующему запуску. Для этого сигнал с выхода элемента 11.q (i.j)-го модуля передается на второй вход элемента И 12.q. В случае если данный сигнал нулевой, то он закрывает элемент 12.q. Если же этот сигнал единичный, то он открывает элемент 12.q и разрешает прохождение сигнала с q-го выхода дешифратора 9 на его выход. Если на q-м выходе дешифратора 9 находится единичный сигнал (что определяет необходимость запуска (i.j)-го модуля после достижения q-й вершины синхронизации), то на выходе элемента 12.q, а значит, и на выходе элемента ИЛИ 17 формируется единичный сигнал. Тем самым обеспечивается подготовка (i.j)-го модуля к последующему запуску. Запуск модуля произойдет в момент перехода сигнала на выходе элемента 17 из единицы в нуль (процесс запуска подробно рассмотрен ниже).

обеспечивается подготовка модулей к последующему запуску. Для этого сигнал с выхода элемента 11.q (i.j)-го модуля передается на второй вход элемента И 12.q. В случае если данный сигнал нулевой, то он закрывает элемент 12.q. Если же этот сигнал единичный, то он открывает элемент 12.q и разрешает прохождение сигнала с q-го выхода дешифратора 9 на его выход. Если на q-м выходе дешифратора 9 находится единичный сигнал (что определяет необходимость запуска (i.j)-го модуля после достижения q-й вершины синхронизации), то на выходе элемента 12.q, а значит, и на выходе элемента ИЛИ 17 формируется единичный сигнал. Тем самым обеспечивается подготовка (i.j)-го модуля к последующему запуску. Запуск модуля произойдет в момент перехода сигнала на выходе элемента 17 из единицы в нуль (процесс запуска подробно рассмотрен ниже).

С появлением единичного сигнала dq на выходе 29.q (1.N)-го модуля первая фаза синхронизации заканчивается и осуществляется переход ко второй фазе.

Единичный сигнал dq с выхода 29.q (1.N)-го модуля поступает на q-й вход блока элементов НЕ 36, в результате чего на q-м выходе указанного блока возникает отрицательный перепад уровня сигнала (1 ---> 0). Данный перепад (являющийся признаком запуска модулей, ожидающих завершение участков группы Bq) одновременно передается на входы 27.q модулей МКС с (1.1)-го по (М.1)-й (первого столбца) и на входы 28.q модулей МКС с (М.1)-го по (М.N)-й (М-й строки). В результате на выходах элементов И 11.q этих модулей также возникает отрицательный перепад уровня сигнала. С выходов 29.q модулей с (1.1)-го по (М-1.1)-й и с (М.2)-го по (М.N)-й перепад уровня сигнала через соответствующие элементы 11.q распространяется на выходы 29.q модулей с (1.2)-го по (М-1.2)-й и с (М-1.3)-го по (М-1.N)-й. Далее аналогичным образом происходит распространение перепада уровня сигнала на выходы 29.q модулей с (1.3)-го по (М-2.3)-й и с (М-2.4)-го по (M-2.N)-й и т.д. В конце концов отрицательный перепад уровня сигнала достигнет один из входов - 27.q или 28.q - (1.N)-го модуля.

В результате на выходе 29.q (1.N)-го модуля будет установлен нулевой сигнал dq.

С появлением нулевого сигнала dq завершается вторая фаза синхронизации и очередной цикл синхронизации параллельных участков в целом. Сразу после образования нулевого сигнала на выходе 29.q (1.N)-го модуля начинается следующий цикл синхронизации.

В процессе распространения перепада уровня сигнала через МКС происходит запуск модулей, ожидающих завершение группы участков Bq. Эти модули реализуют участки k-й программы, непосредственно следующие за участками группы Bq. Например, если Bq = B4 = {Bk3.1(1), Вk1.1(2), Вk1.2(2)} (фиг. 5а), то такими участками будут Вk2.3(1), Вk1.1(3) и Вk3.1(2); соответственно, будет осуществляться запуск модулей m2.3, m1.1 и m3.1.

Запуск модулей МКС рассмотрим на примере функционирования некоторого модуля с номером (i.j).

Если активизация (i.j)-го модуля после окончания группы участков Bq не требуется, то на выходе 3.6 регистра 3 данного модуля присутствует код, отличный от кода НВС aq (этот код может быть нулевым, если (i.j)-й модуль выполняет некоторый участок k-й программы, и ненулевым, если (i.j)-й модуль завершил выполнение некоторого участка, сходящегося в μ-й вершине синхронизации, μ≠q). Соответственно, на q-м выходе дешифратора 9 находится нулевой сигнал. Этот сигнал блокирует элемент И 12.q и поэтому появление перепада уровня сигнала на выходе элемента И 11.q никак не влияет на уровень сигнала на выходе элемента ИЛИ 17. Запуск (i.j)-го модуля не производится.

Если (i. j)-й модуль должен быть активизирован после окончания группы участков Bq (т.е. по достижении вершины синхронизации aq), то на выходе 3.6 регистра 3 этого модуля находится код НВС aq (установленный при работе модуля в режиме В). Соответственно, на q-м выходе дешифратора 9 присутствует сигнал логической единицы, который открывает элемент И 12.q. Поскольку на выходе элемента И 11.q также установлен единичный сигнал, единичный сигнал будет и на выходе элемента 12.q, а значит, и на выходе элемента ИЛИ 17.

Как только на выходе элемента И 11.q возникает отрицательный перепад уровня сигнала, сигнал на выходе элемента 12.q переходит из единицы в нуль и на выходе элемента 17 также формируется отрицательный перепад уровня сигнала. Данный перепад воздействует на одновибратор 19 и возбуждает на его выходе импульс пуска модуля. Одновременно этот же перепад распространяется на вход синхронизации буферного регистра 7 и фиксирует в данном регистре адрес запуска (i.j)-го модуля Aki.j(e+1)*, сформированный при завершении (i. j)-м модулем e-го участка k-й программы (см. режим В). Адрес с выхода регистра 7 подтверждает информацию на выходе блока элементов ИЛИ 14.

В тот же момент импульс с выхода одновибратора 19 поступает на второй вход блока 10 синхронизации и, проходя далее через элемент ИЛИ 35 (фиг. 2) на вход установки триггера 31, переключает данный триггер в единичное состояние. Единичный сигнал, образующийся на прямом выходе триггера 31, включает генератор 30. Таким образом, на выходах блока 10 синхронизации начинается формирование импульсов синхронизации t1 и t2.

Одновременно импульс с выхода одновибратора 19 (фиг. 1) подается на вход сброса регистра 3 и устанавливает его в нулевое состояние. На всех выходах регистра 3 образуются нулевые сигналы. В результате на всех выходах дешифраторов 8 и 9 формируется нулевой уровень сигнала. Адресный код на первом входе блока элементов ИЛИ 14 также становится нулевым. Однако на выходе блока элементов ИЛИ 14 по-прежнему сохраняется адрес Aki.j(e+1)*, поступающий с выхода регистра 7. Соответственно, указанный адрес сохраняется и на информационном входе регистра 2.

Сброс регистра 3 непосредственно после завершения участков группы Bq необходим для того, чтобы исключить повторный запуск (i.j)-го модуля в результате очередного цикла синхронизации. Это связано с тем, что очередной цикл синхронизации начинается сразу после окончания предшествующего цикла и на выходах элементов 13.q всех модулей, реализующих участки группы Bq, все еще могут находиться единичные сигналы. Установка на выходах элементов 13.q нулевых сигналов производится только в момент запуска этих модулей.

Далее первый импульс t1 с первого выхода блока 10 синхронизации через элемент ИЛИ 15 поступает на вход синхронизации регистра 2 и задним фронтом записывает в него адрес Aki.j(e+1)*. Адрес с выхода регистра 2 подается на адресный вход блока 1 и обеспечивает считывание первой команды (e+1)-го участка. Первый импульс t2 со второго выхода блока 10 синхронизации сбрасывает буферный регистр 7 и, поступая одновременно через элемент ИЛИ 16 на вход синхронизации регистра 3, фиксирует в этом регистре считанную из блока 1 команду. Таким образом, (i.j)-й модуль приступает к выполнению (e+1)-го участка k-й программы. Записанная в регистр 3 команда может иметь либо формат Ф2, либо формат Ф3, либо формат Ф4 (фиг. 4). Соответственно, (i.j)-й модуль может перейти в один из трех возможных режимов - A, B или C.

Режим C. В этот режим модуль переходит после записи в регистр 3 команды формата Ф4 (фиг. 4). Работа модуля в режиме C сводится к индикации завершения k-й программы и переходу в пассивное состояние. На выходе 3.8 регистра 3 (фиг. 1) образуется единичный сигнал - метка конца программы (Мкп), на выходе 3.7 как и в режиме В появляется единичная метка конца участка Мку. На всех остальных выходах регистра 3 формируется нулевой уровень сигнала.

Нулевые сигналы с выходов 3.5 и 3.6 регистра 3 формируют нулевой уровень сигнала на выходах дешифраторов 8 и 9. Единичная метка Мкп с выхода 3.8 регистра 3 подается на управляющие входы коммутатора 6 и настраивает его на прием очередного КОП с входа 23 модуля.

Одновременно переход сигнала на выходе 3.7 регистра 3 из нуля в единицу возбуждает импульс на выходе одновибратора 18. Этот импульс поступает на третий вход блока 10 синхронизации, переводит триггер 31 (фиг. 2) в нулевое состояние и тем самым запрещает формирование импульсов синхронизации t1 и t2 на выходах блока 10 синхронизации (фиг. 1). Считывание команд из блока 1 прекращается.

Аналогичным образом завершается функционирование и других модулей МКС. Выполнение k-й программы в целом заканчивается после перехода в пассивное состояние последнего из модулей. После этого сеть может переходить к выполнению очередной программы.

Оценим преимущества предлагаемого технического решения перед прототипом.

Первоначально будем проводить оценку с точки зрения оперативности процесса межмодульной передачи управления при запуске групп параллельных участков (при анализе прототипа нумерация осуществляется в соответствии с описанием прототипа).

В прототипе межмодульная передача управления предусматривает обмен сообщениями, содержащими адреса передачи управления, и может осуществляться двумя способами.

Способ 1. Модуль - инициатор передачи управления (пусть этот модуль имеет номер i.j) последовательно считывает несколько коммуникационных команд (в прототипе это команды формата C или B), каждая из которых обеспечивает формирование и выдачу одного сообщения и, соответственно, запуск одного из требуемых параллельных участков.

Способ 2. Модуль mi.j считывает коммуникационную команду C (или B, если (i. j)-й модуль должен перейти в пассивное состояние), которая обеспечивает запуск параллельного участка, закрепленного, например, за модулем с номером i1.j1.(i1.j1)-й модуль, в свою очередь, после запуска также считывает команду C и производит запуск следующего из требуемых параллельных участков, реализуемого (i2. j2)-м модулем. Далее (i2.j2)-й модуль аналогичным образом активизирует очередной параллельный участок, закрепленный за модулем с номером i3.j3. В конце концов будут активизированы все параллельные участки.

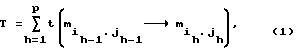

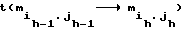

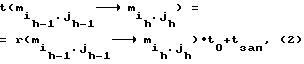

Независимо от используемого способа время межмодульной передачи управления при запуске группы из p параллельных участков (т.е. промежуток между моментом считывания первой коммуникационной команды и моментом запуска последнего, p-го участка) определяется как

где  - время передачи сообщения от модуля

- время передачи сообщения от модуля  модулю

модулю  ;

;

h - порядковый номер запускаемого участка;

для первого способа справедливо равенство  ,

,  поскольку все сообщения передаются (i.j)-м модулем;

поскольку все сообщения передаются (i.j)-м модулем;

для второго способа  .

.

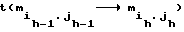

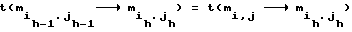

Время  , в свою очередь, зависит от расстояния

, в свою очередь, зависит от расстояния  между модулями

между модулями  и

и  и среднего времени t0 передачи сообщения между соседними модулями и в общем случае

и среднего времени t0 передачи сообщения между соседними модулями и в общем случае

где tзап - время запуска модуля  (промежуток времени от момента поступления сообщения на вход 28 или 29 (ih.jh)-го модуля до момента фиксации первой команды запускаемого участка в регистре 5 команд).

(промежуток времени от момента поступления сообщения на вход 28 или 29 (ih.jh)-го модуля до момента фиксации первой команды запускаемого участка в регистре 5 команд).

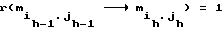

Наименьшее значение T достигается тогда, когда модули  являются соседними (смежными) и, соответственно,

являются соседними (смежными) и, соответственно,  ,

,  В этом случае, исходя из формул (1) и (2),

В этом случае, исходя из формул (1) и (2),

T = Tmin = p(t0+tзап). (3)

Величина t0 представляет собой время обработки сообщения блоком 2 анализа, которое, в свою очередь, складывается из времени пребывания сообщения в блоке памяти сообщений 36, 37 или 35 (t'0) и времени передачи сообщения из указанного блока на один из выходов блока анализа (t''0). Величина tзап представляет собой сумму t0+t'зап, где t'зап - промежуток времени от момента выхода сообщения из блока 2 анализа до момента записи первой команды в регистр 5 команд.

Исходя из всего сказанного формулу (3) можно переписать в виде

Tmin = p(2t'0+2t''0+t'зап). (4)

Нетрудно видеть, что значение t'зап близко к периоду следования импульсов блока 8 синхронизации (τ8), a t''0 - к периоду следования импульсов распределителя 42 (τ42), поэтому можно считать

B то же время

B то же время  где K - средняя длина очереди сообщений в блоке памяти сообщений 36, 37 или 35. Считая, что τ8≈τ42 и обозначая τ8,τ42 как τ, из (4) получим окончательное выражение для Tmin:

где K - средняя длина очереди сообщений в блоке памяти сообщений 36, 37 или 35. Считая, что τ8≈τ42 и обозначая τ8,τ42 как τ, из (4) получим окончательное выражение для Tmin:

Tmin ≈ pτ(2K+3). (5)

В предлагаемой сети, как показано выше, обмен сообщениями при межмодульной передаче управления отсутствует. Запуск p параллельных участков производится практически одновременно в момент появления отрицательного перепада уровня сигнала завершения группы предшествующих параллельных участков на выходах элементов И 11.q (фиг. 1). Время межмодульной передачи управления T* не зависит от значения p и определяется скоростью распространения сигнала через цепочку элементов И 11.q различных модулей.

Величина T* складывается из времени (t1*) между моментом завершения группы предшествующих параллельных участков и моментом формирования единичного сигнала dq на выходе 29.q (1.N)-го модуля, задержки блока элементов НЕ 36 (Δt36), времени (t2*) распространения перепада уровня сигнала с q-го выхода блока 36 до последнего из активизируемых модулей МКС, а также времени запуска указанного модуля (tзап*), т.е. времени от момента появления перепада уровня сигнала на входе 27.q или 28.q модуля до момента фиксации первой команды в регистре 3. В предельном случае, когда последний завершаемый участок выполняется (М. 1)-м модулем, а последний из запускаемых параллельных участков - (1.N)-м модулем (фиг. 3),

t1* = t1*(max) - t2* - t2*(max) = (M + N - 2)t0*,

где t0* - задержка прохождения сигнала через модуль МКС с входа 27.q или 28.q на выход 29.q.

Величина t0* представляет собой задержку срабатывания элемента И  поэтому

поэтому

t

Как и в прототипе, tзап* приближенно равно периоду следования импульсов синхронизации, который, очевидно, может быть принят равным τ. B то же время Δt36≈Δtll.q≡Δt.

Исходя из всего сказанного, наибольшее значение Т* может быть определено как

Для обеспечения устойчивости работы модулей МКС должно выполняться условие τ ≫ Δt, например τ~20Δt(Δt~0.05τ). Поэтому, подставляя Δt = 0.05τ в (6) и учитывая (5), окончательно получим следующие соотношения:

T ≥ Tmin≈pτ(2K+3), (7а)

T*≅ T

Величины p, K, M и N характеризуются одним порядком (они, как правило, не превышают 10), поэтому для приближенной оценки можно считать p = K = M = N ≡ Θ ~ 1...10. С учетом этого допущения выражения (7а) и (7б) можно переписать в виде

T ≥ Tmin ≈ 2Θ2τ+3Θτ, (8а)

T*≅ T

Сравнение выражений (8а) и (8б) позволяет установить, что Tmin > Tmax*. Отсюда следует, что в общем случае T >> T*. Таким образом, в предлагаемой МКС обеспечивается существенно более высокая оперативность межмодульной передачи управления при запуске групп параллельных участков, чем в прототипе.

Наряду с повышением оперативности межмодульной передачи управления предлагаемое решение позволяет значительно уменьшить сложность модуля МКС.

Поскольку межмодульное взаимодействие в МКС не предполагает обмен сообщениями, соответственно, не требуются хранение и выбор маршрутов сообщений, из состава модуля удается исключить блок 2 анализа (здесь нумерация производится в соответствии с описанием прототипа), содержащий три блока памяти сообщений (каждый из которых включает группу из ~10 регистров, демультиплексор и несколько групп из ~10 логических элементов), генератор 39 константы, блок 40 выбора направления передачи сообщения, а также распределитель 42 импульсов и ряд других элементов. Кроме того, из состава модуля исключается блок 3 управления синхронизацией параллельных участков, включающий два отдельных блока памяти условий синхронизации (блоки 55 и 56) и ряд других элементов. Вместо указанных блоков и элементов в состав модуля вводятся регистр 5 вектора соответствия (здесь нумерация дается в соответствии с описанием МКС), дешифраторы 8 и 9, буферный регистр 7, блок элементов ИЛИ 14, три группы из n логических элементов (число логических элементов n представляет собой максимальное число вершин синхронизации в реализуемых программах, которое в большинстве случаев не превышает 50).

Суммарная сложность всех вводимых элементов с учетом соответствующих связей существенно ниже общей сложности блоков 2 и 3 прототипа. Тем самым достигается значительное упрощение модуля МКС. Несмотря на упрощение модулей предлагаемая МКС обладает всеми функциональными возможностями прототипа, позволяя, в частности, производить запуск и синхронизацию произвольных групп участков программ без ограничений на способ их межмодульного распределения.

Таким образом, исходя из всего вышесказанного, предлагаемое изобретение обеспечивает решение заявленной технической задачи, а именно: позволяет повысить оперативность межмодульной передачи в микроконтроллерной сети при запуске групп параллельных участков программ при одновременном упрощении модулей. Это, в свою очередь, способствует повышению общего быстродействия МКС и снижению сложности ее промышленного изготовления.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 2005 |

|

RU2280887C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 2007 |

|

RU2336556C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| ЛОГИЧЕСКИЙ МУЛЬТИКОНТРОЛЛЕР С РАСПРЕДЕЛЕННЫМ ПАРАЛЛЕЛЬНО-КОНВЕЙЕРНЫМ БАРЬЕРНЫМ СИНХРОНИЗАТОРОМ | 2010 |

|

RU2450328C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении распределенных систем программного управления технологическими процессами. Техническим результатом является расширение области применения устройства, повышение оперативности межмодульной передачи управления. Устройство содержит М•N однотипных модулей, объединенных в матричную структуру, каждый модуль включает блок памяти программ, ригистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, три элемента ИЛИ, блок элементов НЕ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, первую и вторую группы элементов И, группу элементов ИЛИ, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки. 1 з.п. ф-лы, 5 ил.

и ко второй группе входов синхронизации (M.J)-го модуля,

и ко второй группе входов синхронизации (M.J)-го модуля,  группа выходов синхронизации (α,β)-го модуля,

группа выходов синхронизации (α,β)-го модуля,

подключена к первой группе входов синхронизации (α.β+1)-го модуля и ко второй группе входов синхронизации (α-l.β)-го модуля, группа выходов синхронизации (l.β)-го модуля соединена с первой группой входов синхронизации (l.β+l)-го модуля, группа выходов синхронизации (α,N)-го модуля соединена со второй группой входов синхронизации (α-l.N)-го модуля.

подключена к первой группе входов синхронизации (α.β+1)-го модуля и ко второй группе входов синхронизации (α-l.β)-го модуля, группа выходов синхронизации (l.β)-го модуля соединена с первой группой входов синхронизации (l.β+l)-го модуля, группа выходов синхронизации (α,N)-го модуля соединена со второй группой входов синхронизации (α-l.N)-го модуля.

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Способ получения аминофенилэтаноламинов или их солей | 1974 |

|

SU533335A3 |

| Система коммутации устройств обработки информации | 1989 |

|

SU1798796A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПРОНИЦАЕМОСТИ ТКАНЫХ И НЕТКАНЫХ МАТЕРИАЛОВ ДЛЯ ИСПОЛЬЗОВАНИЯ В КАЧЕСТВЕ СРЕДСТВ ИНДИВИДУАЛЬНОЙ ЗАЩИТЫ ОТ БАКТЕРИАЛЬНОГО С РАЗНЫМ СТРОЕНИЕМ КЛЕТОЧНОЙ СТЕНКИ И ГРИБКОВОГО ЗАРАЖЕНИЯ ВОЗДУШНО-КАПЕЛЬНЫМ И КОНТАКТНО-БЫТОВЫМ ПУТЕМ | 2021 |

|

RU2770008C1 |

| US 3835896 A, 23.07.1974. | |||

Авторы

Даты

2001-05-27—Публикация

1999-09-13—Подача