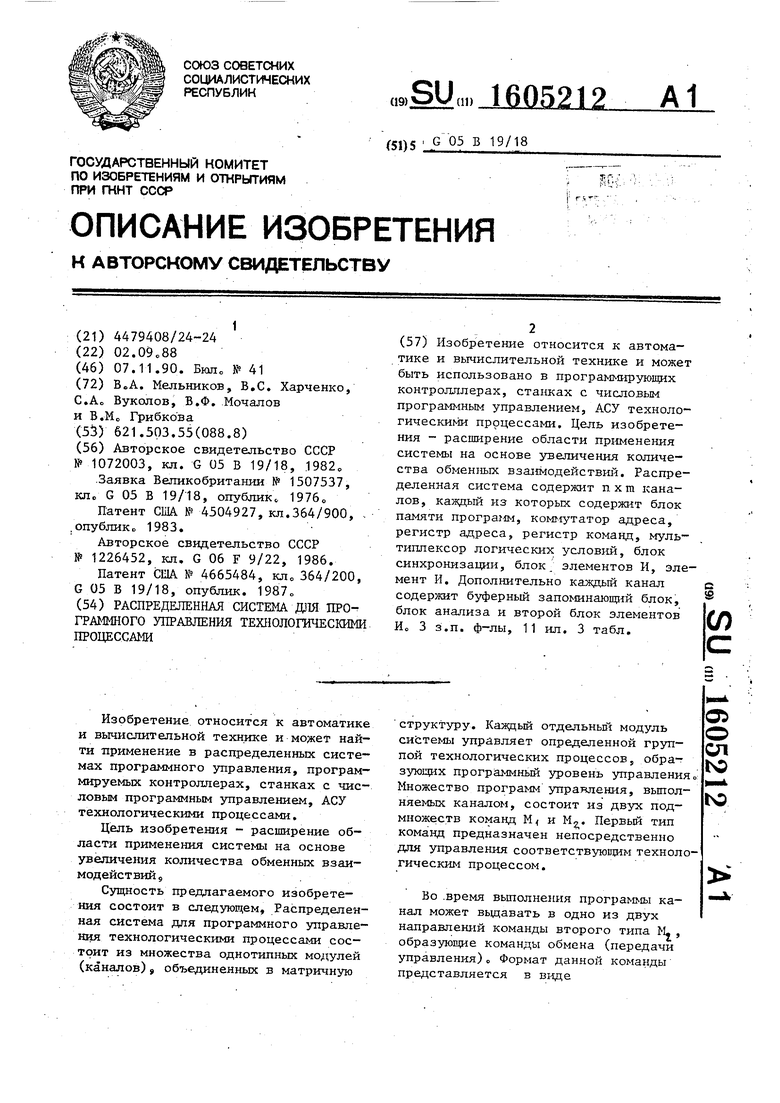

Изобретение относится к автоматике и вычислительной технике и может найти применение в распределенных системах программного управления, программируемых контроллерах, станках с числовым программным управлением, АСУ технологическими процессами.

Цель изобретения - расширение области применения системы на основе увеличения количества обменных взаимодействий j

Сущность предлагаемого изобретения состоит в следующем, .Распределенная система для программного управления технологическими процессами состоит из множества однотипных модулей (каналов), объединенных в матричную

структуру. Каждый отдельньпЧ модуль системы управляет определенной группой технологических процессов, образующих программный уровень управления о Множество программ управления, выполняемых каналом, состоит из двух подмножеств команд М и Mj. Первый тип команд предназначен непосредственно для управления соответствуюи им технологическим процессом.

Во .время выполнения программы канал может вьщавать в одно из двух направлений команды второго типа М,, образующие команды обмена (передачи управления) Формат данной команды представляется в виде

о:

о

СП

to

N3

пр

4

m

k

где ra - номер (код) канала приемника

информации;

m - номер (код) программы, которую должен выполнить канал- приемник с

Каждому каналу, входящему в состав распределенной системы, присваивается свой номер (идентификатор), определяющий его местоположение в матрице по горизонталш и вертикали Обмен командами передачи управления может произ- водиться либо по строке каналов, либо в столбце. Строки и столбцы каналов образуюткольцевую структзфу, что обеспечивает полную реализацию полного взаимодействия отдельных каналов, ,т.ео реализацию дисциплины каждый с каждым с

При поступлении сообщения от сосед- него канала определяется, ему ли пред- назначена поступившая информация.Это происходит путем сравнения кодов каналов приемника сообщения (идентифи- катора канала) с адресной частью сооб- ще1Шя о

При несовпадении кодов сообщение отправляется к соседнему каналу и ТоДо до совпадения кодов либо в столбце, либо в строке каналов При совпадении одного из двух кодов меняется направление продвизкения сообщения.

Введение блока анализа необходимо для реализации процедуры идентификации поступившей информации и выбора дальнейшего ее продвижения в матрице каналов распределенной системьь

Введение буферного запоминающего блока сообщений необходимо для временного хранения кодов программ, поступивших на обслуживание данному каналу

Блок памяти константы предназначен для хранения единственного составного кода, определяющего местоположение к канала в матричной структуре распределенной системы. Процесс считьшания информации из блока памяти происходит по импульсу синхронизации с распределителя.

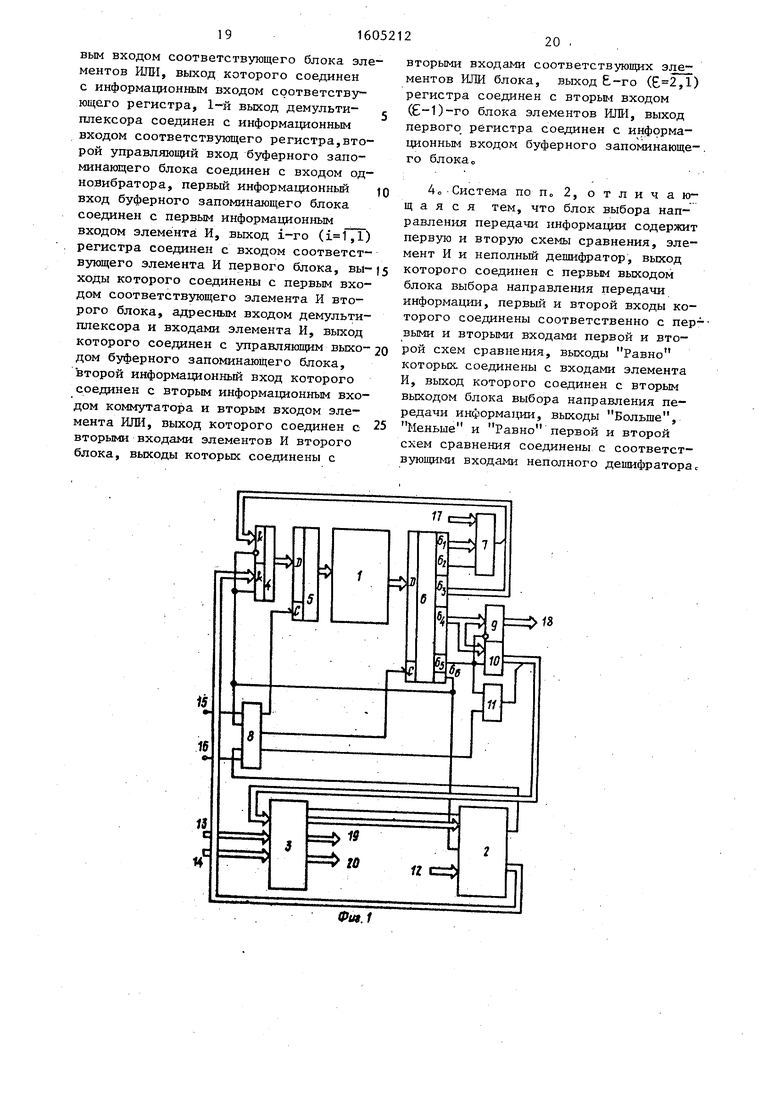

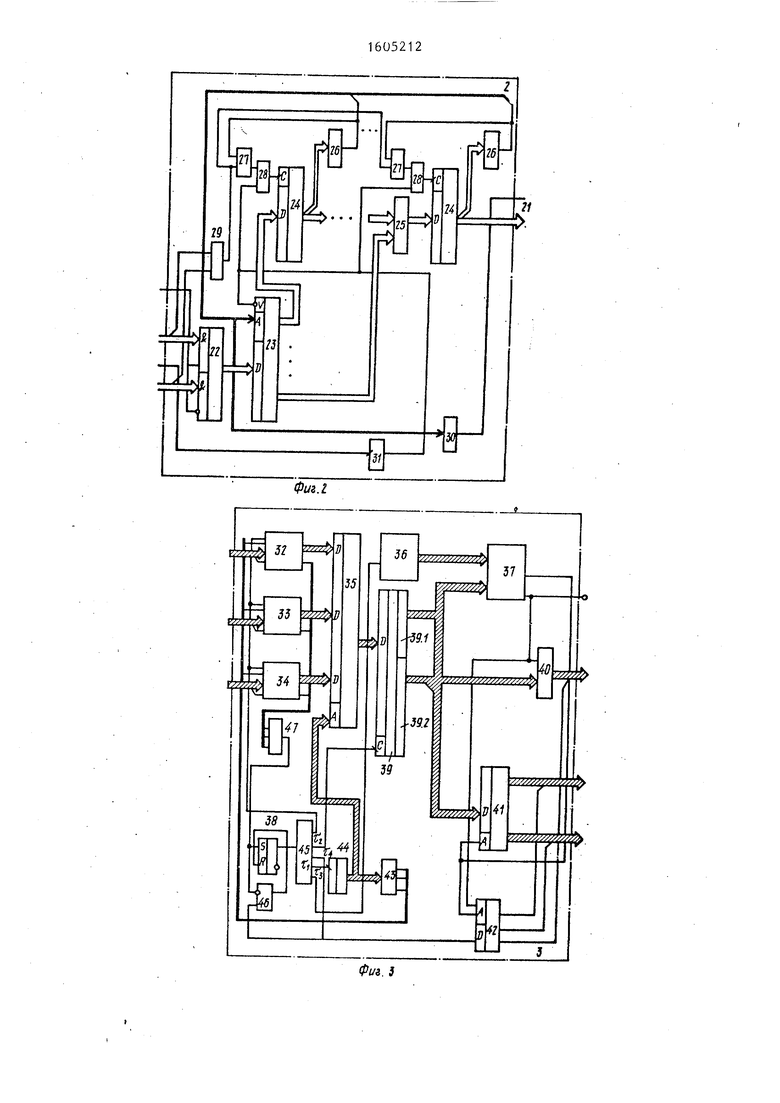

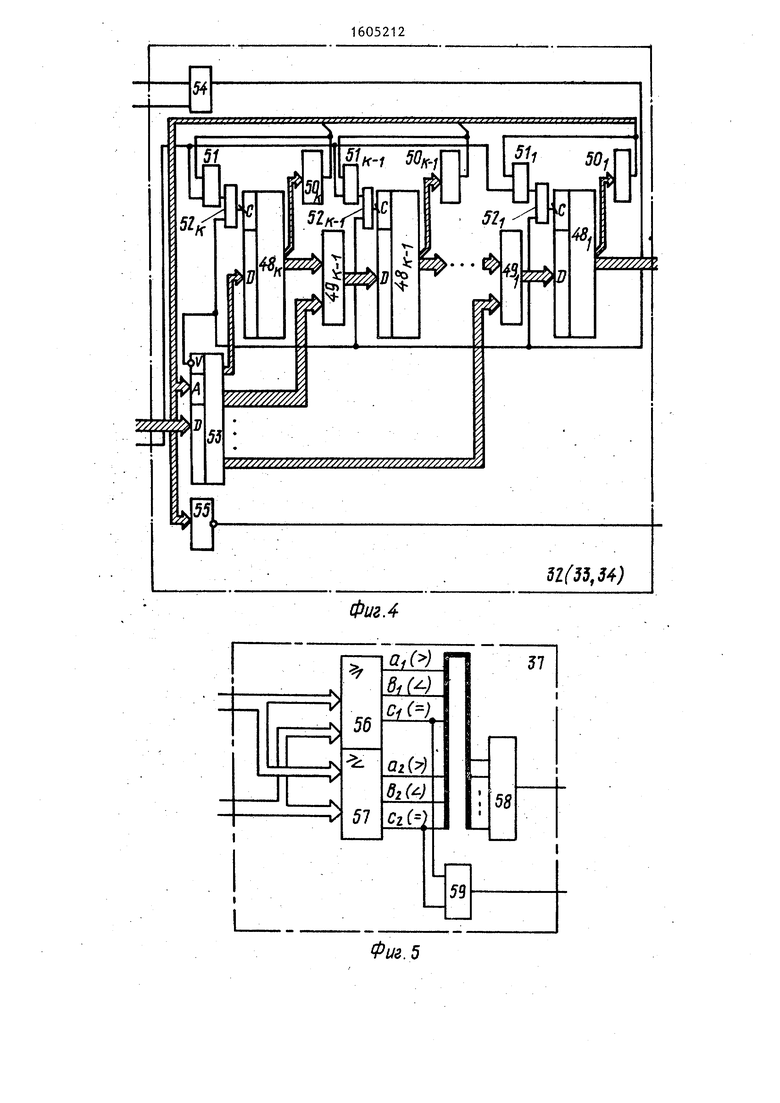

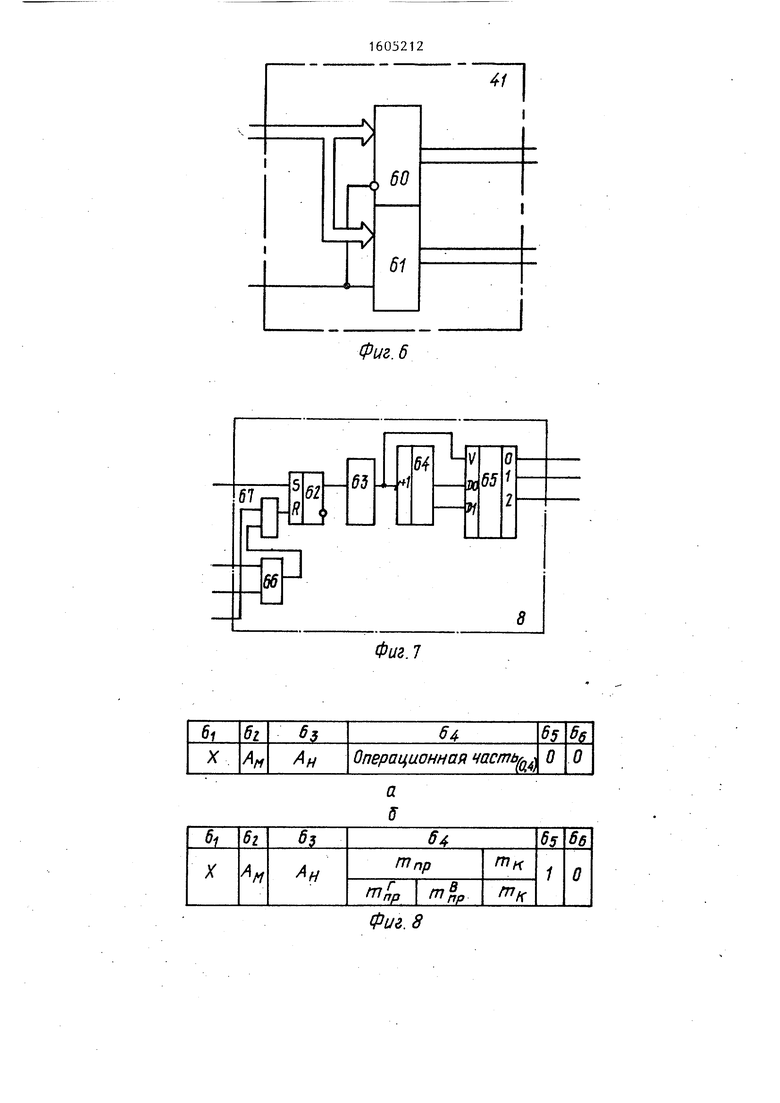

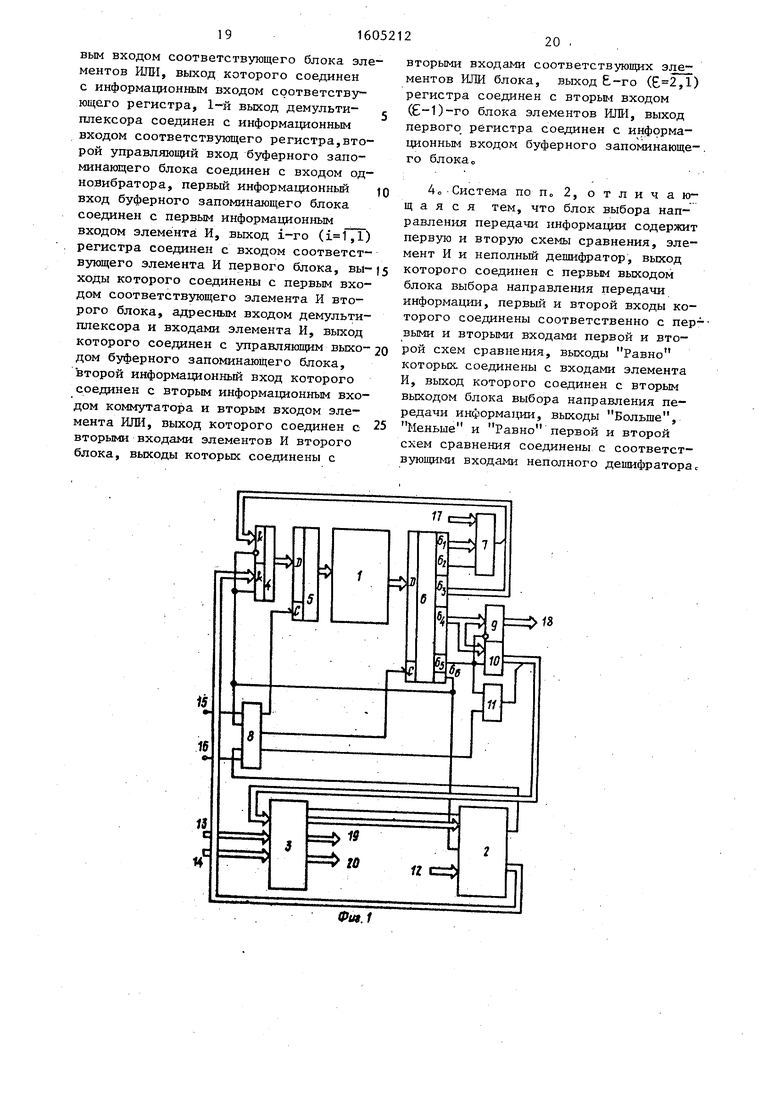

На фиг. 1 представлена функциональ- ная схема -го (i 1,n.xm) канала распределенной системы для программного управления технологическими процессами; на фиг. 2 - функциональная схема буферного запоминающего блока; на фигс 3 - функциональная схема блока

д с 2П

25

35

0

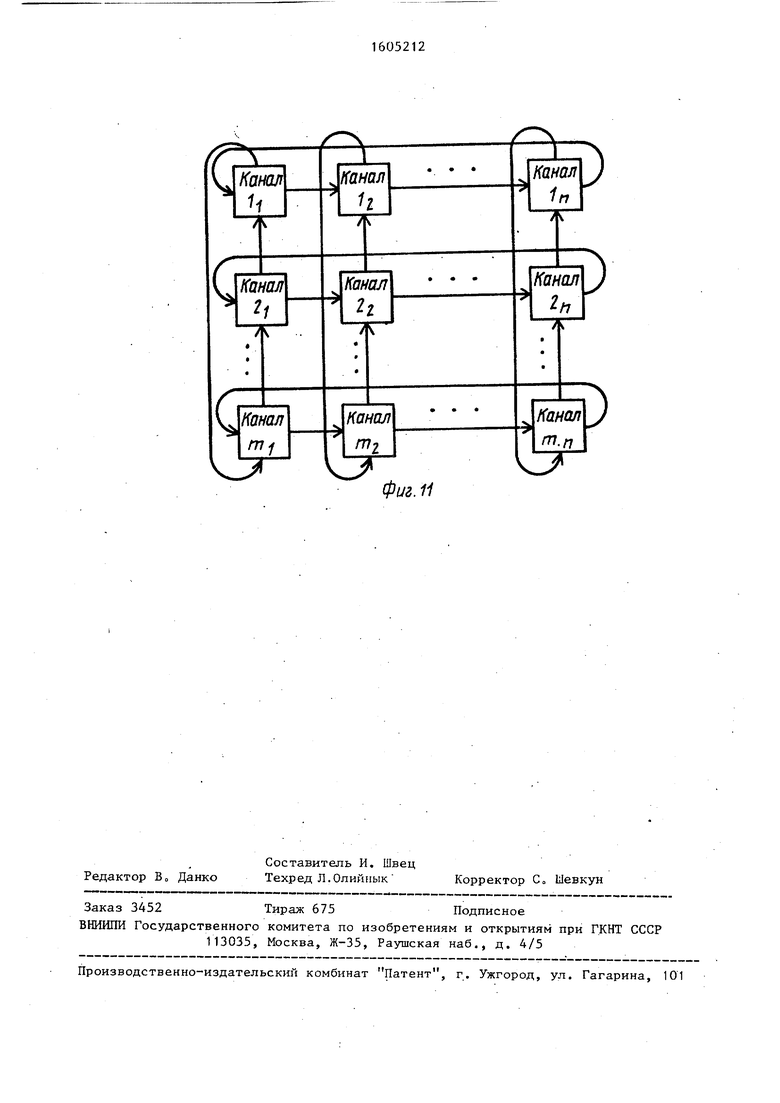

анализа; на фиг. 4 -функциональная схема первого (второго, третьего) блока памяти сообщений; на фиг„ 5 - функциональная схема блока выбора направления передачи информации; на фигс 6 - функциональная схема выходного демультиплексора; на фиг. 7 - функциональная схема блока синхронизации; на фиг 8 - формат команды обработки (а) и формат команды обмена (б); на фиг о 9 - функциональная схема распределителя импульсов; на фиг. 10- временные диаграммы Функционирования распределителя импульсов; на фиг„ t1 - пример кодироватшя матрицы каналов в распределенной системе размерности 3 X 3 и направлений передач команд обменао

i-й канал распределенной системы для программного управления технологическими процессами содержит блок 1 памяти программ, буферньш запоминаю- пщй блок 2 сообщений, блок 3 анализа, коммутатор 4,адреса, регистр 5 адреса, регистр 6 команд, мультиплексор 7 логических условий, блок 8 синхронизации, первый блок элементов И 9, второй блок элементов И 10, элемент И 11, первый 12, второй 13 и третий .14 информационные входы, первый 15 и второй 16 управляющие входы, вход 17 логических условий, первый 18, второй 19 и третий 20 информационные выходыо

Буферный запоминающий блок сообщений (БЗБ) (фиг о 2) содержит информационный выход 21, коммутатор 22, демультиплексор 23, блок регистров 24.1-24.1 (где 1 - глубина очереди), группу блоков элементов РИШ 25s,1- 25.1-1, первый блок элементов И 26.1-26с1, второй блок элементов И 27.1-27.1, блок элементов ИЛИ 28.1- 28Л, элемент ИЛИ 29, элемент И 30, одновибратор 31,

Блок анализа 3 (фиг. 3)-содержит первый 32, второй 33 и третий 34 блоки памяти сообщений, мультиплексор 35, блок 36 памяти константы, блок 37 выбора направления передачи информации, триггер 38, буферный регистр 39 с адресным 39.1 операционным 39.2 полями, блок 40 элементов И, выходной демультиплексор 41, демультиплексор 42 синхронизации, дешифратор 43,счетчик 44, распределитель 45 импульсов, элемент И 46, элемент ИЛИ 47„

Первьш 32, второй 33, третий 34 блоки памяти сообщений (фиго 4) содержит блок регистров 48,, 1-48 К (где К - длина очереди сообщений), группу блоков элементов ИЛИ 49,, 1-49. (К-1) , первый блок элементов И 50о1-50оК, второй блок элементов И 51.1-51.К, блок элементов ИЛИ 52.1-52.К, демуль тигшексор 53, элемент И 54, элемент И-НЕ 55,

Блок выбора направления передачи информации 37 (фиг. 5) содержит первую 56 и вторую 57 схемы сравне1шя, неполньш дешифратор 58, элемент И 59.

Выходной демультиплексор 41 (фиг. содержит первьй 60 и второй 61 блоки элементов Ио

Блок синхронизации (фиг. 7) содержит триггер 62 запуска, генератор 63 тактовых импульсов, счетчик 64, дешифратор 65, элементы И 66 и 67. ,

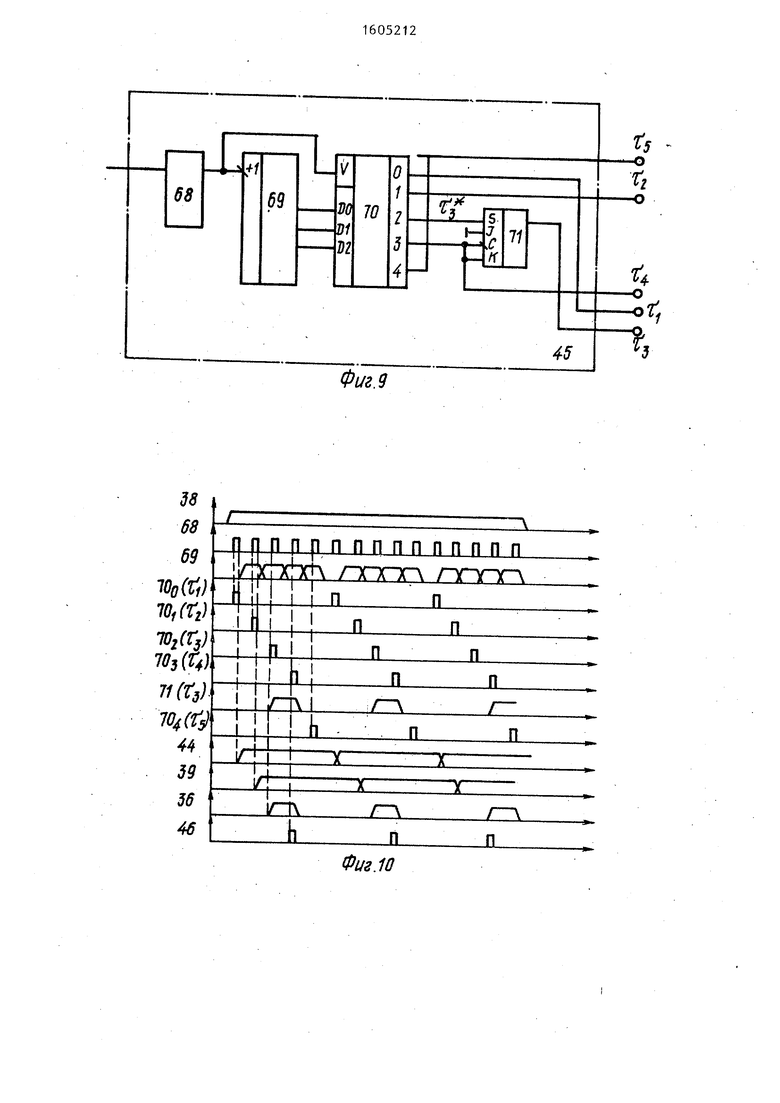

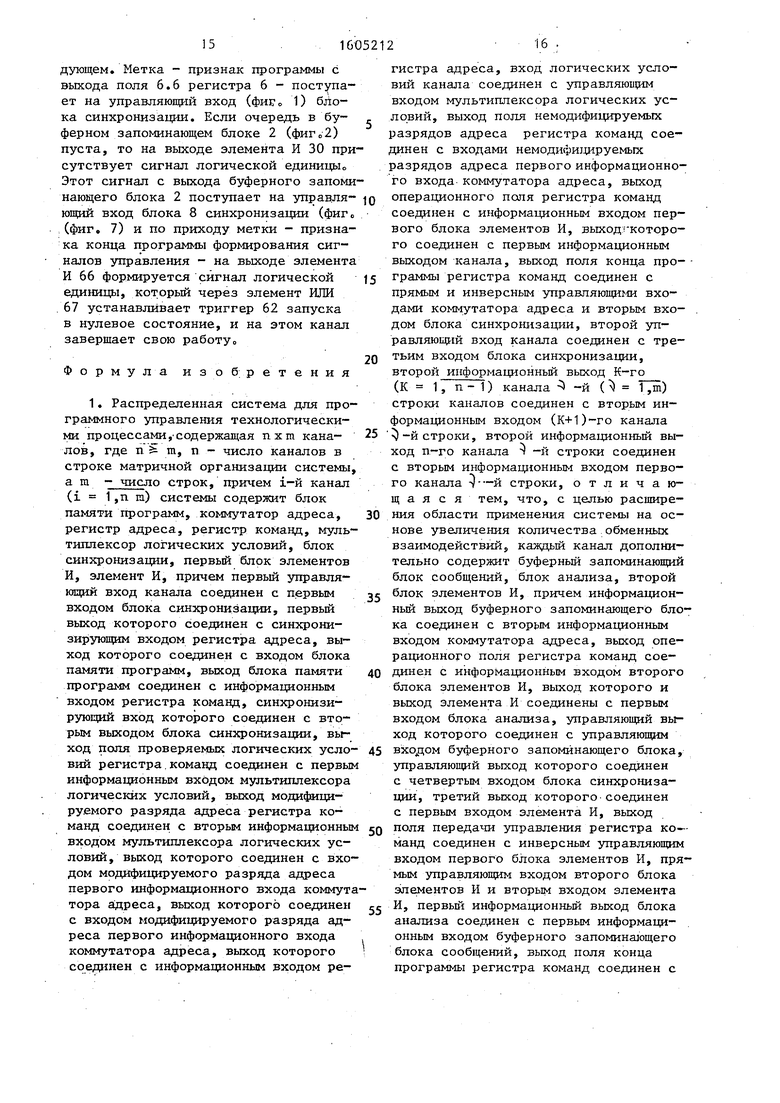

Распределитель 45 импульсов (фиг. содержит генератор 68 тактовых импульсов, счетчик 69, дешифратор 70, триггер 71 управления.

Назначение основных блоков и элементов отдельного канала распределенной системы состоит в следующем.

Блок 1 памяти программ предназна- чен для хранения команд управления и команд обмена (передачи управления аналогичным каналам системы). Буфер- ньм запоминающий блок 2 предназначен для хранения поступивших на обслужи- вание сообщений от других каналов системы и супервизорного устройства (центрального процессора). Блок 3 анализа предназначен для анализа поступивших сообщений на принадлежность информации данному каналу и выбора направления передачи при транзитном прохождении поступившего сообщения. Блок 8 синхронизации предназначен для формирования тактовых импульсов, син- хронизирующих работу канала.

Б блоке 3 анализа назначение основных элементов состоит в следующем. Блоки 32-34 памяти сообщений предназначены для хранения команд обмена, поступивших для вьщачи от собственного канала и соседних (двух) каналов системы (от левого при движении сообщения в строке каналов системы и от нижнего при движении в столбце кана- лов). Блок 36 памяти константы предназначен для хранения кода адреса канала, идентифиидирующего его местоположение в распределенной системе Блок

36 памяти константы может быть выполнен, например, в виде последовательного соединения генератора константы фиксированного кода (тумблерного регистра и т.п.) и блока элементов И, по второму входу которого подключен вход блока памяти.

Блок 37 выбора направления передачи информации предназначен для выбор и модификации направления выдачи соощений в зависимости от соотношения кодов каналов источника и приемника сообще1ШЙ.

Буферный регистр 39 предназначен хранения кода сообп;ения на время его анализа и обработки Выходной демультиплексор 41 предназначен для. коммутации команды обмена на один из выходов.блока 3 анализа и в целом канала к аналогичным каналам системы. Распределитель 45 импульсов предназна че}1 для синхронизации работы блока 3 анализа. Счетчик 44 является последовательным кольцевым и совместно с де- хиифратором 43 служат для последовательного циклического опроса блоков 32-34 памяти сообщений.

В распределенной системе для программного управления процессами (технологическими) , состоящей из однотипных каналов (фиг. 11) осуществляется обмен командами управления в двух направлениях Каждая горизонталь и вертикаль однотипных каналов системы образует соответствующее кольцо каналов, которое может быть выполнено в виде отдельной БИС (СБИС). Тогда ком- плексирование системы будет состоять в последовательном соединении отдельных СБИС о

В исходном (начальном) состоянии элементы памяти системы (каналов) находятся в нулевом состоянии (за исключением разряда поля 6.6 регистра 6 команд, определяющего конец программы управления)

Работа распределенной системы для программного управления технологическими процессами возможна в трех режимах: режиме обработки (вьщачи) собственных команд управления; режиме вьщачи команд обмена; режиме приема и обработки команд обмена.

Так как распределенная система состоит из набора однотипных каналов, то работу системы рассмотрим на примере функционирования отдельного канала.

16

Сигнал на начало работы поступает с управляющего входа 15 канала (фиг.1 Этот сигнал поступает на управляющий вход блока 8 синхронизации (фиг. 7) и поступая на S-вход триггера 62, ус- танавлива ют его в единичное состояние о Генератор 63 начинает формировать тактовые импульсы для синхрони- защш работы канала о В исходном сое- ТОЯН1Ш триггер 62 и счетчик 64 находятся в нулевом состояниио Приведение в исходное состояние счетчика 64 на фиг о 7 не отраткено.

Состояние входов блока 8 синхро- низации в исходном состоянии определяется следующим На первый вход блока 8 синхронизации (фиг 1,7) поступает с входа 15 канала сигнал логического нуля. На второй вход блока 8 синхронизации поступает сигнал логической еданицы (метка - признак конца программы с выхода поля 6.6 регистра 6 команд). На третий вход блока 8 синхронизации постзшает с входа 16 сигнал логического нуля И так как буферный запоминающий блок 2 находится в нулевом состоянии, то с его управляющего выхода на четвертый вход блока синхронизации поступа- ет сигнал логической единицы.

Триггер 38 устанавливается в нулевое состояние по импульсу распределителя 45 при нулевом состоянии регистров. 48.1-48.К блоков 32-34 памяти сообщений.

В исходном состоянии элементы памяти канала находятся в нулевом состоянии (за исключением разряда регистра 6 команд, определяющего признак конца программы управления технологического процесса)„

Работа каналй в режиме обработки собственных команд управления Работа канала в этом режиме функционирования начинается путем подачи на вход 12 (фиг. 1) кода операции, определяющего адрес первой команды программ управления. Этот код подается, например, от диспетчера, организующего про цесс управления

Код операции с входа 12 канала поступает через коммутатор 22 буферного запоминающего блока 2 сообщений (фиго 2) на информационный вход де- мультиплексора 23 Так как блок регистров 24,1-24.1 находится в нулевом состоянии, на выходах элементов И 26.1-26j,l блока находятся сигналы

Q

г 20 5 о

д

5 о

5

28

логической единицы. Эти сигна.пы,. поступая на управляюищй (адресньш) вход демультиплексора 23, разрешают запись информации в первьш регистр 24.1 через блок элементов ИЛИ 25.1. Вместе с адресом программы (кодом операции) на вход 12 канала подается управляющий импульс о Этот импульс --через элемент ИЛИ 29, элемент И 27 о 1 и элемент ИЛИ 28.1 поступает на синхронизирующий вход регистра 24.1 и производит запись в него поступившего кода опера- циис Состояние регистра будет отличным от нулевого и на выходе элемента И 26 о 1 будет сигнал логического нуля, которьй предопределяет запись очередного кода операции во второй регистр 24 о 2 буферного запоминающего блока . При нулевом состоянии j-ro (j ) регистра 24oj на выходе элемента И 26.J будет сигнал логической единицы, поступающий на соответствующий вход элемента И 30 Поэтому на выходе элемента И 30 будет сигнал логической единицы только при нулевом состоянии блока регистров 24 1-24о1.Этот сигнал поступает через управляющий вход блока 2 (фиг 2) на управляющий вход блока 8 синхронизации (фиго1) и разрешает тем самым завершить работу канала при вьщаче последней команды управления (метка - признак конца программы в поле боб регистра 6 команд)о

Одновременно с подачей кода операции на управляющий вход 15 канала (фиго 1) подается сигнал на начало работы Этот сигнал поступает на управляющий вход блока 8 синхронизации (фиго 7), устанавливает триггер 62 запуска в единичное состояние и разрешает тем самым формирование на выходе генератора 63 тактовых импульсов для синхронизации работы канала„ Синхронизация работы осуществляется сигналами с выходов дешифратора 65 блока 8 синхронизации

Первый тактовый импульс с выхода блока 8 синхронизации (фиг 1) поступает на синхронизирующий вход регистра 5 адреса и разрешает запись в него информации с выхода буферного запоминающего блока 2 (первого реги- стра 24о 1 блока регистров 24.1 -24о1) через кo „мyтaтop 4 адреса« По второму тактовому импульсу из блока 1 памяти программ будет сосчитана команда, которая по тактовому импз льсу с выхода блока 8 синхронизации будет занесена в регистр 6 команд (формат сосчитанной команды представлен на фиг. 8„а)о

Так как в поле регистра 6 команд признак передачи управления отсутствует, что операционная часть команды с поля 6„4 регистра 6 поступает через блок элементов И 9 на ин- формационный выход 18 канала для управления технологическим процессом, Поля 6о1, 6.2 и 6,3 регистра 6 команд формируют адрес очередной команды с использованием мультиплексора 7 логи- ческих условий, который предназначен для формирования значения мод фициру- емого разряда адреса очередной команды и реализует его логическую функцию вида

у, х,а , ,x, . z

У - выходной сигнал мультиплексора 7 логических условий; i- х - конъюнкция cZ, oTj о о о о,, соответствующая коду с выхода 6о1 кода логических условий, разрешающему прохождение модифицируемого адресного разряда без изменений;

30

Xg (/(, Xj о,о;20(3 о 00 Olt,

4 Olt ... конъюнкции, соответствуюыще кодам, определяющим прохождение на выход мультиплексора 7 одного из сигналов логических условий z,z,,,., . с. входа 17 логических ус условий канала,

С вьщачей последней команды формируемой программы управления в поле 6,6 регистра 6 заносится метка - приз нак окончания программы Эта метка поступает на управляющий вход коммутатора 4 адреса и разрешает прохояоде- ние через него информации (адреса очередной программы) из буферного запо- минающего блока 2о Кроме того, эта метка поступает на управляющий вход буферного запоминающего блока 2 (фиго 2) и,формирует по фронту на выходе одновибратора 31 импульс. Этот импульс через элементы ИЛИ 28,1-28,1 поступает на синхронизирующие входы блока регистров 24,1-24о1 и осуществляет тем самым сдвиг информации.

п15 2Q

i-

30

35 40

is-QЕсли выполнялась последняя команда, то очередь поступивших на обслуживание запросов становится пустой (нулевое состояние блока регистров 24,1- 24,1)о На выходах элементов И 26,1- 26,1 образуются сигналы логической единицы. На выходе элемента И 30 появляется сигнал логической единицы, ко- торый с выхода буферного запоминающего блока (фиго 1) поступает на вход блока 8 синхронизации (фиг. 7). На выходе элемента И 66 формируется сигнал логической единицы, который через элемент ИЛИ 67 устанавливает триггер 62 запуска в нулевое состояние и канал заверщает свою работу.

Если очередь в буферном запоминающем блоке 2 не пуста, то после сдвига информации в блоке регистров 24„1- 24 о 1 первым тактовым импульсом очередной импульсной последовательности производится запись информации в регистр 5 адреса и далее канал функционирует аналогично рассмотренномуо

Работа канала в режиме вьвдачи команд обмена, В процессе обработки собственных команд канал может вьдавать команды обмена другим аналогичным каналам, образующим двунаправленную к кольцевую структуру распределенной системы.

Формат команды обмена (передачи управления) представлен на фиг. 8„5. В этом случае с поля 6,4 регистра 6 команд подается команда

1 к где т,.- код (номер) канала приемника

информации;

k код (номер) программы, которую должен вьшолнить Шпр-й канал системы; тт- - знак конкатенации (сцештения) , В свою очередь

™пр 1п„р

Ф m

6 пр

где m

пр

в

- номер канала приемника информации в строке аналогичных каналов; рр номер канала приемника

информации в столбце аналогичных каналов.

Одновременно с кодом ш команды обмена с выхода поля 6,5 регистра 6 команд выдается метка - признак передачи управления аналогичному каналу.

Эта метка поступает на управляюиц1е входы блока элементов И 10 и элемента И 11 (фиг о 1) и разрешает тем самым прохождение команды обмена с поля 6«4 регистра 6 через блок элементов И 10 на информационный вход блока 3 анализа (фиго 3)о Вместе с командой обмена с выхода блока 8 синхронизации через элемент И 11 (фиг, 1) поступает так- товый импульс.

Обмен командами в распределенной системе, ;остоящей из однотипных каналов, осуществляется (фиг 11) в двух направлениях. По каждому из направлений в блоке 3 анализа имеется блок памяти сообщений (БЛС) (фиГсЗ). Третий БПС предназначен для хранения команд обмена -от собственного каналао

Команда обмена в рассматриваемом случае поступает на вход БПС 32с Так как блок регистров 48.1-48.К (где К- глубина очереди) (фигс 4) находится в нулевом состоянии, то на выходах элементов И 50.1-50.К находятся сигналы логической единицы. Эти сигналы поступают на адресный вход демульти- .плексора 53 и разрешают тем самым запись поступившего сообщения в пер- вый регистр.48,1 очереди.

Адресация демультигшексора 53 БПС 32-34 (фиго 4) состоит в следующем Нулевые выходы регистров ,К соединены с входами соответствующих элементов И 50,1-50.К Следовательно, при нахождении i-ro (,K) регистра 48 о i в нулевом состоянии на выходе элемента И будет сигнал логичес КОЙ единицы г; . Этот сигнал поступает на адресный вход демультиплексора 53 и на соответствуюшдй вход элемента И-НЕ 55..

При нулевом состоянии регистров 48,1-48оК на выходе элемента И-НЕ 55 будет сигнал логического нуля, который поступает на управлякщий выход

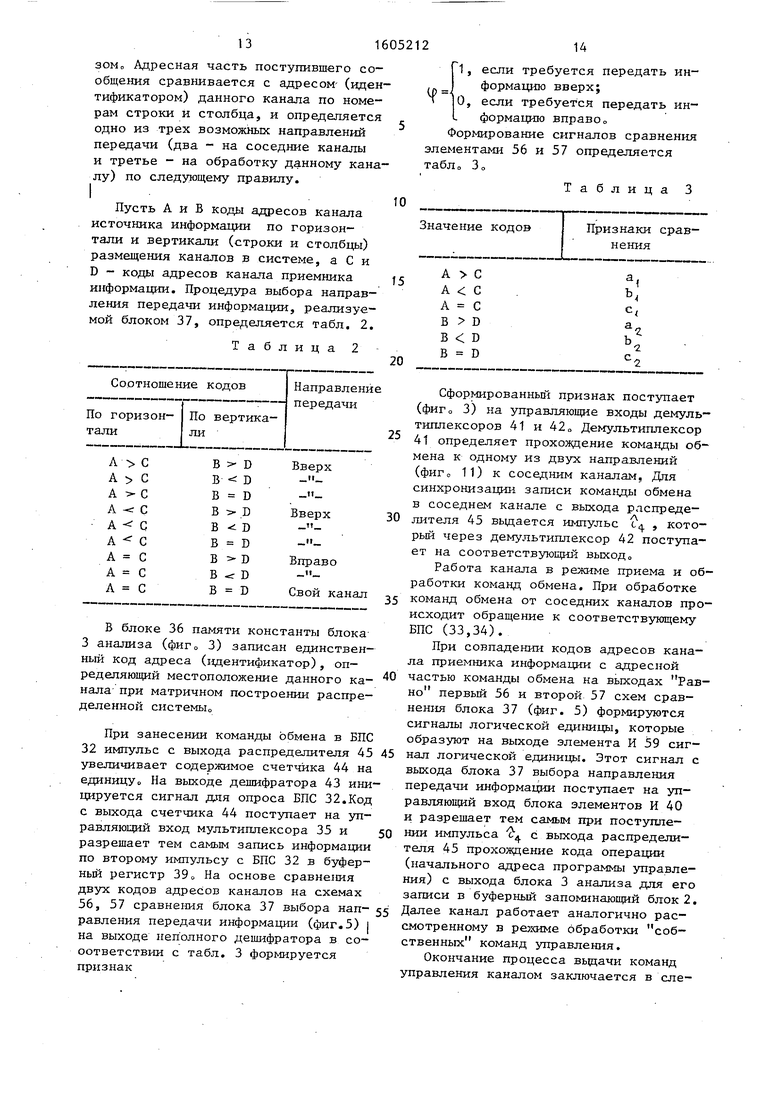

Адресация регистров ,К де- мультиштексором 53 для занесения в них информации определяется табло1,

При занесении информации хотя бы в один регистр 48oi. (,K)(iFj) на выходе элемента И-НЕ 55, например,

Fj-F,,, ,-г + будет сигнал логической единицы.

Таблица 1 Код состояния блока ре- I Адресация ре

гистров

гистра (R)

к-«

R,

Состояние этого регистра (48,1) изменится, и тем самым будет подготовлен для записи очередного сообщения (команды обмена) второй регистр 48.2. При записи команды обмена в регистр 48 о 1 на выходе элемента И-НЕ 55 появляется сигнал логической единицы Этот сигнал с вькода БПС 32 через элемент ИЛИ 47 (фиг о 3) устанавливает триггер 38 в единичное состояние и тем самым разрешает формирование тактовых импульсов на выходе распределителя 45 для синхро шзации работы блока 3 анализао

Синхронизация работы блока 3 анали- за происходит по пяти импульсным последовательностям (фиг. 10)о Цикл (такт) работы состоит из пяти фаз, каждая из которых начинается тактовым импульсом соответствующей импульсной последовательностио

По первому импульсу производится обращение к соответствующему БПС 32- 34 путем увеличения содержимого счетчика 44 на единицу„ По второму импульсу производится запись сообщения в буферный регистр 39, По четвертому импульсу производится вьщача команды обмена либо к соседним каналам системы, либо данному каналу для ее дальнейшей обработки. По третьему импульсу производится обращение к блоку памяти константы 36. По пятому импульсу производится сдвиг информации (команд обмена) в БПС, из которого бьша сосчитана информация для анализао Далее цикл работы блока 3 анализа повторяется путем обращения к очередному блоку памяти сообщений.

Выбор направле1шя передачи информа- 1ЩИ осуществляется следующим обра13

зомо Адресная часть поступившего сообщения сравнивается с адресом- (идентификатором) данного канала по номерам строки и столбца, и определяется одно из трех возможных направлений передачи (два - на соседние каналы и третье - на обработку данному каналу) по следующему правилу.

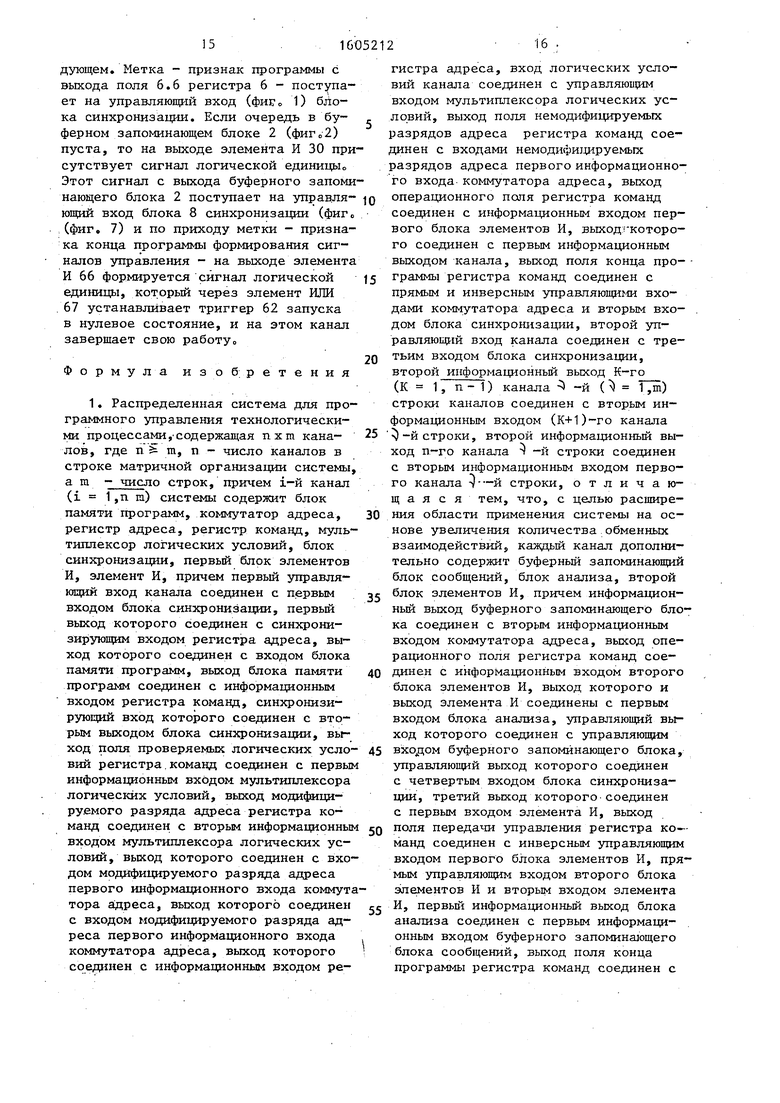

I

Пусть А и В коды адресов канала источника информации по горизонтали и вертикали (строки и столбцы) размещения каналов в системе, а С и D - коды адресов канала приемника информации. Процедура выбора направления передачи информации, реализуемой блоком 37, определяется табл. 2.

Таблица 2

14

1, если требуется передать информацию вверх; О, если требуется передать ин

10

формацию вправос Формирование сигналов сравнения элементами 56 и 57 определяется табЛо 3„

Таблица 3

5

0

Значение кодов

А С

А С

А С

В D

В D

В D

Признаки сравнения

ь,

с

а„

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в программирующих контроллерах, станках с числовым программным управлением, АСУ технологическими процессами. Цель изобретения - расширение области применения системы на основе увеличения количества обменных взаимодействий. Распределенная система содержит N . M каналов, каждый из которых содержит блок памяти программ, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов И, элемент И. Дополнительно каждый содержит буферный запоминающий блок, блок анализа и второй блок элементов И. 3 з.п. ф-лы.

В блоке 36 памяти константы блока 3 анализа (фиго 3) записан единственный код адреса (идентификатор), определяющий местоположение данного канала при матричном построении распределенной системы

При занесении команды обмена в БПС 32 импульс с выхода распределителя 45 увеличивает содержимое счетчика 44 на единицу На выходе делшфратора 43 ини- цируется сигнал для опроса БПС 32.Код с выхода счетчика 44 поступает на управляющий вход мультиплексора 35 и разрешает тем самым запись информации по второму импульсу с БПС 32 в буфер- ньш регистр 39 На основе сравне1шя двух кодов адресов каналов на схемах 56, 57 сравнения блока 37 выбора нап- равления передачи информации (фиг.5) i на выходе неполного дешифратора в со- оответствии с табл. 3 формируется признак

0

5

Сформированный признак поступает (фиго 3) на управляющие входы демуль- типлексоров 41 и 42 Демультиплексор 41 определяет прохождение команды обмена к одному из двух направлений (фиго 11) к соседним каналам, Для синхронизации записи команды обмена в соседнем канале с выхода распределителя 45 вьщается импульс С , который через Демультиплексор 42 поступает на соответствующий выход

Работа канала в режиме приема и обработки команд обмена. При обработке команд обмена от соседних каналов происходит обращение к соответствующему БПС (33,34).

При совпадении кодов адресов канала приемника информации с адресной частью команды обмена на выходах Равно первый 56 и второй 57 схем сравнения блока 37 (фиг. 5) формируются сигналы логической единицы, которые образуют на выходе элемента И 59 сигнал логической единицы. Этот сигнал с выхода блока 37 выбора направления передачи информации поступает на управляющий вход блока элементов И 40 и разрешает тем самым при поступлении импульса ( с выхода распределителя 45 прохождение кода операции (начального адреса программы управления) с выхода блока 3 анализа для его записи в буферный запоминающий блок 2. Далее канал работает аналогично рассмотренному в ре;химе обработки собственных команд управления.

Окончание процесса вьщачи команд управления каналом заключается в еледующем. Метка - признак программы с выхода поля 6.6 регистра 6 - поступает на управляющий вход (фиг 1) бАо- ка синхронизации. Если очередь в бу- фарном запоминающем блоке 2 (фиг о2) пуста, то на выходе элемента И 30 присутствует сигнал логической единицЫо Этот сигнал с выхода буферного запоминающего блока 2 поступает на упранля- ющий вход блока 8 синхронизации (фиг о : (фиг. 7) и по приходу метки - признака конца программы формирования сигналов управления - на выходе элемента И 66 формируется сигнал логической единицы, который через элемент ИЛИ . 67 устанавливает триггер 62 запуска в нулевое состояние, и на этом канал завершает свою работу

Формула изобретения

коммутатора адреса, выход которого соединен с информационным входом ре, Q15

20

25 30 jr 40 45 JQ гс

гистра адреса, вход логических условий канала соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен с входами немодифшдаруемьгх разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом первого блока элементов И, выходгкоторо- го соединен с первым информационным выходом канала, выход поля конца про- граммы регистра команд соединен с прямым и инверсным управляющигш входами коммутатора адреса и вторым входом блока синхронизации, второй управляющий вход канала соединен с третьим входом блока синхронизации, второй информационньй выход К-го (к 1, п - 1) канала -) -и ( ) 1 ,т) строки каналов соединен с вторым информационным входом (К+1)-го канала строки, второй информационный выход п-го канала т -и строки соединен с вторым информационным входом первого канала -V-и строки, о т л и ч а ю- щ а я с я тем, что, с целью расширения области применения системы на основе увеличения количества обменных взаимодействий, калодьш канал дополнительно содержит буферный запоминающий блок сообщений, блок анализа, второй блок элементов И, причем информационньй выход буферного запоминающего блока соединен с вторьм информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом второго блока элементов И, выход которого и выход элемента И соединены с первым входом блока анализа, управляющий выход которого соединен с управляющим входом буферного запоминающего блока, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого-соединен с первым входом элемента И, выход поля передачи управления регистра ко-- манд соединен с инверсным управляющим входом первого блока элементов И, прямым управляющим входом второго блока элементов И и вторым входом элемента И, первьй информационньй выход блока анализа соединен с первым информационным входом буферного запоминающего блока сообщений, выход поля конца программы регистра команд соединен с

вторым управляющим входом буферного запоминающего блока сообщений, первый информационный вход канала соединен с вторым информационным входом буферного запоминающего блока, второй информационный вход канала соединен с вторым входом блока анализа, второй информационньш выход которого соединен с вторым информационным выходом канала, третий информационный вход канала соединен с третьим входом блока анализа, третий информационный выход которого соединен с третьим информационным выходом канала, третий информационный выход j-ro (,l) канала u-го столбца ( Пд 1, п) каналов соединен с третьим информационным входом (j-l)-ro канала, третий информационньш выход первого канала (V-го столбца каналов соединен с третьим информационным входом т-го канала соответствующего столбца каналовс

2 о Система поп,, 1, отличающаяся тем, что блок анализа со- дерлсит первый - третий блоки памяти сообщений, мультиплексор, блок памяти константы, блок выбора направления передачи информации, триггер, буферньш регистр, блок элементов И, выходной демультиплексор, демультигшексор синхронизации, дешифратор, счетчик, распределитель импульсов, элемент И и элемент ИЛИ, выход которого соединен с S-входом триггера и инверсным входом элемента И, выход которого соединен с R-входом триггера, прямой вход триггера соединен с управляющим входом распределителя импульсов, пер- вьш выход которого соединен со счет- ным входом счетчика, выходы счетчика соединены с входами дешифратора и управляющим входом мультиплексора, выход которого соединен с информационным входом буферного регистра, синх- ронизирующий вход которого соединен с вторым выходом распределителя импульсов, третий выход распределителя импульсов соединен с входом считьша- ния блока памяти константы, выход которого соединен с первым входом бло ка выбора направления передачи информации, второй вход которого соединен с выходом адресного поля буферного регистра, выход операционного поля буферного регистра соединен с информа- Iционным входом блока элементов И, выход которого соединен с первым информационным выходом блока анализа, вы-

.« j рп 25ЗОQ д 35

5

ходы адресного и операционного полей буферного регистра соединены с информационным входом выходного демуль- типлексора, nepBbni и второй выходы которого соединены соответственно с вторым и третьим информационными вы ходами блока анализа, первый - третий входы которого соединены с информационным и первым заправляющим входами соответствующих блоков памяти сообщений, информационные выходы которых соединены с соответствующими информационными входами мультиплексора, управляющие выходы блоков памяти сообщений соединены с входами элемента ШШ, четвертый выход распределителя импульсов соединен с прямым входом элемента И и информационным входом демультиплексора синхронизации, выходы которого соединены с соответствующими информационными выходами блока анализа, первьй выход блока выбора направления передачи информации соединен с управляющим входом выходного демультиплексора и управляющим входом демультиплексора синхронизации, второй выход блока выбора направлешм передачи информации соединен с утграв- ляющим входом демультицлексора синхронизации, управляющим входом блока элементов И и управляющим выходом блока анализа, пятый выход распределителя импульсов соединен с тактовьп ш входами первого - третьего блоков памяти сообщений, выходы дешифратора соединены с вторыми управляющими входами соответствующих блоков памяти сообщений о

Зо Система по По 1, отличающаяся тем, что буферньш запоминающий блок содержит коммутатор, демультиплексор, блок из 1 регистров :(где 1 - длина очереди), группу из. (1-1)-го блока элементов ИЛИ, два блока элементов И, блок элементов ИЛИ, элемент ИЛИ, элемент И и одновибра- ;тор, выход которого соединен- с инверс- ным управляющим входом демультиплек- сора и первыми входами элементов ИЛИ блока, выходы которых соединены с синхронизирующш-ш входами соответствующих регистров, первый управляющий вход буферного напоминающего блока соединен с прямым и инверсным ляющими входами коммутатора, выход которого соединен с информационным входом демультиплексора, К-й ( 1-1)j выход которого соединен с пер-

Фи9.1

Фиъ.г

Фиг. 4

Фиг. 5

IF

Фиг. 6

Фиг.7

a 5

Фиг. 8

Фиг.10

| Устройство для программного управления | 1982 |

|

SU1072003A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ управления процессом прессования порошкового материала и устройство для его осуществления | 1987 |

|

SU1507537A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4665484, клс 364/200, G 05 В 19/18, опублик | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1990-11-07—Публикация

1988-09-02—Подача