Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределенных систем программного управления технологическими процессами, роботами и робототехническими комплексами, а также подсистем логического управления многоуровневых иерархических АСУ и мультипроцессорных систем широкого класса.

Известно модульное устройство для программного управления и контроля, содержащее блок памяти, счетчик адреса, регистр микроопераций, мультиплексоры адреса и логических условий, два регистра логических условий, два коммутатора, два дешифратора, шифратор, генератор тактовых импульсов, триггеры пуска и управления, демультиплексор, регистр номера, группу элементов ИЛИ, блок элементов ИЛИ, два элемента ИЛИ и два элемента И [1].

Недостатком этого устройства является значительное число внешних входов и выходов, требуемых для организации взаимодействия с другими аналогичными устройствами, и, следовательно, узкая область его применения.

Известно также устройство для программного управления, включающее блок памяти микрокоманд, счетчики адреса и времени задержки, регистр микроопераций, дешифратор направления передачи управления, коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, элемент запрета, шину микроопераций, четыре элемента ИЛИ и два элемента И [2].

Недостатком указанного устройства является невозможность построения на его основе управляющих систем, обеспечивающих возможность реализации параллельных алгоритмов управления (программ).

Наиболее близким к предлагаемому является распределенная система для программного управления технологическими процессами, содержащая m • n каналов (модулей), каждый из которых включает блок памяти программ, коммутатор адреса, регистры адреса и команд, мультиплексор логических условий, блоки синхронизации и анализа, буферный запоминающий блок, два блока элементов И и элемент И [3].

Недостатком этой системы является узкая область применения, связанная с отсутствием возможности согласования моментов (синхронизации) окончания и инициализации групп параллельных участков программ, закрепленных за различными модулями (отсутствие возможности синхронизации параллельных участков программ для широкого спектра применений является недопустимым, поскольку обусловливает возможность одновременного выполнения несовместимых команд (участков)).

Технической задачей изобретения является расширение области применения системы на основе организации возможности синхронизации завершения параллельных участков программ.

Техническая задача решается тем, что каждый из m • n модулей дискретной микроконтроллерной сети, содержащий блок памяти программ, блок анализа, регистр-счетчик адреса, регистр команд, коммутатор адреса, мультиплексор логических условий, блок синхронизации, первый и второй блоки элементов И, первый элемент И, причем выход коммутатора адреса соединен с информационным входом регистра-счетчика адреса, выход которого соединен с адресным входом блока памяти программ, выход которого подключен к информационному входу регистра команд, выходы кода логического условия и модифицируемой части адреса которого подключены соответственно к управляющему и первому информационному входам мультиплексора логических условий, второй информационный вход которого является входом логических условий модуля, выход мультиплексора логических условий в объединении с выходом немодифицируемой части адреса регистра команд подключен к первому информационному входу коммутатора адреса, первый и второй управляющие входы которого соединены с выходом признака конца программы регистра команд, выход признака формата команды которого соединен с первым входом первого элемента И, а также с управляющими входами первого и второго блоков элементов И, первый управляющий вход модуля соединен с первым входом блока синхронизации, первый выход которого подключен к второму входу первого элемента И, второй выход блока синхронизации соединен с входом синхронизации регистра команд, операционный выход которого подключен к информационным входам первого и второго блоков элементов И, выход первого блока элементов И является операционным выходом модуля, выход второго блока элементов И в объединении с выходом первого элемента И подключен к первому входу блока анализа, второй и третий входы которого являются соответственно первым и вторым информационными входами модуля, первый и второй информационные выходы блока анализа являются соответственно первым и вторым информационными выходами модуля, дополнительно включает блок управления синхронизацией параллельных участков, триггер, третий и четвертый блоки элементов И, с второго по седьмой элементы И, с первого по третий элементы ИЛИ, причем выход признака конца программы регистра команд подключен к выходу конца операции модуля, к третьему управляющему входу коммутатора адреса и к первому входу первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого подключен к второму входу блока синхронизации, третий выход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам триггера, выход третьего элемента И соединен со счетными входами триггера и регистра-счетчика адреса, выход четвертого элемента И соединен с входом синхронизации регистра-счетчика адреса, выход признака передачи управления регистра команд подключен к второму входу первого элемента ИЛИ и к первому входу второго элемента ИЛИ, выход которого соединен с четвертым, пятым и шестым управляющими входами коммутатора адреса, второй и третий информационные входы которого соединены соответственно с входом кода операции модуля и с выходом третьего блока элементов И, выход признака конца параллельного участка регистра команд подключен к информационному входу второго блока элементов И, к третьему входу первого элемента ИЛИ и к второму входу второго элемента ИЛИ, старшие разряды третьего информационного выхода блока анализа соединены с первыми входами третьего и четвертого блоков элементов И, младший разряд третьего информационного выхода блока анализа соединен с первыми входами пятого, шестого и седьмого элементов И и с вторыми входами третьего и четвертого блоков элементов И, первый управляющий выход блока анализа подключен к вторым входам шестого и седьмого элементов И, второй управляющий выход блока анализа подключен к второму входу пятого элемента И, второй управляющий вход модуля соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу седьмого элемена И, выход третьего элемента ИЛИ подключен к третьему входу блока синхронизации, первый выход которого соединен с вторым входом второго элемента И, выход четвертого блока элементов И подключен к информационному входу блока управления синхронизацией параллельных участков, первый и второй входы синхронизации которого соединены соответственно с выходами шестого и пятого элементов И, первый выход блока управления синхронизацией параллельных участков подключен к третьему входу третьего элемента ИЛИ и к входу установки триггера, второй выход и управляющий вход блока управления синхронизацией параллельных участков являются соответственно выходом состояния модуля и входом настройки модуля.

Сущность предлагаемого изобретения состоит в следующем.

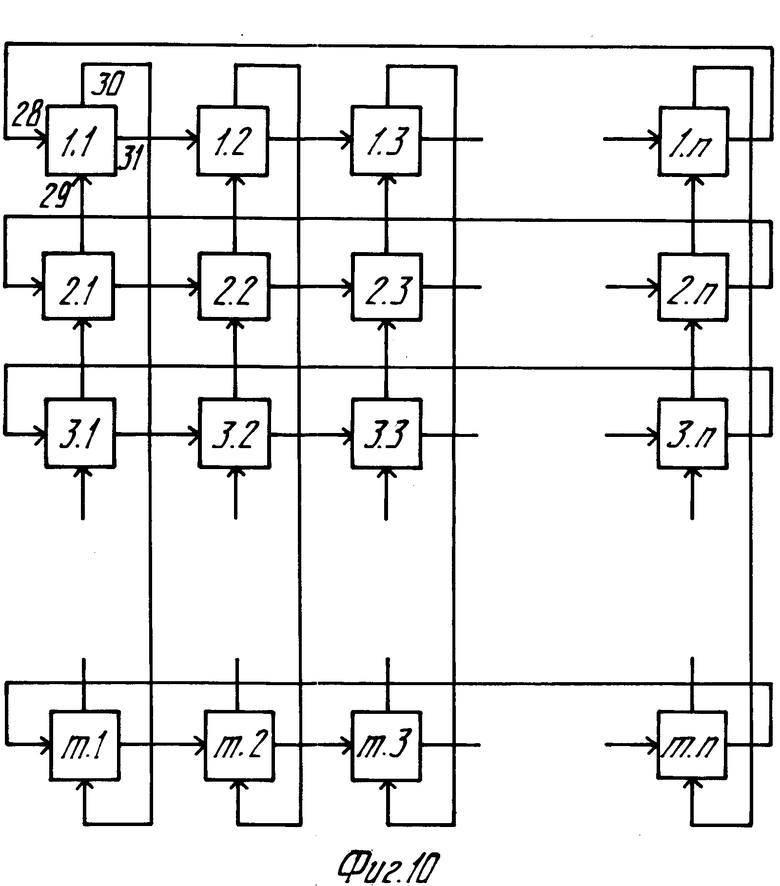

Дискретная микроконтроллерная сеть (ДМС) формируется из набора однотипных модулей, объединяемых в матричную структуру, и предназначается для программного (микропрограммного) управления сложными объектами, поведение которых предполагает одновременное развитие и взамодействие множества процессов. Каждый модуль ДМС выполняется в виде СБИС и имеет два входных и два выходных информационных канала, используемых для подключения к другим аналогичным модулям и обмена управляющей информацией. С целью обеспечения возможности идентификации модулей ДМС им присваиваются номера вида I.J, где I и J имеют смысл соответственно номера (кода номера) строки и номера столбца матричной структуры, содержащих данный модуль, "." - символ объединения (конкатенации) кодов.

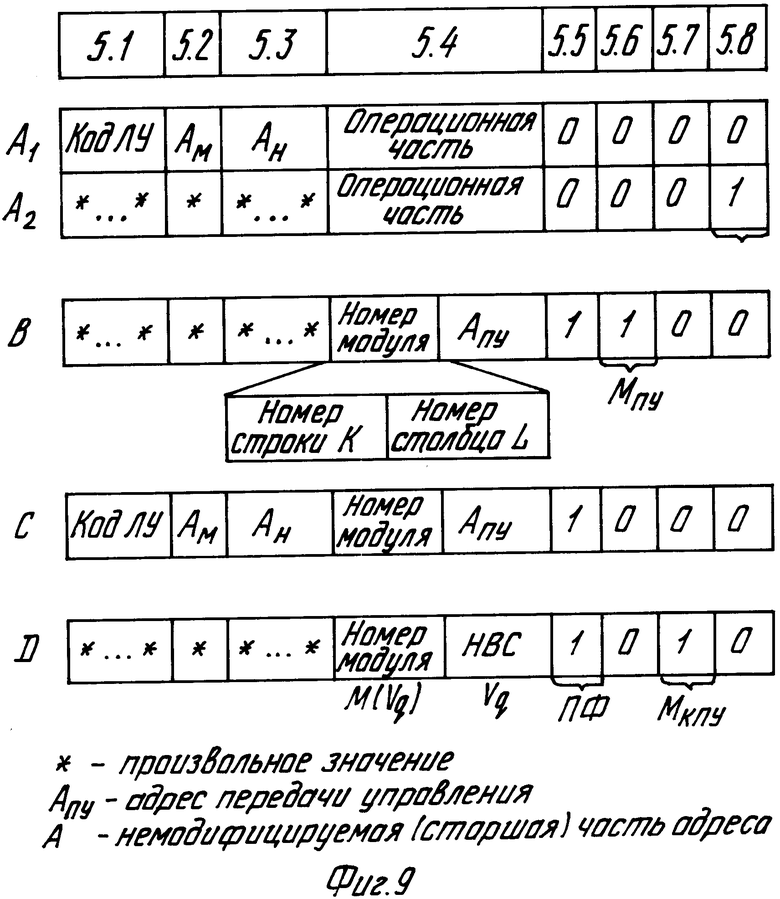

Программа (комплекс программ), реализуемая ДМС, разбивается на множество параллельных и последовательных участков, которые группируются и распределяются между различными модулями. В процессе выполнения выделенных участков программ модули ДМС вырабатывают команды двух типов: операционные (K1), которые передаются непосредственно на вход объекта управления и инициируют исполнение требуемых (микро)операций, и коммуникационные (K2), которые используются для организации взаимодействия различных модулей. Реализация команд типа K2 сводится к формированию и выдаче управляющих сообщений, обеспечивающих инициализацию параллельных или последовательных участков программ или индицирующих завершение выполнения параллельных участков.

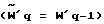

Передача сообщений в ДМС осуществляется транзитным способом. Маршруты передачи сообщений являются фиксированными, а выбор направления ретрансляции сообщений на каждом транзитном отрезке маршрута определяется соотношением кода номера приемника K.L, указываемого в адресной части сообщения, и кода номера текущего транзитного модуля I.J.

Подмножество коммуникационных команд К2 включает команды трех следующих подтипов: команды инициализации последовательных участков (передачи управления) (К21), команды инициализации параллельных участков (К22) и команды - квитанции завершения параллельных участков (К23). Реализация команд типов К21 и К22 состоит в выдаче управляющих сообщений, обеспечивающих соответственно запуск последовательного или параллельного участка программы, закрепленного за определенным модулем сети. Адрес начала инициализируемого участка программы указывается в формате сообщения.

Синхронизация окончания параллельных участков осуществляется на основе предварительной нумерации вершин слияния Vq реализуемых алгоритмов управления (программ) и определения условий синхронизации, а именно указания количества параллельных участков, сходящихся к каждой из вершин слияния Vq (количества ожидаемых событий Wq). Для каждой вершины слияния Vq задается ведущий модуль M(Vq), в качестве которого используется один из модулей, за которым закреплен параллельный участок, завершающийся вершиной Vq. Остальные модули по отношению к указанной вершине рассматриваются как ведомые.

Модули ДМС (независимо от присвоенного им статуса: ведущий или ведомый) после окончания выполнения соответствующих параллельных участков вырабатывают квитанции К23, включающие номер вершины слияния Vq, соответствующей завершенным участкам, и переходят в состояние ожидания. Квинтанции завершения К23 передаются ведущему модулю M(Vq). Модуль M(Vq) принимает квитанции К23 от других модулей и по мере их поступления уменьшает величину W'q - текущее количество ожидаемых событий. В момент поступления последней квинтации и соответственно окончания всех требуемых параллельных участков величина W'q принимает нулевое значение, модуль M(Vq) выходит из состояния ожидания, восстанавливает исходное значение W'q и возобновляет выполнение закрепленных за ним участков программы.

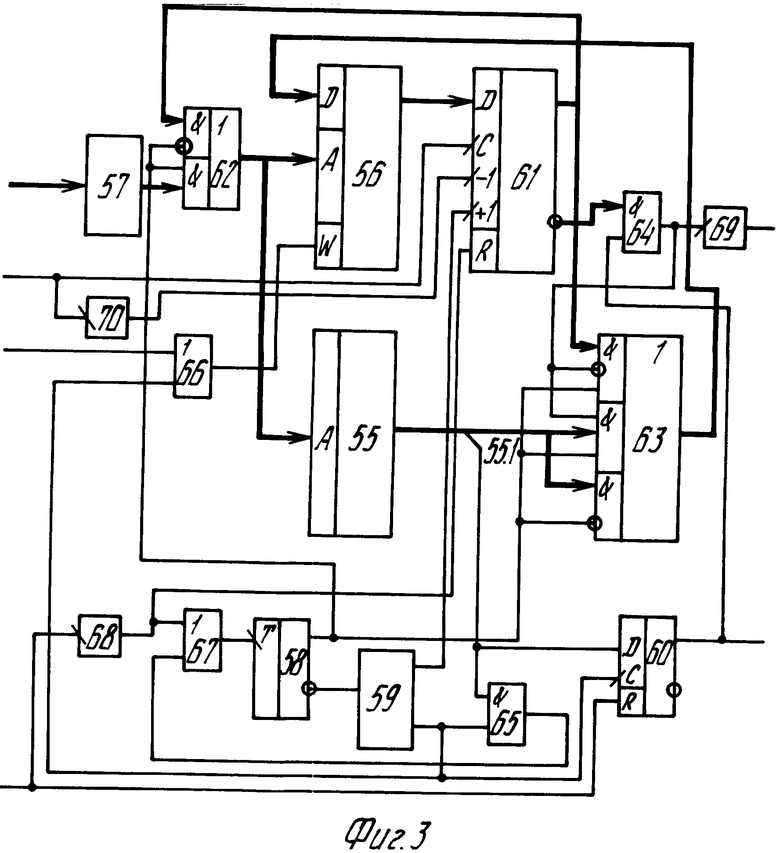

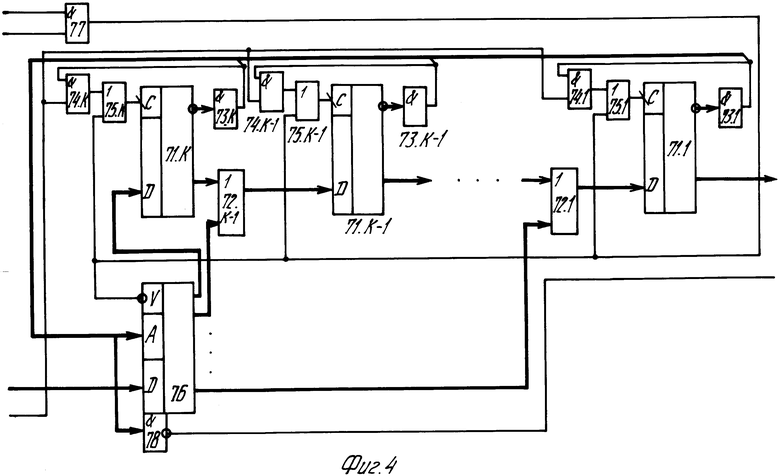

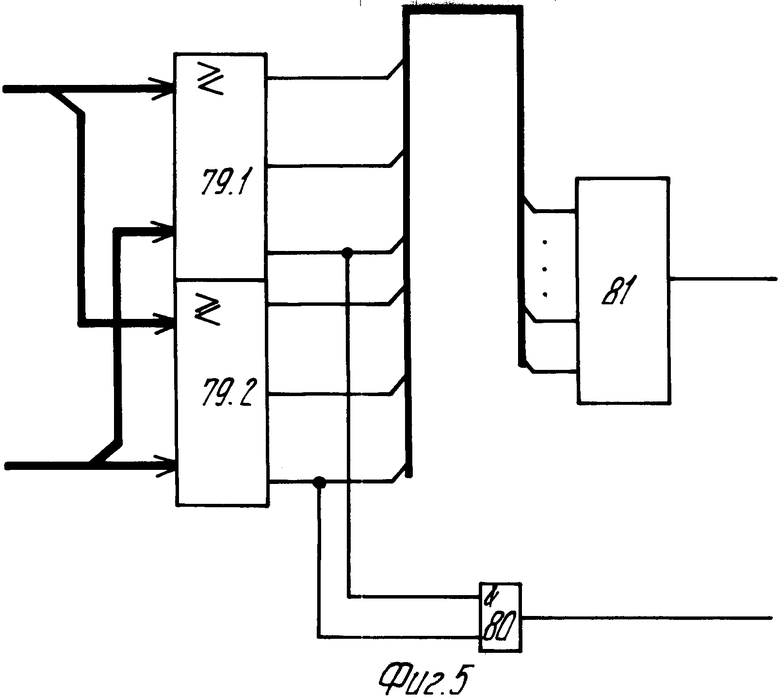

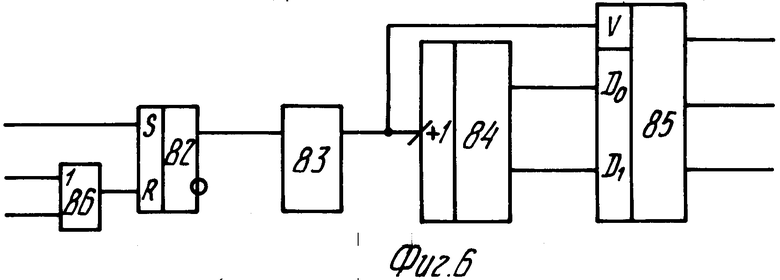

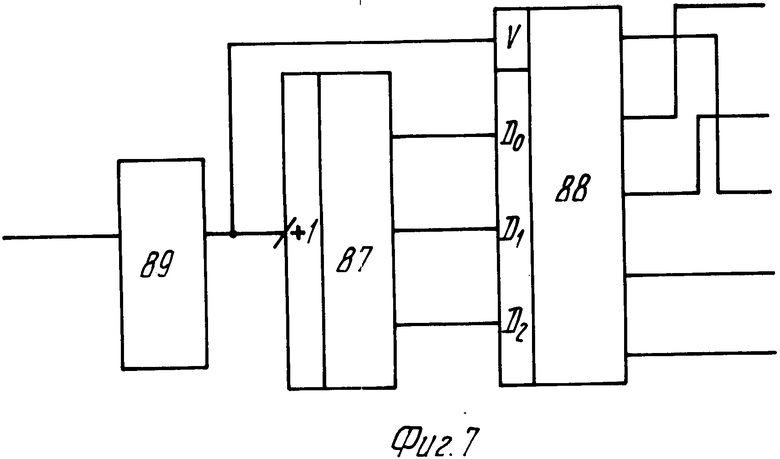

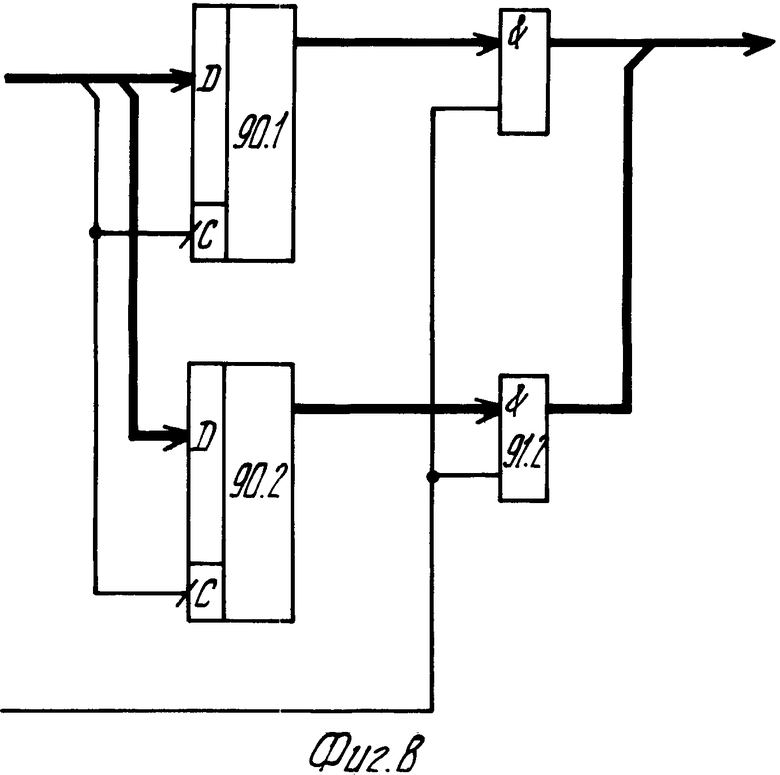

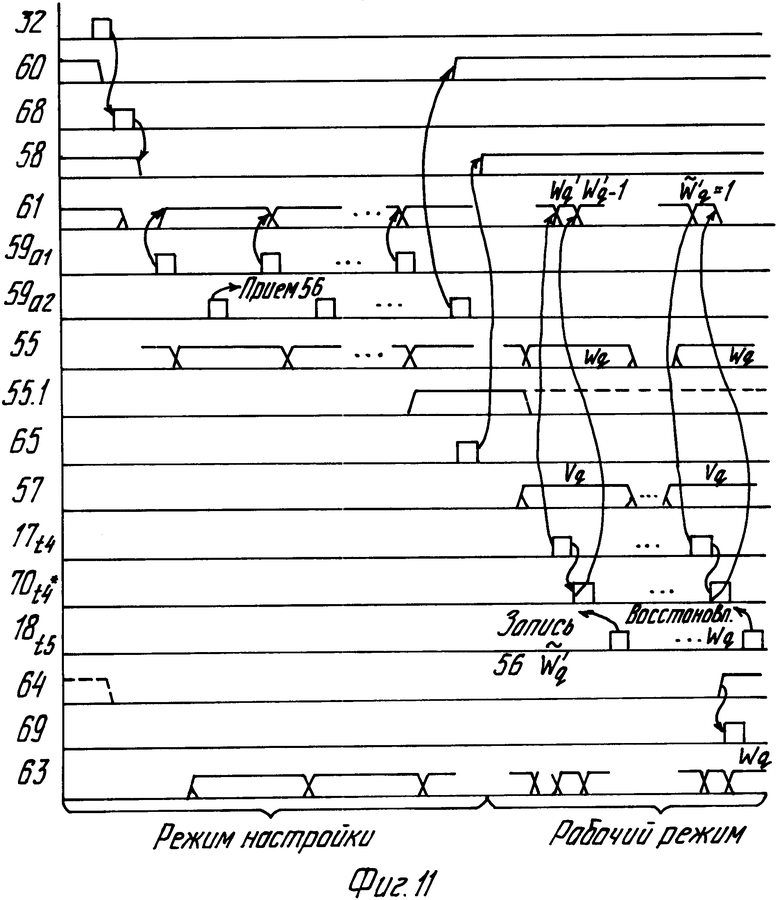

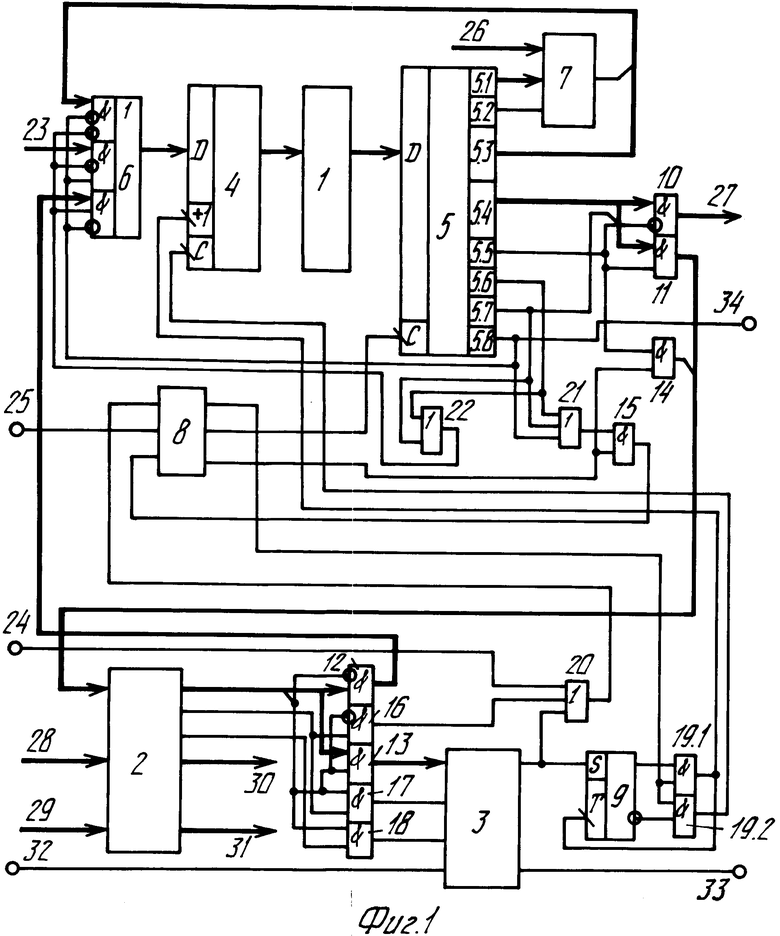

На фиг. 1 изображена функциональная схема модуля ДМС; на фиг. 2 - функциональная схема блока анализа; на фиг. 3 - функицональная схема блока управления синхронизацией параллельных участков; на фиг. 4 - функциональная схема блока памяти сообщений; на фиг. 5 -функциональная схема блока выбора направления передачи сообщения; на фиг. 6 - функциональная схема блока синхронизации; на фиг. 7 - функциональная схема распределителя импульсов, синхронизирующего работу блока анализа; на фиг. 8 - функциональная схема генератора константы; на фиг. 9 - форматы (микро)команд, реализуемые модулями ДМС; на фиг. 10 - структурная схема ДМС; на фиг. 11 - временные диаграммы работы блока управления синхронизацией параллельных участков.

Модуль дискретной микроконтроллерной сети (фиг. 1) содержит блок 1 памяти программ, блок 2 анализа, регистр-счетчик 4 адреса, регистр 5 команд, коммутатор 6 адреса, мультиплексор 7 логических условий, блок 8 синхронизации, первый 10 и второй 11 блоки элементов И, первый элемент И 14, причем выход коммутатора 6 адреса соединен с информационным входом регистра-счетчика 4 адреса, выход которого соединен с адресным входом блока 1 памяти программ, выход которого подключен к информационному входу регистра 5 команд, выходы 5.1 кода логического условия и 5.2 модифицируемой части адреса которого подключены соотвественно к управляющему и первому информационному входам мультиплексора 7 логических условий, второй информационный вход которого является входом 26 логических условий модуля, выход мультиплексора 7 логических условий в объединении с выходом 5.3 немодифицируемой части адреса регистра 5 команд подключен к первому информационному входу коммутатора 6 адреса, первый и второй управляющие входы которого соединены с выходом 5.8 признака конца программы регистра 5 команд, выход 5.5 признака формата команды которого соединен с первым входом элемента И 14, а также с управляющими входами блоков элементов И 10 и 11, первый управляющий вход 25 модуля соединен с первым входом блока 8 синхронизации, первый выход которого подключен к второму входу элемента И 14, второй выход блока 8 синхронизации соединен с входом синхронизации регистра 5 команд, операционный выход 5.4 которого подключен к информационным входам блоков элементов И 10 и 11, выход блока элементов И 10 является операционным выходом 27 модуля, выход блока элементов И 11 в объединении с выходом элемента И 14 подключен к первому входу блока 2 анализа, второй и третий входы которого являются соответственно первым 28 и вторым 29 информационными входами модуля, первый и второй информационные выходы блока 2 анализа являются соответственно первым 30 и вторым 31 информационными выходами модуля, и дополнительно включает блок 3 управления синхронизацией параллельных участков (БУСПУ), триггер 9, третий 12 и четвертый 13 блоки элементов И, второй 15, седьмой 16, шестой 17, пятый 18, третий 19.1 и четвертый 19.2 элементы И, третий 20, первый 21 и второй 22 элементы ИЛИ, причем выход 5.8 признака конца программы регистра 5 команд подключен к выходу 34 конца операции модуля, к третьему управляющему входу коммутатора 6 адреса и к первому входу элемента ИЛИ 21, выход которого соединен с первым входом элемента И 15, вхыод которого подключен к второму входу блока 8 синхронизации, третй выход которого соединен с первыми входами элементов И 19.1 и 19.2, вторые входы которых подключены соответственно к прямому и инверсному выходам триггера 9, выход элемента И 19.1 соединен со счетными входами триггера 9 и регистра-счетчика 4 адреса, выход элемента И 19.2 соединен с входом синхронизации регистра-счетчика 4 адреса, выход 5.6 признака передачи управления регистра 5 команд подключен к второму входу элемента ИЛИ 21 и к первому входу элемента ИЛИ 22, выход которого соединен с четвертым, пятым и шестым упарвляющими входами коммутатора 6 адреса, второй и третий информационные входы которого соединены соответственно с входом 23 кода операции модуля и с выходом блока элементов И 12, выход 5.7 признака конца параллельного участка регистра 5 команд подключен к информационному входу блока элементов И 11, к третьему входу элемента ИЛИ 21 и к второму входу элемента ИЛИ 22, старшие разряды третьего информационного выхода блока 2 анализа соединены с первыми входами блоков элементов И 12 и 13, младший разряд третьего информационного выхода блока 2 анализа соединен с первыми входами элементов И 16, 17 и 18 и с вторыми входами блоков элементов И 12 и 13, первый управляющий выход блока 2 анализа подключен к вторым входам элементов И 16 и 17, второй управляющий выход блока 2 анализа подключен к второму входу элемента И 18, второй управляющий вход 24 модуля соединен с первым входом элемента ИЛИ 20, второй вход которого подключен к выходу элемента И 16, выход элемента ИЛИ 20 подключен к третьему входу блока 8 синхронизации, первый выход которого соединен с вторым входом элемента И 15, выход блока элементов И 13 подключен к информационному входу БУСПУ 3, первый и второй входы синхронизации которого соединены соответственно с выходами элементов И 17 и 18, первый выход БУСПУ 3 подключен к третьему входу элемента ИЛИ 20 и к входу установки триггера 9, второй выход и управляющий вход БУСПУ 3 являются соответственно выходом 33 состояния модуля и входом 32 настройки модуля.

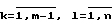

Блок анализа (фиг. 2) предназначен для анализа управляющих сообщений, определения направлений их передачи и выдачи в устанавливаемых в ходе анализа направлениях и содержит блоки памяти сообщений 35 - 37, мультиплексор 38, генератор 39 константы, блок 40 выбора направления передачи сообщения, триггер 41 управления, распределитель 42 импульсов, счетчик 43, дешифратор 44, регистр 45, демультиплексоры 46 и 47, блок элементов И 49, элемент ИЛИ 50, элемент И 51, причем управляющие выходы памяти сообщений 35, 36 и 37 подключены к выходам элемента ИЛИ 50, выход которого соединен с входом установки триггера 41 управления и инверсным входом элемента И 51, выход которого соединен с входом сброса триггера 41 управления, прямой выход которого соединен с входом распределителя 42 импульсов, первый выход которого подключен к входу счетчика 43, второй выход распределителя 42 импульсов соединен с выходом синхронизации регистра 45, третий выход распределителя 42 импульсов соединен с информационным входом демультиплексора 47, выход счетчика 43 соединен с адресным входом мультиплексора 38 и с входом дешифратора 44, выходы с первого по третий которого подключены к управляющим входам блоков памяти сообщений 35-37 соответственно, информационные входы и входы синхронизации записи которых соединены с первым-третьим входами блока анализа соответственно, информационные выходы блоков памяти сообщений 35, 36 и 37 подключены к первому, второму и третьему информационным входам мультиплексора 38 соответственно, выход которого соединен с информационным входом регистра 45, первый выход которого подключен к информационному входу демультиплексора 46 и к первому входу блока 40 выбора направления передачи сообщения, второй вход которого соединен с выходом генератора 39 константы, первый выход блока 40 выбора направления передачи сообщения подключен к адресным входам демультиплексора 46 и 47, а второй выход соединен с первым входом блока элементов И 49, выход которого является третьем информационным выходом блока анализа, второй выход регистра 45 соединен с вторым входом блока элементов И 49 и с информационным входом демультиплексора 46, первый и второй выходы которого подключены соответственно к первому и второму информационным выходом блока анализа, а также дополнительно введенные триггер 48 и элементы И 52.1, 52.2, 53.1, 53.2, причем четвертый выход распределителя 42 импульсов соединен с выходом установки триггера 48, третий выход распределителя 42 импульсов подключен к входам сдвига блоков памяти сообщений 35-37 и к первому входу элемента И 52.1, выход которого является первым управляющим выходом блока анализа, пятый выход распределителя 42 импульсов соединен с прямым входом элемента И 51 и с первым входом элемента И 52.2, выход которого является вторым управляющим выходом блока анализа, пятый выход распределителя 42 импульсов соединен со счетным входом триггера 48, прямой выход которого подключен к управляющему входу генератора 39 константы, информационный вход которого является входом 54 идентификации модуля, второй выход блока 40 выбора направления передачи сообщения соединен с вторыми входами элементов И 52.1 и 52.2 и с инверсными входами элементов И 53.1 и 53.2, прямые входы которых подключены к первому и второму выходам демультиплексора 47 соответственно, выходы элементов И 53.1 и 53.2 соединены с первым и вторым информационными выходами блока анализа соответственно.

Блок управления синхронизацией параллельных участков (БУСПУ) (фиг. 3) предназначен для приема квитанций завершения параллельных участков программ, модификации условий синхронизации, соответствующих различным вершинам слияния, и формирования сигнала запуска модуля при выполнении условий синхронизации параллельных участков и содержит блоки 55 постоянной и 56 оперативной памяти условий синхронизации (БППУС и БОПУС), формирователь 57 адреса, триггер 58 режима, генератор 59 настройки, триггер 60 готовности, счетчик 61, коммутатора 62 и 63, элементы И 64 и 65, элементы ИЛИ 66 и 67, одновибраторы 68, 69 и 70, причем управляющий вход БУСПУ подключен к входу сброса триггера 60 готовности и к входу одновибратора 68, выход которого соединен с входом сброса счетчика 61 и с первым входом элемента ИЛИ 67, выход которого подключен к счетному входу триггера 58 режима, прямой выход которого подключен к прямому и инверсному управляющим входам коммутатора 62 и к первому, второму и третьему управляющим входам коммутатора 63, выход которого подключен к информационному входу БОПУС 56, выход которого соединен с информационным входом счетчика 61, инверсный выход которого соединен с первым входом элемента И 64, прямой выход счетчика 61 соединен с первым информационным входом коммутатора 63 и первым информационным входом коммутатора 62, второй информационный вход которого соединен с выходом формирователя 57 адреса, вход которого является информационным входом БУСПУ, выход коммутатора 62 соединен с адресным входом БОПУС 56 и адресным входом БППУС 55, старшие разряды выхода которого подключены к второму и третьему информационным входам коммутатора 63, а младший разряд (выход) 55.1 соединен с первым входом элемента И 65 и информационным (D) входом триггера 60 готовности, прямой выход которого подключен к второму выходу БУСПУ и к второму входу элемента И 64, выход которого подключен к четвертому и пятому управляющим входам коммутатора 63 и к входу одновибратора 69, выход которого является первым выходом БУСПУ, первый вход синхронизации БУСПУ соединен с выходом синхронизации счетчика 61 и с выходом одновибратора 70, выход которого подключен к вычитающему входу счетчика 61, второй вход синхронизации БУСПУ соединен с первым входом элемента ИЛИ 66, выход которого подключен к входу записи БОПУС 56, инверсный выход триггера 58 режима соединен с входом генератора 59 настройки, первый выход которого соединен с суммирующим входом счетчика 61, второй выход генератора 59 настройки подключен к второму входу элемента ИЛИ 66, к выходу синхронизации триггера 60 готовности и к второму входу элемента И 65, выход которого соединен с вторым входом элемента ИЛИ 67, при этом триггер 60, одновибратор 69 и счетчик 61 срабатывают по фронту, а триггер 58 и одновибраторы 69 и 70 - по срезу управляющих импульсов.

Блок памяти сообщений (БПС) (фиг. 4) служит для приема, хранения и выдачи управляющих сообщений в порядке их поступления и содержит регистры 71.1-71. K (где K - максимальная длина очереди сообщений), блоки элементов ИЛИ 72.1-72. K-1, элементы И 73.1-73.K, 74.1-74.K, элементы ИЛИ 75.1-75.K, демультиплекстор 76, элемент И 77, элемент И-НЕ 78, причем информационный вход демультиплестора 76 является информационным входом БПС, выходы с первого по (K-1)-й демультиплексора 76 соединены с первыми входами блоков элементов ИЛИ 72.1-72. K-1 соответственно, вторые входы которых подключены к прямым выходам регистров 71.2-71.K соответственно, выходы блоков элементов ИЛИ 72.1-72. K-1 подключены к информационным входам регистров 71.1-71.K-1 соответственно, K-й выход демультиплекстора 76 подключен к информационному входу регистра 71.K, вход синхронизации записи БПС подключен к первым входам элементов И 74.1-74.K, выходы которых соединены с первыми входами элементов ИЛИ 75.1-75. K соответственно, выходы которых соединены с входами синхронизации регистров 71.1-71.K соответственно, инверсные выходы которых подключены к входам элементов И 73.1-73.K соответственно, выходы которых соединены с адресным входом демультиплексора 76, с вторыми входами элементов И 74.1-74.K соответственно, а также с входами элемента И-НЕ 78, выход которого является управляющим выходом БПС, первый и второй входы элемента И 77 являются соответственно входом сдвига и управляющим входом БПС, выход элемента И 77 подключен к вторым входам элементов ИЛИ 75.1-75.K и к управляющему входу демультиплекстора 76, прямой выход регистра 71.1 является информационным выходом БПС.

Блок выбора направления передачи сообщения (БВНПС) (фиг. 5) служит для формирования кода направления передачи сообщений и содержит схемы сравнения 79.1 и 79.2, элемент И 80 и неполный дешифратор 81, причем первые и вторые входы схем сравнения 79.1 и 79.2 подключены соответственно к второму и первому входам БВНПС, а выходы соединены с входами дешифратора 81, выход которого является первым выходом блока, выходы равенства схем сравнения 79.1 и 79.2 подключены соответственно к первому и второму входам элемента И 80, выход которого является вторым выходом БВНПС.

Блок синхронизации (БС) (фиг. 6) предназначен для формирования трех сдвинутых относительно друг друга импульсных последовательностей, синхронизирующих работу различных узлов модуля, и включает триггер 82, генератор 83 импульсов, счетчик 84, дешифратор 85 и элемент ИЛИ 86, причем первый вход элемента ИЛИ 86 является первый входом БС, выход элемента ИЛИ 86 соединен с входом сброса триггера 82, вход установки которого является третьим входом БС, прямой выход триггера 82 подключен к управляющему входу генератора 83 импульсов, выход которого подключен к управляющему входу дешифратора 85 и к счетном у входу счетчика 84, выход которого соединены с соответствующими информационными входами дешифратора 85, выходы с первого по третий которого являются выходами с третьего по первый БС соответственно, а второй вход элемента ИЛИ 86 дополнительно является вторым входом БС.

Распределитель импульсов (РИ) (фиг. 7) предназначен для формирования пяти сдвинутых относительно друг друга импульсных последовательностей, синхронизирующих работу элементов блока анализа и блока управления синхронизацией параллельных участков (в рабочем режиме), и содержит счетчик 87, дешифратор 88 и генератор 89 импульсов, вход которого является входом РИ, а выход подключен к управляющему входу дешифратора 88 и счетному входу счетчика 87, выходы которого соединены с соответствующими информационными входами дешифратора 88, первый, второй и третий выходы которого являются соответственно первым, вторым и пятым выходами РИ, четвертый и пятый выходы дешифратора 88 дополнительно являются четвертым и третьим выходами РИ соответственно.

Генератор константы (ГК) (фиг. 8) реализует функции приема, хранения и выдачи кода I.J номера модуля и включает регистры 90.1, 90.2 и блоки элементов И 91.1 и 92.2, причем входы регистров 90.1 и 90.2 образуют информационный вход ГК, а выходы подключены к информационным входам блоков элементов И 91.1 и 91.2 соответственно, управляющие входы которых соединены с управляющим входом ГК, а выходы образуют выход ГК.

Назначение элементов дополнительно введенного блока управления синхронизацией параллельных участков (фиг. 3) состоит в следующем.

Блок 55 постоянной памяти условий синхронизации (БППУС) служит для постоянного хранения и выдачи кодов исходных условий синхронизации Wq, соответствующих различным вершинам слияния Vq, для которых текущий модуль является ведущим. Информация на выходе блока 55 появляется сразу после установления на его адресном входе соответствующего адреса.

Блок 56 оперативной памяти условий синхронизации (БОПУС) служит для хранения, выдачи и приема кодов текущих условий синхронизации W'q, соответствующих вершинам слияния параллельных участков Vq, закрепленным за данным модулем. Информация на выходе блока 56 появляется сразу после установления на его адресном входе соответствующего адреса, а запись модифицированных условий синхронизации  в блок 56 осуществляется в момент подачи на вход записи W импульса синхронизации.

в блок 56 осуществляется в момент подачи на вход записи W импульса синхронизации.

Формирователь 57 адреса предназначен для преобразования кода номера вершины слияния Vq в адрес A(Vq) ячейки БОПУС 56 и ячейки БППУС 55, в которых размещены коды соответственно текущего W'q и исходного Wq условий синхронизации, соответствующих вершине Vq. Формирователь 57 может выполняться на основе программируемой логической матрицы (ПЛМ).

Триггер 58 режима служит для индикации текущего режима работы блока управления синхронизацией параллельных участков (устройства) и управления работы генератора 59 и коммутаторов 62, 63. Триггер 58 переключается в новое состояние по срезу (заднему фронту) импульса на его входе.

Генератор 59 настройки обеспечивает формирование двух сдвинутых относительно друг друга во времени импульсных последовательностей a1 и 2a, синхронизирующих работу блока управления синхронизацией параллельных участков в режиме настройки (перезаписи информации из блока 55 в блок 56).

Триггер 60 готовности служит для формирования сигнала окончания процесса настройки устройства (сигнала готовности), а также блокировки элемента И 64 и срабатывает по положительному перепаду уровня сигнала на его выходе синхронизации (C).

Счетчик 61 реализует две следующие функции:

а) обеспечивает формирование адреса в ходе перезаписи информации из блока 55 в блок 56 (в режиме настройки устройства);

б) обеспечивает формирование кодов модифицированных условий синхронизации  при поступлении квитанций окончания параллельных участков от различных модулей ДМС (в рабочем режиме).

при поступлении квитанций окончания параллельных участков от различных модулей ДМС (в рабочем режиме).

Модифицированное условие синхронизации образуется в результате считывания из блока 56 текущего кода W'q и уменьшения его на единицу  . Счетчик 61 является реверсивным, работает в режиме приема информации в параллельном коде, в режиме прямого счета (+1) и в режиме обратного счета (-1) и срабатывает по фронту соответствующих импульсов синхронизации.

. Счетчик 61 является реверсивным, работает в режиме приема информации в параллельном коде, в режиме прямого счета (+1) и в режиме обратного счета (-1) и срабатывает по фронту соответствующих импульсов синхронизации.

Коммутатор 62 служит для коммутации адресных входов блоков 55 и 56 либо с прямым выходом счетчика 61 (режим настройки), либо с выходом формирователя 57 адреса (рабочий режим) в зависимости от состояния триггера 58 режима.

Элемент И 64 предназначен для формирования сигнала, подтверждающего окончание требуемых параллельных участков, т.е. выполнение условия синхронизации  .

.

Коммутатор 63 служит для коммутации информационного входа блока 56 либо с прямым выходом счетчика 61 (рабочий режим), либо с выходом блока 55 (режим настройки или рабочий режим: восстановление кода исходного условия синхронизации Wq в блоке 56 при окончании всех требуемых параллельных участков) в зависимости от состояния триггера 58 и уровня сигнала на выходе элемента И 64.

Элемент И 65 предназначен для формирования сигнала переключения триггера 58 при завершении работы устройства в режиме настройки (перезаписи кодов условий синхронизации из блока 55 в блок 56). Факт окончания процесса настройки отмечается появлением единичного признака на специальном выходе 55.1 блока 55.

Одновибратор 68 служит для формирования импульса l начальной установки счетчика 61 и переключения триггера 58 режима и вырабатывает импульс по отрицательному перепаду уровня сигнала на его входе.

Элемент ИЛИ 66 служит для формирования импульса синхронизации записи информации в блок 56.

Элемент ИЛИ 67 обеспечивает объединение сигналов переключения триггера 58 режима, поступающих с выходов элемента И 65 и одновибратора 68.

Одновибратор 69 обеспечивает формирование импульса пуска модуля при выполнении условия синхронизации параллельных участков  и срабатывает по положительному перепаду уровня сигнала на его входе.

и срабатывает по положительному перепаду уровня сигнала на его входе.

Одновибратор 70 служит для формирования импульса, инициирующего уменьшение содержимого счетчика 61 на единицу, и срабатывает по отрицательному перепаду уровня сигнала на его входе.

Дискретная микроконтроллерная сеть (ДМС) состоит из m•n однотипных модулей, объединенных в матричную структуру (фиг. 10), причем первый информационный вход 28 модуля i.j,  , соединен с вторым информационным выходом 31 модуля i, j-1, а первый информационный вход 28 модуля i.1 подключен к второму информационному выходу 31 модуля i.n, второй информационный вход 29 модуля k.1,

, соединен с вторым информационным выходом 31 модуля i, j-1, а первый информационный вход 28 модуля i.1 подключен к второму информационному выходу 31 модуля i.n, второй информационный вход 29 модуля k.1,  , соединен с первым информационным выходом 30 модуля k+1. l, а второй информационный вход 29 модуля m.l подключен к первому информационному выходу 30 модуля 1.l.

, соединен с первым информационным выходом 30 модуля k+1. l, а второй информационный вход 29 модуля m.l подключен к первому информационному выходу 30 модуля 1.l.

Учитывая идентичность модулей, образующих ДМС, работу сети рассмотрим на примере функционирования одного из модулей.

Первоначально (фиг. 1-8) регистры 71.1-71. K блоков памяти сообщений 35-37, счетчики 43, 84 и 87, триггеры 9, 41, 48, 82 находятся в нулевом состоянии, триггеры 58 и 60 - в единичном состоянии, счетчик 61 - в состоянии "11...1", все разряды регистра 5 за исключением разряда 5.8, установленного в состояние логической единицы, находятся в состоянии логического нуля, а состояние регистра-счетчика 4, регистра 45, регистров 90.1 и 90.2 не определено (цепи начальной установки на фиг. 1-8 условий не показаны). В блоке 1 (в ячейках с ненулевыми адресами) размещены команды форматов, представленных на фиг. 9, образующие параллельные и последовательные участки программ, закрепленные за рассматриваемым модулем. В ячейках блока 55 размещены коды условий синхронизации (коды Wq) вершин слияния Vq, для которых текущий модуль является ведущим. Состояние ячеек блока 56 не определено (произвольно).

Функционирование ДМС начинается с настройки ее модулей, которая реализуется устройством управления верхнего уровня (УУВУ), например центральным процессором, и включает два этапа. На первом этапе настройки осуществляется установка (загрузка) номеров модулей матричной структуры, на втором - перезапись информации из ячеек блоков 55 в соответствующие ячейки блоков 56.

Этап 1. Код номера текущего модуля I.J формируется УУВУ и в сопровождении импульса синхронизации подается на вход 54 модуля (фиг. 2). С входа 54 код номера модуля I.J передается на информационный вход генератора 39 констант и далее код номера строки модуля I поступает (фиг. 8) на информационный вход регистра 90.1, а код номера столбца J - на информационный вход регистра 90.2. Импульс синхронизации с информационного выхода генератора 39 поступает на входы синхронизации регистров 90.1, 90.2 и обеспечивает установку (запись) кода I.J. Аналогичным образом осуществляется установка номеров других модулей.

Этап 2. Реализация данного этапа настройки начинается с приходом на вход 32 модуля импульса настройки n (фиг. 1). Импульс n передается на управляющий вход блока 3 (БУСПУ) и, поступая (фиг. 3) на вход сброса триггера 60, переключает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 60 поступает на выход 33 модуля и индицирует тем самым начало процесса настройки. Этот же сигнал поступает на второй вход элемента И 64 и формирует (подтверждает) на его выходе сигнал логического нуля.

Одновременно импульс настройки n с управляющего входа БУСПУ поступает на вход одновибратора 68 и задним фронтом (срезом) возбуждает на его выходе импульс l. Импульс l распространяется на вход сброса счетчика 61 и устанавливает его в нулевое состояние. В то же время импульс l с выхода одновибратора 68 через элемент ИЛИ 67 проходит на счетный вход триггера 58 и срезом переводит его в состояние логического нуля, соответствующее режиму настройки модуля. Нулевой сигнал с прямого выхода триггера 58 поступает на управляющие входы коммутаторов 62 и 63 и коммутирует выход первого с прямым выходом счетчика 61, а выход второго - с выходом блока 55. Одновременно единичный сигнал с инверсного выхода триггера 58 поступает на вход генератора 59 и разрешает формирование на его выходах двух сдвинутых относительно друг друга импульсных последовательностей a1 и a2.

Первый импульс a1 с первого выхода генератора 59 поступает на суммирующий вход счетчика 61 и фронтом устанавливает его в состояние "00...01", т.е. инициирует операцию прямого счета (инкремента). Код "00...01" с прямого выхода счетчика 61 через коммутатор 62 передается на адресные входы блоков 55 и 56. Код количества ожидаемых событий Wr, зафиксированный в ячейке блока 55 с адресом "00...01" и соответствующий одной из вершин слияния Vr, закрепленных за текущим модулем, появляется на выходе блока 55 и через коммутатор 63 передается на информационный вход блока 56. Одновременно на младшем выходе (разряде выхода) 55.1 блока 55 формируется сигнал-метка Z, определяющий момент окончания процесса настройки текущего модуля.

Первоначально допустим, что Z = "0".

Нулевой сигнал с выхода 55.1 блока 55 закрывает элемент И 65, а также поступает на D-вход триггера 60. Импульс a2 с второго выхода генератора 59 подается на вход синхронизации триггера 60 и подтверждает его нулевое состояние. Одновременно импульс a2 через элемент ИЛИ 66 проходит на вход записи блока 56 и обеспечивает запись кода Wr в ячейку с адресом "00...01". Поскольку элемент 65 заблокирован нулевым сигналом с выхода 55.1 блока 55, на его выходе сохраняется нулевой уровень сигнала, что исключает срабатывание триггера 58 и переключение его в единичное состояние. С появлением на выходе генератора 59 очередного импульса a1 содержимое счетчика 61 вновь увеличивается на единицу; код "00...010" с прямого выхода счетчика 61 через коммутатор 62 проходит на адресные входы блоков 55 и 56, после чего осуществляется перезапись информации из ячейки с адресом "00...010" блока 55 в соответствующую ячейку блока 56. Более аналогично производится перезапись информации по адресу "00...011, "00...0100" и т.д.

Если Z = "1", т.е. перезаписываемое в текущем такте слово является последним, то единичный сигнал с выхода 55.1 блока 55 открывает элемент 65 и, кроме того, поступает на D-вход триггера 60. Импульс а2 с второго выхода генератора 59 поступает на вход синхронизации триггера 60 и фронтом устанавливает данный триггер в единичное состояние. Сигнал логической единицы с прямого выхода триггера 60 передается на выход 33 модуля и сообщает УУВУ о завершении процесса настройки. Этот же сигнал открывает элемент 64.

Одновременно импульс a2 с второго выхода генератора 59 через элемент ИЛИ 66 проходит на вход записи блока 56 и обеспечивает запись последнего кода Wr, считываемого из блока 55 и поступающего на информационный вход блока 56 через коммутатор 63. Кроме того, импульс a2 через открытый элемент 65 и элемент ИЛИ 67 подается на счетный вход триггера 58 и срезом возвращает его в исходное состояние (состояние логической единицы), соответствующее рабочему режиму рассматриваемого блока. Единичный сигнал с прямого выхода триггера 58 поступает на управляющие входы коммутаторов 62 и 63 и настраивает коммутатор 62 на прием информации с выхода формирователя 57, а коммутатор 63 -на прием информации с прямого выхода счетчика 61 или с выхода блока 55 в зависимости от уровня потенциала на выходе элемента 64. Нулевой сигнал с инверсного выхода триггера 58 выключает генератор 59, и модуль выходит из режима настройки. Временные диаграммы работы блока управления синхронизацией параллельных участков в режиме настройки показаны на фиг. 11. Процесс настройки микроконтроллерной сети в целом завершается в момент появления единичных сигналов на выходах 33 всех (или определенной группы требуемых) модулей.

После реализации режима настройки сети УУВУ формирует код операции и подает указанный код на вход 23 модуля, за которым закреплен начальный последовательный участок, определяя тем самым начальный адрес выполняемой программы (фиг. 1).

Код операции (КОП) с входа 23 модуля поступает на второй информационный вход коммутатора 6 и, так как на его втором и пятом управляющих входах присутствуют соответственно единичный и нулевой сигналы (обусловленные нулевым состоянием разрядов 5.6 и 5.7, а также единичным состоянием разряда 5.8 регистра 5), передается на информационный вход регистра-счетчика 4. Одновременно на вход 24 модуля подается импульс "Пуск". Импульс "Пуск" через элемент ИЛИ 20 поступает (фиг. 6) на вход установки триггера 82 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 82 поступает на управляющий вход генератора 83 и разрешает формирование на его выходе импульсной последовательности m.

Первый импульс с выхода генератора 83 поступает на счетный выход счетчика 84 и управляющий вход генератора 85. Счетчик 84 устанавливается в состояние "01". Код "01" с выхода счетчика 84 поступает на информационные входы дешифратора 85 и возбуждает единичный сигнал на его первом выходе. С исчезновением единичного сигнала на выходе генератора 83 на выходе дешифратора 85 восстанавливается нулевой уровень сигнала. Второй импульс с выхода генератора 83 переключает счетчик в состояние "10" и обусловливает появление единичного уровня сигнала на втором выходе дешифратора 85. Аналогично после появления на выходе генератора 83 третьего импульса счетчик 84 переводится в состояние "11" и обеспечивает образование единичного уровня сигнала на третьем выходе дешифратора 85. С приходом трех очередных импульсов последовательности m процесс возбуждения единичных сигналов на выходах дешифратора 85 повторяется.

Таким образом, на выходах дешифратора 85 (блока синхронизации) начинается формирование трех сдвинутых относительно друг друга импульсных последовательностей П1, П2 и П3.

Импульс П1 с третьего выхода блока 8 подается на первые входы элементов И 19.1 и 19.2, на вторых входах которых находятся сигналы, снимаемые соответственно с прямого и инверсного выходов триггера 9 (фиг. 1). Поскольку триггер 9 находится в исходном (нулевом) состоянии, импульс П1 проходит через элемент 19.2 и, поступая далее на вход синхронизации регистра-счетчика 4, срезом фиксирует в регистре-счетчике 4 присутствующий на его информационном входе КОП. После записи КОП поступает на адресный вход блока 1 и формирует на его выходе первую команду начального последовательного участка выполняемой программы. Команда с выхода блока 1 поступает на информационный вход регистра 5 и в момент возникновения среза очередного импульса П2 на втором выходе блока 8 записывается в регистр.

В дальнейшем ход работы модуля определяется форматом считанной команды (фиг. 9). Возможны следующие варианты.

Вариант 1. Считанная команда имеет формат А1. В этом случае на выходах 5.5-5.8 устанавливается нулевой уровень сигнала. Нулевой согнал - признак формата команды - с выхода 5.5 регистра 5 подается на управляющие входы блоков 10 и 11 и, будучи разрешающим для блока 10 и запрещающим для блока 11, обеспечивает передачу операционной части команды с выхода 5.4 регистра 5 на выход 27 модуля и возбуждение требуемых (микро)операций.

Одновременно осуществляется формирование исполнительного адреса следующей команды.

Код опрашиваемого логического условия (ЛУ) с выхода 5.1 и модифицируемый разряд адреса (Ам) с выхода 5.2 регистра 5 поступают соответственно на управляющий и первый информационный входы мультиплексора 7, на втором информационном входе которого формируются сигналы логических условий, снимаемые с различных датчиков или с выходов специальных схем образования признаков управляемого объекта. Если код ЛУ является нулевым, то на выход мультиплексора 7 передается значение модифицируемого разряда адреса, в противном случае на выход мультиплексора 7 подается значение логического условия, определяемого заданным кодом ЛУ. Сигнал с выхода мультиплексора 7 объединяется с немодифицируемой (старшей) частью адреса с выхода 5.3 регистра 5 и образует исполнительный адрес следующей команды. Этот адрес подается на первый информационный вход коммутатора 6 и, поскольку на выходе 5.8, а также на выходах 5.6 и 5.7 (а значит, и на выходе элемента 22) регистра 5 присутствуют сигналы логического нуля, передается на информационный вход регистра-счетчика 4.

Нулевой сигнал с выхода 5.5 регистра 5 закрывает элемент И 14, а нулевые сигналы с выходов 5.6 - 5.8 формируют нулевой уровень сигнала на выходе элемента ИЛИ 21 и соответственно блокируют элемент И 15. В связи с этим очередной импульс П3, появляющийся на выходе блока 8, не проходит на выходы элементов И 14 и 15 и, следовательно, не вызывает изменения режима функционирования модуля.

Очередной импульс П1 вновь через открытый элемент И 19.2 передается на вход синхронизации регистра-счетчика 4 и фиксирует ранее сформированный на его информационном входе адрес следующей команды. Адрес с выхода регистра-счетчика 4 поступает на адресный вход блока 1 и обеспечивает считывание очередной команды.

Процедура обработки считываемой команды ничем не отличается от процедуры обработки первой команды и поэтому далее модуль функционирует аналогично ранее рассмотренному.

Вариант 2. Считанная команда имеет формат А2 (фиг. 9). На выходе 5.8 регистра 5 формируется единичный сигнал - метка конца программы (Мкп). Данный сигнал поступает на выход 34 конца операции модуля и инициирует окончание текущей операции (программы). Одновременно этот же сигнал через элемент ИЛИ 21 подается на первый вход элемента И 15, а также поступает на первый, второй и третий управляющие входы коммутатора 6. На выходах 5.5 - 5.7 регистра 5 образуются сигналы логического нуля.

Нулевой сигнал с выхода 5.5 регистра 5 поступает на управляющий вход блока элементов И 10 и обеспечивает передачу операционной части команды (или, возможно, нулевого кода) с выхода 5.4 регистра 5 на выход 27 модуля. Этот же сигнал запрещает прохождение информации через блок элементов И 11, а также блокирует элемент И 14. Нулевые сигнала с выходов 5.6 и 5.7 регистра 5 поступают на входы элемента ИЛИ 22 и формируют на его выходе сигнал логического нуля. Нулевой сигнал с выхода элемента 22 поступает на четвертый, пятый и шестой управляющие входы коммутатора 6 и совместно с единичным сигналом с выхода 5.8 регистра 5 настраивает коммутатор 6 на прием кода очередной операции с входа 23 модуля.

Очередной импульс П3 с первого выхода блока 8 синхронизации через открытый элемент И 15 проходит на второй вход блока 8 и далее (фиг. 6) через элемент ИЛИ 86 подается на вход сброса триггера 82 и переключает его в исходное состояние. Нулевой сигнал с прямого выхода триггера 82 останавливает генератор 83. Таким образом, формирование импульсных последовательностей на выходах блока 8 прекращается и модуль (а соответственно и ДМС в целом) переходит в состояние ожидания задания на выполнение очередной операции.

Вариант 3. Считанная команда имеет формат B (фиг. 9). Рассматриваемый модуль переходит в режим передачи управления другому аналогичному модулю ДМС. На выходах 5.5 и 5.6 регистра 5 появляются единичные, на выходах 5.7 и 5.8 - нулевые сигналы, а на выходе 5.4 регистра 5 формируется управляющее сообщение, включающее код номера модуля, которому передается управление, и адрес передачи управления (адрес начала инициализируемого последовательного участка программы).

Единичный сигнал - метка передачи управления (Мпу) - с выхода 5.6 регистра 5 через элемент ИЛИ 21 поступает на первый вход элемента И 15. Кроме того, указанный сигнал через элемент ИЛИ 22 подается на четвертый, пятый и шестой управляющие входы коммутатора 6, на остальные управляющие входы которого передается нулевой сигнал с выхода 5.8 регистра 5. В результате вход коммутатора 6 подключается к выходу блока элементов И 12, чем обеспечивается возможность последующего приема управления от другого модуля ДМС.

В то же время единичный сигнал - признак формата команды (ПФ) с выхода 5.5 регистра 5 поступает на управляющий вход блока элементов И 10 и формирует на его выходе нулевой код. Этот же сигнал открывает элемент И 14 и блок элементов И 11. Управляющее сообщение, сформированное на выходе 5.4 регистра 5, в объединении с нулевым сигналом с выхода 5.7 регистра 5 (выполняющим функцию признака формата вырабатываемого сообщения (коммутационной команды)) через блок 11 поступает на первый вход блока 2 анализа с целью дальнейшего анализа и передачи адресату (приемнику). Очередной импульс П3 с первого выхода блока 8 синхронизации проходит через открытый элемент И 14 на первый вход блока 2 анализа и синхронизирует прием выдаваемого сообщения (работа блока 2 анализа детально рассматривается ниже).

Одновременно импульс П3 через элемент И 15 проходит на второй вход блока 8, через элемент ИЛИ 86 поступает на вход сброса триггера 82, переводит его в нулевое состояние и тем самым выключает генератор 83. Текущий модуль переходит в пассивное состояние, в котором находится вплоть до поступления управляющего сообщения, содержащего адрес передачи управления, от другого модуля.

Вариант 4. Считанная команда имеет формат C (фиг. 9). Текущий модуль переходит в режим запуска параллельного участка программы, закрепленного за другим модулем ДМС. Отличие рассматриваемого режима работы модуля от режима инициализации последовательного участка (передачи управления) состоит в том, что текущий модуль после выдачи соответствующего управляющего сообщения не переходит в пассивное состояние, а приступает к выполнению закрепленного за ним параллельного участка программы.

На выходах 5.6 - 5.8 регистра 5 устанавливается нулевой уровень сигнала, на выходе 5.5 появляется единичный сигнал - признак формата команды, а на выходе 5.4 формируется управляющее сообщение, формат которого аналогичен формату сообщения, вырабатываемого в режиме передачи управления. Единичный сигнал с выхода 5.5 регистра 5 закрывает блок элементов И 10 и запрещает передачу операционной части считанной команды на выход 27 модуля. Этот же сигнал открывает элемент И 14 и блок элементов И 11 и аналогично рассмотренному обеспечивает передачу управляющего сообщения на первый вход блока 2 анализа.

Сигналы логического нуля с выходов 5.6 и 5.7 регистра 5 поступают на входы элемента ИЛИ 22, формируют на его входе сигнал логического нуля и совместно с нулевым сигналом с выхода 5.8 регистра 5 настраивают коммутатор 6 на прием информации с его первого информационного входа. В то же время нулевые сигналы с выходов 5.6-5.8 регистра 5 поступают на входы элемента ИЛИ 21, обусловливают появление на выходе элемента ИЛИ 21 сигнала логического нуля и тем самым блокируют элемент И 15.

Очередной импульс П3 с первого выхода блока 8 проходит через элемент И 14 и обеспечивает прием выдаваемого управляющего сообщения блоком 2 анализа. Поскольку элемент И 15 заблокирован нулевым сигналом с выхода элемента ИЛИ 21, импульс П3 не передается на его выход и, следовательно, не вызывает перехода текущего модуля в пассивное состояние, что имело место в предыдущем случае.

Параллельно с выдачей управляющего сообщения на первый вход блока 2 анализа осуществляется формирование исполнительного адреса следующей команды. Процедура формирования адреса следующей команды полностью совпадает с процедурой формирования адреса при обработке команд формата А1 (см. выше). Адрес следующей команды, получаемый объединением старших разрядов адреса с выхода 5.3 регистра 5 с младшим (модифицируемым) разрядом с выхода мультиплексора 7, через коммутатор 6 проходит на информационный вход регистра-счетчика 4. Очередной импульс П1 с третьего выхода блока 8 через элемент И 19.2 поступает на вход синхронизации регистра-счетчика 4 и срезом фиксирует в нем адрес следующей команды. Указанный адрес с выхода регистра-счетчика 4 подается на адресный вход блока 1 и обеспечивает считывание очередной команды. Текущий модуль приступает к реализации параллельного участка программы и в дальнейшем функционирует аналогично работе модуля при выполнении начального последовательного участка.

Вариант 5. Считанная команда имеет формат D (фиг. 9). В этом случае модуль завершает выполнение параллельного участка программы и вырабатывает соответствующую команду-квитанцию. На выходах 5.5 и 5.7 регистра 5 появляется единичный сигнал, на выходах 5.6 и 5.8 - нулевой сигнал, а на выходе 5.4 формируется управляющая квитанция, подтверждающая завершение выполнения параллельного участка и содержащая номер соответствующей вершины слияния Vq (вершины, к которой сходится выполненный участок), а также номер модуля M(Vq), являющегося ведущим для вершины слияния Vq (в частном случае этим модулем может быть рассматриваемый модуль).

Единичный сигнал - признак формата - с выхода 5.5 регистра 5 открывает элемент И 14 и блок 11, одновременно закрывая блок 10 и запрещая тем самым передачу информации на выход 27 модуля. Единичный сигнал - метка конца параллельного участка программы (Мкпу) - с выхода 5.7 регистра 5 через элемент ИЛИ 21 открывает элемент И 15 и, кроме того, через элемент ИЛИ 22 поступает на четвертый, пятый и шестой управляющие входы коммутатора 6 и совместно с нулевым сигналом с выхода 5.8 регистра 5 настраивает коммутатор 6 на прием информации с выхода блока элементов И 12 (при последующей возможной передаче управления от другого устройства).

Одновременно квитанция с выхода 5.4 регистра 5 совместно с единичной меткой Мкпу с выхода 5.7 регистра 5 через блок 11 поступает на первый вход блока 2 анализа. Очередной тактовый импульс П3 через элемент И 14 проходит на первый вход блока 2 анализа и синхронизирует прием вырабатываемой кавитации. Этот же импульс проходит через открытый элемент И 15 на второй вход блока 8 и выключает генератор 83 (фиг. 6), останавливая, таким образом, процесс формирования импульсов П1, П2, П3. Текущий модуль переходит в пассивное состояние и ожидает либо поступления адреса передачи управления от другого модуля ДМС (в случае, если текущий модуль по отношению к вершине слияния Vq является ведомым), либо появления единичного сигнала, отмечающего окончание процесса синхронизации требуемых параллельных участков, на первом выходе блока 3 (если текущий модуль по отношению к вершине Vr является ведущим).

Таким образом, каждый модуль ДМС в процессе функционирования наряду с формированием и выдачей команд управления на выход 27 вырабатывает управляющие сообщения двух типов: инициализации последовательных или параллельных участков и индикации завершения параллельных участков, отмечаемые соответственно нулевым и единичным признаками (признаками формата коммутационной команды на выходе 5.7 регистра 5) и условно обозначаемые в дальнейшем соответственно как S1 и S2.

Рассмотрим работу модуля ДМС в режиме приема, анализа и передачи (ретрансляции) управляющих сообщений.

Управляющие сообщения S1 и S2, вырабатываемые текущим модулем при обработке команд форматов B, C, D, поступают на первый вход блока 2 анализа, а сообщения, передаваемые соседними модулями, подаются на входы 28 и 29 модуля и далее поступают на второй и третий входы блока 2 анализа (фиг. 1).

Очередное сообщение с первого (второго, третьего) входа блока анализа (фиг. 2) поступает на информационный вход блока памяти сообщений (БПС) 35 (35, 37). Импульс синхронизации, сопровождающий поступающее сообщение, подается на вход синхронизации записи БПС 35 (36, 37). Далее сообщение передается (фиг. 4) на информационный вход демультиплексора 76, на управляющий вход которого поступает нулевой сигнал с выхода элемента И 77, и заносится в существующую очередь управляющих сообщений.

Запись поступившего сообщения в очередь осуществляется следующим образом.

Пусть в рассматриваемый момент очередь управляющих сообщений в БПС имеет длину R<K, т. е. в регистрах 71.1 - 71.R записаны управляющие сообщения, а регистры 71.R+1-71.K находятся в состоянии логического нуля. Так как по меньшей мере один разряд каждого из регистров 71.1-71.R установлен в единичное состояние, на выходах элементов 73.1-73.R формируются сигналы логического нуля. В то же время единичные сигналы с инверсных выходов регистров 71. R+1-71. K обусловливают наличие единичного уровня сигнала на выходах элементов 73. R+1-73.K. Таким образом, на выходах элементов И 73.1-73.K формируется код "11...100...0", характеризующий текущее состояние очереди сообщений в данном БПС.

Код "11. . . 100...0" с выходов элемента И 73.1-73.К поступает на входы элемента И-НЕ 78 и формирует на его выходе сигнал логической единицы (сигнал состояния БПС), подтверждающий наличие сообщений в данном БПС. Этот же код подается на адресный вход демультиплексора 76 и обеспечивает передачу поступившего управляющего сообщения на его (R+1)-й выход. Далее сообщение через блок элементов ИЛИ 72.R+1 подается на информационный вход регистра 71.R+1.

Одновременно импульс синхронизации с входа синхронизации записи БПС поступает на первые входы элементов И 74.1-74.К, на вторые входы которых подаются соответствующие разряды кода, формируемого элементами 73.1-73.К. Указанный импульс через открытые элементы И 74.R+1-74.K и элементы ИЛИ 75. R+1-75. K проходит на входы синхронизации регистров 71.R+1-71.K и срезом производит запись поступившего сообщения в регистр 71.R+1. На выходе элемента И 73.R+1 появляется сигнал логического нуля. Поскольку на информационных входах регистров 71.R+2-71.K находятся нулевые коды, появление импульса синхронизации не вызывает изменения состояния этих регистров.

Код, характеризующий новое состояние очереди управляющих сообщений, с выходов элементов 73.1-73.К вновь поступает на адресный вход демультиплексора 76 и предотвращает передачу очередного поступающего сообщения на информационный вход регистра 71.R+2. Аналогично следующее сообщение передается на вход регистра 71.R+3 и т.д.

Считывание управляющих сообщений из БПС 35 (36, 37) осуществляется в порядке их поступления, т.е. в соответствии с дисциплиной обслуживания FIFO ("первым пришел - первым обслужен").

Сигналы состояния с управляющих выходов БПС 35, 36 и 37 (фиг. 2) поступают на входы элемента ИЛИ 50 и формируют на его выходе обобщенный сигнал состояния, который принимает единичное значение при наличии управляющих сообщений хотя бы в одном из БПС. Единичный сигнал с выхода элемента ИЛИ 50 поступает на вход установки триггера 41 и переводит его в единичное состояние. Этот же сигнал блокирует элемент И 51, не допуская появления единичного сигнала на входе сброса триггера 41. Сигнал логической единицы с прямого выхода триггера 41 поступает на вход распределителя 42 импульсов (фиг. 7) и включает генератор 89. На выходах распределителя 42 начинается формирование пяти сдвинутых относительно друг друга импульсных последовательностей t1, t2, t3, t4, t5.

Импульс t1 с первого выхода распределителя 42 (фиг 2) поступает на вход счетчика 43 и срезом переключает его в состояние "01". Код "01" с выхода счетчика 43 подается на вход дешифратора 44 и возбуждает единичный сигнал на его первом выходе. Этот же код поступает на адресный вход мультиплексора 38, коммутирует его выход с информационным выходом БПС 35 и тем самым обеспечивает передачу сообщения, записанного в регистре 71.1 блока 35 (фиг. 4), на информационный вход регистра 45 (фиг. 2). Импульс t2 с второго выхода распределителя 42 подается на вход синхронизации регистра 45 и производит запись считанного из блока 35 сообщения.

Появление на четвертом выходе распределителя 42 импульса t3 инициирует процесс определения направления дальнейшей передачи поступившего сообщения.

Импульс t3 поступает на вход установки триггера 48 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 48 подается на управляющий вход генератора 39 константы. Далее этот сигнал поступает (фиг. 8) на управляющие входы блоков элементов И 91.1 и 91.2 и обеспечивает передачу кода номера текущего модуля I.J, размещенного в регистрах 90.1, 90.2, на выход генератора константы. Код I.J с выхода генератора 39 (фиг. 2) подается на второй вход блока 40 выбора направления передачи сообщения, на первом входе которого устанавливается код K.L номера приемника обрабатываемого сообщения, поступающий с первого выхода регистра 45. Код I.J удерживается на входе блока 40 до тех пор, пока на пятом выходе распределителя 42 не появится срез импульса t5 и триггер 48 не будет соответственно возвращен в нулевое состояние.

Выбор направления дальнейшей передачи поступившего сообщения производится следующим образом.

Коды I.J и K.L поступают (фиг. 5) на первые и вторые входы схем сравнения 79.1 и 79.2 соответственно и формируют на их выходах трехразрядные унитарные коды, определяемые соотношениями кодов I и K,J и L в соответствии с таблицей. Коды с выходов схем 79.1 и 79.2 подаются на вход неполного дешифратора 81 и устанавливают на его выходе нулевой или единичный сигнал выбора направления передачи (ретрансляции) сообщения. Одновременно сигналы с выходов равенства схем 79.1 и 79.2 поступают на соответствующие входы элемента И 80.

Если имеет место совпадение как кодов I и K, так и кодов J и L, то на выходах равенства обеих схем 79.1 и 79.2 образуются сигналы логической единицы, которые обусловливают появление единичного уровня сигнала на выходе элемента И 80, что соответствует случаю, если текущий модуль является приемником обрабатываемого сообщения. В противном случае на выходе элемента И 80 сохраняется нулевой уровень сигнала. Сигнал с выходов неполного дешифратора 81 и элемента И 80 (условно обозначается как Q1 и Q2 соответственно (таблица)) передаются соответственно на первый и второй выходы блока выбора направления передачи сообщения.

1. Если Q2="0", т.е. текущий модуль I.J не является приемником поступившего сообщения, то (фиг. 2) нулевой сигнал с второго выхода блока 40 блокирует элементы И 52.1, 52.2, а также запрещает прохождение информации с второго выхода регистра 45 через блок элементов И 49. Этот же сигнал открывает элементы И 53.1 и 53.2.

Одновременно сигнал Q1 ( который может быть как единичным, так и нулевым) с первого выхода блока 40 поступает на адресный вход демультиплексоров 46 и 47 и обеспечивает передачу сообщения с выходов регистра 45 либо на первый, либо на второй информационные выходы блока анализа и далее одному из соседних модулей ДМС (либо модулю I-1.J, либо модулю I.J+1). Очередной импульс t4 с третьего выхода распределителя 42 через демультиплексор 47 и один из открытых элементов И 53.1 или 53.2 проходит на первый или второй информационный выход блока анализа и синхронизирует прием выдаваемого управляющего сообщения соответствующим соседним модулем.

Одновременно импульс t4 подается на вход сдвига БПС 35 - 37, на управляющих входах которых присутствуют сигналы с соответствующих выходов дешифратора 44 (в рассматриваемом случае на выходах дешифратора 44 присутствует код "100"), обеспечивающие выбор одного из трех указанных БПС (БПС 35).

Импульс t4 (фиг. 4) через открытый элемент И 77 выбранного БПС (в данном случае БПС 35) проходит на управляющий вход демультиплексора 76 и формирует на всех его выходах нулевой уровень сигнала. Этот же импульс через элементы ИЛИ 75.1 - 75. K поступает на входы синхронизации регистров 71.1 - 71.K и срезом обеспечивает перезапись информации из регистров 71.2 - 71.K в регистры 71.1 - 71.K соответственно, а в регистр 71.K заносит нулевой код с K-го выхода демультиплексора 76, осуществляя тем самым сдвиг очереди управляющих сообщений.

Если в результате сдвига все регистры 71.1 - 71.K устанавливаются в нулевое состояние (т.е. очередь сообщений становится " пустой"), то на выходах элементов И 73.1 - 73.K образуется код "11...1". Этот код поступает на входы элемента И-НЕ 78 и формирует на его выходе сигнал логического нуля. В противном случае уровень сигнала на выходе элемента И-НЕ 78 остается единичным.

Если на управляющих выходах всех БПС 35, 36 и 37 (фиг. 2) образуются сигналы логического нуля, то на выходе элемента ИЛИ 50 также устанавливается нулевой сигнал. Данный сигнал открывает элемент И 51 и тем самым обеспечивает возможность переключения триггера 41 в нулевое состояние. Очередной импульс t5 с пятого выхода распределителя 42 через элемент И 51 подается на вход сброса триггера 41 и восстанавливает его исходное (нулевое) состояние. Одновременно импульс t5 поступает на счетный вход триггера 48 и срезом возвращает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 48 подается на управляющие входы блоков элементов И 91.1 и 91.2 (фиг. 8) и формирует на выходе генератора 39 (фиг. 2) нулевой код. В то же время нулевой сигнал с прямого выхода триггера 41 поступает на вход распределителя 42 и запрещает формирование импульсных последовательностей t1 - t5.

2. Если Q2="1", т.е. текущий модуль является приемником поступившего сообщения, то единичный сигнал с второго выхода блока 40 поступает на первый вход блока элементов И 49 и обеспечивает передачу информации (информационной части сообщения) с второго выхода регистра 45 на третий информационный выход блока анализа. Одновременно этот же сигнал открывает элементы И 52.1 и 52.2, а также блокирует элементы 53.1 и 53.2. Блокировка элементов 53.1 и 53.2 исключает прохождение импульса t4 на первый и второй информационные выходы блока анализа, а следовательно, запрещает прием обрабатываемого сообщения соседними модулями. В то же время очередной импульс t4 с третьего выхода распределителя 42 через открытый элемент И 52.1 проходит на первый управляющий выход, а следующий импульс t5 с пятого выхода распределителя 42, спустя определенное время, через элемент И 52.2 поступает на второй управляющий выход блока анализа.

Аналогично ранее рассмотренному импульс t5 переключает триггер 48 в нулевое состояние и в случае отсутствия управляющих сообщений в БПС 35 - 37 выключает распределитель 42, проходя через открытый элемент И 51 на вход сброса триггера 41.

Рассмотрим процесс обработки управляющих сообщений, адресованных текущему модулю ДМС.

Информационная часть управляющего сообщения с третьего информационного выхода блока 2 анализа (фиг. 1) поступает на первые входы блоков элементов И 12 и 13. Одновременно на этом же выходе блока 2 анализа появляется признак формата сообщения, определяющий принадлежность данного сообщения либо к типу S1, либо к типу S2 (см. выше). Признак формата сообщения поступает на вторые входы блоков 12 и 13, а также на первые входы элементов И 16, 17 и 18.

1. Если сообщение имеет формат S1 (т.е. является командой передачи управления или инициализации параллельного участка), то признак формата является нулевым и поэтому информационная часть поступившего сообщения (интерпретируемая в данном случае как адрес передачи управления) проходит через открытый блок 12 и поступает на третий информационный вход коммутатора 6. Поскольку текущий модуль находится в пассивном состоянии (невозможность функционирования текущего модуля в момент передачи управления от другого модуля обусловлена синхронным окончанием выполнения различных параллельных участков программы) и на выходах 5.8 и 5.7 регистра 5 находятся соответственно нулевой и единичный сигналы, информационная часть поступившего сообщения через коммутатор 6 передается на информационный вход регистра-счетчика 4 адреса.

Спустя определенное время, на первом управляющем выходе блока 2 появляется импульс синхронизации t4. Поскольку признак формата поступившего сообщения является нулевым, импульс t4 проходит через отрытый элемент И 16, а затем через элемент ИЛИ 20 передается на третий вход блока 8 синхронизации, переключает триггер 82 (фиг. 6) в единичное состояние и тем самым запускает генератор 83. На выходах блока 8 начинается формирование импульсных последовательностей П1, П2, П3.

Первый импульс П1 через открытый элемент И 19.2 (что обусловлено нулевым состоянием триггера 9) проходит на вход синхронизации регистра-счетчика 4 и срезом фиксирует в нем информационную часть (адрес передачи управления) поступившего сообщения. Данный адрес с выхода регистра-счетчика 4 поступает на адресный вход блока 1 и обеспечивает считывание первой команды инициализируемого параллельного или последовательного участка программы. По срезу тактового импульса П2 считанная команда заносится в регистр 5. Далее ход работы модуля полностью совпадает с его функционированием при реализации начального последовательного участка программы.

2. Если сообщение имеет формат S2 (т.е. является квитанцией завершения параллельного участка программы), то признак его формата является единичным и поэтому информационная часть сообщения (теперь интерпретируемая как код номера вершины слияния Vq проходит через открытый блок 13 на информационный вход блока 3 управления синхронизацией параллельных участков. Спустя определенное время, на первом управляющем выходе блока 2 появляется импульс t4, а затем (вновь через определенное время) на втором управляющем выходе блока 2 появляется импульс t5.

Поскольку признак формата поступившего сообщения является единичным, импульсы t4 и t5 проходят соответственно через элемент И 17 и 18 и далее подаются на первый и второй входы синхронизации блока 3 (БУСПУ) соответственно.

Код номера вершины слияния (НВС) Vq (информационная часть поступившего сообщения) поступает (фиг. 3) на вход формирователя 57 и обуславливает появление на его выходе адреса A (Vq), являющегося адресом ячейки блока 56, в которой размещен код текущего условия синхронизации параллельных участков, соответствующего вершине Vq. Как было показано выше, данное условие представляет собой код W'q числа незавершенных параллельных участков, сходящихся к вершине Vq. Адрес A(Vq) с выхода формирователя 57 через открытый коммутатор 62 поступает на адресные входы блока 56 и блока 55. Код текущего числа ожидаемых событий W'q, считываемый из блока 56, подается на информационный вход счетчика 61, а код исходного числа ожидаемых событий Wq с выхода блока 55 поступает на второй и третий информационные входы коммутатора 63.

Импульс t4 с первого входа синхронизации БУСПУ подается на вход синхронизации счетчика 61 и фронтом обеспечивает запись кода W'q с выхода блока 56. Одновременно этот же импульс поступает на вход одновибратора 70 и срезом возбуждает на его выходе импульс t*4. Импульс с выхода одновибратора 70 подается на вычитающий вход счетчика 61 и фронтом обеспечивает уменьшение размещенного в нем кода W'q на единицу.

Если вновь образующийся код  не является нулевым (т.е. некоторые из числа требуемых параллельных участков не завершены) и соответственно код на инверсном выходе счетчика 61 отличен от единичного, то на выходе элемента И 64 сохраняется сигнал логического нуля, не допускающий срабатывания одновибратора 69. Одновременно нулевой сигнал с выхода элемента И 64 поступает на четвертый и пятый управляющие входы коммутатора 63, на остальные управляющие входы которого подается единичный сигнал с прямого выхода триггера 58, и модифицированный код количества ожидаемых событий

не является нулевым (т.е. некоторые из числа требуемых параллельных участков не завершены) и соответственно код на инверсном выходе счетчика 61 отличен от единичного, то на выходе элемента И 64 сохраняется сигнал логического нуля, не допускающий срабатывания одновибратора 69. Одновременно нулевой сигнал с выхода элемента И 64 поступает на четвертый и пятый управляющие входы коммутатора 63, на остальные управляющие входы которого подается единичный сигнал с прямого выхода триггера 58, и модифицированный код количества ожидаемых событий  с прямого выхода счетчика 61 через коммутатор 63 передается на информационный вход блока 56.

с прямого выхода счетчика 61 через коммутатор 63 передается на информационный вход блока 56.

Импульс t5 с второго входа синхронизации БУСПУ через элемент ИЛИ 66 проходит на вход записи блока 56 и, поскольку на выходе формирователя 57 все еще присутствует адрес A(Vq) (что обусловливается присутствием информации на третьем информационном выходе блока 2 анализа (фиг. 1, 2) вплоть до момента появления среза импульса t5 на выходе распределителя 42 (см. работу блока анализа), обеспечивает фиксацию нового кода  в ячейке блока 56 с адресом A(Vq). Таким образом, происходит модификация текущего условия синхронизации параллельных участков, сходящихся к вершине Vq.

в ячейке блока 56 с адресом A(Vq). Таким образом, происходит модификация текущего условия синхронизации параллельных участков, сходящихся к вершине Vq.

Если же вновь образующийся код  становится нулевым (что соответствует завершению всех требуемых параллельных участков), то на инверсном выходе счетчика 61 образуется единичный код. Этот код поступает на первый вход элемента 64 и формирует на его выходе положительный перепад уровня сигнала, который воздействует на одновибратор 69 и возбуждает на его выходе импульс p. Единичный сигнал с выхода элемента 64, кроме того, поступает на четвертый и пятый управляющие выходы коммутатора 63 и коммутирует его выход с выходом блока 55. Код исходного числа ожидаемых событий Wq с выхода блока 55 проходит на выход коммутатора 63 и поступает на информационный вход блока 56. Тактовый импульс t5 через элемент ИЛИ 66 подается на вход записи блока 56 и фиксирует код Wq в ячейке с адресом A(Vq), восстанавливая, таким образом, исходное значение W'q=Wq и обеспечивая возможность повторной синхронизации параллельных участков, сходящихся к вершине слияния Vq ( что может потребоваться при реализации циклических программ).

становится нулевым (что соответствует завершению всех требуемых параллельных участков), то на инверсном выходе счетчика 61 образуется единичный код. Этот код поступает на первый вход элемента 64 и формирует на его выходе положительный перепад уровня сигнала, который воздействует на одновибратор 69 и возбуждает на его выходе импульс p. Единичный сигнал с выхода элемента 64, кроме того, поступает на четвертый и пятый управляющие выходы коммутатора 63 и коммутирует его выход с выходом блока 55. Код исходного числа ожидаемых событий Wq с выхода блока 55 проходит на выход коммутатора 63 и поступает на информационный вход блока 56. Тактовый импульс t5 через элемент ИЛИ 66 подается на вход записи блока 56 и фиксирует код Wq в ячейке с адресом A(Vq), восстанавливая, таким образом, исходное значение W'q=Wq и обеспечивая возможность повторной синхронизации параллельных участков, сходящихся к вершине слияния Vq ( что может потребоваться при реализации циклических программ).

Импульс p с выхода одновибратора 69 поступает на вход установки триггера 9 (фиг. 1) и переключает триггер 9 в состояние логической единицы. Единичный сигнал с прямого выхода триггера 9 открывает элемент И 19.1, а нулевой сигнал с инверсного выхода соответственно блокирует элемент И 19.2. Одновременно импульс p проходит через элемент ИЛИ 20, поступает на третий вход блока 8 синхронизации и разрешает формирование на его выходах импульсных последовательностей П1, П2, П3.

Первый импульс П1 через открытый элемент И 19.1 подается на счетный вход регистра-счетчика 4, в котором размещен адрес, соответствующий последней считанной из блока 1 команде (команде окончания параллельного участка), и срезом инициирует операцию прямого счета. Адрес, размещенный в регистре-счетчике 4, увеличивается на единицу и, поступая далее на адресный вход блока 1, обеспечивает считывание очередной команды. Текущий модуль возобновляет выполнение программы и далее функционирует аналогично рассмотренному. В то же время импульс p с выхода элемента И 19.1 поступает на счетный вход триггера 9 и срезом возвращает триггер 9 в нулевое состояние, вновь обеспечивая блокировку элемента И 19.1 и открывая элемент И 19.2.

Таким образом, введенные в устройство дополнительные блоки, элементы и обусловленные ими связи обеспечивают возможность синхронизации завершения произвольных групп параллельных участков программ. Использование средств синхронизации позволяет исключить возможность одновременного выполнения несовместимых команд (участков программы), что может иметь место при применении прототипа. Наличие возможности синхронизации параллельных участков позволяет использовать микроконтроллерную сеть, например, при построении систем логического управления сложными многофункциональными объектами, алгоритмы поведения которых предполагают параллельное протекание множества взаимосвязанных процессов при необходимости согласования моментов начала и завершения их определенных подмножеств. Указанные особенности предлагаемого изобретения обеспечивают существенное расширение области применения микроконтроллерной сети.

| название | год | авторы | номер документа |

|---|---|---|---|

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределенных систем программного управления технологическими процессами. Технической задачей изобретения является расширение области применения системы на основе организации возможности синхронизации завершения параллельных участков программ. Дискретная микроконроллерная сеть содержит m • n модулей, где n - число модулей в строке матричной организации сети; m - число строк, содержащих блок памяти программ; блок анализа, регистр-счетчик адреса, регистр команд, коммутатор адреса, мультиплексор логических условий, блок синхронизации, блоки элементов И, элементы И, триггер, элементы ИЛИ и блок управления синхронизацией параллельных участков. 4 з.п. ф-лы, 11 ил., 1 табл.

соединен с вторым информационным выходом модуля i, j - 1, а первый информационный вход модуля i, 1 подключен к второму информационному выходу модуля i, n, второй информационный вход модуля k, l,