Изобретения относятся к аналоговой вычислительной технике и могут использоваться в системах автоматического управления и регулирования, информационно-измерительных системах, устройствах релейной защиты и автоматики.

Известен дифференциатор напряжений [1], содержащий операционные усилители, диодно-емкостные запоминающие ячейки, генератор прямоугольных импульсов, триггер, элемент НЕ, элементы задержки.

Недостатком аналога является возможность получения только первой производной исследуемого напряжения.

Наиболее близким техническим решением к предлагаемому является дифференцирующее устройство [2], содержащее операционные усилители, разделительные диоды, запоминающие конденсаторы, два генератора прямоугольных импульсов, распределитель уровней и триггер.

Недостатками прототипа являются:

1) узкий динамический диапазон (ограниченный частотный спектр исследуемого сигнала) устройства;

2) недостаточно высокая надежность устройства из-за большого количества связей между элементами;

3) неудобство в эксплуатации из-за необходимости подключения к выходам устройства дополнительных повторителей напряжения с высокоомными входами.

Технические задачи, решаемые изобретениями - расширение динамического диапазона исследуемого сигнала, а также повышение надежности и удобства в эксплуатации устройства.

Указанные технические задачи (в первом варианте реализации устройства) решаются благодаря тому, что в дифференцирующем устройстве, содержащем входной зажим и n+1 (где n - максимальный порядок получаемой производной) выходных зажимов, (n+1)-канальный распределитель уровней, первый и второй генераторы прямоугольных импульсов, триггер, n+1 блоков выделения приращений напряжения, каждый из которых включает конденсатор, первая обкладка которого соединена с шиной нулевого потенциала, и блок вычитания, вход уменьшаемого которого соединен с информационным входом блока выделения приращений напряжения, причем информационный вход первого блока выделения приращений напряжения подключен ко входному зажиму устройства, первый выход i-го блока выделения приращений напряжения (при i=1...n+1) соединен с i-м выходным зажимом устройства, а управляющий вход i-го блока выделения приращений напряжения подключен к (n-i+2)-му выходу распределителя уровней, тактовый вход которого подключен к выходу второго генератора прямоугольных импульсов, а (n+1)-й выход соединен со входом установки нуля триггера, инверсный выход которого соединен со входом установки нуля распределителя уровней, у блоков выделения приращений напряжения дополнительно введены вторые выходы, причем информационный вход i-го (при i=2...n+1) блока выделения приращений напряжения подключен ко второму выходу (i-1)-го блока выделения приращений напряжения, выход первого генератора прямоугольных импульсов соединен с тактовым входом триггера, а в каждый блок выделения приращений напряжения дополнительно введены повторитель напряжения и коммутатор, информационный вход которого подключен к информационному входу блока выделения приращений напряжения, управляющий вход которого соединен с управляющим входом коммутатора, выход которого связан со второй обкладкой конденсатора и входом повторителя напряжения, выход которого соединен со входом вычитаемого блока вычитания и первым выходом блока выделения приращений напряжения, второй выход которого подключен к выходу блока вычитания; каждый из блоков вычитания (в первом варианте их реализации) содержит операционный усилитель, выход которого является выходом блока вычитания и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый входной резистор подключен ко входу вычитаемого блока вычитания, вход уменьшаемого которого через второй входной резистор соединен с неинвертирующим входом операционного усилителя, который соединен с шиной нулевого потенциала через дополнительный резистор; каждый из блоков вычитания (во втором варианте их реализации) содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый входной резистор подключен ко входу уменьшаемого блока вычитания, выход первого операционного усилителя через второй входной резистор соединен с инвертирующим входом второго операционного усилителя, который через третий входной резистор подключен ко входу вычитаемого блока вычитания и через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока вычитания, не инвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала; повторитель напряжения содержит операционный усилитель, выход которого является выходом повторителя напряжения и соединен с инвертирующим входом операционного усилителя, неинвертирующий вход которого является входом повторителя напряжения.

Указанные технические задачи (во втором варианте реализации устройства) решаются благодаря тому, что в дифференцирующем устройстве, содержащем входной зажим и n+1 (где n - максимальный порядок получаемой производной) выходных зажимов, (n+1)-канальный распределитель уровней, первый и второй генераторы прямоугольных импульсов, триггер, n+1 блоков выделения приращений напряжения, каждый из которых включает первый и второй диоды, конденсатор, первый блок вычитания, вход уменьшаемого которого подключен к информационному входу блока выделения приращений напряжения, а выход соединен с анодом первого диода, катод которого объединен с анодом второго диода и через конденсатор соединен с шиной нулевого потенциала, причем информационный вход первого блока выделения приращений напряжения подключен ко входному зажиму устройства, первый выход i-го блока выделения приращений напряжения, (при i = 1. . .n+1) соединен с i-м выходным зажимом устройства, а управляющий вход i-го блока выделения приращений напряжения подключен к (n-i+2)-му выходу распределителя уровней, тактовый вход которого подключен к выходу второго генератора прямоугольных импульсов, а (n+1)-й выход соединен со входом установки нуля триггера, инверсный выход которого соединен со входом установки нуля распределителя уровней, у блоков выделения приращений напряжения дополнительно введены вторые выходы, причем информационный вход i-го (при i = 2.. . n+1) блока выделения приращений напряжения подключен ко второму выходу (i-1)-гo блока выделения приращений напряжения, выход первого генератора прямоугольных импульсов соединен с тактовым входом триггера, а в каждый блок выделения приращений напряжения дополнительно введены элемент НЕ, повторитель напряжения, второй блок вычитания и блок суммирования, выход которого соединен с катодом второго диода, анод которого через повторитель напряжения соединен с первым выходом блока выделения приращений напряжения и со входом вычитаемого второго блока вычитания, выход которого является вторым выходом блока выделения приращений напряжения, информационный вход которого соединен с объединенными входом уменьшаемого второго блоков вычитания и первым входом блока суммирования, второй вход которого объединен со входом вычитаемого первого блока вычитания и через элемент НЕ подключен к управляющему входу блока выделения приращений напряжения; каждый из блоков вычитания (в первом варианте их реализации) содержит операционный усилитель, выход которого является выходом блока вычитания и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый входной резистор подключен ко входу вычитаемого блока вычитания, вход уменьшаемого которого через второй входной резистор соединен с не инвертирующим входом операционного усилителя, который соединен с шиной нулевого потенциала через дополнительный резистор; каждый из блоков вычитания (во втором варианте их реализации) содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый входной резистор подключен ко входу уменьшаемого блока вычитания, выход первого операционного усилителя через второй входной резистор соединен с инвертирующим входом второго операционного усилителя, который через третий входной резистор подключен ко входу вычитаемого блока вычитания и через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока вычитания, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала; блок суммирования (в первом варианте его реализации) содержит операционный усилитель, выход которого является выходом блока суммирования и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый дополнительный резистор соединен с шиной нулевого потенциала, которая через второй дополнительный резистор соединена с неинвертирующим входом операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования; блок суммирования (во втором варианте его реализации) содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования, выход первого операционного усилителя через третий входной резистор соединен с инвертирующим входом второго операционного усилителя, который через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока суммирования, не инвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала; повторитель напряжения содержит операционный усилитель, выход которого является выходом повторителя напряжения и соединен с инвертирующим входом операционного усилителя, не инвертирующий вход которого является входом повторителя напряжения.

Существенными отличиями предлагаемого устройства являются введение у всех блоков выделения приращений напряжения вторых выходов, новая организация связей между элементами устройства, а также введение в каждый блок выделения приращений напряжения новых элементов - повторителя напряжения и коммутатора (в первом варианте реализации устройства) или элемента НЕ, повторителя напряжения, второго блока вычитания и блока суммирования (во втором варианте реализации устройства) с новой организацией связей между элементами блока выделения приращений напряжения. Совокупность элементов и связей между ними обеспечивают достижение положительного эффекта - расширение динамического диапазона исследуемого сигнала, а также повышение надежности и удобства в эксплуатации устройства.

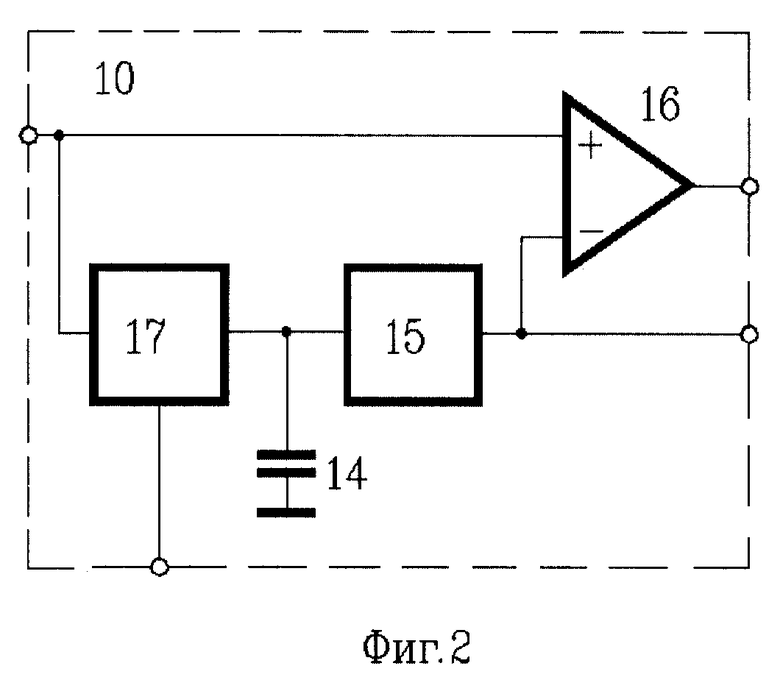

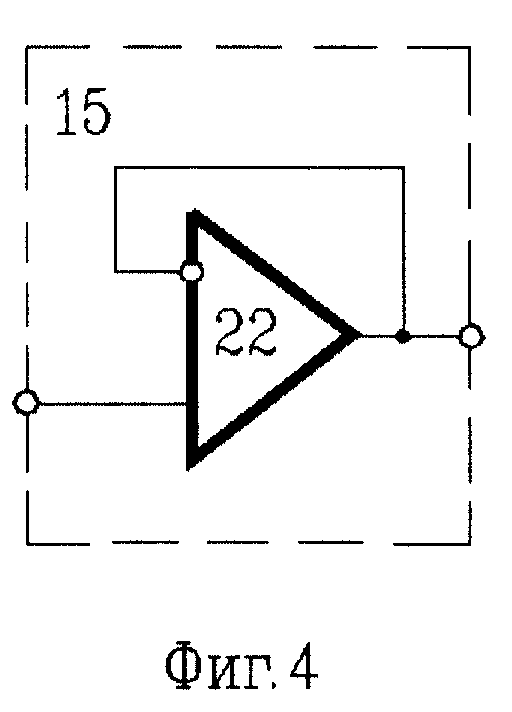

На фиг.1 представлена схема устройства, на фиг.2 и 3 - варианты реализации схемы блока выделения приращений напряжения, на фиг.4 - схема повторителя напряжения, на фиг.5 и 6 - варианты реализации схемы блока вычитания, на фиг.7 и 8 - варианты реализации схемы блока суммирования.

Устройство (фиг.1) содержит входной зажим 1, и n+1 (где n - максимальный порядок получаемой производной) выходных зажимов 2-5, (n+1)-канальный распределитель 6 уровней (РУ), триггер 7, первый 8 и второй 9 генераторы прямоугольных импульсов (ГПИ), выход ГПИ 8 соединен с тактовым входом триггера 7, инверсный выход которого соединен со входом установки нуля РУ 6, тактовый вход которого подключен к выходу ГПИ 9, n+1 блоков 10-13 выделения приращений напряжения (БВПН), причем информационный вход i-го (при i = 2...n+1) БВПН подключен к выходу (i-1)-го БВПН, а управляющий вход i-го (при i = 1... n+1) БВПН подключен к (n-i+2)-му выходу РУ 6, информационный вход первого БВПН 10 подключен ко входному зажиму 1 устройства, выходы БВПН 10-13 соединены соответственно с выходными зажимами 2-5, (n+1)-й выход РУ 6 соединен со входом установки нуля триггера 7.

В первом варианте реализации каждый из блоков 10-13 выделения приращений напряжения (фиг.2) содержит (на примере БВПН 10) конденсатор 14, повторитель 15 напряжения (ПН), блок 16 вычитания (БВ) и коммутатор 17, информационный вход которого подключен к информационному входу БВПН 10 и объединен со входом уменьшаемого БВ 16, выход которого является вторым выходом БВПН 10, управляющий вход которого соединен с управляющим входом коммутатора 17, выход которого связан со входом ПН 15 и через конденсатор 14 с шиной нулевого потенциала, выход ПН 15 соединен со входом вычитаемого БВ 16 и первым выходом БВПН 10.

Во втором варианте реализации каждый из блоков 10-13 выделения приращений напряжения (фиг.3) содержит (на примере БВПН 10) конденсатор 14, ПН 15, второй БВ 16 и первый БВ 17, блок 18 суммирования (БС), элемент НЕ 19, первый 20 и второй 21 диоды, катод диода 20 и анод диода 21 объединены и соединены со входом ПН 15 и через конденсатор 14 с шиной нулевого потенциала, выход ПН 15 соединен со входом вычитаемого БВ 16 и первым выходом БВПН 10, информационный вход которого соединен с объединенными первым входом БС 18 и входами уменьшаемого БВ 17 и БВ 16, выход которого является вторым выходом БВПН 10, управляющий вход которого через элемент НЕ 19 соединен с объединенными входом вычитаемого БВ 17 и вторым входом БС 18.

Повторитель 15 напряжения (фиг.4) содержит операционный усилитель (ОУ) 22, выход которого является выходом ПН 15 и соединен с инвертирующим входом ОУ 22, неинвертирующий вход которого является входом ПН 15.

Каждый из блоков 16-17 (в первом варианте их реализации, изображенном на фиг.5) содержит (на примере БВ 16) ОУ 23, выход которого является выходом БВ 16 и через резистор 24 обратной связи соединен с инвертирующим входом ОУ 23, который через первый входной резистор 25 подключен ко входу вычитаемого БВ 16, вход уменьшаемого которого через второй входной резистор 26 соединен с неинвертирующим входом ОУ 23, который соединен с шиной нулевого потенциала через дополнительный резистор 27.

Каждый из блоков 16-17 вычитания (во втором варианте их реализации, изображенном на фиг. 6) содержит (на примере БВ 16) первый ОУ 28, инвертирующий вход которого через первый входной резистор 29 подключен ко входу уменьшаемого БВ 16 и через первый резистор 30 обратной связи соединен с выходом первого ОУ 28, который через второй входной резистор 31 соединен с инвертирующим входом второго ОУ 32, который через третий входной резистор 33 подключен ко входу вычитаемого БВ 16 и через второй резистор 34 обратной связи соединен с выходом второго ОУ 32, являющегося выходом БВ 16, неинвертирующие входы первого ОУ 28 и второго ОУ 32 соединены с шиной нулевого потенциала.

Блок 18 суммирования (в первом варианте его реализации, изображенном на фиг. 7) содержит ОУ 35, выход которого является выходом БС 18 и через резистор 36 обратной связи соединен с инвертирующим входом ОУ 35, который через первый дополнительный резистор 37 соединен с шиной нулевого потенциала, которая через второй дополнительный резистор 38 соединена с неинвертирующим входом ОУ 35, который через первый и второй входные резисторы 39 и 40 подключен к первому и второму входам БС 18.

Блок 18 суммирования (во втором варианте его реализации, изображенном на фиг. 8) содержит первый ОУ 41, инвертирующий вход которого через первый 42 и второй 43 входные резисторы подключен к первому и второму входам БС 18, а также через первый резистор 44 обратной связи соединен с выходом первого ОУ 41, который через третий входной резистор 45 соединен с инвертирующим входом второго ОУ 46, который через второй резистор 47 обратной связи соединен с выходом второго ОУ 46, являющегося выходом БС 18, неинвертирующие входы первого ОУ 41 и второго ОУ 46 соединены с шиной нулевого потенциала.

Рассмотрим работу первого варианта устройства.

При нулевом состоянии триггера 7 единичное напряжение с его инверсного выхода приложено ко входу установки нуля РУ 6, что удерживает последний также в нулевом состоянии, несмотря на то, что на его тактовый вход поступают импульсы ГПИ 9. При этом нулевое напряжение с выходов распределителя 6 приложено к управляющим входам БВПН 10-13, в результате напряжение на конденсаторах 14 поддерживается постоянным и равным для каждого конденсатора значению, накопленному в предыдущем такте работы устройства.

По заднему фронту очередного импульса ГПИ 8 происходит срабатывание триггера 7, который снимает единичное напряжение со входа установки нуля РУ 6 и на его выходах поочередно с частотой f2 ГПИ 9 (f2>f1) появляются единичные потенциалы. При этом происходит поочередное обновление информации, запоминаемой на конденсаторах 14, начиная с последнего БВПН 13.

Напряжение, запоминаемое на конденсаторах 14, представляет собой приращение соответствующего порядка, которое является, как известно, линейной композицией входного сигнала и приращений более низкого порядка.

При появлении сигнала на последнем, (n+1)-м, выходе РУ 6 триггер 7 возвращается в нулевое состояние, РУ 6 переходит в нулевое состояние покоя и все коммутаторы 17 (при первом варианте реализации БВПН 10-13) или диоды 20 и 21 (при втором варианте реализации БВПН 10-13) снова оказываются закрытыми до начала следующего такта.

Устройство работает аналогично как при отрицательных, так и при положительных производных, а также при положительных и отрицательных значениях входного сигнала. При его запуске переходной процесс в вычислении i-й производной заканчивается через i тактов.

Второй вариант реализации устройства (отличающийся от первого схемой БВПН 10-13) работает аналогично первому.

Преимуществами предлагаемого устройства по сравнению с известными являются расширение динамического диапазона исследуемого сигнала (в 2n раз), а также повышение надежности (число соединений уменьшается на n(n-1)) и удобства в эксплуатации. Схема устройства реализуется на интегральных микросхемах; выбор варианта реализации схемы БВПН зависит от имеющейся в наличии разработчика элементной базы.

Источники информации

1. А.с. СССР 591871, кл. G 06 G 7/18, 1976.

2. А.с. СССР 984728, кл. G 06 G 7/18, 1981 (прототип).

Изобретения относятся к вычислительной технике и могут быть использованы в системах автоматического управления. Техническим результатом является расширение диапазона исследуемого сигнала. Каждый вариант устройства содержит распределитель уровней, генераторы прямоугольных импульсов, триггер и блоки выделения приращений напряжения, при этом в первом варианте изобретения блок выделения приращений напряжения дополнительно содержит повторитель напряжения и коммутатор, а во втором варианте - элемент НЕ, повторитель напряжения, второй блок вычитания и блок суммирования. 2 с. и 8 з.п.ф-лы, 8 ил.

| Устройство для резки | 1981 |

|

SU984728A1 |

| Дифференциатор напряжений | 1976 |

|

SU591871A1 |

| Устройство для дифференцирования | 1987 |

|

SU1462305A1 |

| Дифференцирующее устройство | 1984 |

|

SU1264170A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ КАЧЕСТВА ГОМЕОПАТИЧЕСКИХ ЛЕКАРСТВЕННЫХ СРЕДСТВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1997 |

|

RU2112976C1 |

| US 4293918 А, 06.10.1981. | |||

Авторы

Даты

2002-08-20—Публикация

2000-07-07—Подача