Текст описания в факсимильном виде (см. графическую часть). Т1

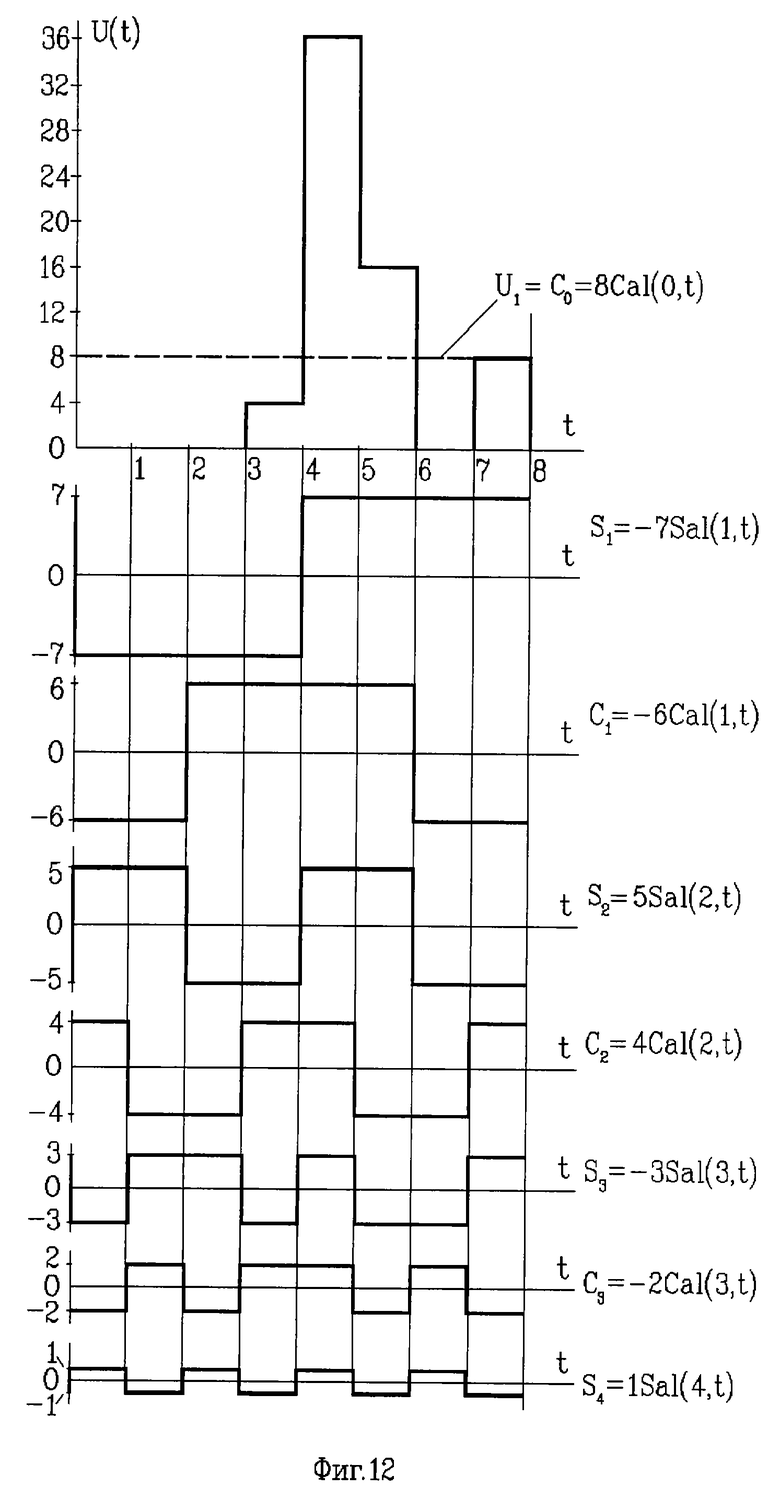

Изобретения относятся к области вычислительной техники и могут быть использованы для спектрального анализа сигналов произвольной формы. Техническим результатом является расширение функциональных возможностей. Устройства содержат блок суммирования, счетчик и генератор прямоугольных импульсов. Первый вариант устройства дополнительно содержит дешифратор и матрицу арифметических блоков, представляющих собой двухвходовые блоки суммирования и блоки вычитания, и ключи, второй вариант содержит цифровой блок памяти, входные зажимы и каналы, содержащие инверторы, элементы НЕ и ключи. 2 с. и 7 з.п.ф-лы, 12 ил., 2 табл.

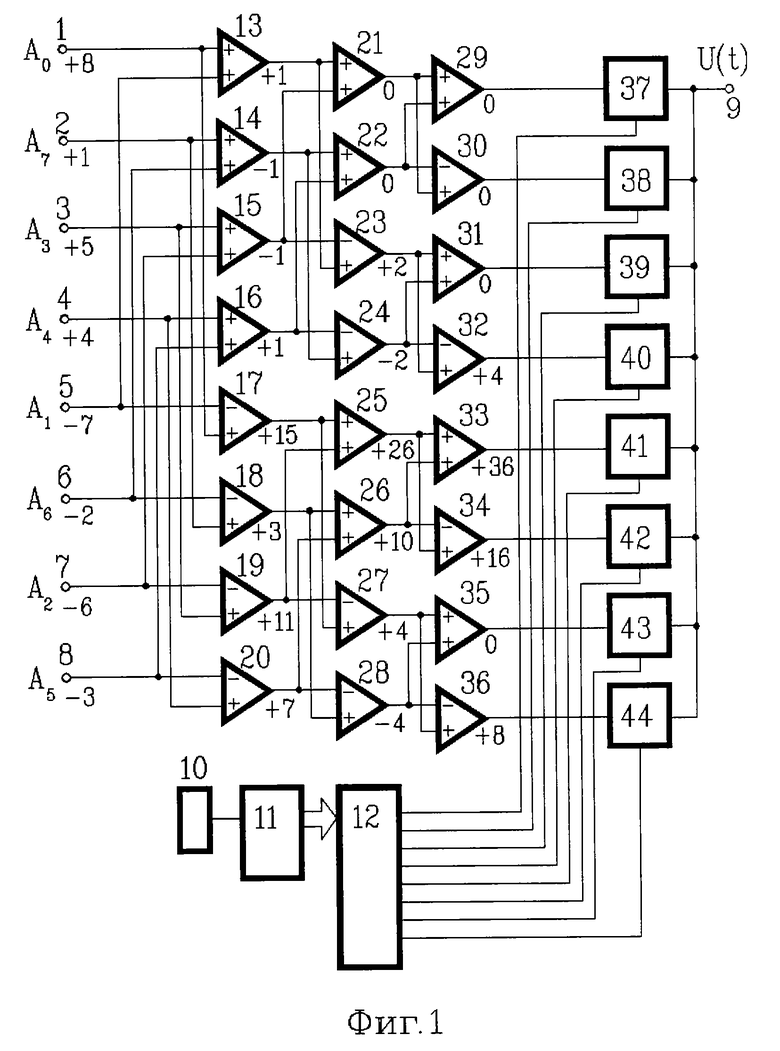

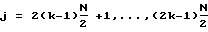

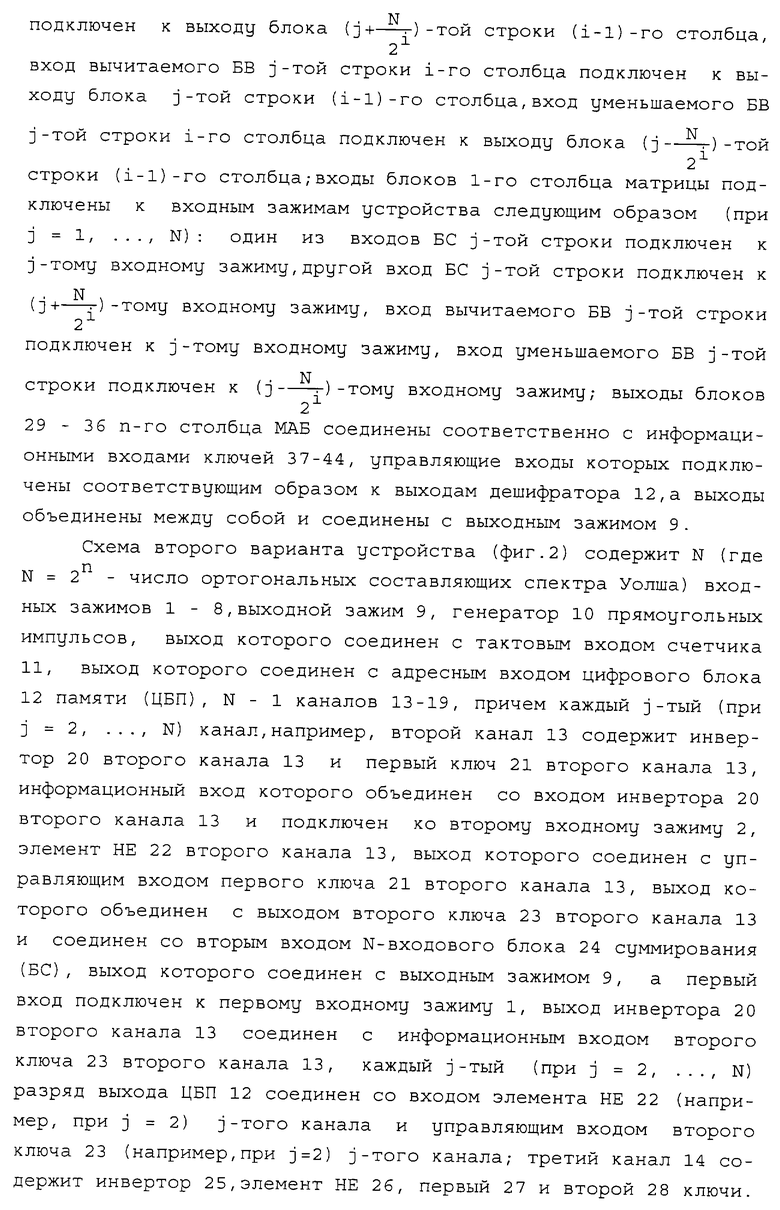

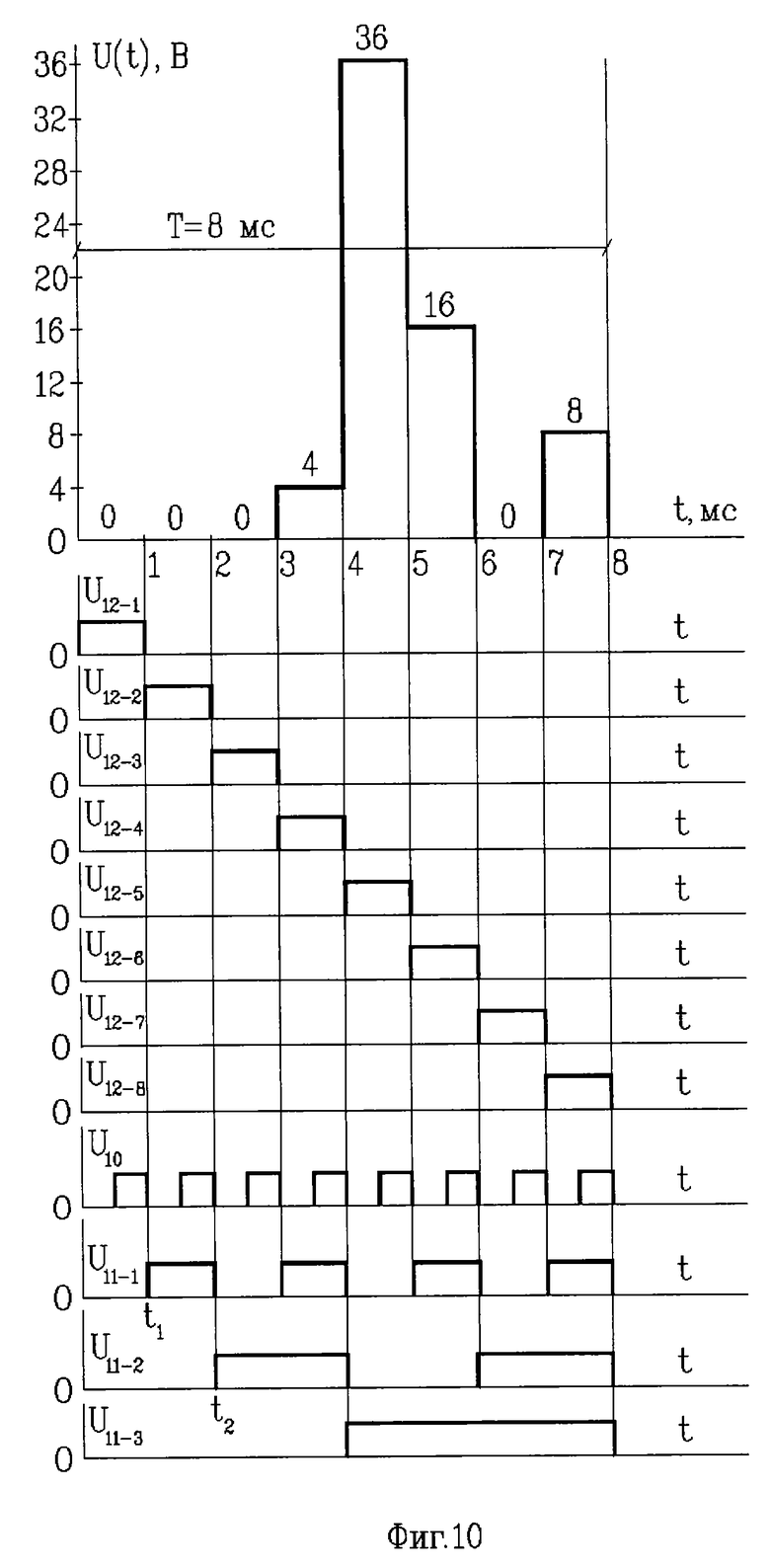

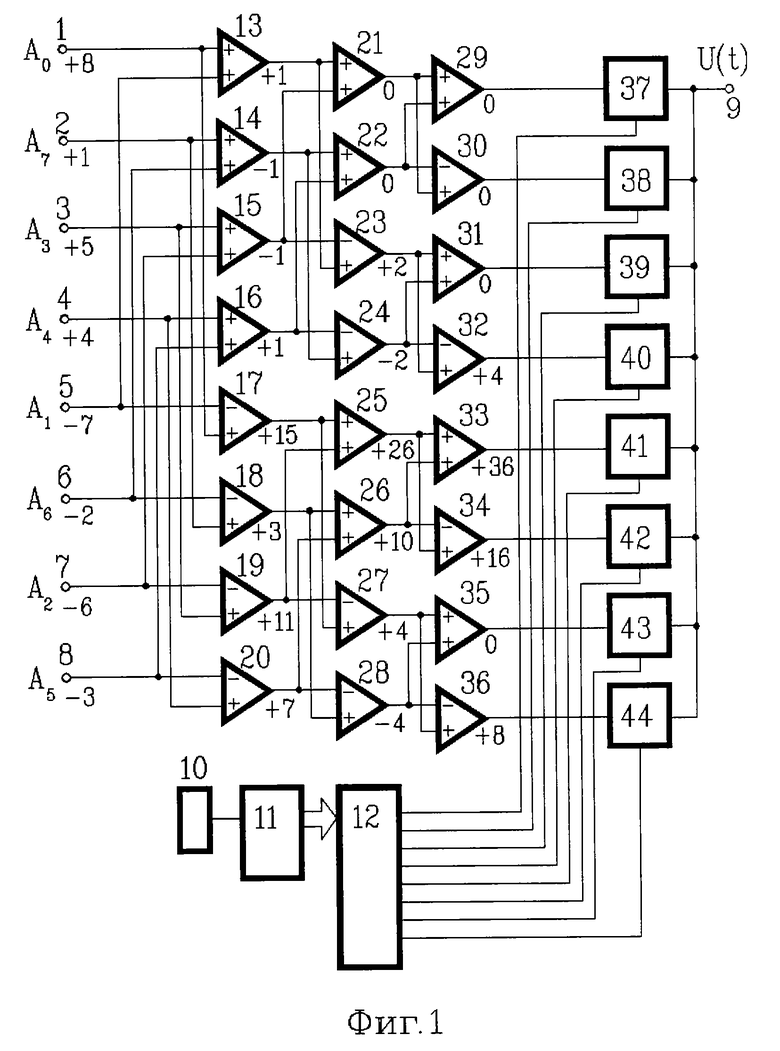

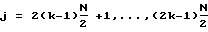

1. Устройство для обратного преобразования Уолша (первый вариант), содержащее блок суммирования, счетчик, дешифратор и генератор прямоугольных импульсов, выход которого соединен с тактовым входом счетчика, выход которого соединен с управляющим входом дешифратора, отличающееся тем, что в него дополнительно введены заполненная матрица арифметических блоков размера N•n (где N=2n - число ортогональных составляющих спектра Уолша), представляющих собой двухвходовые блоки суммирования и блоки вычитания, и N ключей, выходы которых объединены между собой и соединены с выходным зажимом устройства, N входных зажимов которого соединены соответственно со входами матрицы арифметических блоков, у которой блоки суммирования являются ij-ми (где i=1,..., n - номер столбца матрицы, a j=1,...,N - номер строки матрицы) элементами матрицы арифметических блоков при i=l,...,n,  (где k= 1, ..., 2i-1 - номер группы строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания;

(где k= 1, ..., 2i-1 - номер группы строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания;  число элементов в группе строк i-го столбца;

число элементов в группе строк i-го столбца;

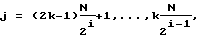

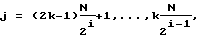

, а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i=1,..., n,

, а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i=1,..., n,

причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,..., n, j=1,..., N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока

причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,..., n, j=1,..., N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока  строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, вход уменьшаемого блока вычитания j-й строки i-го столбца подключен к выходу блока

строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, вход уменьшаемого блока вычитания j-й строки i-го столбца подключен к выходу блока  строки (i-1)-го столбца; входы блоков 1-го столбца матрицы подключены к входным зажимам устройства следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к j-му входному зажиму, другой вход блока суммирования j-й строки подключен к

строки (i-1)-го столбца; входы блоков 1-го столбца матрицы подключены к входным зажимам устройства следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к j-му входному зажиму, другой вход блока суммирования j-й строки подключен к  входному зажиму, вход вычитаемого блока вычитания j-й строки подключен к j-му входному зажиму, вход уменьшаемого блока вычитания j-й строки подключен к

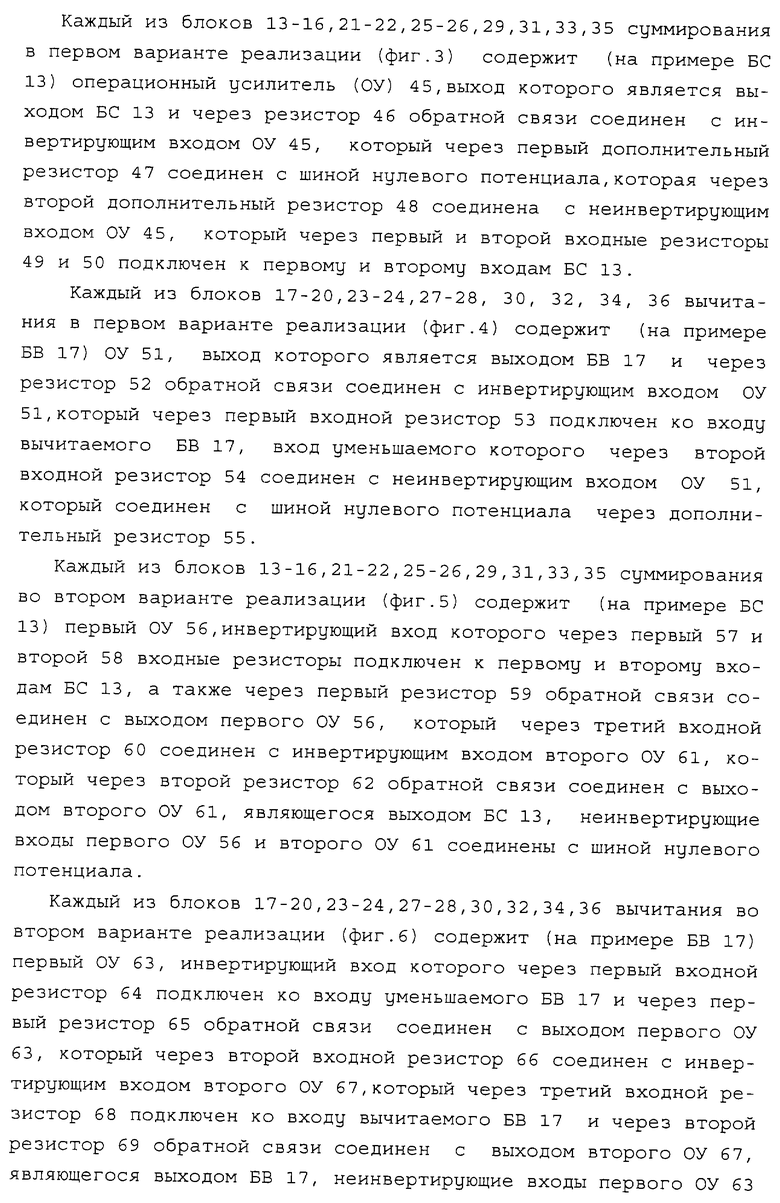

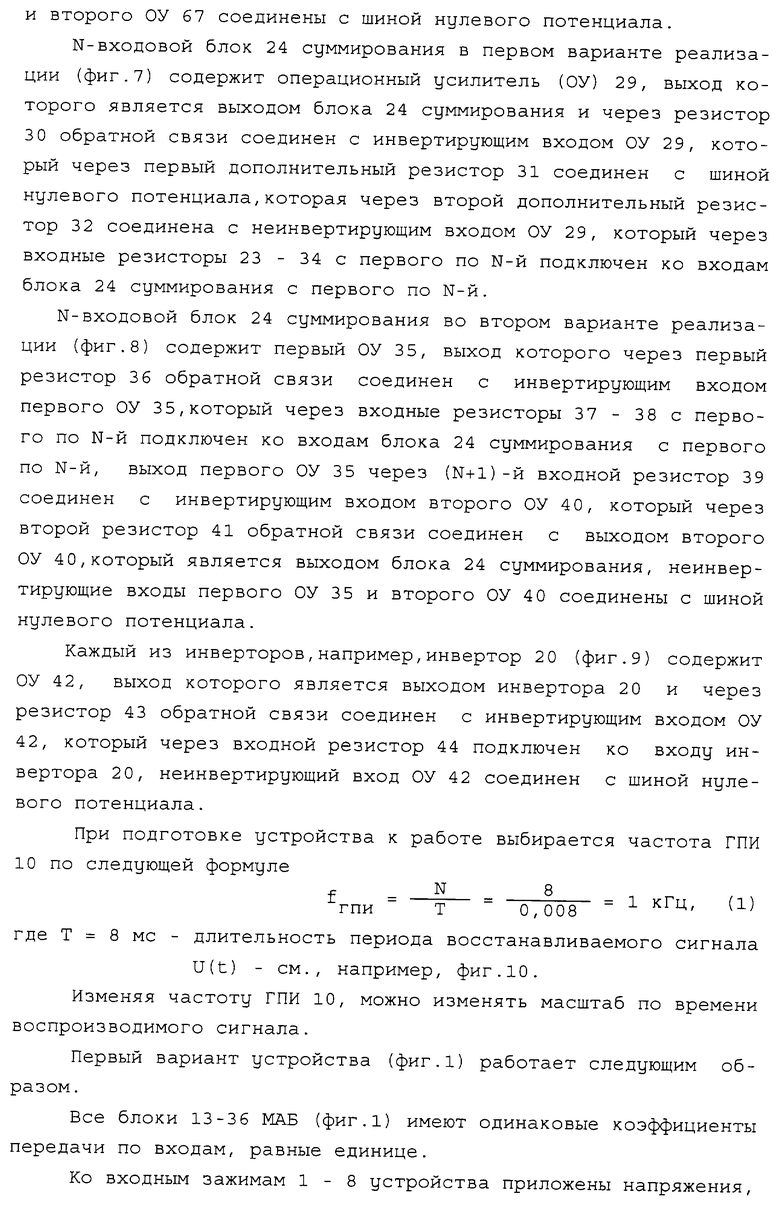

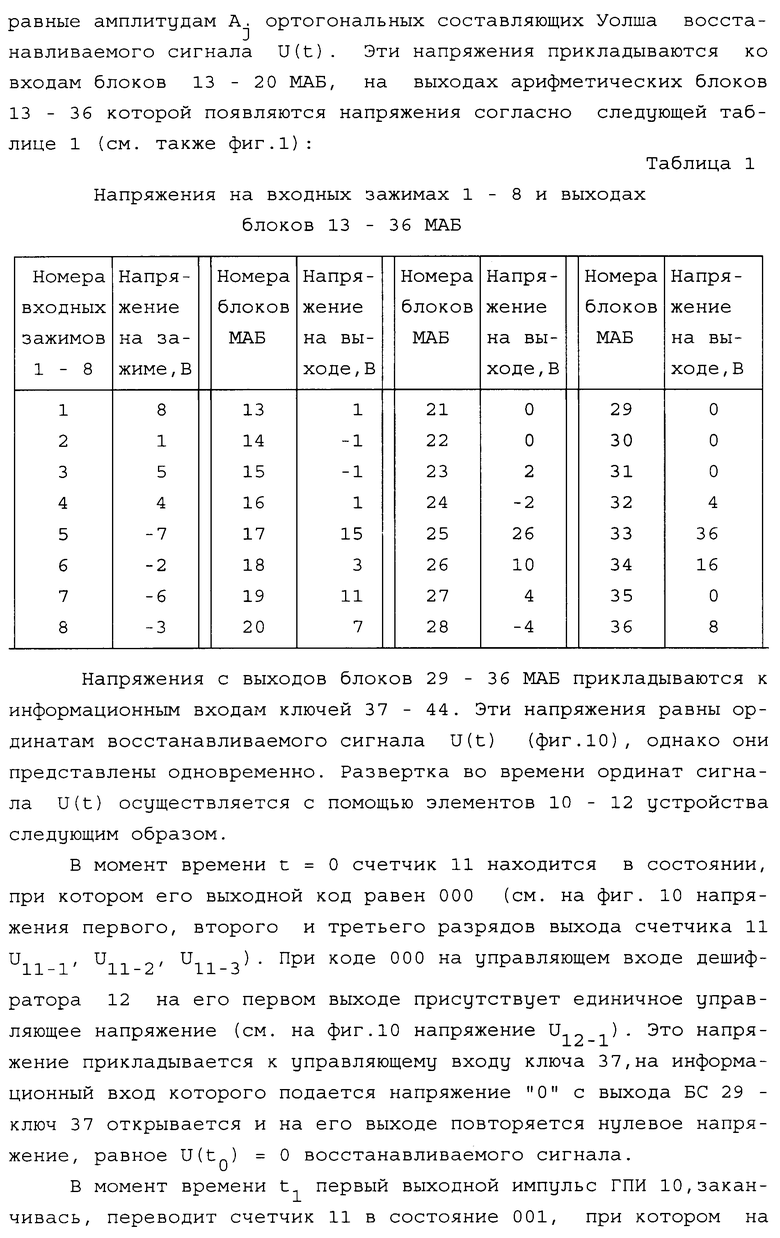

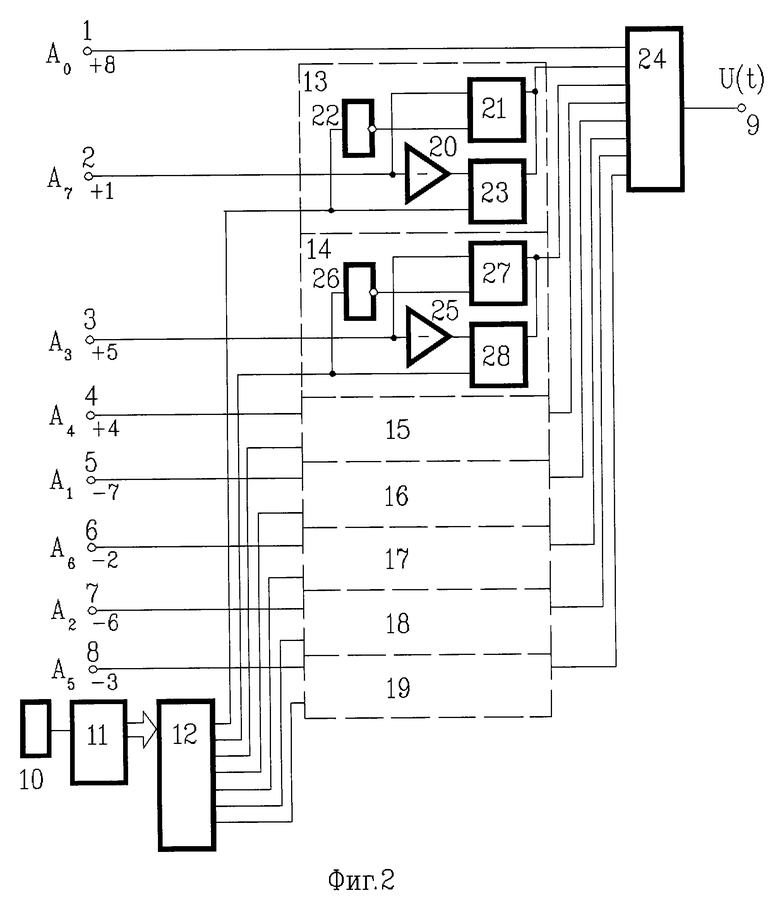

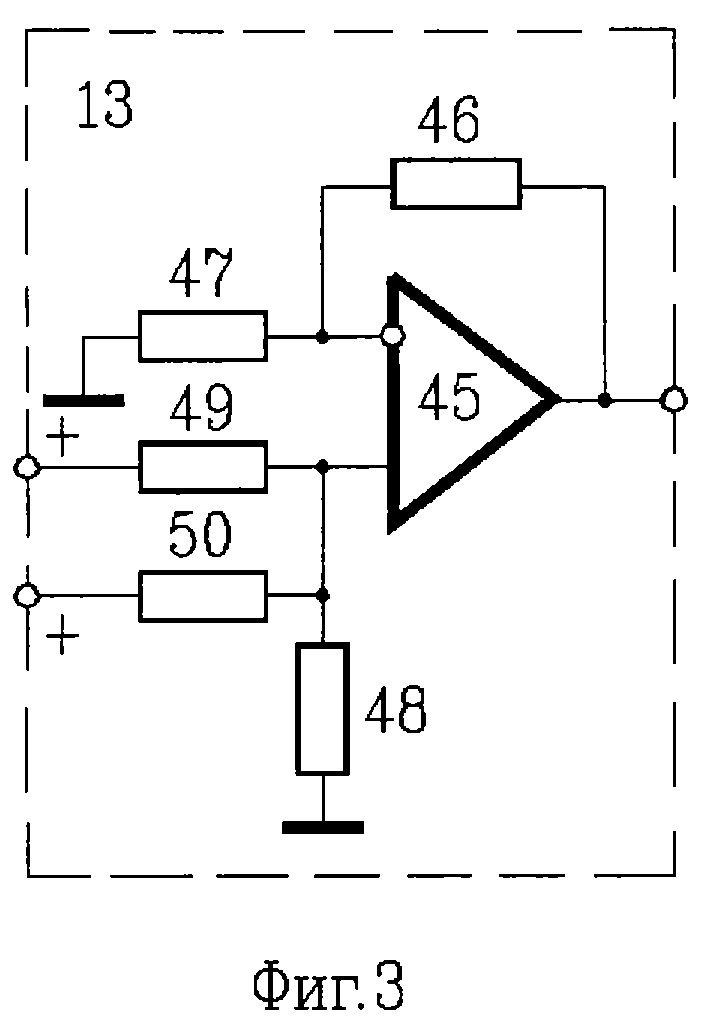

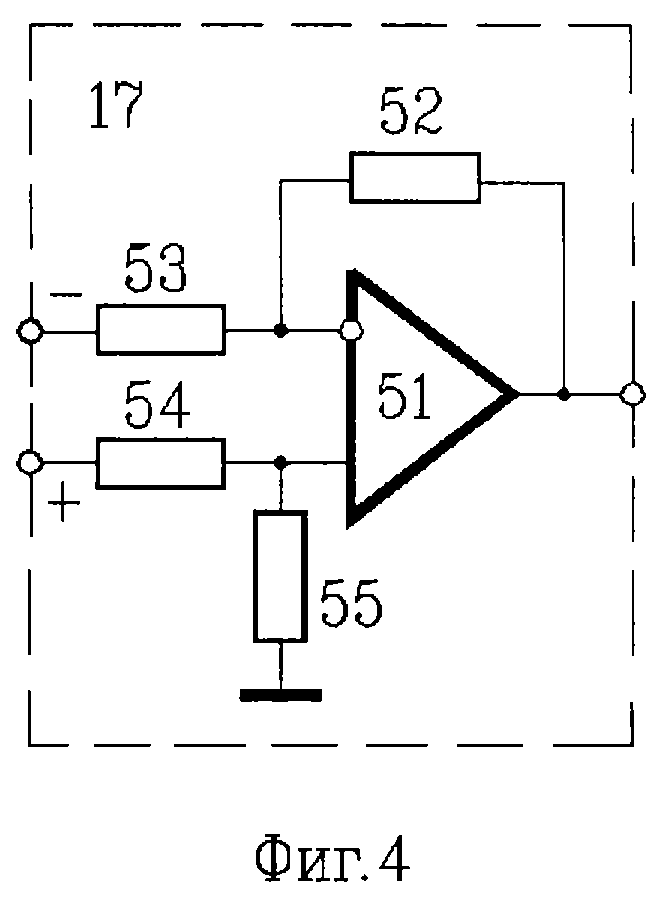

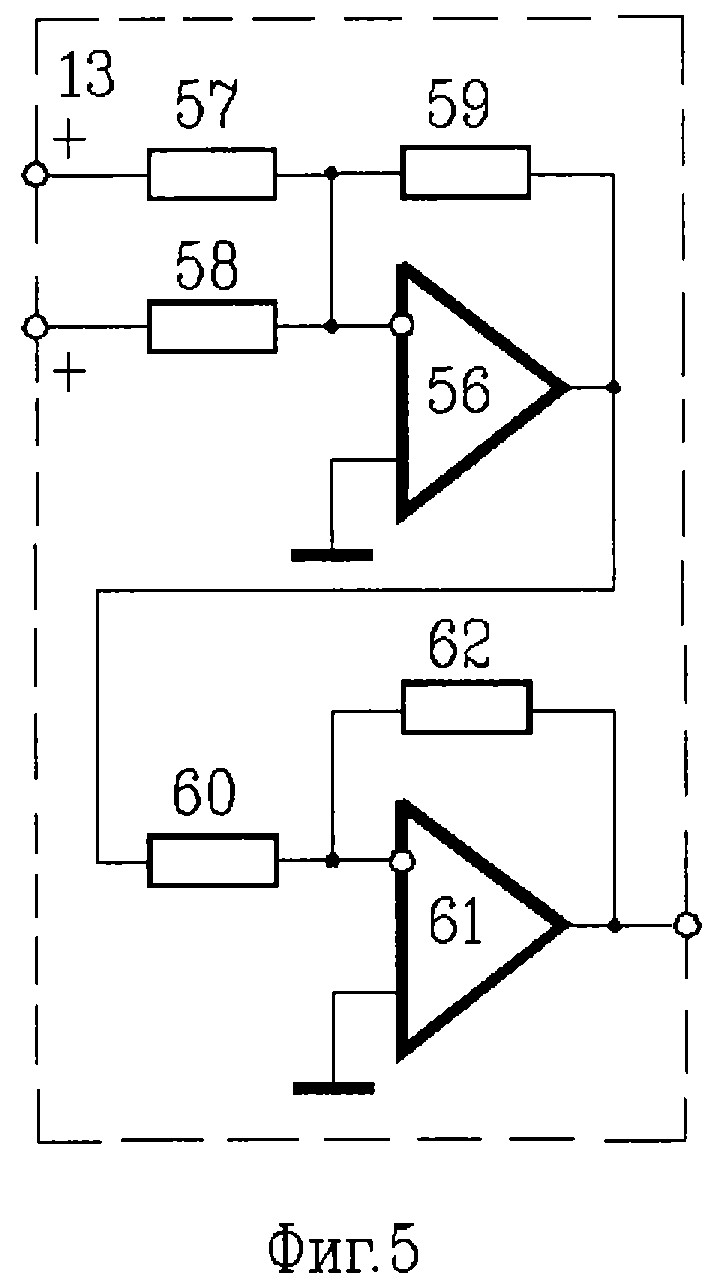

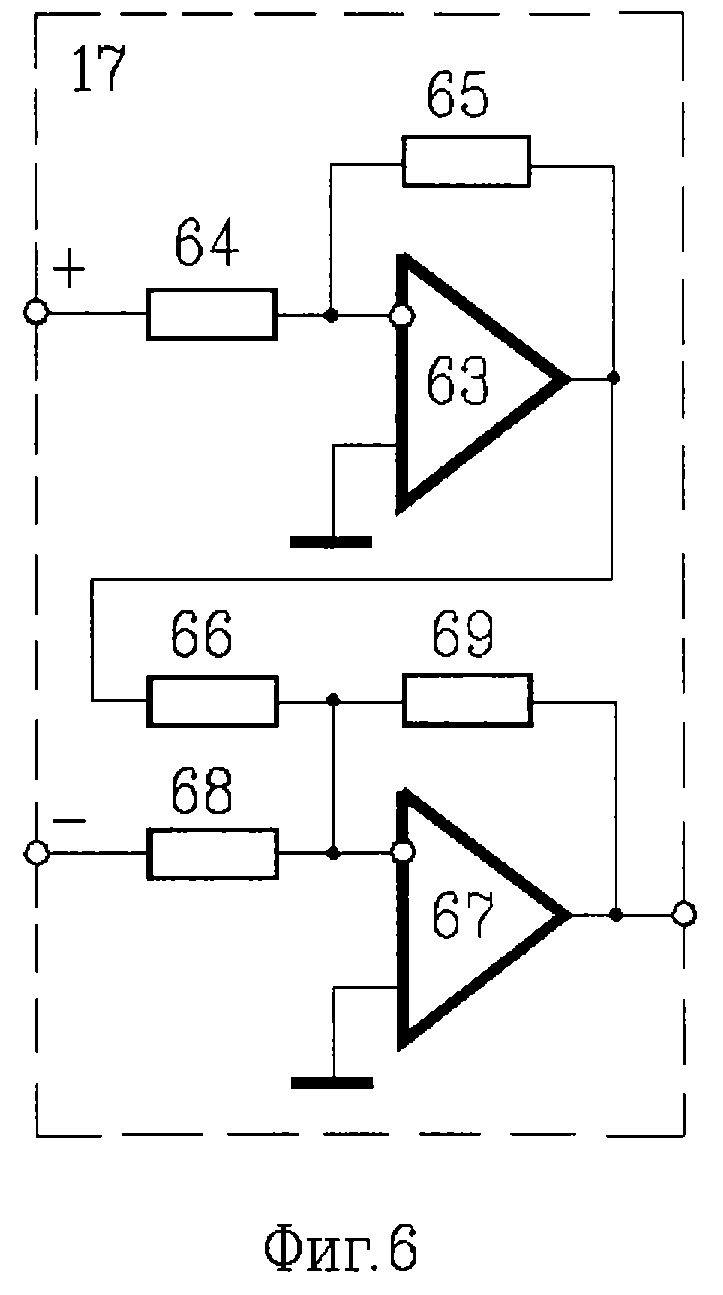

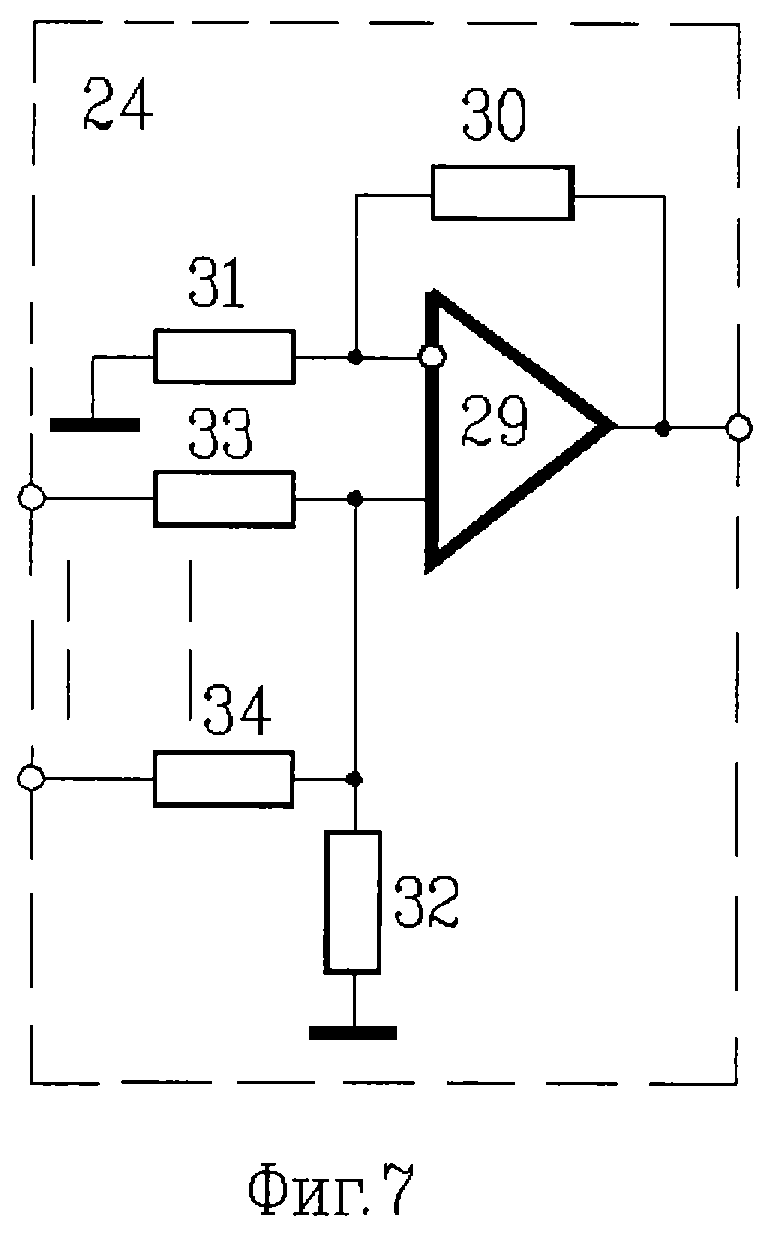

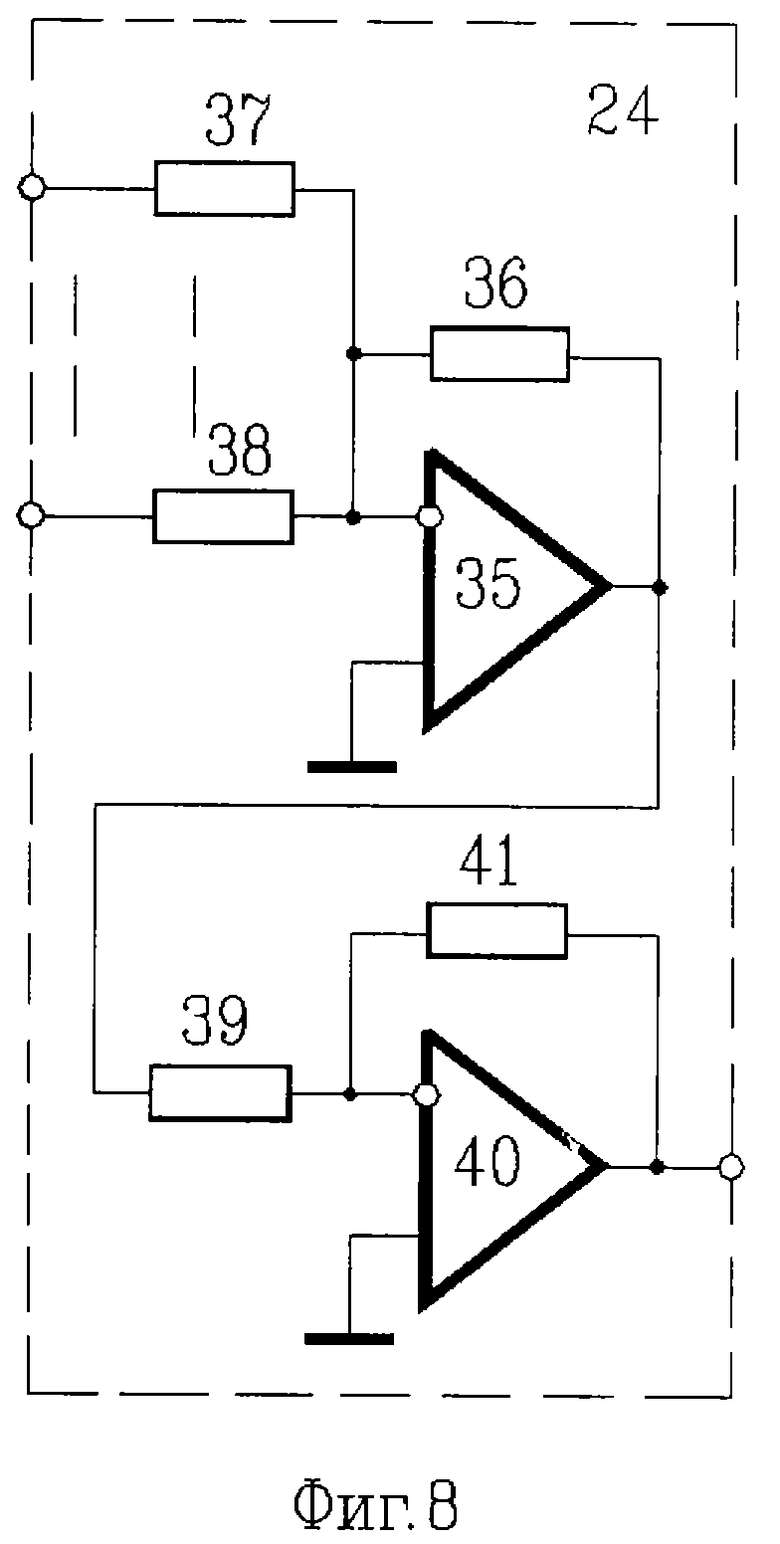

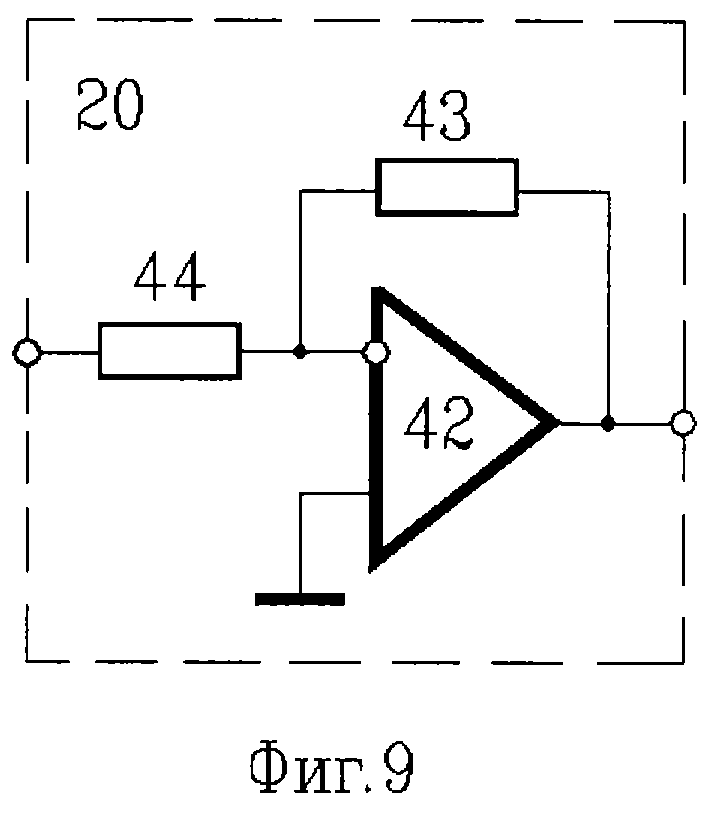

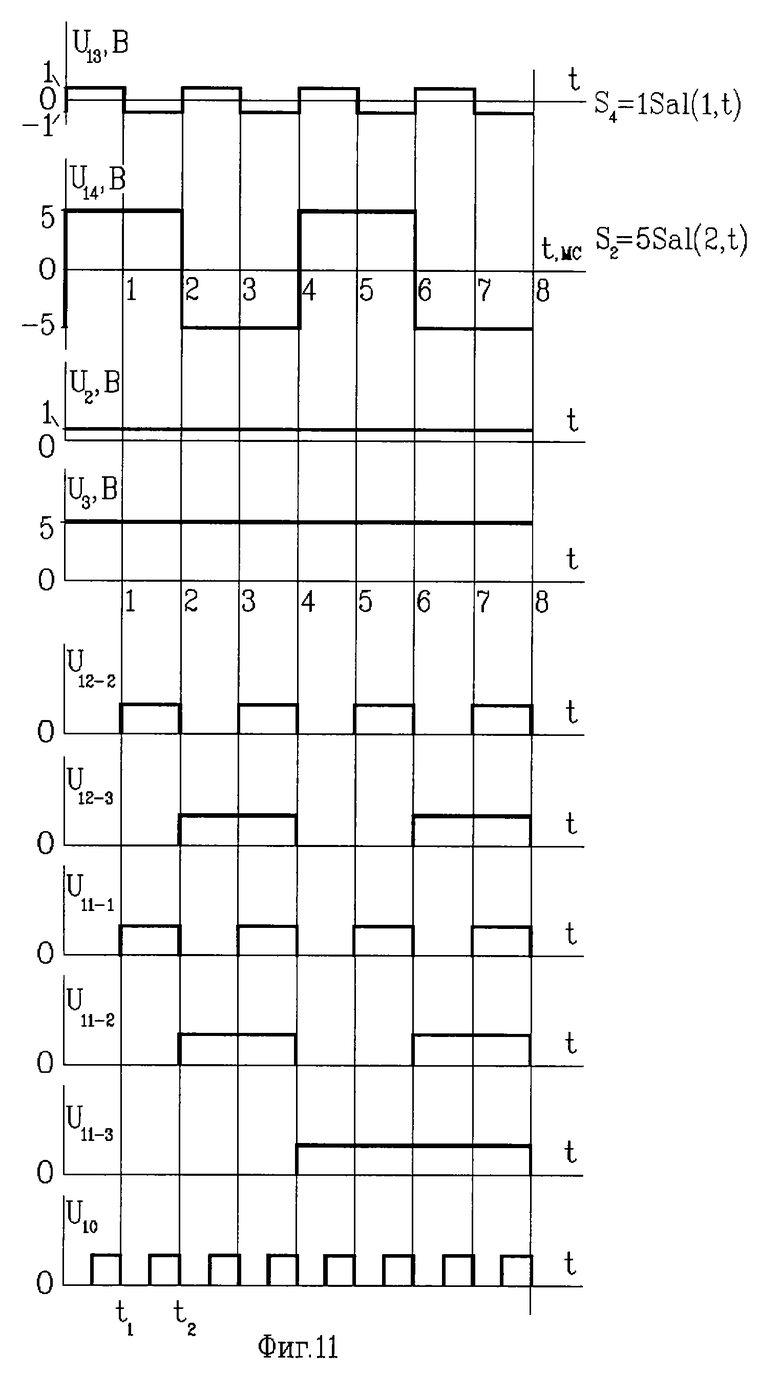

входному зажиму, вход вычитаемого блока вычитания j-й строки подключен к j-му входному зажиму, вход уменьшаемого блока вычитания j-й строки подключен к  входному зажиму; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с информационным входом j-го ключа, управляющий вход которого подключен к j-му выходу дешифратора. 2. Устройство по п.1, отличающееся тем, что каждый из блоков суммирования в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока суммирования и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый дополнительный резистор соединен с шиной нулевого потенциала, которая через второй дополнительный резистор соединена с неинвертирующим входом операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования. 3. Устройство по п.1, отличающееся тем, что каждый из блоков вычитания в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока вычитания и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый входной резистор подключен ко входу вычитаемого блока вычитания, вход уменьшаемого которого через второй входной резистор соединен с неинвертирующим входом операционного усилителя, который соединен с шиной нулевого потенциала через дополнительный резистор. 4. Устройство по п.1, отличающееся тем, что каждый из блоков суммирования во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования, выход первого операционного усилителя через третий входной резистор соединен с инвертирующим входом второго операционного усилителя, который через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока суммирования, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала. 5. Устройство по п.1, отличающееся тем, что каждый из блоков вычитания во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый входной резистор подключен ко входу уменьшаемого блока вычитания, выход первого операционного усилителя через второй входной резистор соединен с инвертирующим входом второго операционного усилителя, который через третий входной резистор подключен ко входу вычитаемого блока вычитания и через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока вычитания, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала. 6. Устройство для обратного преобразования Уолша (второй вариант), содержащее N-входовой (где N - число ортогональных составляющих спектра Уолша) блок суммирования, счетчик и генератор прямоугольных импульсов, выход которого соединен с тактовым входом счетчика, выход N-входового блока суммирования соединен с выходным зажимом устройства, отличающееся тем, что в него дополнительно введены цифровой блок памяти, N входных зажимов, N-1 каналов, содержащих N-1 инверторов, N-1 элементов НЕ, 2(N-1) ключей, причем каждый j-й (при j=2,...,N) входной зажим соединен со входом инвертора j-го канала и информационным входом первого ключа j-го канала, управляющий вход которого подключен к выходу элемента НЕ j-го канала, а выход объединен с выходом второго ключа j-го канала и соединен с j-м входом N-входового блока суммирования, первый вход которого подключен к первому входному зажиму, выход инвертора j-того канала соединен с информационным входом второго ключа j-го канала, выход счетчика соединен с адресным входом цифрового блока памяти, каждый j-й (при j=2,...,N) разряд выхода которого соединен со входом элемента НЕ и управляющим входом второго ключа j-го канала. 7. Устройство по п.6, отличающееся тем, что N-входовой блок суммирования в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока суммирования и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый дополнительный резистор соединен с шиной нулевого потенциала, которая через второй дополнительный резистор соединена с неинвертирующим входом операционного усилителя, который через входные резисторы с первого по N-й подключен ко входам блока суммирования с первого по N-й. 8. Устройство по п.6, отличающееся тем, что N-входовой блок суммирования во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через входные резисторы с первого по N-й подключен ко входам блока суммирования с первого по N-й, выход первого операционного усилителя через (N+1)-й входной резистор соединен с инвертирующим входом второго операционного усилителя, который через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока суммирования, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала. 9. Устройство по п. 6, отличающееся тем, что каждый из инверторов содержит операционный усилитель, выход которого является выходом инвертора и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через входной резистор подключен ко входу инвертора, неинвертирующий вход операционного усилителя соединен с шиной нулевого потенциала.

входному зажиму; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с информационным входом j-го ключа, управляющий вход которого подключен к j-му выходу дешифратора. 2. Устройство по п.1, отличающееся тем, что каждый из блоков суммирования в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока суммирования и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый дополнительный резистор соединен с шиной нулевого потенциала, которая через второй дополнительный резистор соединена с неинвертирующим входом операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования. 3. Устройство по п.1, отличающееся тем, что каждый из блоков вычитания в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока вычитания и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый входной резистор подключен ко входу вычитаемого блока вычитания, вход уменьшаемого которого через второй входной резистор соединен с неинвертирующим входом операционного усилителя, который соединен с шиной нулевого потенциала через дополнительный резистор. 4. Устройство по п.1, отличающееся тем, что каждый из блоков суммирования во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования, выход первого операционного усилителя через третий входной резистор соединен с инвертирующим входом второго операционного усилителя, который через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока суммирования, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала. 5. Устройство по п.1, отличающееся тем, что каждый из блоков вычитания во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый входной резистор подключен ко входу уменьшаемого блока вычитания, выход первого операционного усилителя через второй входной резистор соединен с инвертирующим входом второго операционного усилителя, который через третий входной резистор подключен ко входу вычитаемого блока вычитания и через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока вычитания, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала. 6. Устройство для обратного преобразования Уолша (второй вариант), содержащее N-входовой (где N - число ортогональных составляющих спектра Уолша) блок суммирования, счетчик и генератор прямоугольных импульсов, выход которого соединен с тактовым входом счетчика, выход N-входового блока суммирования соединен с выходным зажимом устройства, отличающееся тем, что в него дополнительно введены цифровой блок памяти, N входных зажимов, N-1 каналов, содержащих N-1 инверторов, N-1 элементов НЕ, 2(N-1) ключей, причем каждый j-й (при j=2,...,N) входной зажим соединен со входом инвертора j-го канала и информационным входом первого ключа j-го канала, управляющий вход которого подключен к выходу элемента НЕ j-го канала, а выход объединен с выходом второго ключа j-го канала и соединен с j-м входом N-входового блока суммирования, первый вход которого подключен к первому входному зажиму, выход инвертора j-того канала соединен с информационным входом второго ключа j-го канала, выход счетчика соединен с адресным входом цифрового блока памяти, каждый j-й (при j=2,...,N) разряд выхода которого соединен со входом элемента НЕ и управляющим входом второго ключа j-го канала. 7. Устройство по п.6, отличающееся тем, что N-входовой блок суммирования в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока суммирования и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый дополнительный резистор соединен с шиной нулевого потенциала, которая через второй дополнительный резистор соединена с неинвертирующим входом операционного усилителя, который через входные резисторы с первого по N-й подключен ко входам блока суммирования с первого по N-й. 8. Устройство по п.6, отличающееся тем, что N-входовой блок суммирования во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через входные резисторы с первого по N-й подключен ко входам блока суммирования с первого по N-й, выход первого операционного усилителя через (N+1)-й входной резистор соединен с инвертирующим входом второго операционного усилителя, который через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока суммирования, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала. 9. Устройство по п. 6, отличающееся тем, что каждый из инверторов содержит операционный усилитель, выход которого является выходом инвертора и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через входной резистор подключен ко входу инвертора, неинвертирующий вход операционного усилителя соединен с шиной нулевого потенциала.

(где k= 1, ..., 2i-1 - номер группы строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания;

(где k= 1, ..., 2i-1 - номер группы строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания;  число элементов в группе строк i-го столбца;

число элементов в группе строк i-го столбца;

, а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i=1,..., n,

, а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i=1,..., n,

причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,..., n, j=1,..., N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока

причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,..., n, j=1,..., N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока  строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, вход уменьшаемого блока вычитания j-й строки i-го столбца подключен к выходу блока

строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, вход уменьшаемого блока вычитания j-й строки i-го столбца подключен к выходу блока  строки (i-1)-го столбца; входы блоков 1-го столбца матрицы подключены к входным зажимам устройства следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к j-му входному зажиму, другой вход блока суммирования j-й строки подключен к

строки (i-1)-го столбца; входы блоков 1-го столбца матрицы подключены к входным зажимам устройства следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к j-му входному зажиму, другой вход блока суммирования j-й строки подключен к  входному зажиму, вход вычитаемого блока вычитания j-й строки подключен к j-му входному зажиму, вход уменьшаемого блока вычитания j-й строки подключен к

входному зажиму, вход вычитаемого блока вычитания j-й строки подключен к j-му входному зажиму, вход уменьшаемого блока вычитания j-й строки подключен к  входному зажиму; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с информационным входом j-го ключа, управляющий вход которого подключен к j-му выходу дешифратора.

входному зажиму; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с информационным входом j-го ключа, управляющий вход которого подключен к j-му выходу дешифратора.