Изобретение относится к неразрушающему контролю изделий и может быть использовано для определения их поверхностных дефектов.

Известен прибор для дефектоскопии поверхностей изделий, имеющий магниточувствительный преобразователь, определяющий уровень сигнала, который многократно принудительно изменяют посредством последовательных автоматических переключений до превышения порога, при этом регистрируют положение переключателя, по которому судят о структуре поверхностного слоя материала (авторское свидетельство СССР 1499205, МКИ G 01 N 27/82).

За прототип принят магнитотелевизионный дефектоскоп по авторскому свидетельству СССР 1523981, МКИ G 01 N 27/82, который снабжен многоэлементным чувствительным узлом для считывания с контролируемого изделия магнитного рельефа.

Обработка информации о рельефе выполняется пороговым блоком, вычислителем, счетчиками, блоком управления и генератором, соединенными между собой и с указателем по двухканальной схеме.

Известные дефектоскопы позволяют получать информацию об изделиях на участках, ограниченных размерами чувствительного узла, и не приспособлены к непрерывному контролю.

Целью изобретения является упрощение технологии непрерывного контроля партии однотипных изделий.

Суть предлагаемого изобретения заключается в постепенном совмещении очередных зон многоэлементного чувствительного блока с последующими участками контролируемого изделия и согласованном отключении предыдущих для продолжения непрерывного контроля последующих изделий.

Суть изобретения реализована совместным синхронным использованием множества сегментов памяти, многорядного блока преобразователей, содержащего отдельные датчики дефекта, усреднителя, пороговой линейки и индикатора. Синхронная работа устройства поддерживается блоком последовательно-параллельного управления, снабженного счетчиками, соединенными по двухступенчатой схеме.

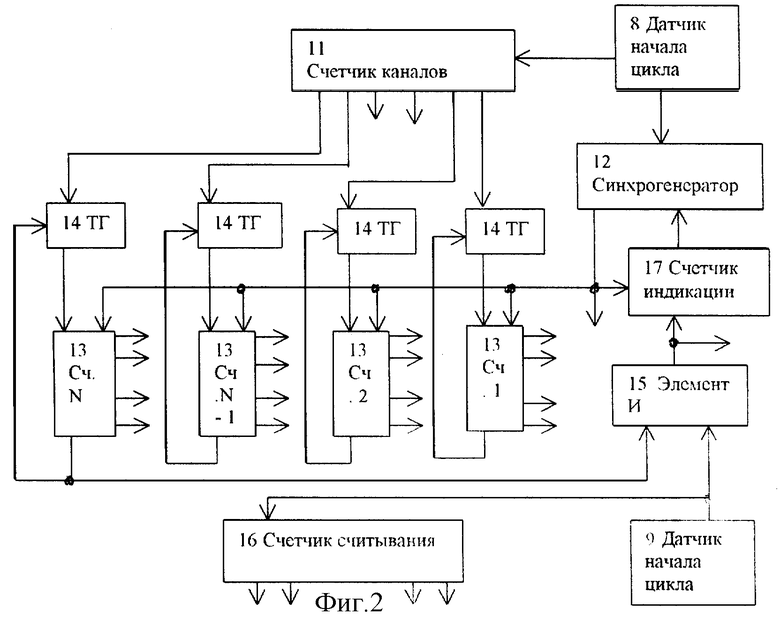

Устройство многоканального дефектоскопа представлено блок-схемой на фиг. 1.

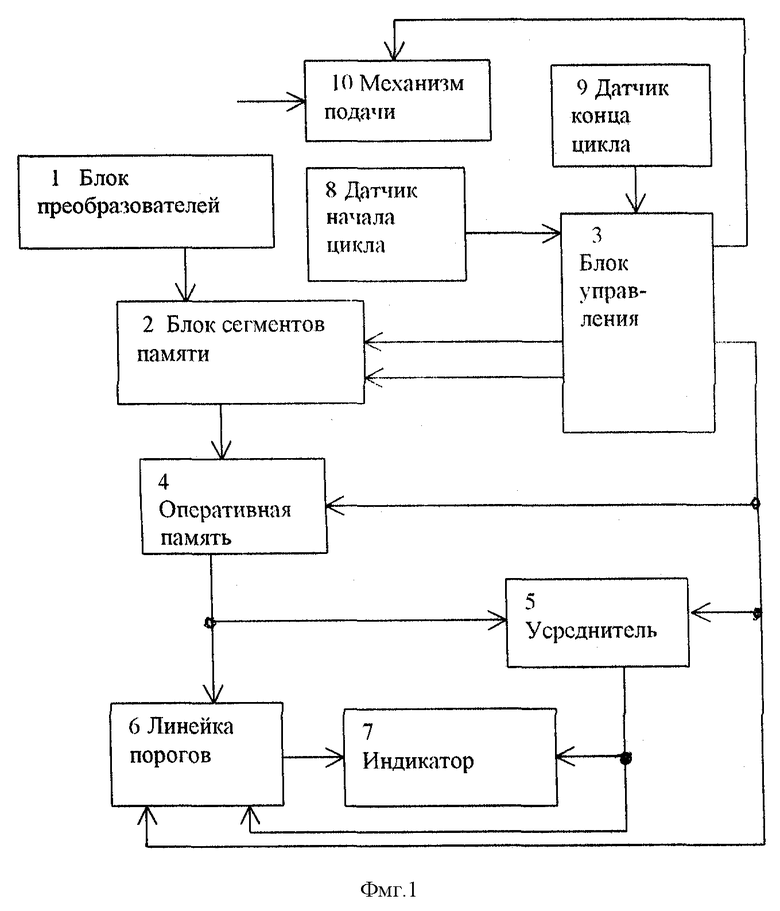

На фиг. 2 приведена схема блока последовательно-параллельного управления многоканального дефектоскопа.

Многорядный блок преобразователей 1 имеет множество датчиков дефекта для определения особенностей на поверхности контролируемых изделий. Датчики дефекта размещены рядами - N в несколько - М шеренг, то есть в каждом ряду по М датчиков дефекта.

Шаги между рядами датчиков дефекта и их шеренгами в многорядном блоке преобразователей 1 соответствуют зоне чувствительности отдельного датчика дефекта.

Протяженность шеренги выбрана не менее длины контролируемого изделия, в частности для роликов подшипника она превышает размер трех их диаметров,

Ряды ориентированы вдоль образующей ролика и соответствуют его длине.

Информационные выходы многорядного блока преобразователей 1 подключены к блоку сегментов памяти 2. Блок сегментов памяти снабжен множеством (М N G) ячеек памяти, составляющих N регистров, которые сгруппированы в несколько (G) сегментов.

Количество ячеек памяти в отдельном регистре выбрано равным количеству датчиков дефекта (М) в каждом ряду (N).

Количество сегментов в блоке сегментов памяти выбрано равным количеству контролируемых изделий в их партии (G).

Выходы датчиков дефекта отдельного ряда подключены параллельно к одноименным регистрам всех сегментов блока сегментов памяти соответственно номерам шеренг и их ячеек.

Таким образом, каждый первый датчик дефекта отдельного ряда подключен параллельно к первой ячейке в одноименных регистрах всех сегментов соответственно и так далее.

Управляющие входы записи регистров в отдельных сегментах блока сегментов памяти соединены с соответствующими первыми выходами блока последовательно-параллельного управления 3.

Информационные выходы блока сегментов памяти соединены с оперативной памятью 4, которая имеет количество ячеек, равное количеству их в одном сегменте, то есть, М N. При этом одноименные информационные выходы разных сегментов объединены на соответствующих входах оперативной памяти.

Управляющие входы считывания регистров, принадлежащих отдельным сегментам блока сегментов памяти, соединены с соответствующими вторыми выходами блока последовательно-параллельного управления 3.

Информационные выходы оперативной памяти 4 соединены параллельно с одноименными входами усреднителя 5 и линейки порогов 6.

Выходы усреднителя 5 и линейки порогов 6 соединены с разными входами индикатора 7.

Разрешающие входы оперативной памяти 4, усреднителя 5 и линейки порогов 6 соединены с третьим выходом блока последовательно-параллельного управления 3.

Линейка порогов снабжена входом ввода уставки, соединенным с выходом усреднителя.

Четвертый выход блока последовательно-параллельного управления соединен с управляющим входом механизма подачи 10, который кроме того снабжен входом "Пуск".

Блок последовательно-параллельного управления первым и вторым входами соединен соответственно с датчиками начала 8 и конца 9 циклов.

Датчик начала цикла размещен на уровне первого ряда датчиков дефекта многорядного блока преобразователей в зоне передней выступающей части контролируемого изделия по направлению его подачи.

Датчик конца цикла размещен на уровне последнего ряда датчиков дефекта многорядного блока преобразователей в зоне задней выступающей части контролируемого изделия.

Блок последовательно-параллельного управления 3 содержит счетчик каналов 11, имеющий G выходов и соединенный своим счетным входом с датчиком начала цикла 8 и входом синхрогенератора 12, и несколько счетчиков циклов 13, подключенных разрешающими входами через триггеры самоблокировки 14 к его G выходам.

Выходы счетчиков цикла являются первыми выходами блока последовательно-параллельного управления. Количество выходов у каждого из счетчиков цикла равно М, то есть по числу шеренг.

Вход сброса каждого триггера самоблокировки соединен с последним разрядом своего счетчика цикла.

Последний разряд последнего счетчика цикла кроме того соединен параллельно с элементом И 15, второй управляющий вход которого является вторым входом блока последовательно-параллельного управления и соединен с выходом датчика конца цикла и входом счетчика считывания 16, имеющим G выходов.

Выходы счетчика считывания являются вторыми выходами блока последовательно-параллельного управления.

Выход элемента И является четвертым выходом блока последовательно-параллельного управления и соединен параллельно с входами счетчика индикации 17 и механизма подачи 10.

Выход счетчика индикации соединен со вторым входом синхрогенератора 12.

Третий выход блока последовательно-параллельного управления является выходом синхрогенератора и подключен параллельно ко всем счетным входам счетчиков цикла и к разрешающим входам линейки порогов, оперативной памяти и усреднителя.

Для контроля партии роликов количество выходов счетчика каналов 11 равно количеству роликов в партии, то есть подшипнике.

Рассмотрим работу многоканального дефектоскопа на примере контроля рабочих поверхностей роликов в подшипнике при частичной его разборке, то есть, без внутреннего кольца, вместо которого установлен многорядный блок преобразователей.

После запуска механизма подачи 10 начинается смещение партии контролируемых изделий и счетчик каналов 11 переключает свои выходы по каждому сигналу, поступающему от датчика начала цикла 8, который отмечает приближение очередного контролируемого изделия. В частности, одного из роликов, установленных в сепаратор и наружную обойму подшипника, приводимого в движение фрикционом механизма подачи. Одновременно запускается синхрогенератор 12.

В соответствии с конструкцией подшипника очередной сигнал от датчика начала цикла поступает после смещения предыдущего ролика на расстояние не менее диаметра ролика.

Включенные между счетчиками каналов 11 и цикла 13 триггеры самоблокировки 14 удерживают свои счетчики цикла в рабочем состоянии, несмотря на переключения выходов счетчика каналов при смещении очередных контролируемых изделий из партии вдоль многорядного блока преобразователей.

Синхрогенератор через первый выход первого счетчика цикла разрешает внесение в первый регистр памяти первого сегмента информации, полученной от первого ряда датчиков дефекта многорядного блока преобразователей. Информация от датчиков дефекта каждого ряда вносится в ячейки регистров параллельно.

Следующий синхроимпульс отключает предыдущий выход счетчика цикла и включает очередной, допуская внесение информации в последующий регистр памяти от последующего ряда датчиков дефекта. В пределах каждого сегмента запись информации происходит последовательно ряд за рядом.

Блок последовательно-параллельного управления после прохождения предыдущим контролируемым изделием одной трети протяженности шеренг подключает очередной счетчик цикла и информация об очередном контролируемом изделии начинает поступать в последовательные регистры памяти другого сегмента.

Таким образом, информация о трех контролируемых изделиях параллельно поступает в блок сегментов памяти 2 от одного многорядного блока преобразователей, но со сдвигом во времени и в разные ее сегменты.

Когда первое контролируемое изделие покидает границы многорядного блока преобразователей, в его начале размещается четвертое и датчик конца цикла подает сигнал на счетчик считывания.

При этом последний разряд первого счетчика цикла перебрасывает свой триггер и счетчик в исходное состояние.

Первый выход счетчика считывания, воздействуя на вход считывания блока сегментов памяти, передает информацию из первого сегмента в оперативную память. Из оперативной памяти после разрешающих команд синхрогенератора она поступает в усреднитель и на линейку порогов.

Усреднитель определяет среднее значение по всему объему сегмента и передает его в качестве общей уставки на линейку порогов и в индикатор. Усреднение информации всего объема сегмента позволяет получить значение порога, обладающее высокой достоверностью, без применения эталонных образцов на разные типы дефектов. Исключение эталонных образцов дефектов упрощает технологию контроля.

Линейка порогов выделяет возможные превышения сопоставляемой информации и передает их в индикатор по другому входу.

Индикатор фиксирует полученные данные, по которым судят о качестве или дефектности контролируемого изделия в целом без классификации типа дефектов.

Сигналы последнего разряда последнего счетчика цикла и датчика конца совместно через элемент И включают счетчик индикации, который, спустя два импульса, необходимых для вывода последней информации, отключает синхрогенератор после отключения механизма подачи.

Предлагаемое изобретение, позволяя избежать применения эталонных образцов на разнообразные типы дефектов, существенно упрощает и сокращает процесс оценки качества изделий, особенно, при непрерывном дефектоскопировании их партии.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ВИБРОДИАГНОСТИКИ РОТОРНЫХ МЕХАНИЗМОВ | 1999 |

|

RU2153660C1 |

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИРОВАНИЯ ЦИКЛИЧЕСКИ ФУНКЦИОНИРУЮЩИХ ОБЪЕКТОВ | 2000 |

|

RU2177607C1 |

| АНАЛИЗАТОР РЕЖИМОВ ТЯГОВОГО СРЕДСТВА | 2000 |

|

RU2192668C2 |

| СПОСОБ ЭЛЕКТРОИНДУКЦИОННОЙ ДЕФЕКТОСКОПИИ МАТЕРИАЛОВ | 1999 |

|

RU2159425C1 |

| ИЗМЕРИТЕЛЬ УГЛА ОПЕРЕЖЕНИЯ ВПРЫСКА ТОПЛИВА В ДИЗЕЛЬ | 2002 |

|

RU2211364C1 |

| ТРЕХКООРДИНАТНЫЙ ПРИВОД | 2001 |

|

RU2239906C2 |

| ИЗМЕРИТЕЛЬ УГЛА ОПЕРЕЖЕНИЯ ВПРЫСКА ТОПЛИВА В ДИЗЕЛЬ | 2003 |

|

RU2241138C2 |

| ИЗМЕРИТЕЛЬ НАКЛОНА ВАЛА РОТОРНОГО МЕХАНИЗМА | 2003 |

|

RU2253088C1 |

| ПУТЕВОЙ ИНСТРУМЕНТ | 1999 |

|

RU2176001C2 |

| ПЕЧЬ ДЛЯ СУШКИ ОБМОТОК ЭЛЕКТРОМАШИН | 2001 |

|

RU2204879C2 |

Изобретение относится к неразрушающему контролю изделий и может быть использовано для определения их поверхностных дефектов. Технический результат: упрощение технологии непрерывного контроля партии однотипных изделий. Сущность изобретения заключается в совместном синхронном использовании множества сегментов памяти, многорядного блока преобразователей, содержащего отдельные датчики дефекта, усреднителя, пороговой линейки и индикатора. Синхронная работа устройства поддерживается блоком последовательно-параллельного управления, снабженного счетчиками, соединенными по двухступенчатой схеме. 2 з.п.ф-лы, 2 ил.

| Магнитотелевизионный дефектоскоп | 1988 |

|

SU1523981A1 |

| Магнитотелевизионный дефектоскоп | 1986 |

|

SU1397818A1 |

| Приемное устройство для электрической телескопии | 1924 |

|

SU5035A1 |

| US 4430614, 07.02.1984 | |||

| US 4445088, 24.04.1984. | |||

Авторы

Даты

2002-12-10—Публикация

2001-08-14—Подача