Изобретение относится к вычислительной технике и может быть использовано в распределенных вычислительных системах, содержащих несколько активных источников информации, подключенных к общей магистрали.

Известно многоканальное устройство для подключения абонентов к общей магистрали (А.c. СССР 860073, G 06 F 9/46, 1979), содержащее регистр адреса, счетчик, триггер, группу элементов И, два дешифратора, два коммутатора, сумматор по mod 2 и соответствующие связи между ними. Однако известное устройство может быть использовано только в вычислительных системах, общая магистраль которых построена таким образом, что сигналы от нескольких источников складываются по ИЛИ. Если это условие не выполняется, устройство не может быть использовано. Таким образом, недостатком устройства является ограниченная область применения. Кроме того, общая магистраль является многолинейной, и значительная стоимость магистрали приводит к тому, что при удалении источников информации друг от друга общая стоимость вычислительной системы резко возрастает.

Наиболее близким по технической сущности к предлагаемому является устройство для подключения источника информации к общей магистрали (А.c. СССР 1156085, G 06 F 13/36, 1983), содержащее регистр адреса, счетчик приоритета и первый триггер, выход которого соединен с входом разрешения тактирования счетчика приоритета, тактовый и группа установочных входов которого соединены соответственно с тактовым входом устройства и с группой выходов регистра адреса, отличающееся тем, что, с целью расширения области применения, в него введены первый и второй согласующие элементы, одновибратор, элемент И, 2И-ИЛИ, первый, второй и третий триггеры и первый и второй элементы задержки, при этом вход и выход первого согласующего элемента соединены соответственно с магистралью и с входом одновибратора, выход которого соединен с информационным входом второго триггера и с инверсным входом элемента И, прямой вход которого соединен с входом запроса устройства, выход элемента И соединен с прямым входом первого триггера, инверсный вход которого соединен с выходом переполнения счетчика приоритета и с входом первого элемента задержки, выход которого соединен с синхровходом второго триггера и с входом второго элемента задержки, выход которого соединен с прямым входом третьего триггера, инверсный вход которого соединен с выходом второго триггера, выходы второго и третьего триггеров соединены соответственно с выходами отказа связи и разрешения связи устройства, выход первого триггера и тактовый вход устройства соединены с первым и вторым входами элемента 2И-ИЛИ, выход которого через второй согласующий элемент соединен с общей магистралью.

Недостаток устройства-прототипа заключается в том, что не обеспечивается передача различными абонентами сообщений различных приоритетов (категорий срочности), в связи с тем что приоритеты при передаче информации жестко закреплены за абонентами.

Целью изобретения является разработка устройства подключения источника информации к общей магистрали, обеспечивающего приоритетное обслуживание потоков сообщений различных категорий срочности от каждого из абонентов с разными приоритетами в системе.

Поставленная цель достигается тем, что в известное устройство подключения источника информации к общей магистрали, содержащее первый и второй согласующие элементы, одновибратор, первый, второй и третий триггеры, первый и второй элементы И, первый и второй элементы задержки, причем вход и выход первого согласующего элемента соединены соответственно с общей магистралью и входом одновибратора, выход которого соединен с информационным входом второго триггера и инверсным входом второго элемента И, прямой вход которого является входом запроса устройства, а выход второго элемента И соединен с прямым входом первого триггера, инверсный вход которого соединен с входом первого элемента задержки, выход которого соединен с синхровходом второго триггера и входом второго элемента задержки, выход которого соединен с прямым входом третьего триггера, выход которого является выходом "Разрешения передачи" устройства, а выход второго триггера является выходом ''отказ'' устройства, первый вход первого элемента И является информационным входом устройства, а выход второго согласующего элемента соединен с общей магистралью, дополнительно введены блок анализа приоритета, датчик случайных чисел, N-дешифраторов, где N≥2, первый, второй и третий элементы ИЛИ, формирователь импульсов, четвертый триггер. Причем первый элемент ИЛИ выполнен N-входовым. Выход первого триггера соединен со входом формирователя импульсов. Выход формирователя импульсов соединен с инверсным входом первого триггера и вторым входом второго элемента ИЛИ. Выход второго элемента ИЛИ соединен с входом второго согласующего элемента, а первый вход соединен с выходом первого элемента И. Второй вход первого элемента И соединен с выходом четвертого триггера. Инверсный вход четвертого триггера соединен с входом запроса устройства, а прямой вход подключен к выходу первого элемента ИЛИ. N-входов первого элемента ИЛИ соединены с выходами соответствующих N-дешифраторов, информационные входы которых объединены и соединены с выходом датчика случайных чисел, а сигнальные входы каждого из N-дешифраторов соединены с соответствующими выходами блока анализа приоритета. Вход блока анализа приоритета соединен с приоритетным входом устройства. Вход датчика случайных чисел соединен с выходом "Разрешение передачи" устройства и вторым входом третьего элемента ИЛИ. Выход третьего элемента ИЛИ соединен с инверсным входом третьего триггера, а первый вход третьего элемента ИЛИ соединен с выходом второго триггера.

Благодаря новой совокупности существенных признаков за счет введения блока анализа приоритета, датчика случайных чисел, дешифраторов и соответствующих новых связей обеспечивается возможность приоритетного обслуживания потоков сообщений различных категорий срочности от каждого из абонентов системы по приоритету.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявляемое устройство поясняется чертежами:

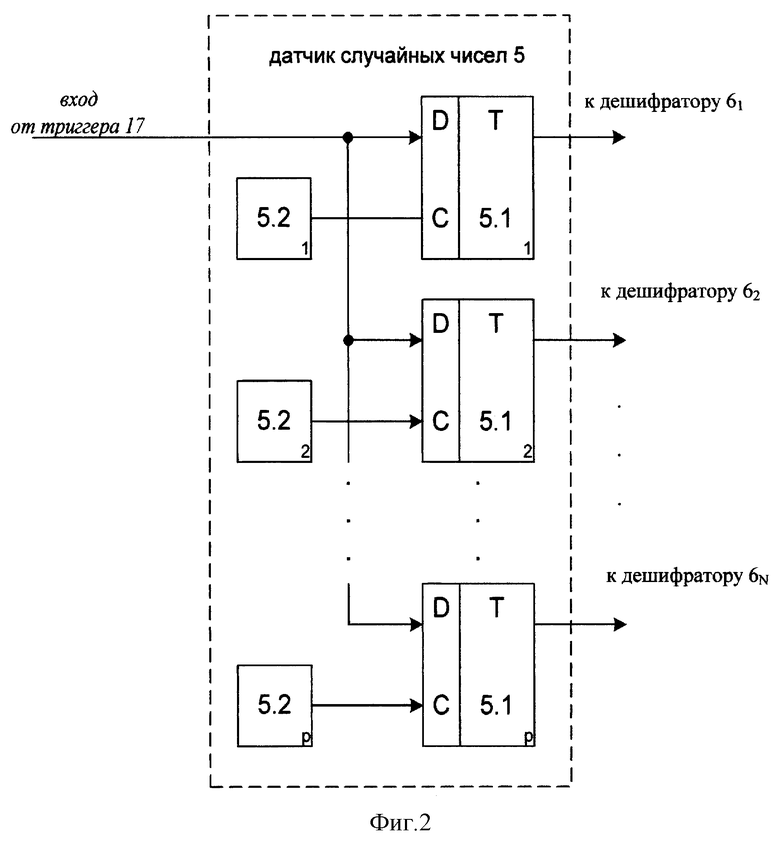

фиг. 1 - функциональная схема устройства;

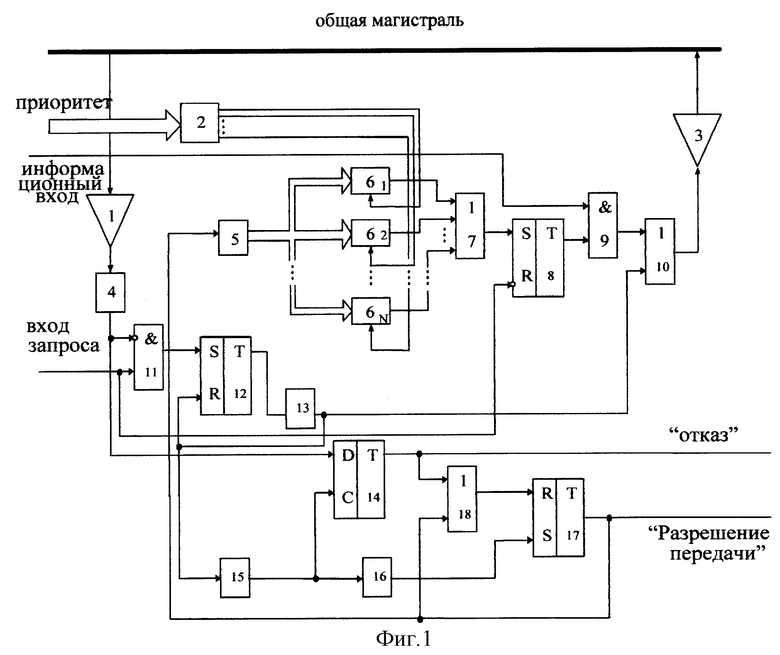

фиг. 2 - схема датчика случайных чисел.

Заявляемое устройство подключения источника информации к общей магистрали, показанное на фиг.1, состоит из: первого согласующего элемента 1, второго согласующего элемента 3, блока 2 анализа приоритета, одновибратора 4, датчика 5 случайных чисел, первого триггера 12, второго триггера 14, третьего триггера 17, четвертого триггера 8, первого элемента И 9, второго элемента И 11, первого элемента 15 задержки, второго элемента 16 задержки, N дешифраторов (61-6N), первого элемента ИЛИ 7, второго элемента ИЛИ 10, третьего элемента ИЛИ 18, формирователя 13 импульсов. Вход и выход первого согласующего элемента 1 соединены соответственно с общей магистралью и входом одновибратора 4. Выход одновибратора 4 соединен с информационным входом второго триггера 14 и инверсным входом второго элемента И 11. Прямой вход второго элемента И 11 соединен с входом запроса устройства и инверсным входом четвертого триггера 8. Выход второго элемента И 11 соединен с прямым входом первого триггера 12. Выход первого элемента 15 задержки соединен с синхровходом второго триггера 14 и входом второго элемента 16 задержки. Выход второго элемента 16 задержки соединен с прямым входом третьего триггера 17. Инверсный вход второго триггера 12 соединен с выходом формирователя 13 импульсов, вторым входом второго элемента ИЛИ 10 и входом первого элемента 15 задержки. Инверсный вход третьего триггера 17 соединен с выходом третьего элемента ИЛИ 18. Выход третьего триггера 17 соединен с выходом разрешения передачи устройства, входом датчика 5 случайных чисел и вторым входом третьего элемента ИЛИ 18. Первый вход третьего элемента ИЛИ 18 соединен с выходом отказа устройства и выходом второго триггера 14. Выход первого триггера 12 соединен с входом формирователя 13 импульсов. Вход блока 2 анализа приоритета соединен входом приоритета устройства. Выходы блока 2 анализа приоритета соединены с сигнальными входами соответствующих дешифраторов 6. Информационные входы дешифраторов 6 соединены с выходом датчика 5 случайных чисел. Выходы дешифраторов 6 соединены с входами первого элемента ИЛИ 7. Выход первого элемента ИЛИ 7 соединен с прямым входом четвертого триггера 8. Выход четвертого триггера 8 соединен со вторым входом первого элемента И 9. Первый вход первого элемента И 9 соединен с информационным входом устройства. Выход элемента И 9 соединен с первым входом второго элемента ИЛИ 10. Выход второго элемента ИЛИ 10 соединен с входом второго согласующего элемента 3. Выход второго согласующего элемента 3 соединен с общей магистралью.

Датчик 5 случайных чисел, показанный на фиг.2, предназначен для выдачи случайной кодовой комбинации с целью обеспечения возможности приоритетного обслуживания пакета при передаче и состоит из D-триггеров 5.11-5.1р и генераторов 5.21-5.2p шума, при этом информационные входы триггеров 5.11-5.1р соединены с выходом триггера 17, а тактовые входы триггеров 5.11-5.1р соединены с выходами генераторов 5.21-5.2p шума соответственно.

Входящие в общую функциональную схему элементы имеют следующее назначение.

Блок 2 анализа приоритета представляет собой демультиплексор, предназначенный для распределения сигналов с одного входа на несколько выходов и описан в книге - Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова. - СПВВИУС, 1995, с. 152 -156.

Генераторы 5.21-5.2p шума предназначены для формирования случайно изменяющихся во времени выходных напряжений. Схемы их известны и описаны в книге - Элементы радиоэлектронных устройств / Б.И.Коротков. - М.: Радио и связь, 1988, рис.7.24, с. 107.

Сумматоры по модулю два, входящие в группу дешифраторов (61-6N), предназначены для суммирования по модулю два в двоичном коде двух разрядов, поступающих на входы каждого из них. Могут быть реализованы по схеме, описанной в книге - Импульсные и цифровые устройства. Цифровые узлы и их проектирование на микросхемах / О.И.Лебедев, А.М.Сидоров. - Л.: ВАС, 1980, рис. 2.9, с. 31-34.

Дешифраторы 61-6N предназначены для преобразования двоичного кода в напряжение логического уровня известны и описаны в книге - Популярные цифровые микросхемы / В.Л.Шило. - М.: Радио и связь, 1987, с. 130-142.

Формирователь 13 импульсов предназначен для формирования из логического уровня короткого импульса, идентичен, известен и описан в книге - Основы цифровой техники / Л.А.Мальцева. - М.: Радио и связь, 1986, рис. 21, с. 30.

Остальные элементы общей функциональной схемы известны и описаны, например:

Логические элементы И 9, 11 в книге - Основы цифровой техники /Л.А.Мальцева, Э. М.Фромберг. - М.: Радио и связь, с. 30 31. Могут быть реализованы на ИМС серий 133 и 564.

Логические элементы ИЛИ 7, 10, 18 (фиг.1) - в книге Основы импульсной и цифровой техники/ Под общей ред. А.М. Сидорова. - СПВВИУС, 1995, рис. 2.4, с. 39-41.

Датчик 5 случайных чисел в книге - Основы цифровой техники /Л.А.Мальцева, Э.М.Фромберг. - М.: Радио и связь, - с. 30 31.

RS-триггеры 8, 12, 17 в книге - Микросхемы и их применение: Справочное пособие./ В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. - М.: Радио и связь 1984, с.122, рис.4.16. Могут быть реализованы на ИМС серий 133, 564.

Элементы 15 и 16 задержки в книге - Цифровые интегральные микросхемы: Справочник / П.П.Мальцев и др. - М.: Радио и связь 1994, с. 52.

Согласующие элементы 1 и 3 могут быть реализованы на ИМС К100ЛМ102, описанной в книге - Элементы радиоэлектронных устройств / Б.И.Горошков. - М. : Радио и связь, 1988, с.119.

D-триггеры 14, 5.11-5.1p в книге - Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова. - СПВВИУС, 1995, с. 90-91.

Одновибратор 4 может быть реализован на ИМС К155АГ1, описанной в книге - Элементы радиоэлектронных устройств / Б.И. Горошков. - М.: Радио и связь, 1988, с.135.

Заявляемое устройство работает следующим образом.

В основу достижения заявленного технического результата включается сущность работы заявленного устройства, которая заключается в том, что при необходимости передачи пакета и при условии освобождения линии связи с вероятностью Рi передает пакет, а с вероятностью (1-Pi) откладывает передачу до начала следующего сигнала незанятости канала (где i-приоритет передаваемого пакета), причем P1>P2>P3 >...> PN, то есть вероятность предоставления линии связи для передачи пакетов высших приоритетов выше, чем соответствующая вероятность для низкоприоритетных пакетов. Тем самым обеспечивается первоочередное обслуживание высокоприоритетных пакетов в потоке пакетов различных приоритетов от каждого из абонентов.

Функциональная схема устройства подключения источников информации к общей магистрали, реализующего выполнение описанных функций, приведена на фиг. 1.

В исходном состоянии триггеры 8, 12, 14, 17 находятся в нулевом состоянии, на входе запроса и на выходах отказа и разрешения передачи устройства - логический нуль. При передаче по каналу связи информации на выходе одновибратора 4 сохраняется уровень логической единицы. Если канал свободен, на выходе одновибратора - логический нуль.

Пусть канал занят (то есть некоторые абоненты потребовали подключения к каналу, установив на своих входах запроса уровень логической единицы). Так как второй элемент И 11 закрыт по инверсному входу, то попытки подключения абонентов к каналу связи начинаются после того, как на выходе одновибратора 4 устанавливается уровень логического нуля. Этот момент наступает для всех абонентов с точностью до времени Т распространения сигнала в канале связи. Сигнал с уровнем логической единицы со входа запроса подготавливает к переходу в единичное состояние четвертый триггер 8, а также устанавливает в единичное состояние первый триггер 12, который выдает сигнал с уровнем логической единицы на вход формирователя 13 импульсов. Импульс с выхода последнего поступает на вход первого элемента 15 задержки, через второй элемент ИЛИ 10 и второй согласующий элемент 3 в линию связи, а также переводит первый триггер 12 в нулевое состояние. С выхода первого элемента 15 задержки импульс поступает на вход второго элемента 16 задержки, а также на синхровход второго триггера 14. Последний переходит в единичное состояние только в том случае, если на выходе одновибратора 4 устанавливается уровень логической единицы (то есть канал связи занят другим абонентом). При этом на выходе отказа устройства устанавливает уровень логической единицы, сигнализируя абоненту о том, что требование на подключение не удовлетворено (третий триггер 17 удерживается в нулевом состоянии сигналом с уровнем логической единицы, поступающим на инверсный вход третьего триггера 17 раньше, чем импульс с выхода второго элемента 16 задержки - на прямой вход этого триггера).

Если в момент прихода импульса с выхода первого элемента 15 задержки на синхровход второго триггера 14 на выходе одновибратора 4 устанавливается уровень логического нуля (то есть канал связи свободен), то второй триггер 14 остается в нулевом состоянии, а третий триггер 17 переходит в единичное состояние.

Одновременно с сигналом запроса на приоритетный вход устройства (и соответственно на вход блока 2 анализа приоритета) поступает кодовая комбинация приоритета передаваемого сообщения. При этом с одного из N выходов блока 2 анализа приоритета (где N число приоритетов) сигнал с уровнем логической единицы поступает на управляющий вход соответствующего дешифратора 6, при этом последний подготавливается к приему случайной кодовой комбинации от датчика 5 случайных чисел.

Как только третий триггер 17 переходит в единичное состояние, сигнал с уровнем логической единицы с его выхода поступает на выход разрешения передачи устройства, затем переводит третий триггер 17 в исходное (нулевое) состояние, а также поступает на управляющий вход датчика 5 случайных чисел; случайная кодовая комбинация с выходов последнего в параллельном коде поступает одновременно на входы всех N дешифраторов 6. Подготовленный к приему случайной кодовой комбинации дешифратор 6i (где i - приоритет передаваемого сообщения) с вероятностью Pi выдает сигнал с уровнем логической единицы через многовходовый первый элемент ИЛИ 7 на единичный вход четвертого триггера 8 (с вероятностью (1-Pi) это событие не происходит). В первом случае четвертый триггер 8 открывает первый элемент И 9, обеспечивая тем самым передачу информации в канал связи с информационного входа устройства через второй элемент ИЛИ 10 и второй согласующий элемент 3.

При снятии сигнала запроса с соответствующего входа устройства последнее переходит в исходное состояние.

Датчик 5 случайных чисел работает следующим образом.

На D-входах каждого из триггеров 5.1 имеют место случайно изменяющиеся во времени выходные напряжения независимых генераторов 5.2 шума. Если в момент появления импульса на счетном входе С р-го триггера 5.1 выходное напряжение р-го генератора 5.2 шума ниже порога срабатывания триггера, то на выходе триггера будет иметь место уровень логического нуля (в противном случае - уровень логической единицы). Случайная кодовая комбинация с выходов триггера 5.1 поступает на сигнальные входы дешифраторов 61-6N.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2216869C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2002 |

|

RU2207735C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2157561C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2002 |

|

RU2212107C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| УСТРОЙСТВО ДЛЯ ПРИОРИТЕТНОГО ОБСЛУЖИВАНИЯ ЗАЯВОК | 1999 |

|

RU2158022C1 |

| СПОСОБ ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2001 |

|

RU2179737C1 |

Изобретение относится к вычислительной технике и может быть использовано в распределенных вычислительных системах, содержащих несколько активных источников информации, подключенных к общей магистрали. Техническим результатом является возможность обеспечения приоритетного обслуживания потоков сообщений различных категорий срочности от каждого из абонентов с разными приоритетами в системе. Устройство содержит два согласующих элемента, блок анализа приоритета, одновибратор, датчик случайных чисел, четыре триггера, два элемента И, два элемента задержки, N дешифраторов, три элемента ИЛИ, формирователь импульсов. 2 ил.

Устройство подключения источника информации к общей магистрали, содержащее первый и второй согласующие элементы, одновибратор, первый, второй и третий триггеры, первый и второй элементы И, первый и второй элементы задержки, причем вход и выход первого согласующего элемента соединены соответственно с общей магистралью и входом одновибратора, выход которого соединен с информационным входом второго триггера и инверсным входом второго элемента И, прямой вход которого является входом запроса устройства, а выход второго элемента И соединен с прямым входом первого триггера, инверсный вход которого соединен с входом первого элемента задержки, выход которого соединен с синхровходом второго триггера и входом второго элемента задержки, выход которого соединен с прямым входом третьего триггера, выход которого является выходом "Разрешения передачи" устройства, а выход второго триггера является выходом "отказ" устройства, первый вход первого элемента И является информационным входом устройства, а выход второго согласующего элемента соединен с общей магистралью, отличающееся тем, что в него дополнительно введены блок анализа приоритета, датчик случайных чисел, N дешифраторов, где N≥2, первый, второй и третий элементы ИЛИ, причем первый элемент ИЛИ выполнен N-входовым, формирователь импульсов, четвертый триггер, при этом выход первого триггера соединен со входом формирователя импульсов, выход которого соединен с инверсным входом первого триггера и вторым входом второго элемента ИЛИ, выход которого соединен с входом второго согласующего элемента, а первый вход второго элемента ИЛИ соединен с выходом первого элемента И, второй вход которого соединен с выходом четвертого триггера, инверсный вход которого соединен с входом запроса устройства, а прямой вход подключен к выходу первого элемента ИЛИ, N входов которого соединены с выходами соответствующих N дешифраторов, информационные входы которых объединены и соединены с выходом датчика случайных чисел, а сигнальные входы каждого из N дешифраторов соединены с соответствующими выходами блока анализа приоритета, вход которого соединен с приоритетным входом устройства, а вход датчика случайных чисел соединен с выходом "Разрешение передачи" устройства и вторым входом третьего элемента ИЛИ, выход которого соединен с инверсным входом третьего триггера, а первый вход третьего элемента ИЛИ соединен с выходом второго триггера.

| Устройство для подключения источника информации к общей магистрали | 1983 |

|

SU1156085A1 |

| Устройство для приоритетного подключения источников информации к магистрали | 1979 |

|

SU860073A2 |

| DE 3334123 A1, 11.04.1985 | |||

| US 4707782 A, 17.11.1987. | |||

Авторы

Даты

2002-12-10—Публикация

2001-01-09—Подача