Изобретение относится к вычислительной технике и может использоваться в узлах коммутации пакетов (сообщений) сети связи с интеграцией служб, сети передачи данных (сети ПД) автоматизированной системы управления (АСУ) при управлении передачей пакетной информации по широковещательному многоточечному радиоканалу. И, кроме того, предназначено для расширения арсенала данных технических устройств.

Известно устройство для управления передачей данных по радиоканалу (А.С. СССР 1162058, кл. Н 04 L 7/00, 1985), содержащее синхронизатор, первый и второй элементы И, элемент задержки, элемент ИЛИ, счетчик, триггер цикла передачи, генератор случайных чисел, блок сравнения, триггер разрешения передачи, формирователь импульсов.

Однако устройство имеет недостаток: относительно малую пропускную способность, что обусловлено отсутствием адаптации схемы устройства к изменению параметров нагрузки.

Известно устройство для управления передачей данных по радиоканалу (А.С. СССР 1319298, МПК5 Н 04 L 7/00, 1990), содержащее генератор случайных чисел и синхронизатор, первый, второй, третий и четвертый элементы И, счетчик, блок сравнения, триггер цикла передачи, триггер разрешения передачи, два формирователя импульсов, элемент ИЛИ, два элемента задержки.

Однако устройство имеет недостаток: относительно малую пропускную способность, что обусловлено отсутствием адаптации схемы устройства к изменению параметров нагрузки.

Наиболее близким по технической сущности и выполняемым функциям к заявляемому является устройство управления передачей данных по радиоканалу (см. патент Р. Ф. 2116004, МПК 5 Н 04 L 7/00, от 20.07.98 г.), содержащее кодер, генератор случайных чисел, синхронизатор, счетчик, первый и второй элементы И, RS-триггер, блок сравнения, блок преобразования, первый и второй дискретные фильтры Калмана, счетчик необслуженной нагрузки и первый счетчик обслуженной нагрузки, решающий блок, коррелятор, блок анализа адреса и категории срочности, причем информационный вход и сигнальный выход кодера являются соответственно информационным входом и сигнальным выходом устройства, выход блока преобразования подключен к сигнальному входу кодера, информационному входу генератора случайных чисел и информационному входу счетчика, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом генератора случайных чисел, управляющий вход которого подключен к выходу первого элемента И и входу "Сброс" (вход R) RS-триггера, вход "Установка" (вход S) которого подключен к выходу блока сравнения, являющемуся управляющим выходом устройства, выход RS-триггера подключен ко второму входу второго элемента И, первый вход которого соединен с выходом синхронизатора и управляющим входом счетчика, а выход второго элемента И соединен со вторым входом первого элемента И, вход коррелятора является сигнальным входом устройства, а выход коррелятора подключен к входу решающего блока, информационно-адресный выход которого подключен к информационно-адресному входу блока анализа адреса и категории срочности, а первый и второй управляющие выходы решающего блока подключены к входам соответственно счетчика необслуженной нагрузки и первого счетчика обслуженной нагрузки, выходы счетчика необслуженной нагрузки и первого счетчика обслуженной нагрузки подключены ко входам соответственно первого и второго фильтров Калмана, выходы которых подключены соответственно к первому и второму входам блока преобразования, вход адреса и категории срочности блока анализа адреса и категории срочности является входом адреса и категории срочности устройства, а первый и второй информационные выходы блока анализа адреса и категории срочности являются соответственно первым и вторым информационными выходами устройства.

Данное устройство осуществляет управление передачей данных по радиоканалу с множественным доступом и обеспечивает, в сравнении с рассматриваемыми аналогами, повышение пропускной способности канала связи за счет адаптации к изменению параметров нагрузки.

Однако устройство-прототип все же имеет относительно невысокую пропускную способность, это объясняется тем, что оно не обеспечивает группирование потока пакетов от абонентов, адаптацию объема пакетизатора с учетом интенсивности и характера группирования потока пакетов от абонентов и потоковой обстановки в канале множественного доступа.

Целью изобретения является разработка устройства управления передачей данных в канале множественного доступа, обеспечивающего более высокую пропускную способность за счет группирования потока пакетов от абонентов, адаптацию объема пакетизатора с учетом интенсивности и характера группирования потока пакетов от абонентов и потоковой обстановки в канале множественного доступа.

Поставленная цель достигается тем, что в известное устройство управления передачей данных по радиоканалу, содержащее синхронизатор, выход которого соединен с первым входом первого элемента И и входом счетчика, выход которого соединен с первым входом блока сравнения, выход которого соединен с единичным входом RS-триггера, выход которого соединен с вторым входом первого элемента И, выход которого соединен с вторым входом второго элемента И, первый вход которого является управляющим входом устройства, выход второго элемента И соединен с нулевым входом RS-триггера и управляющим входом датчика случайных чисел, выход которого соединен с вторым входом блока сравнения, коррелятор, вход которого является сигнальным входом устройства, а выход соединен с сигнальным входом решающего блока, первый и второй информационные выходы которого соединены с входами соответственно счетчика необслуженной нагрузки и счетчика обслуженной нагрузки, а выходы счетчиков необслуженной и обслуженной нагрузки соединены с входами соответственно первого и второго фильтров Калмана, выходы первого и второго фильтров Калмана соединены соответственно с первым и вторым входами блока преобразования, дополнительно введены пакетизатор, блок адаптации, блок управления передачей. Причем информационный вход пакетизатора является информационным входом устройства, а выход пакетизатора является информационным выходом устройства. Управляющий вход блока адаптации соединен с управляющим входом пакетизатора и является управляющим входом устройства, а сигнальный вход блока адаптации соединен с выходом блока преобразования и информационным входом блока управления передачей. Управляющий вход блока управления передачей соединен с выходом блока сравнения, а выход блока управления передачей соединен с сигнальным входом пакетизатора. М адресных выходов блока адаптации, где М=1, 2,..., соединены с соответствующими М адресными входами пакетизатора.

Благодаря новой совокупности существенных признаков за счет введения пакетизатора, блока адаптации и блока управления передачей и соответствующих новых связей возможно динамически оценивать параметры нагрузки от абонентов и в канале множественного доступа, а по результатом оценки адаптировать объем пакетизатора устройства, чем обеспечивается повышение пропускной способности канала множественного доступа.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявленное устройство поясняется чертежами:

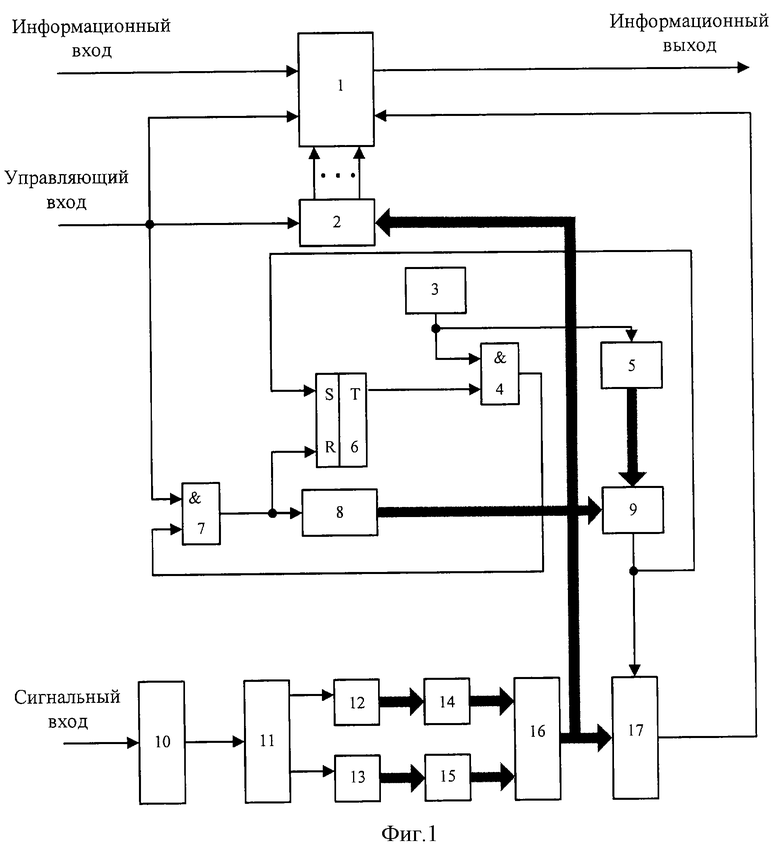

фиг. 1 - функциональная схема устройства управления передачей данных в канале множественного доступа;

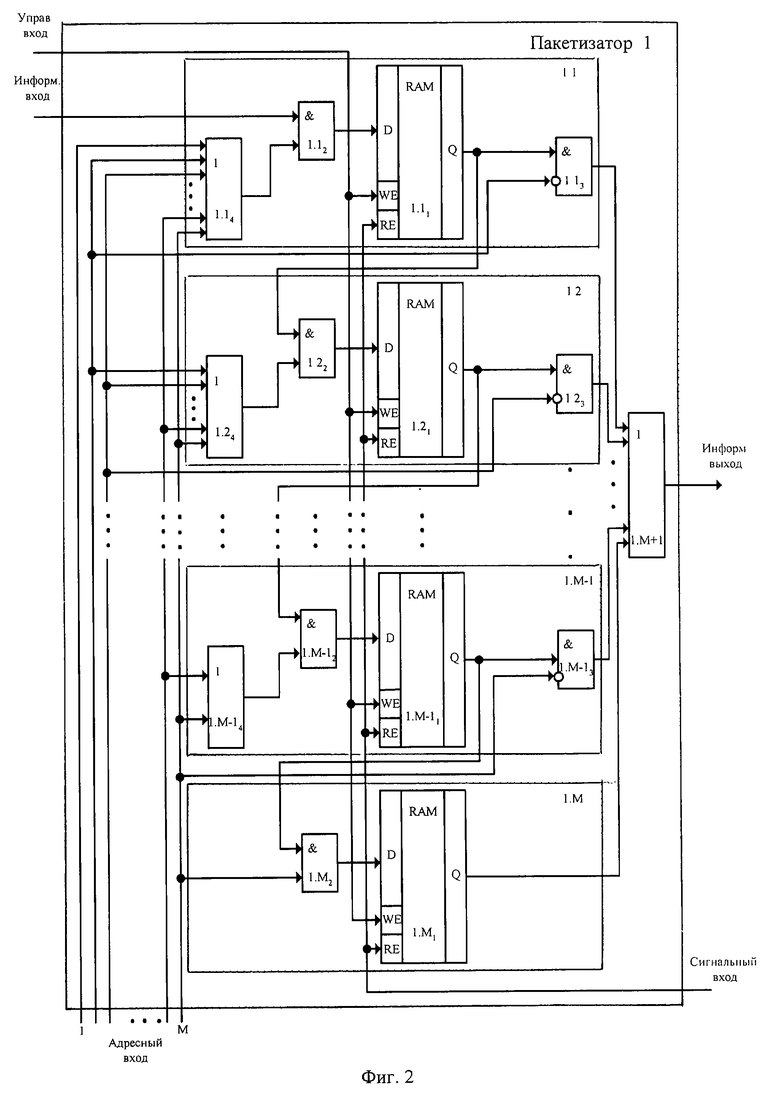

фиг.2 - схема пакетизатора;

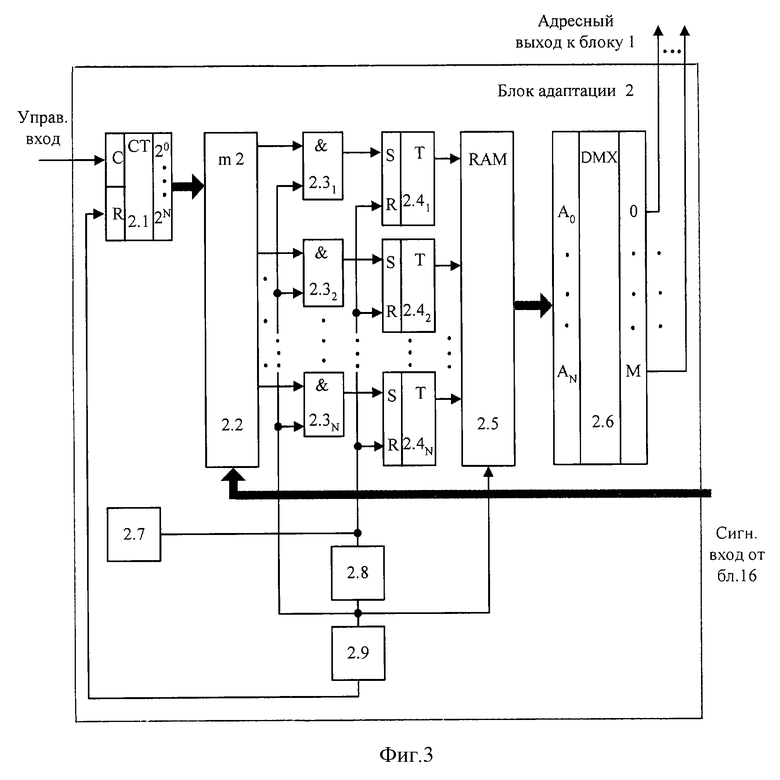

фиг.3 - схема блока адаптации;

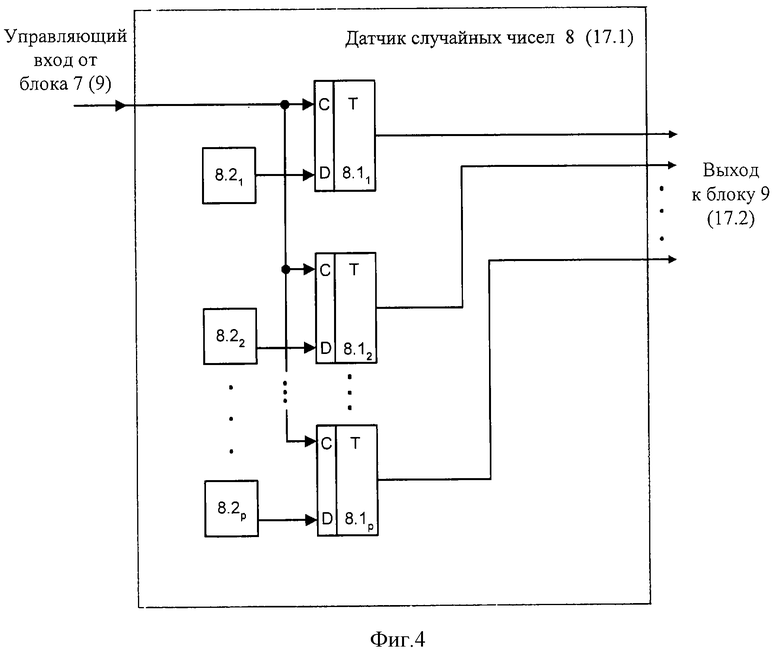

фиг.4 - схема датчика случайных чисел;

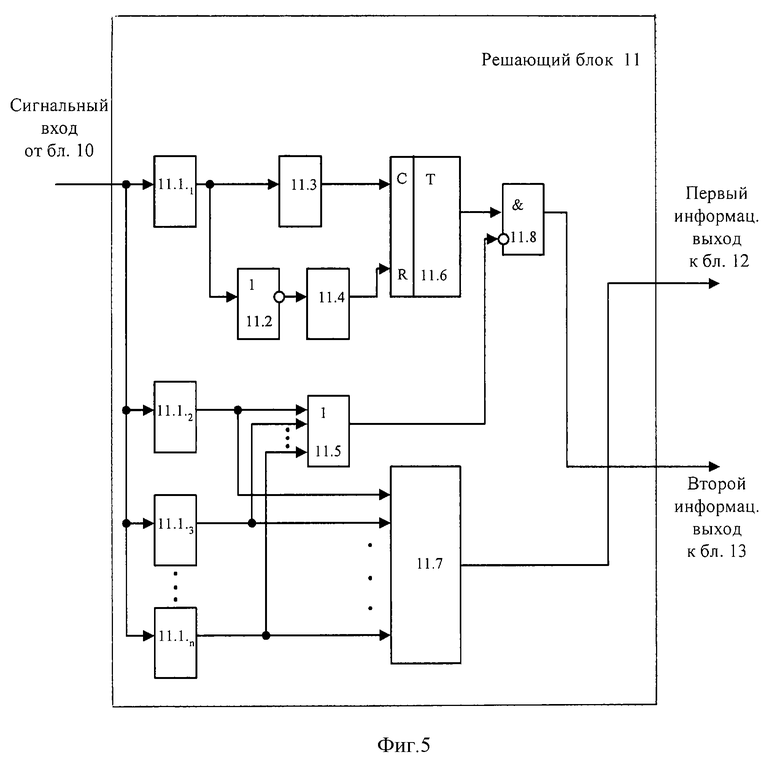

фиг.5 - схема решающего блока;

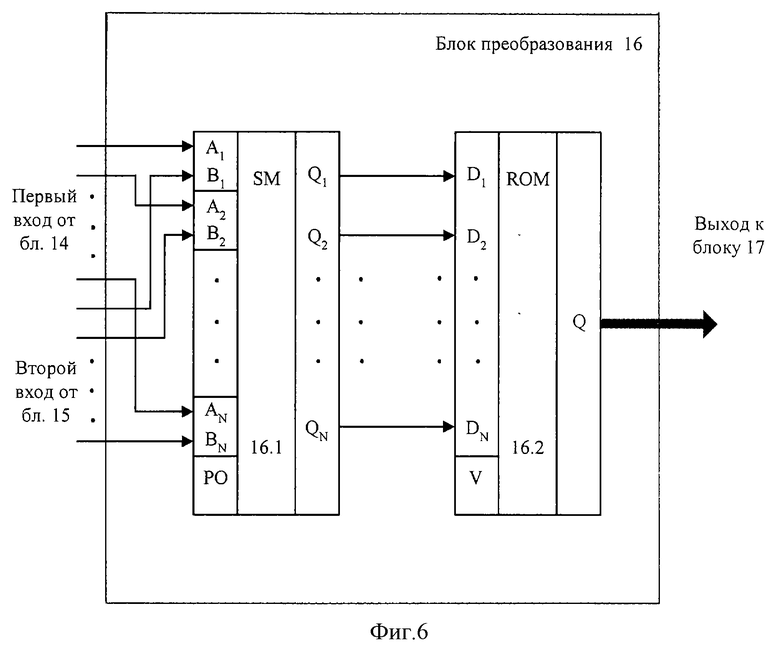

фиг.6 - схема блока преобразования;

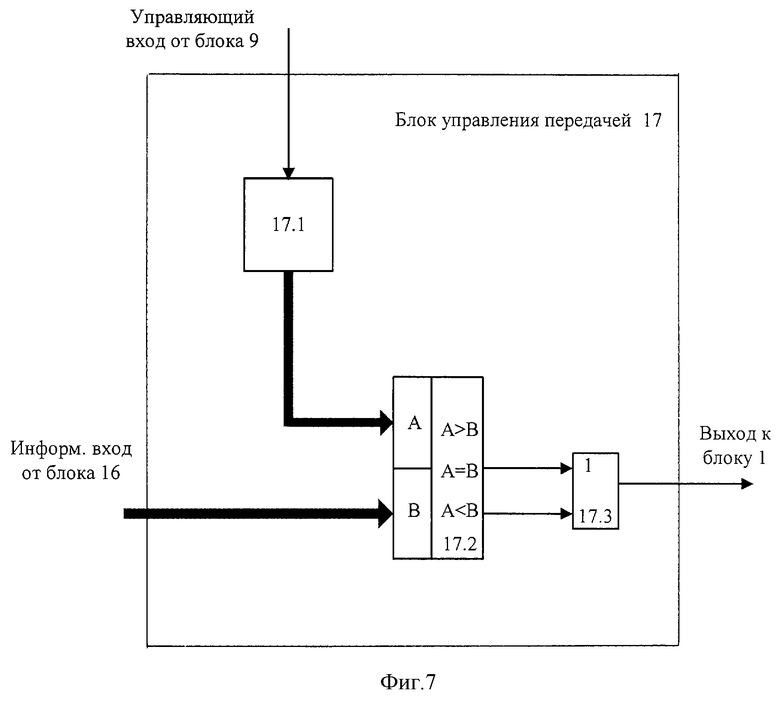

фиг.7 - схема блока управления передачей;

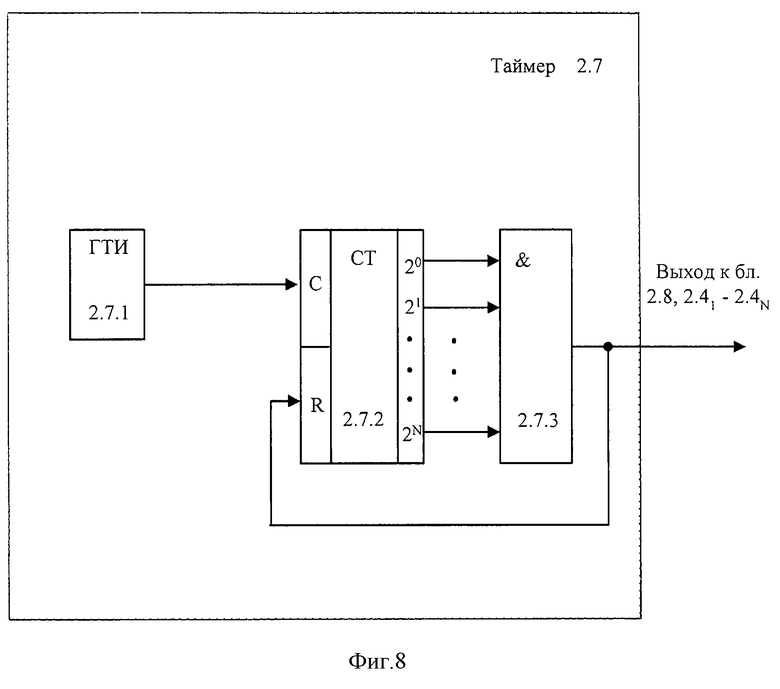

фиг.8 - схема таймера.

Заявляемое устройство управления передачей данных в канале множественного доступа, показанное на фиг.1, состоит из: пакетизатора 1, блока адаптации 2, синхронизатора 3, первого элемента И 4, счетчика 5, RS-триггера 6, второго элемента И 7, датчика случайных чисел 8, блока сравнения 9, коррелятора 10, решающего блока 11, счетчика необслуженной нагрузки 12, счетчика обслуженной нагрузки 13, первого фильтра Калмана 14, второго фильтра Калмана 15, блока преобразования 16, блока управления передачей 17. Причем, информационный вход пакетизатора 1 является информационным входом устройства, а выход пакетизатора является информационным выходом устройства. Управляющий вход блока адаптации 2 соединен с управляющим входом пакетизатора 1 и является управляющим входом устройства. Сигнальный вход блока адаптации 2 соединен с выходом блока преобразования 16 и информационным входом блока управления передачей 17, управляющий вход которого соединен с выходом блока сравнения 9 и единичным входом RS-триггера 6. Выход блока управления передачей 17 соединен с сигнальным входом пакетизатора 1. М адресных выходов блока адаптации, где М=1, 2,..., соединены с соответствующими М адресными входами пакетизатора. Выход синхронизатора 3 соединен с первым входом первого элемента И 4 и входом счетчика 5, а выход счетчика 5 соединен с первым входом блока сравнения 9. Выход RS-триггера 6 соединен с вторым входом первого элемента И 4, выход которого соединен с вторым входом второго элемента И 7, первый вход которого является управляющим входом устройства. Выход второго элемента И 7 соединен с нулевым входом RS-триггера 6 и управляющим входом датчика случайных чисел 8, выход которого соединен с вторым входом блока сравнения 9. Вход коррелятора 10 является сигнальным входом устройства, а выход соединен с сигнальным входом решающего блока 11. Первый и второй информационные выходы решающего блока 11 соединены с входами соответственно счетчика необслуженной нагрузки 12 и счетчика обслуженной нагрузки 13, а выходы счетчиков необслуженной нагрузки 12 и обслуженной нагрузки 13 соединены с входами соответственно первого фильтра Калмана 14 и второго фильтра Калмана 15. Выходы первого фильтра Калмана 14 и второго фильтра Калмана 15 соединены соответственно с первым и вторым входами блока преобразования 16.

Входящие в общую структурную схему элементы имеют следующее назначение.

Пакетизатор 1 предназначен для накопления определенного числа пакетов от абонента данного устройства и передачи их в едином пакете. Может быть реализован по схеме, показанной на фиг.2. Он состоит из оперативных запоминающих устройств (ОЗУ) l.l1, 1.21,..., l.M-l1, 1.M1, элементов И l.12, 1.22,..., l. M-12, l. M2, элементов НЕ-И 1.13, 1.23,..., 1.М-13, элементов ИЛИ 1.14, 1.24, ..., l.M-14, l.M+1. Причем, первый вход элемента И 1.12 является информационным входом блока, а выходы элементов И 1.12, 1.22,..., l.M-12, 1.М2 соединены соответственно с информационными входами D ОЗУ l.l1, 1.21,..., 1. М-11, l.M1. Выходы ОЗУ l.l1, 1.21,..., l.M-l1 соединены соответственно с первыми входами элементов НЕ-И 1.13, 1.23,..., 1.М-13 и первыми входами элементов И 1.22,..., l.M-l2, l.M2. Входы записи WE ОЗУ l.l1, 1.21,..., l.M-l1, 1. М1 являются управляющим входом блока, а входы считывания RE ОЗУ l.l1, 1.21, . . ., l.M-l1, 1.М1 соединены с сигнальным входом блока. М входов элемента ИЛИ 1.14 соединены соответственно с М адресными входами блока, а выход соединен со вторым входом элемента И l.l2. M-1 входов элемента ИЛИ 1.24 соединены соответственно с M-1 адресными входами блока, а выход соединен с вторым входом элемента И 1.22. Первый и второй входы элемента ИЛИ 1.М-14 соединены соответственно с M-1 и М адресными входами блока, а выход соединен с вторым входом элемента И l.M-l2. Второй вход элемента И l.M2 соединен с М-м адресным входом блока, а инверсные входы элементов НЕ-И 1.13, 1.23,..., 1. М-13 соединены соответственно с 2, 3,..., М адресными входами блока. Выходы элементов НЕ-И 1.13, 1.23, . . ., 1.М-13 и выход ОЗУ 1.М1 соединены соответственно с входами М-входового элемента ИЛИ 1.М+1, а его выход является информационным выходом блока.

Блок адаптации 2 предназначен для управления пакетизатором 1 в зависимости от соотношения интенсивности поступления пакетов от абонента данного устройства и суммарной интенсивности поступления пакетов от всех устройств в канал множественного доступа. Может быть реализован по схеме, показанной на фиг. 3. Он состоит из двоичного счетчика 2.1, сумматора "по модулю два" 2.2, N-элементов И 2.31 - 2.3N, N-RS-триггеров 2.41-2.4N, где N - разрядность кодовых комбинаций (например, N= 8), оперативного запоминающего устройства (ОЗУ) 2.5, демультиплексора 2.6, таймера 2.7, первого элемента задержки 2.8, второго элемента задержки 2.9. Причем, счетный вход двоичного счетчика 2.1 является управляющим входом устройства, а выход соединен с информационным входом сумматора "по модулю два" 2.2. Выходы сумматора "по модулю два" 2.2 соединены соответственно с первыми входами N элементов И 2.31-2.3N, выходы которых соединены соответственно с единичными входами N RS-триггеров 2.41-2.4N. Выходы N RS-триггеров 2.41-2.4N соединены соответственно с входами оперативного запоминающего устройства (ОЗУ) 2.5, выход которого соединен с входом демультиплексора 2.6. М выходов демультиплексора 2.6 образуют адресную шину выхода к пакетизатору 1, где М - максимальное количество функциональных ОЗУ, включаемых в пакетизаторе 1 (например, М=2...40). Сигнальный вход сумматора "по модулю два" является сигнальным входом блока. Выход таймера 2.7 соединен с входом первого элемента задержки 2.8 и с нулевыми входами N RS-триггеров 2.41-2.4N. Выход первого элемента задержки 2.8 соединен с входом записи ОЗУ 2.5 и с входом второго элемента задержки 2.9, а также и с вторыми входами N элементов И 2.31-2.3N. Выход второго элемента задержки 2.9 соединен с входом установки R двоичного счетчика 2.1.

Синхронизатор 3 предназначен для формирования синхроимпульсов и представляет собой генератор тактовых импульсов. Схема его известна и описана, например, в книге: Микросхемы и их применение: Справ. пособие. / 1984, - с. 213, рис. 7.6. Может быть реализован на интегральных микросхемах (ИМС) серий 511, 176.

Счетчик 5 предназначен для отсчета количества синхроимпульсов, счетчик 2.1, входящий в блок адаптации 2, предназначен для отсчета количества бит, счетчик 2.7.2, входящий в таймер 2.7, предназначен для отсчета количества тактовых импульсов за интервал анализа. Могут быть реализованы по схеме, описанной - Основы импульсной и цифровой техники. / Под общей ред. А.М. Сидорова, -СПВВИУС, 1995, рис.5.38, с.169-172.

Датчик случайных чисел 8 (17.1) предназначен для выдачи случайной кодовой комбинации по управляющему сигналу. Может быть реализован по схеме, показанной на фиг.4. Он состоит из р-D-триггеров 8.11- 8.1р (17.1.11-17.1.1р) и р-генераторов шума 8.21-8.2р (17.1.21-17.1.2р), где р - разрядность случайных кодовых комбинаций (например, р=8). Тактовые входы С всех D-триггеров соединены между собой и являются управляющим входом датчика случайных чисел. Информационные входы D D-тригтеров соединены с выходами соответствующих р генераторов шума 8.21-8.2р (17.1.21-17.1.2р). Выходы D-триггеров 8.11-8.1р (17.1.11-17.1.1р) образуют шину выхода датчика случайных чисел.

Блок сравнения 9 (17.2) предназначен для сравнения кодовых комбинаций. Схема его известна и описана, например, в книге: Лебедев И.О., Сидоров А.М. Импульсные цифровые устройства. - Л.: ВАС, 1980, - с.51-53, рис.2.33, 2.34. Может быть реализован на ИМС серий 133, 564.

Коррелятор 10 предназначен для согласованного приема широкополосных сигналов пользователей. Он представляет собой квазикогерентный приемник с поиском и синхронизацией по времени и по частоте. Схема его известна и описана, например, в книге: Варакин Л. Е. Системы связи с шумоподобными сигналами. -М. : Радио и связь, 1985, - с.315-323. Может быть реализован на ИМС серий 176, 155.

Решающий блок 11 предназначен для определения факта успешной передачи в канале или оценки кратности конфликта в противном случае. Одним из вариантов реализации решающего блока 11 может быть схема, показанная на фиг.5, при этом он состоит из n компараторов 11.11-11.1n, инвертора 11.2, первого и второго формирователей импульсов 11.3, 11.4 соответственно, RS-триггера 11.6, элемента НЕ-И 11.8, (n-1)-входового элемента ИЛИ 11.5, где n определяется максимальным количеством конфликтующих корреспондентов (например, n= 32), преобразователя параллельного кода в последовательный 11.7. Причем объединенные входы n компараторов 11.11-11.1n являются сигнальным входом решающего блока 11, выход первого компаратора 11.11 соединен с входом первого формирователя импульсов 11.3 и входом инвертора 11.2. Выход инвертора 11.2 соединен с входом второго формирователя импульсов 11.4, выход которого соединен с нулевым входом RS-тригтера 11.6. Выход первого формирователя импульсов 11.3 соединен с единичным входом RS-триггера 11.6, выход которого соединен с первым входом элемента И 11.8. Выход элемента И 11.8 является первым информационным выходом решающего блока 11. Выходы n-1 компараторов 11.12-1l. ln соединены с n-1 входами элемента ИЛИ 11.5 и n-1 входами преобразователя кодов 11.7 соответственно, выход преобразователя кодов 11.7 является вторым информационным выходом решающего блока 11, выход элемента ИЛИ 11.5 соединен с вторым инверсным входом элемента И 11.8.

Счетчики необслуженной нагрузки 12 и обслуженной нагрузки 13 предназначены для подсчета числа соответственно конфликтов и успешных передач. Идентичны, их схемы известны и описаны, например, в книге: Микросхемы и их применение: Справ. пособие. / В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. - М.: Радио и связь, 1984, - с.139, рис. 4.38. Могут быть реализованы на ИМС серий 133, 564.

Дискретные фильтры Калмана 14 и 15 предназначены для рекурсивного оценивания случайного процесса обслуживания заявок в устройстве, позволяющего получать несмещенные оценки с минимальными дисперсиями ошибок оценивания. Дискретные фильтры Калмана 14 и 15 представляют собой устройства рекурсивного оценивания нестационарного состояния системы, обеспечивающие оптимальность оценок в смысле минимума среднеквадратической ошибки. Схемы их известны и описаны, например, в книге: Теория оценивания и ее применение в связи и управлении / Э.Сейдж, Дж.Мелс. -М.: Связь, 1976, -с.252-264. Могут быть реализованы на ИМС серий 176.

Блок преобразования кодовых комбинаций 16 предназначен для выработки решения по оптимальной вероятности выхода на передачу на основе анализа соотношения интенсивностей обслуженного и необслуженного потоков пакетов в канале множественного доступа. Блок преобразования кодовых комбинаций 16 может быть реализован, например, по схеме, показанной на фиг.6, которая включает в себя сумматор 16.1 и постоянное запоминающее устройство (ПЗУ) 16.2, причем входы сумматора 16.1 являются входами блока. Выходы сумматора 16.1 являются входами ПЗУ 16.2. Выходы ПЗУ 16.2 являются выходами блока.

Блок управления передачей 17 предназначен для выдачи сигнала считывания на пакетизатор 1 с выбранной вероятностью. Может быть реализован по схеме, показанной на фиг. 7, при этом он состоит из датчика случайных чисел 17.1, блока сравнения 17.2 и элемента ИЛИ 17.3. Управляющий вход датчика случайных чисел 17.1 является управляющим входом блока, а выход соединен с входом А блока сравнения 17.2. Вход В блока сравнения 17.2 является информационным входом блока. Первый и второй выходы блока сравнения 17.2 соединены соответственно с первым и вторым входами элемента ИЛИ 17.3, выход которого является выходом блока.

Сумматор "по модулю два" 2.2, входящий в блок адаптации 2, предназначен для выработки кодовой комбинации, характеризующей соотношение интенсивностей поступления пакетов от абонента данного устройства и суммарной интенсивности поступления пакетов от всех устройств в канал множественного доступа. Может быть реализован по схеме, описанной: Шило В.Л. Популярные микросхемы ТТЛ. -М.: "Аргус", 1993, с.19-20, на ИМС серий 155, 555.

Оперативное запоминающее устройство (ОЗУ) 2.5, входящее в блок адаптации 2, предназначено для записи и считывания кодовой комбинации, характеризующей соотношение интенсивностей поступления пакетов от абонента данного устройства и суммарной интенсивности поступления пакетов от всех устройств в канал множественного доступа, за определенный временной интервал, и ОЗУ l.l1, 1.21, . . . . l.M-1, 1.M, входящие в пакетизатор, предназначены для записи и считывания пакетов от абонента данного устройства. Могут быть реализованы по схеме, описанной: Шило В.Л. Популярные микросхемы ТТЛ. - М.: "Аргус", 1993, с.53-54, на ИМС серий 155, 531.

Демультиплексор 2.6, входящий в блок адаптации 2, предназначен для формирования сигнала логической единицы на одном из выходов в соответствии с кодовой комбинацией на входе. Может быть реализован по схеме, описанной - Цифровые интегральные микросхемы: Справочник. / П.П.Мальцев, Н.С.Долидзе, М. И.Критенко и др. - М.: Радио и связь, 1994, с.32, на ИМС серий 555.

Таймер 2.7, входящий в состав блока адаптации 2, предназначен для отсчета длительности интервала анализа. Может быть реализован по схеме, описанной на фиг.8. При этом он состоит из генератора тактовых импульсов 2.7.1, счетчика 2.7.2 и элемента И 2.7.3. Выход генератора тактовых импульсов соединен со счетным входом двоичного счетчика 2.7.2, N выходов которого соединены соответственно с N входами элемента И 2.7.3. Выход элемента И 2.7.3 соединен с входом установки счетчика 2.7.2 и является выходом таймера 2.7.

Элементы задержки 2.8 и 2.9, входящие в блок адаптации 2, предназначены для задержки сигнала. Могут быть реализованы на базе регистра сдвига, известны и описаны - Цифровые интегральные микросхемы: Справочник. /П.П. Мальцев и др., - М.: Радио и связь, 1994, с.52.

Генераторы шума 8.21-8.2р (17.1.21-17.1.2р), входящие в датчик случайных чисел 8 (17.1), предназначены для формирования случайно изменяющихся во времени выходных напряжений. Схемы генераторов шума известны и описаны в книге - Элементы радиоэлектронных устройств. / Б.И. Коротков, - М.: Радио и связь, 1988, рис.7.24, с.107.

Компараторы 11.11-11.1n, входящие в решающий блок 11, предназначены для выработки управляющего сигнала логического уровня. Принципы построения и схема их реализации известны и описаны, например, в книге: Микросхемы и их применение: Справочное пособие / В.А.Батушев, В.Н.Мирошниченко, - М.: Радио и связь, 1983, - рис.2.33(6), с.82.

Формирователи импульсов 11.3 и 11.4, входящие в решающий блок 11, предназначены для формирования из логического уровня короткого импульса, идентичны, известны и описаны, например, в книге: Мальцева Л.А. и др. Основы цифровой техники. - М.: Радио и связь, 1986, - рис.21, с.30.

Преобразователь кодов 11.7, входящий в решающий блок 11, предназначен для преобразования параллельного кода кодовой комбинации в последовательный код. Может быть реализован по схеме, описанной в работе "Полупроводниковые цифровые микросхемы. Справочник", В.Л. Шило, Челябинск: Металлургия, 1989, рис. 2.52 а, с.246-250.

Сумматор 16.1 предназначен для суммирования кодовых комбинаций, поступающих от фильтров Калмана 14 и 15, и выдачи результата сложения на входы постоянного запоминающего устройства 16.2. Схема его известна и описана, например, в книге: Основы импульсной и цифровой техники / Под общей ред. А. М. Сидорова. - СПб.: СПВВИУС: 1995, -рис.5.5, с.137-139.

Постоянное запоминающее устройство 16.2 предназначено для выдачи варианта кодовой комбинации, соответствующей оптимальной вероятности выхода на передачу по кодовой комбинации - адресу, поступающей от сумматора 16.1. Схема его известна и описана, например, в книге: Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова. - СПб.: СПВВИУС, 1995, -рис. 6.10, с.197-199.

Генератор тактовых импульсов 2.7.1, входящий в блок таймера 2.7, предназначен для формирования тактовых импульсов. Схема его известна и описана, например, в книге: Микросхемы и их применение: Справ. пособие. / 1984, - с. 213, рис.7.6. Может быть реализован на интегральных микросхемах (ИМС) серий 511, 176.

Логические элементы И, входящие в блоки описываемого устройства, идентичны, известны и описаны, например, в книге: Мальцева Л.А., Фромберг Э.М. Основы цифровой техники - М.: Радио и связь, 1986. - с.30-31. Могут быть реализованы на ИМС серий 133 и 564.

Логические элементы ИЛИ, входящие в блоки описываемого устройства, идентичны, известны и описаны, например, в книге: Основы импульсной и цифровой техники / Под общей ред. А.М.Сидорова. - СПВВИУС, 1995, рис.2.4, с.39-41.

RS-триггеры, входящие в блоки описываемого устройства, известны и описаны, например, в книге: Батушев В.А., Вениаминов В.П., Ковалев В.Г. и др. Микросхемы и их применение: Справ. пособие. - М.: Радио и связь, 1984, с. 122, рис.4.16. Могут быть реализованы на ИМС серий 133, 564.

D-триггеры 8.11-8.lp (17.1.11-17.1.1р), входящие в датчик случайных чисел 8 (17.1), известны и описаны - Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, с.90-91.

Инвертор 11.2, входящий в решающий блок 11, предназначен для формирования выходного напряжения с логическим уровнем, противоположным логическому уровню входного напряжения. Схема его известна и описана, например, в книге: Справочная книга радиолюбителя-конструктора: В двух книгах под ред. Н.И.Чистякова, кн. 1, -М.: Радио и связь, 1993, - рис.1.47 в, с.30.

Функциональная схема устройства, реализующего выполнение описанных функций управления передачей данных по каналу множественного доступа, приведена на фиг.1.

Заявленное устройство работает следующим образом.

При включении питания (схема питания не приводится) триггер 6 устанавливается в режим хранения логической единицы. Синхронизатор 3 выдает импульсы с интервалом времени, равным длительности интервала передачи пакета, при этом импульсы поступают на первый вход первого элемента И 4 и на вход счетчика 5, вызывая последовательную смену кодовых комбинаций на выходе счетчика 5 (число кодовых комбинаций равно числу "окон" в цикле передачи).

При появлении в канале множественного доступа передаваемой информации принятый пакет поступает в устройство через сигнальный вход на вход коррелятора 10, на выходе которого выделяется отклик поступающего сигнала. Решающий блок 11 по данному отклику позволяет определить количество корреспондентов, одновременно работающих в канале множественного доступа.

Если величина отклика свидетельствует о конфликте двух и более корреспондентов, одновременно работающих в канале множественного доступа, то с первого информационного выхода решающего блока 11 информация о кратности конфликта (то есть о количестве конфликтующих корреспондентов) поступает на вход счетчика необслуженной нагрузки 12. Если в канале работает один корреспондент, то на единицу увеличивается содержимое счетчика обслуженной нагрузки 13.

По окончании интервала анализа количества обслуженных и необслуженных заявок с выходов блоков 12 и 13 значения количества пакетов, попавших в конфликт и успешно переданных, подаются на дискретные фильтры Калмана 14 и 15 соответственно. В них реализуется алгоритм оценивания наблюдаемых параметров в нормальных шумах канала связи для дискретного времени, определяемого длительностью цикла передачи. Этот алгоритм формирует линейную несмещенную оценку с минимальной дисперсией. Устройство и порядок функционирования дискретного фильтра Калмана представлены в работе "Оптимальное управление системами", Э.П. Сейдж, И.С. Уайт, стр. 216-223, М.: "Радио и связь", 1982 г.

На основе оценок обслуженной и необслуженной нагрузки в блоке преобразования 16 производится расчет вероятности своевременной доставки пакета и выбор оптимальной вероятности выхода на передачу в соответствии с методикой, представленной в работе "Сборник молодых ученых за 1996 год", г.Орел, ВИПС, а также в статье "Методика оценки частного показателя эффективности линий многоканальной радиосвязи", Е.Г.Белобров, А.Ю.Сафонов, стр.8-17. Для максимизации вероятности своевременной доставки пакета в канале множественного доступа используются методы динамического программирования Беллмана, заключающиеся в последовательном выполнении пошаговой оптимизации, где оптимальное управление определяется лишь состоянием канала множественного доступа и целью и не зависит от его состояния в предыдущие моменты времени. Устройство и принцип работы устройства дискретного динамического программирования на основе принципов Беллмана рассмотрено в работе "Оптимальное управление системами" Э.П.Сейдж, И.С.Уайт (стр.278-287).

При этом кодовая комбинация, соответствующая оптимальной вероятности выхода на передачу, поступает одновременно на информационный вход блока управления передачей 17 и на сигнальный вход блока адаптации 2. Периодически поступающие на управляющий вход блока адаптации 2 сигналы запроса передачи позволяют оценить интенсивность поступления пакетов от абонента, на сигнальный вход блока адаптации 2 от блока преобразования 16 поступает текущее значение оптимальной вероятности выхода на передачу. С адресного выхода блока адаптации 2 на адресный вход пакетизатора 1 поступает решение о включении требуемого количества элементов памяти при передаче информации абонента в канал множественного доступа.

При возникновении необходимости в передаче пакета на управляющий вход устройства поступает сигнал запроса передачи (в виде уровня логической единицы). Данный сигнал поступает на управляющие входы пакетизатора 1 и блока адаптации 2 (тем самым обеспечивается запись информации абонента в пакетизатор 1). При этом очередной сигнал с выхода синхронизатора 3 (в виде единичного импульса) через открытый первый элемент И 4 поступает на второй вход второго элемента И 7. Так как второй элемент И 7 открыт по первому входу сигналом запроса передачи, то единичный импульс с выхода второго элемента И 7 поступает на вход R триггера 6, переводя его в нулевое состояние, а также на управляющий вход датчика случайных чисел 8, который выдает в параллельном коде на второй вход блока сравнения 9 кодовую комбинацию, соответствующую номеру окна в цикле передачи, выбранного для передачи пакета. При этом триггер 6 закрывает первый элемент И 4.

В момент совпадения кодовых комбинаций на первом и втором входах блока сравнения 9 последний выдает сигнал в виде единичного импульса на управляющий вход блока управления передачей 17, а также переводит триггер 6 в единичный режим. При этом блок управления передачей 17 с выбранной вероятностью выдает сигнал с уровнем логической единицы на сигнальный вход пакетизатора 1 (по этому сигналу осуществляется считывание информации из пакетизатора 1 в канал множественного доступа).

Пакетизатор 1, функциональная схема которого показана на фиг.2, работает следующим образом. В процессе работы устройства блок адаптации 2 постоянно оценивает интенсивность поступления пакетов от абонента данного устройства и выдает информацию об этой интенсивности на один из М адресных входов пакетизатора 1. В соответствии с этим в каждый конкретный момент времени в пакетизаторе 1 к его входу и выходу подключено i ОЗУ 1.1. Запись информации в ОЗУ осуществляется при поступлении сигнала запроса передачи на управляющий вход пакетизатора 1. Считывание информации в канал множественного доступа осуществляется по сигналу с уровнем логической единицы, поступающему с выхода блока управления передачей 17 на сигнальный вход пакетизатора 1.

Блок адаптации 2, функциональная схема которого показана на фиг.3, работает следующим образом. Сигналы запроса передачи, имеющие уровень логической единицы, поступают на управляющий вход блока адаптации 2 и, соответственно, на счетный вход двоичного счетчика 2.1. Содержимое счетчика 2.1 характеризует интенсивность поступления пакетов от абонента в текущем интервале анализа. Отсчет длительности интервала анализа обеспечивает таймер 2.7. С выхода счетчика 2.1 кодовая комбинация, характеризующая интенсивность поступления пакетов от абонента, поступает на первый вход сумматора 2.2. На второй вход последнего от блока преобразования 16 поступает информация о потоковой ситуации в канале множественного доступа. В результате на выходах сумматора 2.2, изменяясь в течение интервала анализа, присутствует кодовая комбинация, характеризующая соотношение интенсивностей поступления пакетов от абонента данного устройства и суммарной интенсивности поступления пакетов от всех устройств в канал множественного доступа.

По окончании очередного интервала анализа таймер 2.7 выдает сигнал с уровнем логической единицы на входы R всех N триггеров 2.4 (при этом все они переводятся в режим хранения логического нуля) и на вход первого элемента задержки 2.8. Сигнал таймера, задержанный на время, достаточное для обнуления триггеров, с выхода первого элемента задержки 2.8 поступает на вторые входы всех N элементов И 2.3 и открывает их на время поступления сигнала. Одновременно этот же сигнал поступает на вход записи оперативного запоминающего устройства (ОЗУ) 2.5, обеспечивая запись кодовой комбинации с выходов сумматора 2.2 в ОЗУ 2.5. Далее сигнал, задержанный во втором элементе задержки 2.9 на время, достаточное для записи кодовой комбинации в ОЗУ 2.5, поступает на вход R счетчика 2.1 и переводит его в исходное (нулевое) состояние для набора статистики в следующем интервале анализа.

Кодовая комбинация с выхода ОЗУ 2.5 поступает на вход демультиплексора 2.6, вызывая появление сигнала с уровнем логической единицы на одном из его выходов, который поступает далее на соответствующий вход пакетизатора 1.

Датчик случайных чисел 8 (17.1), функциональная схема которого приведена на фиг. 4, работает следующим образом. На D входах каждого из D-триггеров 8.11-8. lp (17.1.11-17.1.1р) имеют место случайно изменяющиеся во времени выходные напряжения независимых генераторов шума 8.21-8.2р (17.1.21-17.1.2р). Если в момент появления импульса на С входе i-гo триггера 8.11-8.1p (17.1.11-17.1.1р) выходное напряжение i-гo генератора шума 8.21-8.2р (17.1.21-17.1.2р) ниже порога срабатывания триггера, то на выходе триггера будет иметь место уровень логического нуля (в противном случае - уровень логической единицы). Случайная кодовая комбинация с выходов триггеров 8.11-8.1p (17.1.11-17.1.1р) поступает на вход блока сравнения кодовых комбинаций 9 (17.2).

Решающий блок 11, показанный на фиг.5, работает следующим образом. Информация из канала множественного доступа с выхода коррелятора 10 поступает на вход решающего блока 11. Здесь отклик коррелятора поступает на входы компараторов 11.11-11.1n. Если величина отклика превышает порог срабатывания компаратора 11.11, но не превышает порога срабатывания компаратора 11.12 (то есть в канале множественного доступа работает только один корреспондент), то сигнал с уровнем логической единицы с выхода компаратора 11.11 при посредстве формирователей импульсов 11.3 и 11.4 и инвертора 11.2 переводит триггер 11.6 в режим хранения логической единицы. При этом наличие на управляющем инверсном входе элемента И 11.8 уровня логического нуля приводит к появлению на выходе элемента И 11.8 сигнала с уровнем логической единицы, который поступает на второй информационный выход решающего блока 11 (и далее на вход счетчика обслуженной нагрузки 13). Если в канале множественного доступа произошел конфликт, то величина отклика коррелятора будет пропорциональна числу конфликтующих корреспондентов. Поэтому на выходах k первых компараторов из общего числа n появляются сигналы с уровнем логической единицы, которые поступают на соответствующие входы преобразователя кодов 11.7. Преобразователь кодов 11.7 с первого информационного выхода решающего блока 11 в последовательном коде передает кодовую комбинацию, соответствующую числу конфликтующих корреспондентов, на вход счетчика необслуженной нагрузки 12.

Блок преобразования 16, функциональная схема которого приведена на фиг. 6, работает следующим образом. Кодовые комбинации, характеризующие интенсивность потоков обслуженной и необслуженной нагрузки, поступающие на первый и второй сигнальные входы блока преобразования с выходов фильтров Калмана 14 и 15 соответственно, суммируются в сумматоре 16.1. Кодовая комбинация - результат сложения с выходов сумматора 16.1 поступает на входы ПЗУ 16.2, в котором хранятся варианты решения на изменение вероятности выхода на передачу. Очередное решение в виде кодовой комбинации с выходов ПЗУ 16.2 поступает на выход блока преобразования 16.

Блок управления передачей 17, функциональная схема которого приведена на фиг.7, работает следующим образом. Информация о выбранной устройством вероятности выхода на передачу, поступающая на информационный вход блока управления передачей 17 с выхода блока преобразования 16, поступает на вход В блока сравнения 17.2. При этом на вход А блока сравнения 17.2 поступает случайная кодовая комбинация с выхода датчика случайных чисел 17.1, вырабатываемая по сигналу с выхода блока сравнения 9, поступающему на управляющий вход блока управления передачей 17. В результате сравнения кодовых комбинаций блок сравнения 17.2 с заданной вероятностью выдает сигнал с уровнем логической единицы на выход блока управления передачей 17.

Таймер 2.7, показанный на фиг.8, работает следующим образом. Генератор тактовых импульсов 2.7.1 вырабатывает тактовые импульсы, которые поступают на счетный вход счетчика 2.7.2. При появлении на всех N выходах счетчика 2.7.2 сигналов с уровнем логической единицы на выходе N-входового элемента И формируется сигнал с уровнем логической единицы, который поступает на выход блока и одновременно на вход установки R счетчика 2.7.2, переводя его в исходное (нулевое) состояние для начала отсчета следующего интервала анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2148294C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2001 |

|

RU2211540C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168870C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| УСТРОЙСТВО ПОДКЛЮЧЕНИЯ ИСТОЧНИКОВ ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 2001 |

|

RU2194301C2 |

Изобретение относится к вычислительной технике и может использоваться в узлах коммутации пакетов (сообщений) сети связи. Целью изобретения является разработка устройства управления передачей данных в канале множественного доступа, обеспечивающего более высокую пропускную способность за счет группирования потока пакетов от абонентов, адаптацию объема пакетизатора с учетом интенсивности и характера группирования потока пакетов от абонентов и потоковой обстановки в канале множественного доступа. Устройство управления передачей данных в канале множественного доступа состоит из пакетизатора блока адаптации, синхронизатора первого элемента, счетчика RS-триггера, второго элемента, датчика случайных чисел блока сравнения, коррелятора, решающего блока, счетчика необслуженной нагрузки, счетчика обслуженной нагрузки, первого фильтра Калмана, второго фильтра Калмана, блока преобразования, блока управления передачей. 8 ил.

Устройство управления передачей данных в канале множественного доступа, содержащее синхронизатор, выход которого соединен с первым входом первого элемента И и входом счетчика, выход которого соединен с первым входом блока сравнения, выход которого соединен с единичным входом RS-триггера, выход которого соединен с вторым входом первого элемента И, выход которого соединен с вторым входом второго элемента И, первый вход которого является управляющим входом устройства, выход второго элемента И соединен с нулевым входом RS-триггера и управляющим входом датчика случайных чисел, выход которого соединен с вторым входом блока сравнения, коррелятор, вход которого является сигнальным входом устройства, а выход соединен с сигнальным входом решающего блока, первый и второй информационные выходы которого соединены с входами соответственно счетчика необслуженной нагрузки и счетчика обслуженной нагрузки, а выходы счетчиков необслуженной и обслуженной нагрузки соединены с входами соответственно первого и второго фильтров Калмана, выходы первого и второго фильтров Калмана соединены соответственно с первым и вторым входами блока преобразования, отличающееся тем, что дополнительно введены пакетизатор, информационный вход которого является информационным входом устройства, а выход пакетизатора является информационным выходом устройства, блок адаптации, управляющий вход которого соединен с управляющим входом пакетизатора и является управляющим входом устройства, сигнальный вход блока адаптации соединен с выходом блока преобразования и информационным входом блока управления передачей, управляющий вход которого соединен с выходом блока сравнения, а выход блока управления передачей соединен с сигнальным входом пакетизатора, М адресных выходов блока адаптации, где М= 1, 2, . . . , соединены с соответствующими М адресными входами пакетизатора.

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| RU 2055394 C1, 27.02.1996 | |||

| US 5592518 A, 07.01.1997 | |||

| US 5574753 A, 12.11.1996. | |||

Авторы

Даты

2003-11-20—Публикация

2002-04-25—Подача