Изобретение относится к вычислительной технике и может найти применения при разработке автоматизированных систем управления различными процессами и большими системами, а также при оценке качества алгоритмического обеспечения.

Известно устройство для выбора оптимальных решений, содержащее блок элементов памяти показателей размерностью m•n, блок из n элементов выбора минимума, первый блок из п и второй из m элементов выбора максимума, первый и второй блоки ключей по n коммутирующих элементов, первый и второй блоки вычитателей по m•n элементов и блок из m индикаторов (авторское свидетельство CCСР 1774354, кл. G 06 F 15/419, 1990).

Недостатками этого устройства являются затруднительное получение информации для матрицы значений априорных вероятностей исходов в случае неопределенности, а также невозможность охарактеризовать качество алгоритмического обеспечения по показателю эффективности.

Наиболее близким аналогом (прототипом) является устройство для выбора рациональных решений, содержащее блок элементов памяти решений в виде матрицы размерностью m•n, блок элементов памяти ситуации, блок элементов памяти опроса, элемент памяти, сумматор с накоплением, делитель, блок компараторов в виде матрицы размерностью m•n, блок умножителей, блок элементов ИЛИ, блок сумматоров с накоплением, распределитель импульсов, генератор тактовых импульсов и блок индикаторов (патент РФ 2158955, кл. G 06 F 15/173, 2000).

Это устройство позволяет устранить затруднения в случае неопределенности исходной информации, но оно имеет следующие недостатки:

- не позволяет характеризовать качество алгоритмического обеспечения по показателю эффективности;

- не дает возможность оценить квалификацию лиц, принимающих решение (ЛПР).

Техническим результатом заявленного изобретения является расширение функциональных возможностей за счет устранения указанных недостатков. Это можно осуществить следующим образом. Показатель эффективности алгоритмического обеспечения W можно оценить по следующей формуле:

W=Pпр•Pсв.пр, (1)

где Рпр - вероятность правильного принятия решения;

Рсв.пр - вероятность своевременного и правильного принятия решения.

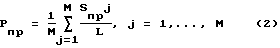

где М - число рассматриваемых ситуаций;

L - количество ЛПР, участвующих в работе для j-й ситуации;

Sпрj - число правильно принятых решений для j-й ситуации.

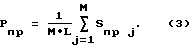

Для удобства аппаратурной реализации формулу (2) целесообразно переписать в следующем виде:

Величина Sпрj определяется путем подсчета в столбце матрицы итогов работы чисел, отличных от нуля. Эта матрица размерностью LxM включает в себя исходную информацию, представляющую времена, затрачиваемые различными ЛПР в процессе работы по поиску рациональных вариантов решений. В случае неправильного решения в соответствующую ячейку матрицы засылается нуль.

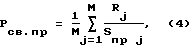

где Rj - число своевременно правильно принятых для j-й ситуации решений.

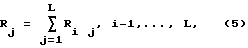

где

где tij - текущее значение времени, затраченное на принятие решения i-м ЛПР в j-й ситуации;

tдоп - допустимое время на принятие решения.

Технический результат достигается тем, что устройство для оценки эффективности алгоритмического обеспечения, содержащее блок элементов памяти решений, выполненный в виде матрицы, блок элементов памяти ситуаций, блок элементов памяти опроса, первый блок компараторов, выполненный в виде матрицы, блок умножителей, блок элементов ИЛИ первый блок сумматоров с накоплением, первый элемент памяти, первый сумматор с накоплением, первый делитель, блок индикаторов, генератор тактовых импульсов и первый распределитель импульсов, вход которого соединен с выходом генератора тактовых импульсов, первый выход распределителя импульсов - с входами записи первого элемента памяти, а также с входами записи всех элементов памяти блока элементов памяти решений, блока элементов памяти ситуаций и блока элементов памяти опроса, второй выход распределителя импульсов соединен с входами считывания элементов блока элементов памяти опроса, третий выход - с входом считывания первого элемента памяти, с четвертого по четвертый +m выходы - с входами считывания с первого по m-й элементов блока элементов памяти решений и блока элементов памяти ситуаций, пятый +m выход - с входами считывания сумматоров первого блока сумматоров с накоплением, выходы которых подключены к входам индикаторов блока индикаторов, а информационные входы - к выходам элементов блока элементов ИЛИ, первые входы которых соединены с выходами умножителей блока умножителей, а со второго по m-й входы - с выходами компараторов первого блока компараторов, начиная со второй строки, а выходы первой строки первого блока компараторов подключены к первым входам умножителей блока умножителей, вторые входы которых соединены с выходом первого делителя, первый вход которого подключен к выходу первого сумматора с накоплением, с первого по L-й входы которого соединены с соответствующими выходами элементов памяти блока элементов памяти опроса, информационные входы которых являются входами первой группы входов устройства, информационные входы элементов памяти блока элементов памяти ситуаций являются входами второй группы входов устройства, а выходы каждого из элементов блока памяти ситуаций подключены к первым входам компараторов соответствующей строки первого блока компараторов, вторые входы которых соединены с соответствующими выходами элементов памяти блока элементов памяти решений, информационные входы которых являются третьей группой входов устройства, информационный вход первого элемента памяти является первым входом устройства, дополнительно содержит коммутатор, блок элементов памяти итогов работы, выполненный в виде матрицы, второй и третий элементы памяти, второй и третий блоки компараторов, выполненные в виде матриц, второй и третий блоки сумматоров с накоплением, блок делителей, второй и третий сумматоры с накоплением, второй, третий и четвертый делители, умножитель, блок индикации и второй распределитель импульсов, вход которого соединен с выходом генератора тактовых импульсов, шестой выход второго распределителя импульсов - с управляющим входом коммутатора, а седьмой выход - с входом считывания третьего элемента памяти, информационный вход которого является вторым входом устройства, а выход подключен к первым входам третьего и четвертого делителей, вторые входы которых соединены с выходами соответственно второго делителя и третьего сумматора с накоплением, с первого по М-й входы которого подключены к выходам соответствующих делителей блока делителей, первые входы которых соединены с выходами соответствующих сумматоров второго блока сумматоров с накоплением, а вторые входы - с выходами соответствующих сумматоров третьего блока сумматоров с накоплением, с первого по L-й входы каждого из которых подключены к выходам с первого по L-й компараторов соответствующего столбца второго блока компараторов, первые входы каждого из которых соединены с выходом второго элемента памяти, информационный вход которого является третьим входом устройства, информационные входы каждого элемента блока элементов памяти итогов работы являются входами четвертой группы входов устройства, выходы каждого из этих элементов памяти подключены ко вторым входам каждого компаратора второго блока компараторов, а также к входам каждого компаратора третьего блока компараторов, выходы каждого компаратора соответствующего столбца которого соединены с первым по L-й входы соответствующего сумматора второго блока сумматоров с накоплением, выходы каждого из которых подключены к соответствующим М входам второго сумматора с накоплением, выход которого соединен с первым входом второго делителя, второй вход которого подключен к первому выходу коммутатора, второй выход которого соединен со вторым входом первого делителя, а информационный вход коммутатора - с выходом первого элемента памяти, выход третьего делителя подключен к первому входу умножителя, второй вход которого соединен с выходом четвертого делителя, а выход умножителя - с входом блока индикации.

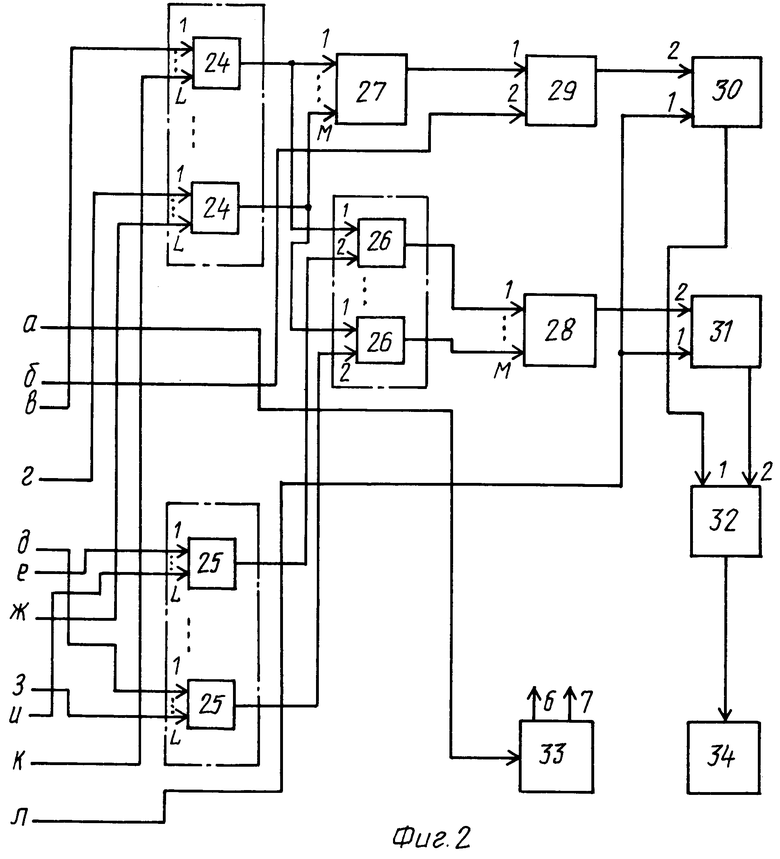

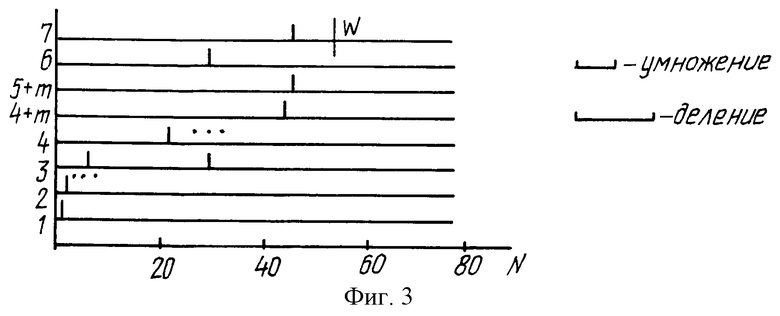

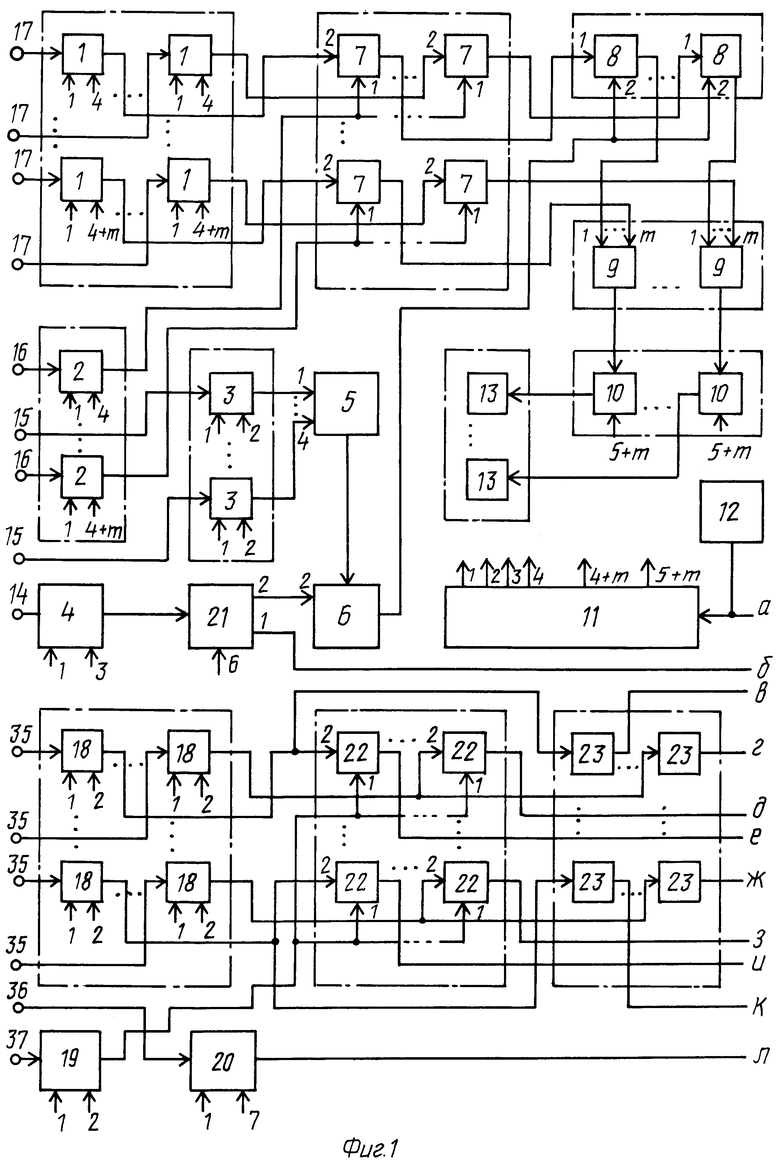

Нa фиг. 1 и 2 представлена функциональная схема устройства (для ликвидации громоздкости связи между распределителями импульсов и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг.3 изображена циклограмма работы устройства для оценки эффективности алгоритмического обеспечения (по оси ординат обозначены номера выходов распределителей импульсов, а по оси абсцисс - число тактов, причем длительность операции сложения принята за один такт, а длительности остальных вычислительных операций приведены справа).

Устройство для оценки эффективности алгоритмического обеспечения (фиг.1 и 2) содержит блок элементов памяти решений 1 в виде матрицы размерностью m•n, где m - количество аргументов в виде лингвистических переменных, а n - число вариантов решений, блок элементов памяти ситуации 2 из m элементов, блок элементов памяти опроса 3 из L элементов, первый элемент памяти 4, первый сумматор с накоплением 5, первый делитель 6, первый блок компараторов 7 в виде матрицы размерностью m•n, блок умножителей 8 из n элементов, блок элементов ИЛИ 9 из n элементов, первый блок сумматоров с накоплением 10 из n элементов, первый распределитель импульсов 11, генератор тактовых импульсов 12, блок индикаторов 13 из n элементов, первый вход 14 устройства, первую 15, вторую 16 и третью 17 группы входов устройства, блок элементов памяти итогов работы 18 в виде матрицы размерностью L•M, второй 19 и третий 20 элементы памяти, коммутатор 21, второй 22 и третий 23 блоки компараторов в виде матриц размерностью L•M, второй 24 и третий 25 блоки сумматоров с накоплением из М элементов каждый, блок делителей 26 из М элементов, второй 27 и третий 28 сумматоры с накоплением, второй 29, третий 30 и четвертый 31 делители, умножитель 32, второй распределитель импульсов 33, блок индикации 34, четвертую группу входов 35 устройства, второй 36 и третий 37 входы устройства.

Устройство для оценки эффективности алгоритмического обеспечения работает следующим образом. С третьей группы входов 17 аргументы в виде лингвистических переменных для различных вариантов решений подаются на информационные входы элементов памяти блока элементов памяти решений 1 (фиг.1). Со второй группы входов 16 устройства аргументы в виде лингвистических переменных для текущей ситуации поступают на информационные входы элементов памяти блока элементов памяти ситуаций 2. С первой группы входов 15 устройства подаются весовые коэффициенты Кi важности базового аргумента по результатам опроса ЛПР на информационные входы элементов блока элементов памяти опроса 3. С первого входа 14 устройства количество ЛПР L поступает на информационный вход первого элемента памяти 4. С четвертой группы входов 35 устройства значения времен tij подаются на информационные входы элементов памяти блока элементов памяти итогов работы 18 (если решение каким-либо ЛПР было принято неправильно, то в соответствующий элемент засылается нулевое значение tij). Со второго входа 36 устройства количество ситуаций М засылается на информационный вход третьего элемента памяти 20. С третьего входа 37 устройства допустимое время tдоп на принятие решения направляется на информационный вход второго элемента памяти 19. При этом управляющие сигналы на входы записи всех указанных элементов поступают с первого выхода первого распределителя импульсов 11. Темп работы устройства задается генератором тактовых импульсов 12.

По управляющему сигналу со второго выхода первого распределителя импульсов 11 на входы считывания элементов памяти блока элементов опроса 3 с выходов этих элементов сигналы, соответствующие величинам Кi (весовым коэффициентом базового аргумента, по мнению i-го ЛПР), подаются на входы первого сумматора с накоплением 5 (Ki≥1). По этому же сигналу со второго выхода первого распределителя импульсов 11 на входы считывания элементов памяти блока элементов памяти итогов работы 18 с выходов этих элементов значения времен tij поступают на вторые входы соответствующих компараторов второго блока компараторов 22 и на входы соответствующих компараторов третьего блока компараторов 23. Кроме того, по управляющему сигналу со второго выхода первого распределителя импульсов 11 на вход считывания второго элемента памяти 19 с выхода блока 19 величины допустимого времени на принятие решений tдоп подается на первые входы каждого компаратора второго блока компараторов 22.

С выхода первого сумматора с накоплением 5 сумма величин Кi поступает на первый вход первого делителя 6, на второй вход которого по управляющему сигналу с третьего выхода первого распределителя импульсов 11 на вход считывания первого элемента памяти 4 с выхода блока 4 через коммутатор 21 подается величина L. В данном случае сигнал на управляющий вход блока 21 не подается. С выхода первого делителя 6 величина весового коэффициента К, который является осреднением всех Кi, поступает на вторые входы умножителей блока умножителей 8.

По сигналам с четвертого по четвертый +m выходов первого распределителя импульсов 11 на соответствующие входы считывания с выходов элементов памяти блока элементов памяти решений 1 и блока элементов памяти ситуации 2 коды, соответствующие аргументам решений и ситуации подаются на входы компараторов первого блока компараторов 7. Эти компараторы настроены следующим образом. При совпадении кодов аргументов решений и ситуации на выходе компаратора будет "1". В случае различия кодов на выходе компаратора будет "0".

С выходов компараторов первой горизонтали блока 7 сигналы поступают на первые входы умножителей 8, где производится умножение этих сигналов на весовой коэффициент К учитывающий важность первого аргумента. С выходов остальных горизонталей первого блока компараторов 7 и умножителей блока 8 сигналы через блок 9 элементов ИЛИ подаются на информационные входы сумматоров с накоплением блока 10.

После окончания подсчета по сигналу с пятого +m выхода первого распределителя импульсов 11 на входы считывания сумматоров с накоплением блока 10 с их выходов число совпадений аргументов каждого из n вариантов решений и текущей ситуации поступает на входы блока индикаторов 13. Следует отметить, что за счет наличия весового коэффициента в случае совпадения первого аргумента будет суммироваться не "1", а величина, в К раз большая. Сравнивая показания индикаторов, можно выбрать рациональный вариант решения, который будет соответствовать наибольшему числу совпадений аргументов варианта решения и текущей ситуации.

Каждый компаратор второго блока компараторов 22 настроен в соответствии с формулой (6). С выходов первого столбца блока 22 сигналы, соответствующие значениям Ri1 подается на входы первого сумматора третьего блока 25 сумматоров с накоплением (фиг.1 и 2). Аналогичным образом направляются сигналы с выходов последующих столбцов блока 22. С выхода каждого из М сумматоров блока 25 величины Rj, вычисленные по формуле (5), засылаются на вторые входы каждого из М делителей блока 26 делителей.

Каждый компаратор третьего блока компараторов 23 настроен следующим образом: если входной сигнал больше нуля, то на выходе компаратора будет единица, в противном случае (при равенстве нулю) на выходе компаратора - нуль. В каждом из компараторов блока 23 заранее "прошит" сигнал низкого уровня, соответствующий нулю. Сигналы с каждого из М столбцов подаются на соответствующие сумматоры второго блока сумматоров 24, с выходов которых величины Sпрj поступают на входы второго сумматора с накоплением 27, а также на первые входы соответствующих делителей блока делителей 26, с выходов которых М значений Rj/Sпpj подаются на входы третьего сумматора с накоплением 28.

С выхода второго сумматора с накоплением 27 величина  засылается на первый вход второго делителя 29, на второй вход которого с выхода первого элемента памяти 4 через коммутатор 21 подается значение L. При этом управляющие сигналы на вход считывания блока 4 и управляющий вход коммутатора 21 направляются соответственно с третьего выхода первого распределителя импульсов 11 и с шестого выхода второго распределителя импульсов 33. С выхода блока 29 величина

засылается на первый вход второго делителя 29, на второй вход которого с выхода первого элемента памяти 4 через коммутатор 21 подается значение L. При этом управляющие сигналы на вход считывания блока 4 и управляющий вход коммутатора 21 направляются соответственно с третьего выхода первого распределителя импульсов 11 и с шестого выхода второго распределителя импульсов 33. С выхода блока 29 величина  направляется на второй вход третьего делителя 30, на первый вход которого с выхода третьего элемента памяти 20 по сигналу с седьмого выхода второго распределителя импульсов 33 на вход считывания блока 20 подается значение М. Это же значение засылается также на первый вход четвертого делителя 31.

направляется на второй вход третьего делителя 30, на первый вход которого с выхода третьего элемента памяти 20 по сигналу с седьмого выхода второго распределителя импульсов 33 на вход считывания блока 20 подается значение М. Это же значение засылается также на первый вход четвертого делителя 31.

С выходов каждого делителя блока 26 делителей величины Rj/Sпpj направляются на соответствующие М входов третьего сумматора с накоплением 28, с выхода которого значение  подается на второй вход четвертого делителя 31. С выходов третьего 30 и четвертого 31 делителей значения Рпр и Pсв.пр, определенные по формулам (3) и (4), поступают соответственно на первый и второй входы умножителя 32. С выхода блока 32 величина показателя эффективности алгоритмического обеспечения W, вычисляемая по формуле (1), подается на вход блока индикации.

подается на второй вход четвертого делителя 31. С выходов третьего 30 и четвертого 31 делителей значения Рпр и Pсв.пр, определенные по формулам (3) и (4), поступают соответственно на первый и второй входы умножителя 32. С выхода блока 32 величина показателя эффективности алгоритмического обеспечения W, вычисляемая по формуле (1), подается на вход блока индикации.

Таким образом, описанное устройство расширяет функциональные возможности, что проявляется в следующем:

- устройство позволяет охарактеризовать качество алгоритмического обеспечения по показателю эффективности;

- появляется возможность оценить квалификацию лиц, принимающих решение;

- на основе полученных результатов можно сформулировать пути повышения достоверности решений, воплощений которых на практике будет способствовать повышению качества алгоритмического обеспечения,

- можно наметить пути совершенствования уровня подготовки ЛПР.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в различных областях (отраслях) в процессе выбора рациональных решений и оценки эффективности алгоритмического обеспечения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОЦЕНКИ ЭФФЕКТИВНОСТИ УПРАВЛЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2517409C2 |

| СПОСОБ ОЦЕНКИ ЭФФЕКТИВНОСТИ УПРАВЛЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326442C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА РАЦИОНАЛЬНЫХ РЕШЕНИЙ | 2000 |

|

RU2158955C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА РАЦИОНАЛЬНОГО ВАРИАНТА | 2001 |

|

RU2202822C1 |

| СПОСОБ ОЦЕНКИ ИНФОРМАЦИИ ОБ ЭФФЕКТИВНОСТИ ФУНКЦИОНИРОВАНИЯ СИСТЕМЫ И УСТРОЙСТВО НА ЕГО ОСНОВЕ ДЛЯ РЕШЕНИЯ ЗАДАЧ УПРАВЛЕНИЯ, КОНТРОЛЯ И ДИАГНОСТИКИ | 2016 |

|

RU2622858C1 |

| СПОСОБ ОЦЕНКИ ИНФОРМАЦИИ О СИСТЕМЕ С НАСТРОЙКОЙ НА ОСНОВЕ АДАПТИВНОЙ МОДЕЛИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2628474C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ | 2001 |

|

RU2178201C1 |

| УСТРОЙСТВО КОНТРОЛЯ ЭНЕРГИИ, ПЕРЕДАВАЕМОЙ ПО ВОЛОКОННО-ОПТИЧЕСКИМ ЛИНИЯМ СВЯЗИ (ВАРИАНТЫ) | 1999 |

|

RU2152133C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

Изобретение относится к области вычислительной техники и может быть использовано в автоматизированных системах управления. Техническим результатом является расширение класса решаемых задач. Устройство содержит блок элементов памяти решений, блок элементов памяти ситуаций, блок элементов памяти опроса, блоки компараторов, блок умножителей, блок элементов ИЛИ, блоки сумматоров с накоплением, элементы памяти, сумматоры с накоплением, делители, генератор тактовых импульсов, распределители импульсов, коммутатор, блок элементов памяти итогов работы, блок делителей, умножитель, блок индикаторов и блок индикации. 3 ил.

Устройство для оценки эффективности алгоритмического обеспечения, содержащее блок элементов памяти решений, выполненный в виде матрицы, блок элементов памяти ситуаций, блок элементов памяти опроса, первый блок компараторов, выполненный в виде матрицы, блок умножителей, блок элементов ИЛИ, первый блок сумматоров с накоплением, первый элемент памяти, первый сумматор с накоплением, первый делитель, блок индикаторов, генератор тактовых импульсов и первый распределитель импульсов, вход которого соединен с выходом генератора тактовых импульсов, первый выход распределителя импульсов - с входами записи первого элемента памяти, а также с входами записи всех элементов памяти блока элементов памяти решений, блока элементов памяти ситуаций и блока элементов памяти опроса, второй выход распределителя импульсов соединен с входами считывания элементов блока элементов памяти опроса, третий выход - с входом считывания первого элемента памяти, с четвертого по четвертый +m выходы - с входами считывания с первого по m-ый элемент блока элементов памяти решений и блока элементов памяти ситуаций, пятый +m выход - с входами считывания сумматоров первого блока сумматоров с накоплением, выходы которых подключены к входам индикаторов блока индикаторов, а информационные входы - к выходам элементов блока элементов ИЛИ, первые входы которых соединены с выходами умножителей блока умножителей, а со второго по m-ый входы - с выходами компараторов первого блока компараторов, начиная со второй строки, выходы первой строки первого блока компараторов подключены к первым входам умножителей блока умножителей, вторые входы которых соединены с выходом первого делителя, первый вход которого подключен к выходу первого сумматора с накоплением, с первого по L-ый входы которого соединены с соответствующими выходами элементов памяти блока элементов памяти опроса, информационные входы которых являются входами первой группы входов устройства, информационные входы элементов памяти блока элементов памяти ситуаций являются входами второй группы входов устройства, а выходы каждого из элементов блока памяти ситуаций подключены к первым входам компараторов соответствующей строки первого блока компараторов, вторые входы которых соединены с соответствующими выходами элементов памяти блока элементов памяти решений, информационные входы которых являются третьей группой входов устройства, информационный вход первого элемента памяти является первым входом устройства, отличающееся тем, что оно дополнительно содержит коммутатор, блок элементов памяти итогов работы, выполненный в виде матрицы, второй и третий элементы памяти, второй и третий блоки компараторов, выполненные в виде матриц, второй и третий блоки сумматоров с накоплением, блок делителей, второй и третий сумматоры с накоплением, второй, третий и четвертый делители, умножитель, блок индикации и второй распределитель импульсов, вход которого соединен с выходом генератора тактовых импульсов, шестой выход второго распределителя импульсов - с управляющим входом коммутатора, а седьмой выход - с входом считывания третьего элемента памяти, информационный вход которого является вторым входом устройства, а выход подключен к первым входам третьего и четвертого делителей, вторые входы которых соединены с выходами соответственно второго делителя и третьего сумматора с накоплением, с первого по М-ый входы которого подключены к выходам соответствующих делителей блока делителей, первые входы которых соединены с выходами соответствующих сумматоров второго блока сумматоров с накоплением, а вторые входы - с выходами соответствующих сумматоров третьего блока сумматоров с накоплением, с первого по L-ый входы каждого из которых подключены к выходам с первого по L-ый компараторов соответствующего столбца второго блока компараторов, первые входы каждого из которых соединены с выходом второго элемента памяти, информационный вход которого является третьим входом устройства, информационные входы каждого элемента блока элементов памяти итогов работы являются входами четвертой группы входов устройства, с которых значения времен по управляющему сигналу со второго выхода распределителя импульсов поступают на вторые входы соответствующих компараторов второго блока компараторов и на входы соответствующих компараторов третьего блока компараторов, при этом выходы каждого из этих элементов памяти подключены ко вторым входам каждого компаратора второго блока компараторов, а также к входам каждого компаратора третьего блока компараторов, выходы каждого компаратора соответствующего столбца которого соединены с первым по L-ый входы соответствующего сумматора второго блока сумматоров с накоплением, выходы каждого из которых подключены к соответствующим М входам второго сумматора с накоплением, выход которого соединен с первым входом второго делителя, второй вход которого подключен к первому выходу коммутатора, второй выход которого соединен со вторым входом первого делителя, а информационный вход коммутатора - с выходом первого элемента памяти, выход третьего делителя подключен к первому входу умножителя, второй вход которого соединен с выходом четвертого делителя, а выход умножителя - с входом блока индикации.

| УСТРОЙСТВО ДЛЯ ВЫБОРА РАЦИОНАЛЬНЫХ РЕШЕНИЙ | 2000 |

|

RU2158955C1 |

| Устройство для выбора оптимальных решений | 1990 |

|

SU1774354A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НА ГРАФАХ | 1996 |

|

RU2100838C1 |

| Устройство для выбора оптимальных решений | 1989 |

|

SU1640716A1 |

| US 5535406 А, 09.07.1996 | |||

| US 5361373 А, 01.11.1994. | |||

Авторы

Даты

2003-06-27—Публикация

2002-03-11—Подача