Настоящее изобретение относится к миниатюризированным устройствам для съемки изображений, в особенности для снятия отпечатков пальцев.

Для автоматического распознавания изображений с типовым структурированием, как, например, в случае отпечатка пальца, наряду с блоком для съемки изображения требуется также блок для обработки изображения для выделения существенных составных частей, как, например, характерных для отпечатка пальца деталей. Использовавшиеся до настоящего времени решения (см., например, IBM Technical Disclosure Bulletin 17, 406-407, 1974) требуют дорогостоящих схем, которые занимают много места и потребляют значительную энергию. Поэтому для съемки малых изображений, например, отпечатков пальцев, используют блоки датчиков, отдельные от блоков обработки и оценки. Блоки датчиков состоят из большого числа отдельных сенсорных элементов, которые упорядочены в виде растра. Блок обработки состоит чаще всего из микроконтроллера и/или цифрового процессора сигналов. Однако такие гибридные системы для применения в качестве продукта массового производства являются слишком дорогостоящими, так что подобные конструкции для целого ряда областей применения связаны с весьма высокими затратами. Алгоритмы для оценки снятого изображения зачастую очень сложны, особенно если, как в случае, представленном в вышеупомянутой публикации, необходимо выделять особые характеристики снятого изображения и сравнивать его с эталонными изображениями.

Известен способ съемки и обработки отпечатков пальцев на растре, разделенном на шестиугольные элементы (см. A.P. Fitz, R.J. Green: "Fingerprint preprocessing on hexagonal grid", European Convention on Security and Detection, London 1995, p. 257-260). В этом способе для упрощения черно-белого изображения обрабатываются частичные растры из соответственно 7 отдельных шестиугольников, упорядоченных в одном шестиугольнике. Дальнейшее развитие этого способа описано в публикации: Richard С. Staunton: "An analysis of hexagonal thinning algorithms and skeletal shape representation", Pattern Recognition 29, 1131-1146,. 1996. С помощью описанного алгоритма широкие линии изображения сокращаются до минимально возможной ширины.

В публикации: W.Weber e.a.: "On the Application of the Neuron MOS Transistor Principle for Modem VLSI Design", IEEE Transactions on Electron Devices 43, 1700-1708 (1996) описаны транзисторные структуры, с помощью которых могут строиться логические схемы с взвешиванием (оценкой) входных величин.

Задачей настоящего изобретения является создание устройства для съемки изображения, которое пригодно для применения при малых размерах изображения и для определения и обработки детальных особенностей структур линий изображения.

Эта задача решается с помощью устройства, имеющего признаки пункта 1 формулы изобретения. Дальнейшее развитие изобретения отражено в зависимых пунктах.

В устройстве, соответствующем изобретению, изображение, например, отпечатка пальца, воспринимается с помощью множества сенсорных элементов, которые упорядочены в виде растра предпочтительно с шестиугольной структурой. Для каждого сенсорного элемента имеется собственный процессорный элемент, который расположен вблизи соответствующего сенсорного элемента. Процессорные элементы предназначены для того, чтобы запоминать значения, получаемые из измеренной величины, выработанной сенсорным элементом, предпочтительно логический "0" или логическую "1", и выполнять соответственно реализованные алгоритмы, чтобы изменить запомненное значение в том случае, если выполняются определенные условия для данного значения и значений из запоминающих устройств смежных процессорных элементов. Эти алгоритмы могут быть предназначены в особенности для того, чтобы исключить нерегулярности в воспринятом изображении, которые несущественны для распознавания основной структуры. Кроме того, с помощью этих алгоритмов контуры изображения, например, выделяются более четко тем, что широкие линии сокращаются до определяемой растром минимальной стандартной ширины. В случае если устройство предназначено для обнаружения и идентификации отпечатков пальцев, в процессорных элементах могут быть реализованы алгоритмы оценки, с помощью которых могут устанавливаться характерные элементы изображения (такие детали, как, например, окончания и разветвления линий) и сравниваться с сохраненными эталонами.

Поэтому отдельный элемент соответствующего изобретению устройства содержит сенсорный элемент и предусмотренный для обработки процессорный элемент с запоминающим устройством. Такой блок устройства может поэтому изготавливаться в виде схемы с использованием способа изготовления микроэлектронных компонентов. Каждый процессорный элемент связан с группой процессорных элементов, точно определенной из остальных процессорных элементов таким образом, что данный процессорный элемент может получать значения, переданные от связанных с ним процессорных элементов. Предпочтительно каждый процессорный элемент таким путем связывается со смежными процессорными элементами (в случае шестиугольного растра с шестью процессорными элементами). Процессорный элемент подает имеющееся в его запоминающем устройстве значение на соседние процессорные элементы (например, шесть) и получает через соответствующий вход от этих процессорных элементов переданное значение, которое было сохранено соответствующим соседним процессорным элементом. Группа процессорных элементов, связанных с данным процессорным элементом, не должна обязательно охватывать смежные с ним процессорные элементы, но может в соответствии с реализованными алгоритмами включать дополнительно или исключительно удаленные процессорные элементы.

Взаимные соединения между процессорными элементами осуществляются предпочтительно с помощью электропроводных соединений. Применение растра, который формируется подобно выстиланию паркета из одинаковых по величине предпочтительно правильных шестиугольников, в качестве основы для размещения отдельных блоков, которые включают в себя соответственно сенсорный элемент и процессорный элемент, имеет то преимущество, что съемка изображений осуществляется особенно эффективно с учетом требуемой дальнейшей обработки. Это обусловлено плотностью элементов "паркета", числа имеющихся смежных элементов и симметрии конфигурации.

Особое преимущество соответствующего изобретению устройства состоит в том, что обеспечивается обнаружение очень малых структур изображения, так как блоки, из которых составлено изображение, содержат процессорные элементы и требуют для своего размещения весьма незначительной площади. Процессорные элементы работают полностью параллельно и управляются посредством общих линий тактового сигнала, питания и управления. С помощью общих линий управления процессорные элементы могут конфигурироваться во множество определенных состояний, каждое из которых соответствует конкретному этапу обработки, на основе использования определенного алгоритма. Вследствие интеграции процессорных элементов в рамках предусмотренного для съемки изображений растра скорость обработки данных очень высока, и потребляется очень мало энергии. Хотя каждый процессорный элемент может быть реализован как схема малой мощности и работает в этом случае относительно медленно, благодаря параллельной обработке достигаются очень хорошие функциональные характеристики системы в целом.

Предпочтительно выходы процессорных элементов на краю растра связаны с их свободным выходом, так что на краях выполняются квази-зеркально симметричные краевые условия. Поле данной конфигурации может считываться последовательно посредством расположенных у края схем адресации.

Отдельный процессорный элемент образует примитивный автомат. Он имеет запоминающее устройство, в котором может запоминаться значение, соответствующее измеренному значению, полученному сенсорным элементом, а также логическую схему, которая из этого значения и из приложенных к входам данного процессорного элемента значений от связанных процессорных элементов, определяет новое действительное значение, которое запоминается в запоминающем устройстве вместо предыдущего значения. Предпочтительно процессорный элемент имеет блок памяти с двумя запоминающими устройствами состояний, из которых каждый раз активно только одно. В запоминающем устройстве может, например, запоминаться логический "0" или логическая "1", и это значение соответствует измеренному значению соответствующего сенсорного элемента. В другом запоминающем устройстве сохраняется значение, являющееся дополнительным к данному значению (т. е. в рассматриваемом примере логическая "1" или соответственно логический "0"), так что совокупность таких вторых запоминающих устройств содержит инвертированное изображение.

Ниже приведено описание устройства, соответствующего изобретению, со ссылками на чертежи фиг.1-фиг.11.

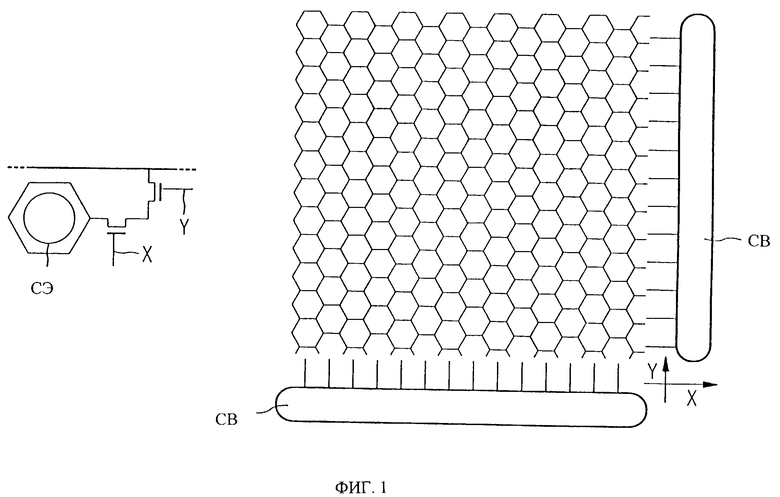

Фиг.1 - конфигурация сенсорных элементов и процессорных элементов в случае использования шестиугольного растра.

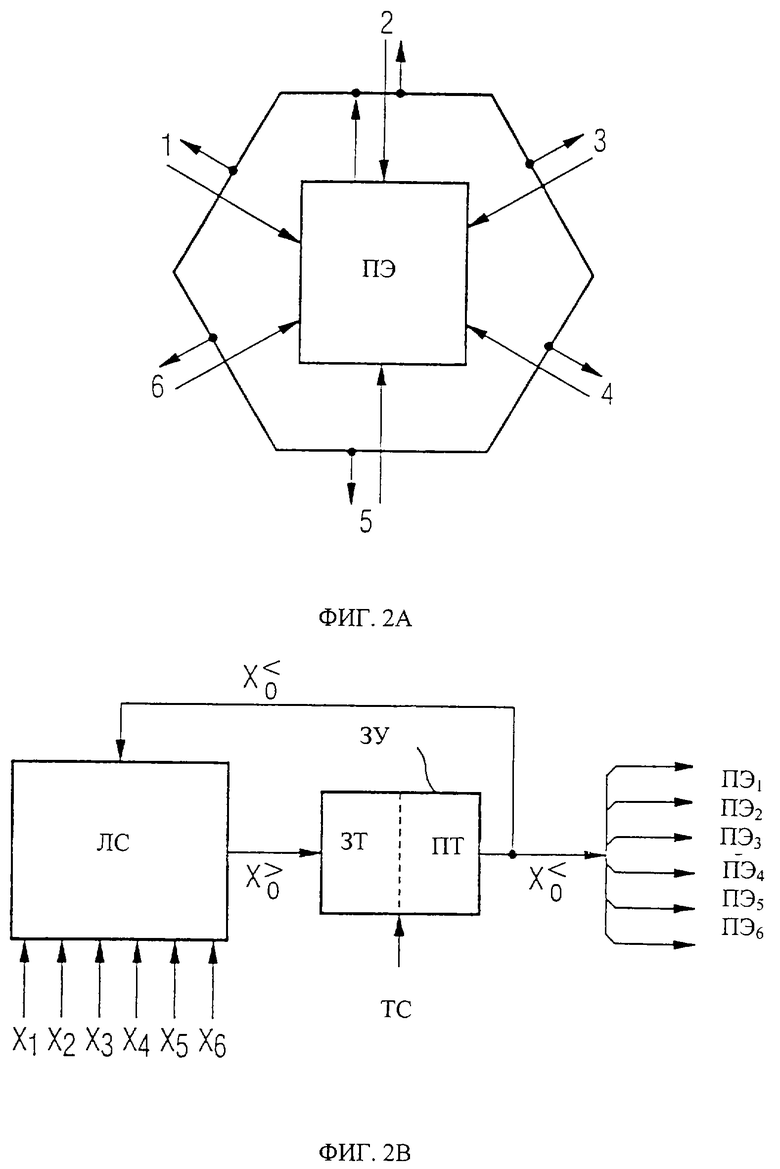

Фиг. 2а - схема входов и выходов процессорного элемента для примера шестиугольного растра.

Фиг.2b - блок-схема построения процессорного элемента.

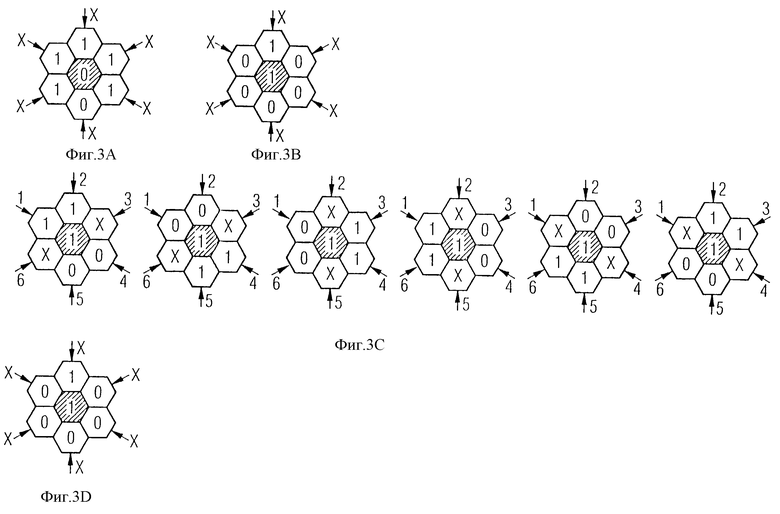

Фиг. 3 - различные группы для значений, запоминаемых связанными процессорными элементами.

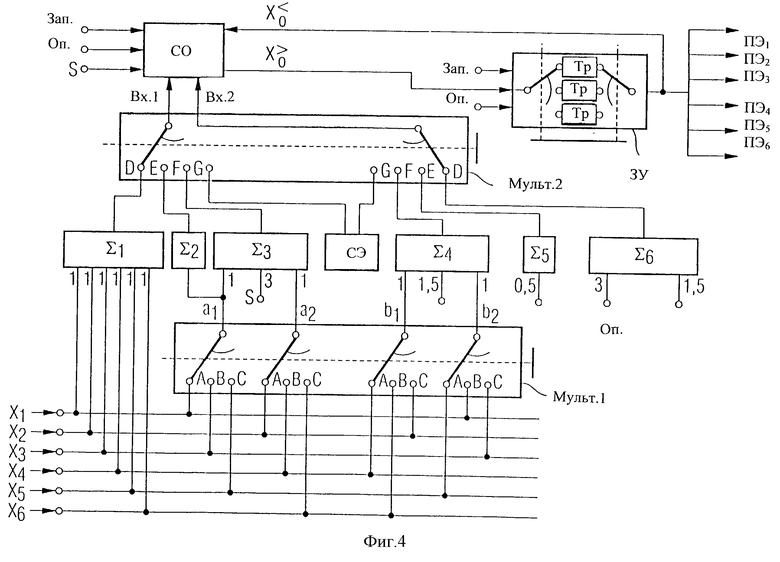

Фиг.4 - пример осуществления схемы процессорного элемента.

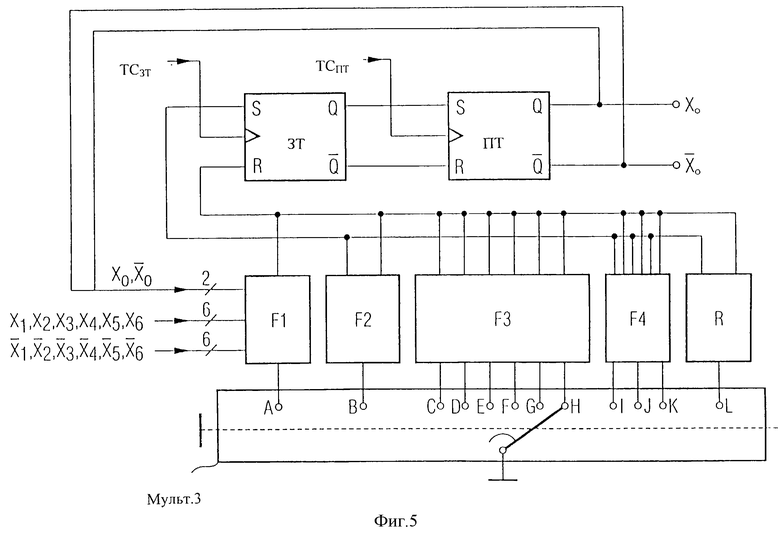

Фиг. 5 - альтернативный пример осуществления схемы процессорного элемента.

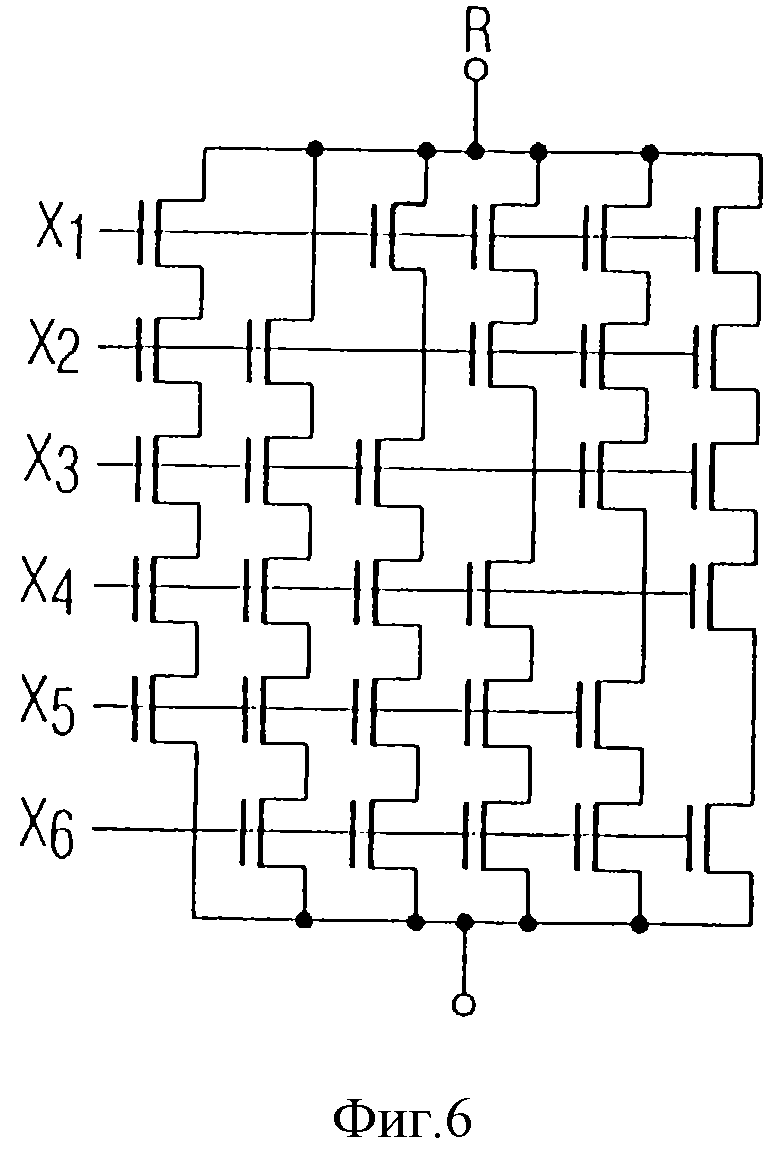

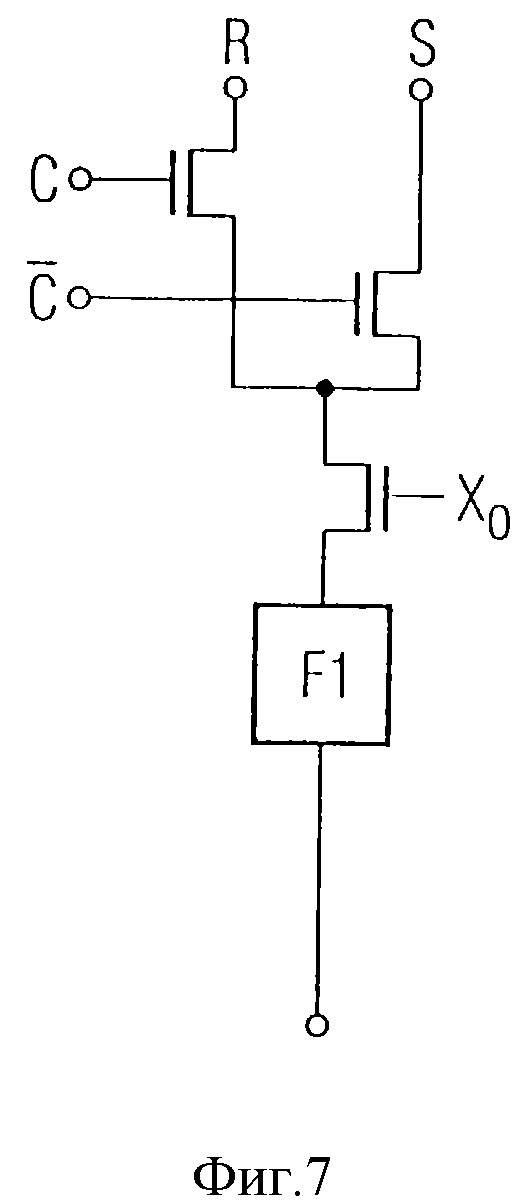

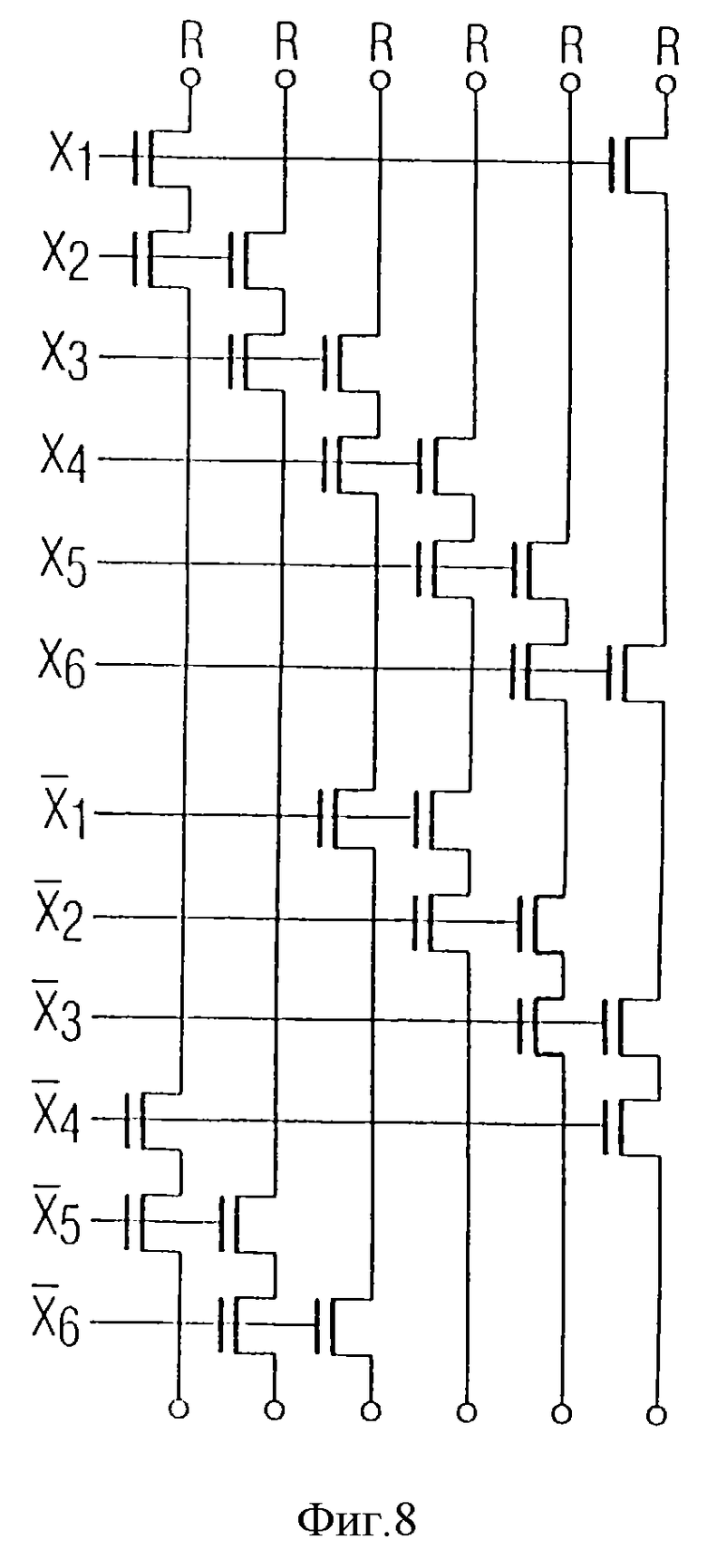

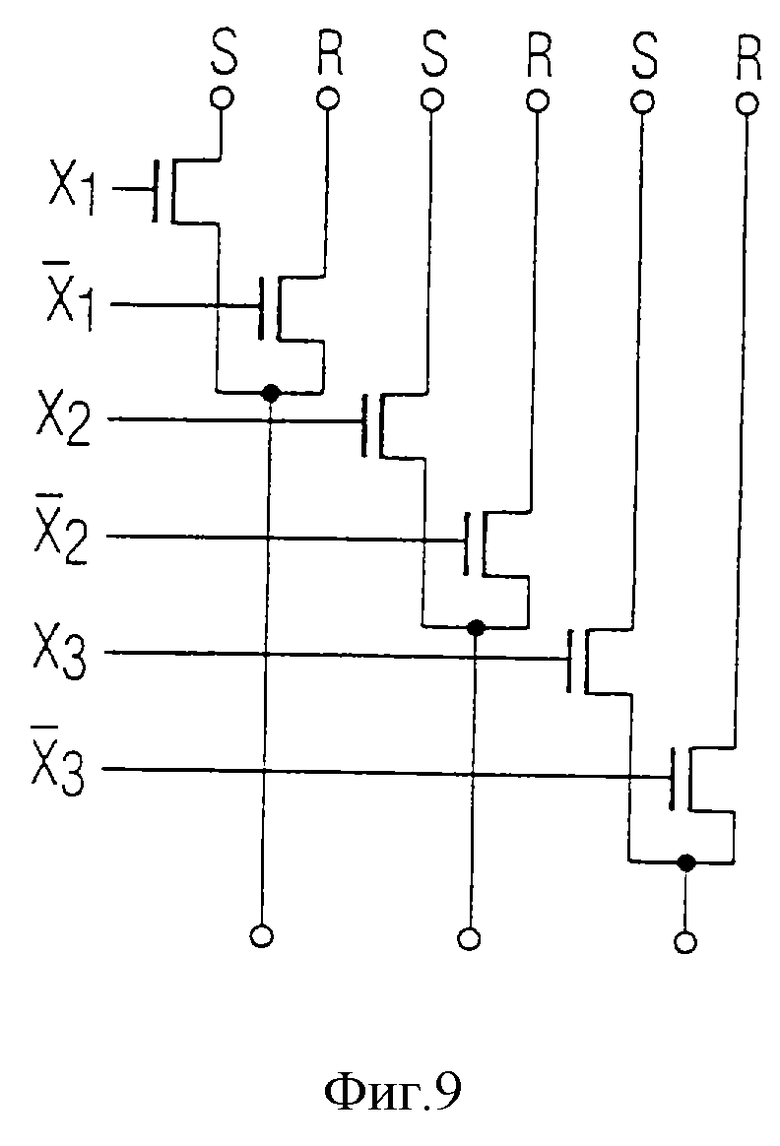

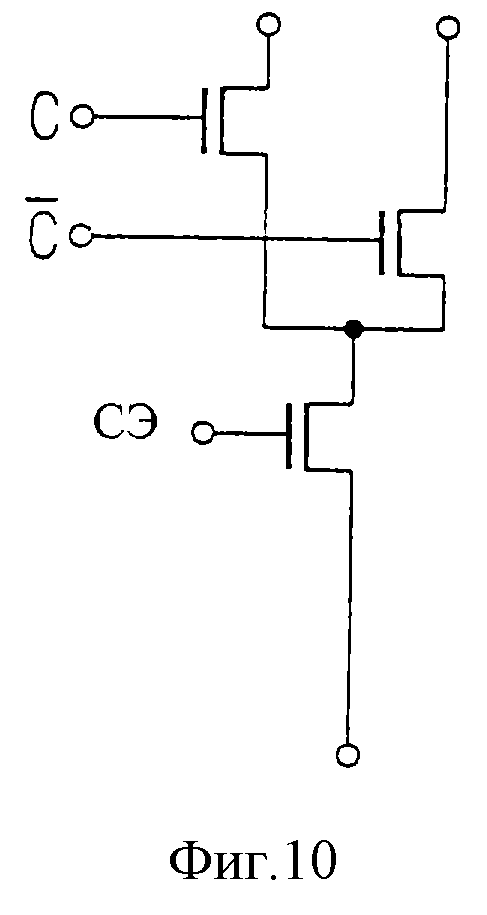

Фиг.6-10 - схемы соединений для блоков схем по фиг.5.

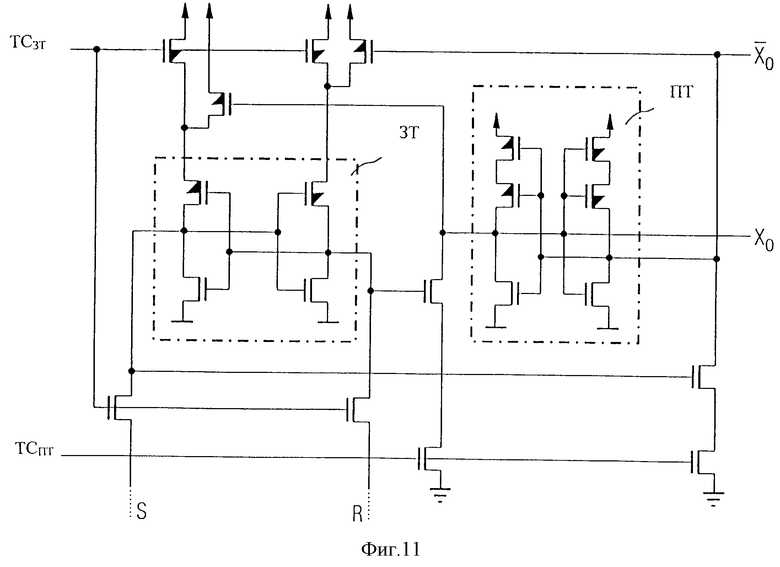

Фиг.11 - устройство запоминания на основе блока задающего и подчиненного RS-триггеров для устройства по фиг.5-10.

На фиг. 1 представлена схема соответствующего изобретению устройства на виде сверху. В виде растра, образованного в данном примере одинаковыми шестиугольниками, упорядочены отдельные сенсорные элементы СЭ. На левой стороне на фиг.1 показан пример такого сенсорного элемента с круговой сенсорной поверхностью и с транзисторами выбора для Х-направления и для Y-направления, представленными в увеличенном виде. Сенсорные элементы могут иметь другие геометрические формы, в частности (например, шестиугольные) размеры, соответствующие подразделению растра. Каждому сенсорному элементу соответствует процессорный элемент, который предпочтительно интегрирован в устройство непосредственно под сенсорным элементом в области соответствующей частичной площади растра.

Для считывания сенсорных полей могут, например, использоваться схемы выбора (СВ) (например, схемы указателя), которые в данном примере управляют блоками сенсорного поля по Х-направлению и по У-направлению. Таким путем можно считывать значения, запомненные процессорными элементами. Эта процедура соответствует в принципе считыванию матричных запоминающих устройств. Существенным для устройства; соответствующего изобретению, является то, что процессорные элементы выполнены интегрированными в растр в непосредственной близости от соответствующих сенсорных элементов. Если это устройство предусмотрено для использования в качестве датчика отпечатка пальца, то предпочтительным является то, что отдельный сенсорный элемент для емкостного измерения по существу выполнен в виде обкладки конденсатора внутри структурированного электрически проводящего слоя и расположен под опорной площадкой для кончика пальца. Сенсорный элемент или соответствующий процессорный элемент имеет в этом случае схему, с помощью которой может формироваться логический "0" или логическая "1", в зависимости от емкости, определяемой зарядом или напряжением, измеряемым сенсорным элементом.

В предпочтительном варианте осуществления устройства применяется показанный на фиг. 1 шестиугольный растр, и каждый процессорный элемент связан с шестью соседними в этом растре процессорными элементами. На фиг.2а показан такой процессорный элемент ПЭ с выходом, который разветвляется на шесть выходов 1, 2, 3, 4, 5 и 6 к смежным процессорным элементам. Процессорный элемент имеет, кроме того, по одному входу для каждого из шести смежных процессорных элементов. Таким путем можно значение, запомненное в запоминающем устройстве процессорного элемента, передать к шести соседним процессорным элементам.

На фиг. 2b представлена блок-схема, иллюстрирующая способ функционирования процессорного элемента. Значения от связанных процессорных элементов, т. е. в данном примере шесть значений X1, Х2, Х3, Х4, Х5 и Х6 от шести соседних процессорных элементов, вместе с собственным запомненным значением X

Процессорные элементы могут быть, например, выполнены с возможностью осуществления нескольких алгоритмов, с помощью которых может упрощаться структура определяемого изображения или может улучшаться четкость его контура. При определении отпечатка пальца измеренное значение отдельного сенсорного элемента, зависящее от структуры отпечатка пальца, преобразуется в логический "0" или в логическую "1". Таким путем получается изображение отпечатка пальца в виде черно-белого изображения, разрешающая способность которого соответствует величине используемого растра. Качество этого изображения улучшается за счет применения различных алгоритмов, позволяющих выработать характерные детали изображения и тем самым обеспечить возможность идентификации отпечатка пальца.

На фиг.3а показана конфигурация из семи элементов растра, причем центральный элемент окружен шестью остальными элементами. Каждый элемент содержит свой собственный сенсорный элемент и свой собственный процессорный элемент с запоминающим устройством, в котором запоминается текущее значение "0" или "1" соответствующего элемента изображения. Для такой конфигурации из семи элементов в последующем для простоты будет использоваться термин "шаблон". Для обработки полученного изображения процессорный элемент оценивает запомненное в нем значение совместно со значениями от связанных с ним, в данном случае шести, процессорных элементов и определяет таким путем новое значение. Алгоритмы выполняются необходимым образом последовательно друг за другом, причем соответствующий процессорный элемент выполняет определенный алгоритм только при выполнении необходимых условий.

Может быть предусмотрен алгоритм заполнения белых пятен в черно-белом изображении. С этой целью белые точки изображения, которым, например, присвоено логическое значение "0" и которые окружены по меньшей мере пятью черными точками изображения, могут преобразовываться в черную точку изображения (см. шаблон на фиг.3а). Логическая схема процессорного элемента устанавливает, что запомненное значение равно "0" и что из связанных с ним шести процессорных элементов по меньшей мере пять передают значение "1". Тем самым выполняется условие изменения белой точки изображения на черную точку изображения, и процессорный элемент запоминает значение "1". При использовании запоминающего устройства, соответствующего показанному на фиг.2b, с задающим и подчиненным RS- триггерами, новое значение, при управлении тактовым сигналом Т, переписывается из задающего триггера в подчиненный триггер.

Отдельные черные точки изображения, которые выделяются на фоне более крупных структур, могут быть удалены при использовании еще одного алгоритма. Если в процессорном элементе запомнено значение "1" и от соседних процессорных элементов передано максимум одно значение "1", как это имеет место для шаблона, показанного на фиг.3b, то процессорный элемент в результате действия соответствующего алгоритма может изменить значение "1" на значение "0". Тем самым края структуры изображения сглаживаются. Предпочтительно этот алгоритм сначала применяется для того, чтобы структуру линий изображения сделать более четкой. Затем заполняются белые пробелы путем замены значения центральной точки изображения в шаблоне, соответствующем фиг.3а, с "0" на "1". Ориентация при этом не играет никакой роли, т.е. шаблоны, показанные на фиг.3а и 3b, могут быть повернуты на угол, кратный 60o.

Обработка шаблона, показанного на фиг.3с, сужает широкие линии до линий шириной в один пиксель. Значения, обозначенные символом "х", могут представлять собой "0" или "1" и безразличны для данного алгоритма. Существенным является лишь то, что оба процессорных элемента одной пары передают значение "1", а процессорные элементы другой пары передают значение "0". Процессорные элементы пар находятся по соседству друг с другом, и каждый процессорный элемент пары не находится по соседству с процессорными элементами другой пары, так что обе пары, как представлено для различных ориентации шаблонов на фиг. 3с, размещены параллельно одна другой. Этот алгоритм применяется для одного шаблона по фиг.3с во всем изображении, затем для другого шаблона по фиг.3с также во всем изображении и т.д. для всех показанных шаблонов. Алгоритм осуществляется многократно циклически все время в одной и той же последовательности шаблонов, которая сама по себе может быть любой и не обязательно должна соответствовать последовательности, показанной на фиг.3с.

Предусмотрен еще один алгоритм, предназначенный для определения концов линий. Конец линии шириной в один пиксель изображен на шаблоне по фиг.3d. Последний элемент изображения линии образует центральный элемент этого шаблона. Этот элемент имеет поэтому значение "1", в то время как из числа соседних точек изображения только одна имеет значение "1". Алгоритм устанавливает все значения с "1" на "0", за исключением тех точек изображения, которые образуют конец линии. Можно получить дополнительную информацию о направлении линии на концах, применяя этот алгоритм также для шаблонов, которые по сравнению с шаблоном по фиг.3d повернуты на угол, кратный 60o. Эта информация о направлении может дополнительно использоваться для идентификации содержания изображения (например, отпечатка пальца).

При выделении детальных характерных особенностей отпечатка пальца эти алгоритмы применяются многократно один за другим. Предпочтительно сначала использовать алгоритм удаления отдельных черных точек изображения и сглаживания контуров линий. Затем заполняются белые пробелы в изображении. Затем попеременно применяются алгоритмы для сужения линий (шаблоны согласно фиг. 3с) и алгоритмы для удаления отдельных черных точек изображения до тех пор, пока в результате не будет получено изображение с четкими контурами и со всеми существенными детальными характерными особенностями отпечатка пальца. В зависимости от размеров растра и желательной точности число проходов этих алгоритмов может быть установлено соответствующим образом. Наконец, применяются алгоритмы для нахождения концов линий.

Предпочтительно применяются запоминающие блоки, которые имеют два запоминающих устройства, так чтобы могли быть запомнены значения, полученные из измеренных значений процессорных элементов, и значения, являющиеся дополнительными к ним. Тем самым вторые запоминающие устройства запоминающего блока содержат инвертированное изображение, т.е. негативное изображение по отношению к исходному черно-белому изображению. С помощью этого инвертированного изображения можно отыскать точки разветвления линий, так как образующие линии промежуточные пространства между линиями оканчиваются в точках разветвления, так что концы линий инвертированного изображения маркируют точки разветвления линий исходного изображения.

Логические и вычислительные операции указанных алгоритмов могут быть реализованы в виде схем в достаточно миниатюризированной форме и поэтому могут быть реализованы в процессорном элементе, который непосредственно соотносится с сенсорным элементом растра устройства. Путем соответствующего соединения процессорных элементов между собой в соответствующем изобретению устройстве можно обеспечить выполнение подобных алгоритмов процессорными элементами, которые интегрированы в растр конфигурации сенсорных элементов и которые одновременно имеют функциональные возможности, достаточные для обработки изображений.

Для реализации логической схемы процессорного элемента можно, например, применять нейронные МОП (металл-окисел-полупроводник)-схемы, с помощью которых могут быть реализованы приведенные выше алгоритмы, например, соответствующие схеме по фиг.4. Схема содержит блок, представляющий собой схему оценки (СО), на которую подаются соответствующим образом взвешенные значения через ряд соответственно попарно переключаемых нейронных МОП-транзисторов. Схема оценки может представлять собой, например, ключевую схему с фиксацией состояния (защелку), которая после оценки сохраняет свое состояние. Сигналы, подаваемые на вход запуска (Зап.) и опорный вход (Оп.), обеспечивают принятие решения, следует ли проводить оценку или нет. Посредством входа S схеме оценки может быть дана команда выдать негативное выходное значение. В случае S= 1 схема может, например, выдавать значение "1", если значение на первом входе Вх. 1 больше, чем значение на втором входе Вх.2. В случае S=0 схема выдает соответственно значение "1", если значение на первом входе Вх.1 меньше, чем значение на втором входе Вх.2.

Схема содержит также первый мультиплексор Мульт.1, второй мультиплексор Мульт.2 и шесть сумматоров Σ1, Σ2, Σ3, Σ4, Σ5, и Σ6, которые могут быть реализованы, например, посредством нейронных МОП-транзисторов. Значения X1, Х2, Х3, Х4, X5 и Х6, выработанные соседними процессорными элементами, со входа соответствующих схем, показанных на фиг.4, подаются на первый сумматор Σ1 или на входы первого мультиплексора Мульт.1. Между несколькими имеющимися входами А, В и С первого мультиплексора осуществляется одновременное переключение, так что всякий раз либо входные значения на входах А, либо входные значения на входах В, либо входные значения на входах С связываются с четырьмя выходами первого мультиплексора.

Второй мультиплексор Мульт.2 переключается одновременно, так что оба выхода связываются либо с обоими входами D, Е, F и G. Каждая пара нейронных МОП-транзисторов представляет за счет специальным образом установленного соотношения емкостей определенный тип алгоритма (указывается числами, приведенными на входах сумматоров), т.е. в рассматриваемом примере представлены шаблоны, соответствующие фиг.3. Сумматоры Σ1 и Σ6, Σ2 и Σ5, Σ3 и Σ4 вместе соответственно образованы парами нейронных МОП-транзисторов. В случае, если выбран вход F, то на входах Вх.1 и Вх.2 блока присутствуют значения a1+а2+3S и соответственно b1+b2+1,5, вычисленные сумматорами Σ3 и Σ4. В соответствии с вышеописанным свойством блока СО, в случае S=1, между названными значениями на входах блока СО будет иметь место знак неравенства ">", а в случае S= 0 для указанных значений определяющим для оценки будет знак неравенства "<".

Путем выбора пар нейронных МОП-транзисторов (входы D, Е и F второго мультиплексора Мульт.2) в примере по фиг.3 три из необходимых алгоритмов могут преобразовываться. В случае S=1, Оп.=1 и при переключении второго мультиплексора на вход D, сумматоры Σ1 и Σ6 выдают сумму значений с X1 по Х6 и значение 4,5, которые сравниваются между собой посредством знака неравенства ">". Тем самым устанавливается, выработали ли по меньшей мере пять соседних процессорных элементов значение "1".

В случае S= 1 или S=0 и Оп.=0 и при подключении второго мультиплексора Мульт.2 на вход D, к входам Вх.1 и Вх.2 блока СО прикладывается сумма значений с X1 по Х6 и значение 1,5. В схеме оценки устанавливается, является ли сумма значений, переданных соседними процессорными элементами, большей (S=1) или меньшей (S= 0) чем 1,5. Это важно для алгоритмов исключения отдельных черных точек изображения и для сглаживания краев линий и для алгоритмов идентификации концов линий.

С помощью комбинации сумматоров Σ2 и Σ5 и схемы второго мультиплексора на вход Е можно сдвинуть значение "1" в рамках рассматриваемой конфигурации в трех различных направлениях.

Если второй мультиплексор подключен на вход F, то между собой сравниваются значения a1+а2+3S и b1+b2+1,5. Если S=0, то проверяется, является ли первое значение меньшим, чем второе значение. Если S=1, то проверяется, является ли первое значение большим, чем второе значение. Это может иметь место только в том случае, если не - a1 и а3 оба равны "0" и b1 и b2 оба равны "1" или наоборот. В случае, если a1=а2="0" или "1" и b1=b2="1" или "0", то блок СО выдает значение "0", что желательно для алгоритма сужения линий. В соответствии с соединениями входов, значения a1 и а2 и соответственно b1 и b2 поставлены в соответствие двум парам связанных процессорных элементов, компоненты которых являются смежными один другому и не являются смежными компонентам другой пары.

Если для оценки выработанного нейронными МОП-транзисторами взвешенного потенциала используется ключевая схема с фиксацией состояния, устройство запоминания состояния может быть реализовано любым однокаскадным триггером, так как действительное состояние соответственно запомнено в схеме оценки (т. е. схема оценки представляет собой задающий триггер, а триггером устройства запоминания состояния является подчиненный триггер). Также устройство запоминания состояния (УЗС) имеет вход запуска (Зап.), с помощью которого принимается решение, принято ли новое состояние или нет. Могут иметься несколько таких устройств запоминания состояния, между которыми может осуществляться переключение, как представлено для показанного на фиг.4 запоминающего устройства. Тем самым можно обеспечить запоминание промежуточных состояний в процессе обработки. Для считывания значения "0" или "1", соответствующего измеренному значению соответствующего сенсорного элемента, второй мультиплексор Мульт. 2 переключается на входы G. От блока СО новые значения соответствующих точек изображения X

Логическая схема в блоке СО предпочтительно выполнена таким образом, что оценка или принятие нового значения в устройство запоминания состояния осуществляется только тогда, когда накопленное самим оценивающим процессорным элементом значение выполняет соответствующие условия. Для алгоритмов сглаживания краев, сужения линий и отыскания концов линий это условие состоит в том, что запомненное значение X

Показанный на фиг. 5 вариант схемы содержит несколько функциональных блоков F1, F2, F3, F4 и R. Кроме того, имеются декодер, реализующий принцип "1 из 12", показанный в виде мультиплексора Мульт.3, и специальные задающий и подчиненный RS-триггеры для запоминания состояния и для проведения оценки. Функциональные блоки состоят соответственно из некоторого числа n-МОП-транзисторов, которые соответствующим образом как логическая схема "И" и логическая схема "ИЛИ" включены последовательно или параллельно и запускаются логическим уровнем "0" или "1" на управляющем электроде. Функциональный блок имеет два вывода, между которыми он, в зависимости от состояния, в котором он находится, обеспечивает протекание тока или непроводящее состояние. Несколько таких функциональных блоков включены параллельно; однако всегда только один функциональный блок через мультиплексор Мульт.3 соединен с массой. Шесть входов для передаваемых от связанных процессорных элементов значений X1, X2, Х3, X4, Х5 и Х6 и для дополнительных к ним значений для упрощения чертежа показаны одной линией.

На фиг.6 показано возможное выполнение функционального блока F1, на фиг. 7 - выполнение функционального блока F2, на фиг.8 - выполнение функционального блока F3, на фиг.9 - выполнение функционального блока F4 и на фиг. 10 - выполнение функционального блока R. Функциональный блок F1 замыкается накоротко на массу, если по меньшей мере пять ил шести значений от X1 до Х6 имеют логическое значение "1" (для выполнения алгоритма, обеспечивающего заполнение пробелов). С помощью функционального блока F2 могут выполняться алгоритмы выравнивания краев и для идентификации концов линий. С помощью общей управляющей величины С (фиг.7) осуществляется переключение между этими двумя алгоритмами. Функциональный блок F3 служит для того, чтобы осуществлять алгоритм сужения линий. С помощью функционального блока F4 можно смещать значения в точках изображения концов линий в трех основных направлениях растра. С помощью функционального блока R (фиг.10) может считываться вырабатываемое сенсорным элементом логическое значение (вход СЭ).

Ввиду применяемой n-МОП-транзисторной логики пропускания в показанных на чертежах схемах к входам R и S задающего и подчиненного триггеров постоянно приложен только "0" (потенциал массы) или "1" (вывод разомкнут, так как переключатель заперт). При применении комплементарной транзисторной логики пропускания можно получить соответственно инвертированные логические уровни, что, однако, повлечет за собой удвоение потребной площади для размещения.

Пример выполнения соответствующего устройства запоминания состояния, пригодного для осуществления схемы по фиг.5, показан на фиг.11. Способ работы этого специализированного триггера особенно предпочтителен для того, чтобы описанные алгоритмы осуществлять во взаимосвязи с указанными функциональными блоками. Имеющиеся триггеры управляются тактовыми сигналами Тзт и Тпт, которые смещены во времени один относительно другого. Путем тиражирования подчиненного триггера возможно запоминание нескольких состояний, если осуществляется выбор с помощью дополняющего мультиплексора.

Изобретение относится к способам распознавания образов. Его применение в дактилоскопических исследованиях посредством сенсорных элементов, упорядоченных в растр, позволяет получить технический результат в виде снижения энергопотребления и миниатюризации аппаратуры для снятия отпечатков пальцев при одновременном увеличении ее разрешающей способности. Этот результат достигается благодаря тому, что каждый элемент растра содержит помимо сенсорного еще и процессорный элемент, благодаря чему обработка изображения осуществляется параллельно. Отдельный процессорный элемент имеет как минимум одно запоминающее устройство для хранения значения, измеренного сенсорным элементом, а также логическую схему, которая на основе этого значения и аналогичных значений, измеренных соседними элементами растра, определяет истинное значение элемента изображения, которое и записывается в запоминающее устройство. 6 з.п. ф-лы, 11 ил.

| Система для распознавания дактилоскопических отпечатков | 1991 |

|

SU1836696A3 |

| СПОСОБ ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ ПАПИЛЛЯРНОГО УЗОРА | 1993 |

|

RU2051415C1 |

| US 5635723 A, 03.06.1997. | |||

Авторы

Даты

2003-06-27—Публикация

1998-12-14—Подача