Изобретение относится к электронному запоминающему устройству (ЗУ) с электрически программируемыми ячейками ЗУ, адресной шиной для адресации ячеек ЗУ, а также с управляемым формирователем напряжения программирования для выработки напряжения программирования для ячеек ЗУ.

Электронные запоминающие устройства такого рода в общем случае реализуют на полупроводниковой интегральной микросхеме, которая имеет, например, модуль электрически стираемого программируемого постоянного запоминающего устройства (ЭСППЗУ) с полем ЗУ и с формирователем напряжения программирования, а также другой модуль со схемой декодирования и логической схемой, с которым связаны входы и выходы интегральной микросхемы. Поле ЗУ представляет собой собственно запоминающее устройство и включает в себя некоторую конфигурацию из множества ячеек памяти.

Для программирования отдельных ячеек ЭСППЗУ к ним должно прикладываться напряжение программирования, которое составляет, например, 20 В и значительно превышает напряжение питания, составляющее, например, 5 B. Оптимальное напряжение программирования получают в интегральной микросхеме из напряжения питания с помощью регулируемого формирователя напряжения.

В ЕР-А-0594294 описано электронное запоминающее устройство, содержащее электрически программируемые ячейки ЗУ, адресную шину для адресации ячеек памяти, а также управляемое напряжение программирования для выработки напряжения программирования для ячеек ЗУ.

После изготовления такой полупроводниковой интегральной микросхемы необходимо, в числе прочего, протестировать ЭСППЗУ для проверки его функциональный возможностей. Для этого предусмотрены специальные команды программирования, с помощью которых программируется поле ЗУ.

В одном из таких испытаний напряжение программирования снижается, например, на определенное значение, чтобы проверить, не становятся ли ячейки ЗУ при таком напряжении программирования перепрограммируемыми.

Это напряжение программирования подается извне через дополнительный контактный вывод тестирования в полупроводниковую интегральную микросхему. Этот контактный вывод тестирования, однако, для нормального режима ЗУ не требуется. Он занимает площадь микросхемы, препятствуя увеличению емкости ЗУ или приводя к увеличению габаритов интегральной микросхемы по сравнению с тем, как это было бы необходимо.

В основе изобретения лежит задача создания электронного запоминающего устройства вышеупомянутого типа, в котором для проведения тестирования функций ЗУ не требуется упомянутый контактный вывод тестирования.

Согласно пункту 1 формулы изобретения, эта задача решается тем, что в электронном запоминающем устройстве вышеупомянутого типа предусмотрено переключающее устройство, которое приводится в действие сигналом режима тестирования и с помощью которого адресная шина в режиме тестирования присоединяется к формирователю напряжения программирования таким образом, что посредством подаваемых адресных битов может устанавливаться предварительно задаваемое тестовое напряжение программирования.

Преимущество этого решения состоит в том, что благодаря применению адресных битов в структуре команды интегральной микросхемы не требуются дополнительные операции в декодере команд или логике управления, чтобы передать номинальные значения формирователю напряжения программирования.

Кроме того, в случае, когда в ЗУ сохраняются данные, критичные с точки зрения их защищенности, из-за отсутствия контактного вывода тестирования для потенциального нарушителя исключается возможность несанкционированного доступа. Команды тестирования могут быть постоянным образом "зашиты" в интегральной микросхеме еще в процессе ее изготовления, чтобы исключить возможность последующей манипуляции ими.

Наконец, такое запоминающее устройство требует меньше места в микросхеме, так что при одинаковых габаритах плотность компоновки ЗУ на интегральной микросхеме повышается, или сама микросхема при той же емкости ЗУ может быть выполнена с меньшими габаритами.

В зависимых пунктах охарактеризованы предпочтительные варианты осуществления изобретения.

При этом в качестве тестового напряжения программирования может, в частности, задаваться напряжение, при котором ячейки ЗУ в состоянии без ошибок еще не становятся перепрограммируемыми.

Ячейки ЗУ образуют предпочтительно поле ЭСППЗУ. Однако можно использовать и другие типы ЗУ, для которых напряжение программирования необходимо для изменения содержимого ЗУ и должно варьироваться для целей тестирования.

Кроме того, предварительно задаваемое тестовое напряжение программирования в режиме тестирования предпочтительно устанавливается посредством команды программирования.

В качестве переключающего устройства может быть использован мультиплексор.

Формирователь напряжения программирования в общем случае является регулируемым, так что с помощью адресных битов в режиме тестирования можно задавать номинальные значения для тестового напряжения программирования.

Кроме того, адресные биты, подаваемые в тестовом режиме в качестве составной части одной или нескольких тестовых команд программирования, могут сохраняться в запоминающем устройстве и выполняться по мере необходимости.

Дополнительные детали, признаки и преимущества изобретения поясняются в последующем описании предпочтительного варианта осуществления изобретения с помощью чертежей, на которых представлено следующее.

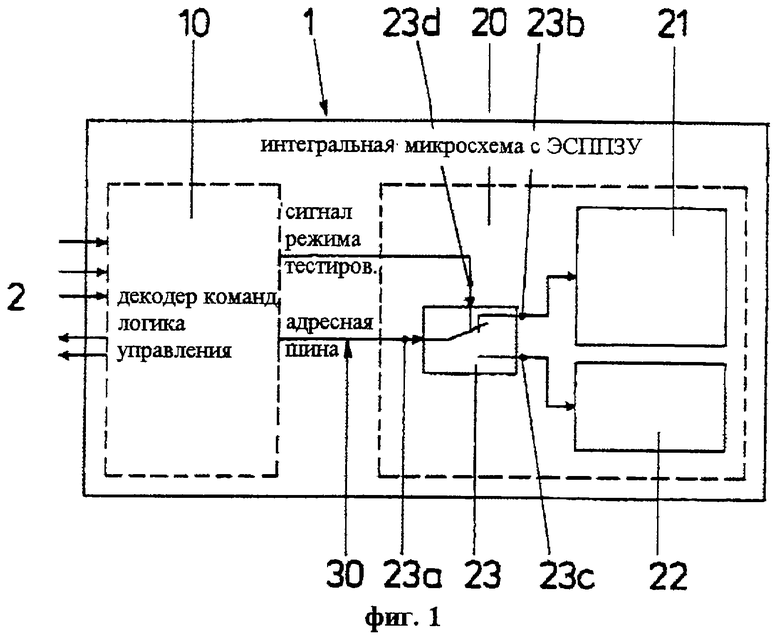

Фиг.1 - структурная схема упомянутого варианта выполнения.

Фиг.2а и 2b - структура различных команд для подачи на схему по фиг.1.

Электронное запоминающее устройство 1 с входами и выходами 2 содержит, согласно фиг.2, первый схемный модуль 10, второй схемный модуль 20, а также адресную шину 30, соединяющую оба схемных модуля.

Первый схемный модуль 10 содержит декодер команд и схемы для логики управления. Кроме того, с этим модулем связаны входы и выходы 2 запоминающего устройства 1.

Второй схемный модуль 20 имеет поле 21 ЗУ с множеством отдельных ячеек ЗУ, формирователь 22 напряжения программирования со средствами регулирования, а также мультиплексор 23, с входом 23а которого соединена адресная шина 30. Мультиплексор 23 имеет два выхода 23b, 23с, из которых один соединен с полем 21 ЗУ, а другой - с формирователем 22 напряжения программирования. Мультиплексор 23 выполняет функцию переключателя для присоединенной к его входу 23а адресной шины 30, переключая ее между полем 21 ЗУ и формирователем 22 напряжений программирования. Процесс переключения управляется сигналом режима тестирования, подаваемым на управляющий вход 23d.

После изготовления такого электронного запоминающего устройства 1 необходима проверка безошибочности выполнения его функций. Особенно должно гарантироваться то, что ячейки ЗУ становятся перепрограммируемыми только при достижении предварительно заданного напряжения программирования, а не уже при существенно более низком напряжении. Тем самым существовала бы опасность непреднамеренного изменения содержимого ячеек ЗУ, если, например, ввиду непредсказуемых обстоятельств внезапно повысилось бы напряжение питания. В процессе соответствующего тестирования напряжение программирования снижается на определенное значение, чтобы проверить, не допускают ли ячейки ЗУ как раз при этом напряжении возможность перепрограммирования. Так как с помощью этого теста все ячейки ЗУ исследуются одновременно, не требуется их адресация.

Поэтому для проведения тестирования мультиплексор 23 посредством своего управляющего входа 23d управляется сигналом режима тестирования, так что адресная шина 30 присоединяется ко второму выходу 23с, связанному с формирователем 22 напряжения программирования. Затем напряжение программирования, подаваемое через адресную шину 30, снижается на предварительно определенную величину, причем адресные биты непосредственно подаются в контур регулирования формирователя 22 напряжения программирования и задают новое номинальное значение для пониженного напряжения программирования. Наконец, мультиплексор 23 переключается обратно, и ячейки ЗУ могут проверяться на предмет изменения; их содержимого.

Установку напряжения программирования можно реализовать простым способом в структуре команды интегральной микросхемы.

В случае показанной на фиг.2а известной структуры команды считывания и программирования, включающей в себя часть команды, адресную часть и часть данных, команда программирования в режиме тестирования может иметь форму, представленную на фиг.2b. Биты с 8 по 15 адресной части служат при этом, например, для установки тестового напряжения программирования, в то время как биты с 0 по 7 части команды используются для последующих установок режима тестирования или могут оцениваться как "безразличные".

Изобретение относится к электронным запоминающим устройствам (ЗУ) с электрически программируемыми ячейками. Техническим результатом является возможность хранения и защиты в ЗУ данных, критичных с точки зрения их защищенности. Устройство содержит электрически программируемые ячейки, адресную шину для адресации, управляемый формирователь напряжения программирования, переключающее устройство. 6 з.п. ф-лы, 3 ил.

| Бисерная мельница | 1974 |

|

SU594294A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО МАГАЗИННОГО ТИПА | 1991 |

|

RU2081459C1 |

| US 5615159 А, 25.03.1997 | |||

| US 5596537 А, 21.01.1997 | |||

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ВЫХОДНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2006971C1 |

| US 5177745 A, 05.01.1993. | |||

Авторы

Даты

2003-11-20—Публикация

1998-06-24—Подача