Изобретение касается полупроводникового запоминающего устройства, по крайней мере, с одной, в частности, энергонезависимой ячейкой памяти, которая имеет следующие отличительные признаки:

- предусмотрен избирательный транзистор с каналом типа n, а также запоминающий транзистор с каналом типа n,

- избирательный транзистор с каналом n имеет избирательный вывод затвора, а также два избирательных канальных вывода, причем избирательный вывод затвора соединяется с ведущей к ячейке памяти горизонтальной шиной,

- запоминающий транзистор с каналом типа n имеет запоминающий вывод затвора или управляющий затвор, а также два запоминающих канальных вывода,

- второй запоминающий канальный вывод и первый избирательный канальный вывод соединяются друг с другом, причем другой запоминающий канальный вывод или другой избирательный канальный вывод соединяется с ведущей к ячейке памяти вертикальной шиной,

причем полупроводниковое запоминающее устройство имеет, по крайней мере, один переходный транзистор с первым и вторым переходными канальными выводами, причем первый переходный канальный вывод соединяется с запоминающим выводом затвора.

При стандартных полупроводниковых запоминающих устройствах отдельные транзисторы выполнены по технологии полевых транзисторов (FET) на одной полупроводниковой подложке. При этом запоминающий транзистор имеет плавающий затвор (floating gate), так что он за счет подачи надлежащих напряжений на канальные выводы и на вывод затвора может программироваться так, что он надолго или энергонезависимо может принимать желаемое состояние.

Для считывания ячейки памяти запоминающий канальный вывод и избирательный канальный вывод соединены между собой, причем другой свободный запоминающий канальный вывод или другой свободный избирательный канальный вывод соединен с ведущей к ячейке памяти вертикальной шиной. При этом избирательный транзистор управляется так, что он проводит. Если тогда при подаче напряжения на соответствующую вертикальную шину течет ток, то запоминающий транзистор в предыдущем шаге был запрограммирован на "проводящий" или записан. Если при подаче этого напряжения на вертикальную шину при проводящем избирательном транзисторе ток не течет, то запоминающий транзистор в предыдущем шаге был запрограммирован на "непроводящий" или стерт.

В ЕР 0317443 А1 показана ячейка памяти на двух транзисторах, которая включает в себя избирательный транзистор и транзистор с плавающим затвором. Затвор транзистора с плавающим затвором для управления нагружается особым напряжением.

При стандартных запоминающих устройствах особенно проблематичным является то, что необходимые для программирования напряжения должны производиться с высокими технологическими затратами. Сверх того, при программировании ячейки памяти часто происходят ошибки в других ячейках памяти, к которым в данный момент времени не было произведено обращение для программирования.

Поэтому задачей изобретения является изготовление серийной ячейки памяти, а также стандартного полупроводникового запоминающего устройства, которое может безошибочно программироваться с небольшими технологическими затратами.

Эта задача решается за счет того, что переходной транзистор выполнен как переходной транзистор с каналом типа р, причем второй переходной канальный вывод не соединяется, как при современном уровне техники, с внешним напряжением управляющего затвора, а соединяется с ведущей к ячейке памяти горизонтальной шиной.

Изобретение основано на знании того, что при стандартных схемах должны преодолеваться потери порогового напряжения в переходном транзисторе, так что должны предусматриваться более высокие напряжения переходного затвора. Эта проблема может решаться за счет того, что переходной транзистор выполняется как транзистор с уменьшенным пороговым напряжением, что, тем не менее, должно окупаться повышенными технологическими затратами.

При исполнении в соответствии с изобретением и неправильном включении переходного транзистора для программирования запоминающего транзистора больше нет необходимости в преодолении порогового напряжения переходного затвора, так что возможно надежное программирование с небольшими технологическими затратами.

Изобретение основывается далее на знании того, что напряжение управляющего затвора на основании особого неправильного включения переходного транзистора в уровне техники при современных неуправляемых ячейках памяти "плавает" в неопределенном свободном ходе, что может приводить к емкостным связям выше критических напряжений программирования. Такие емкостные связи выше критических более не имеют места при ячейках памяти полупроводникового запоминающего устройства в соответствии с изобретением, так как при программировании полупроводникового запоминающего устройства каждый вывод запоминающего затвора находится в определенном состоянии.

Вывод переходного затвора переходного транзистора при исполнении в соответствии с изобретением может нагружаться измененным на высокое напряжение логическим сигналом. Более рационально для этого использовать логический сигнал, который также управляет соответствующим состоянием программирования ячейки памяти. За счет исполнения переходного транзистора как переходного транзистора с каналом типа р при этом устраняется необходимость в дорогом для изготовления инверторе для управления выводом переходного затвора, так как переходный транзистор с каналом типа р тогда заперт, если управляется затвор, и наоборот. В принципе, переходный транзистор с таким инвертором все же так же может выполняться, как переходный транзистор с каналом типа n.

С помощью устройства в соответствии с изобретением полное напряжение программирования может подаваться без потерь и без других особых мероприятий через канал переходного транзистора на выводы запоминающих затворов.

Между прочим, стоит упомянуть о том, что изобретение также может осуществляться посредством запоминающего устройства, в котором запоминающий и избирательный транзисторы выполнены как транзисторы с каналом типа р, если переходной транзистор в данном случае выполняется как транзистор с каналом типа n. Такое устройство все же скорее является неупотребительным, тем не менее может привносить с собой преимущества, когда желательна так называемая "дырочная проводимость" для передачи носителей заряда.

В усовершенствовании изобретения управляющая схема имеет разгрузочный транзистор с каналом типа n, который имеет вывод разгрузочного затвора, а также первый и второй разгрузочные канальные выводы, причем первый разгрузочный канальный вывод соединяется с выводом запоминающего затвора, причем второй разгрузочный канальный вывод соединен с массой и причем вывод разгрузочного затвора соединяется с той управляющей шиной, через которую управляется переходной транзистор.

Такой разгрузочный транзистор во время программирования ячейки памяти обеспечивает, что вывод запоминающего затвора при процессе программирования находится при определенном потенциале, в частности при потенциале массы. Как раз при запертом переходном транзисторе за счет этого гарантируется, что вывод запоминающего затвора определенно находится при потенциале 0 В.

Полупроводниковое запоминающее устройство в соответствии с изобретением организовано в строки и столбцы, причем в пределах строк выводы избирательных затворов и выводы запоминающих затворов нескольких ячеек памяти включены параллельно и причем в пределах столбцов первые запоминающие канальные выводы или же вторые избирательные канальные выводы включены параллельно. Таким образом, запоминающее устройство в соответствии с изобретением может особенно просто компоноваться в строки и столбцы.

При этом предусмотрен, по крайней мере, один столбец, схема управления которого имеет включенный неправильно в соответствии с изобретением переходный транзистор. Схема управления дополнительно может иметь по одному транзистору выбора блока с каналом типа р с выводом затвора выбора блока, а также с двумя канальными выводами выбора блока, причем первый канальный вывод выбора блока соединяется с ведущей к ячейке памяти горизонтальной шиной и причем второй канальный вывод выбора блока соединяется с первым переходным канальным выводом. За счет этого полупроводниковое запоминающее устройство для программирования ячеек памяти может подразделяться на отдельные блоки, что особенно предпочтительно, так как благодаря этому больше нет необходимости программировать определенные состояния для всей строки полупроводникового запоминающего устройства, а только лишь для выбранного из этой строки блока. За счет этого, в частности, также возможно стирать отдельный блок. Для этого предусмотрена управляющая шина выбора блока, которая соединяется с выводами затворов выбора блока таким образом, что транзисторы выбора блоков могут управляться через управляющую шину выбора блоков.

Изобретение также касается вообще схемы управления для управления, по крайней мере, одной ячейкой памяти с включенным неправильно, как указанно выше, переходным транзистором.

Изобретение ниже подробнее описано со ссылкой на чертежи посредством двух примеров исполнения.

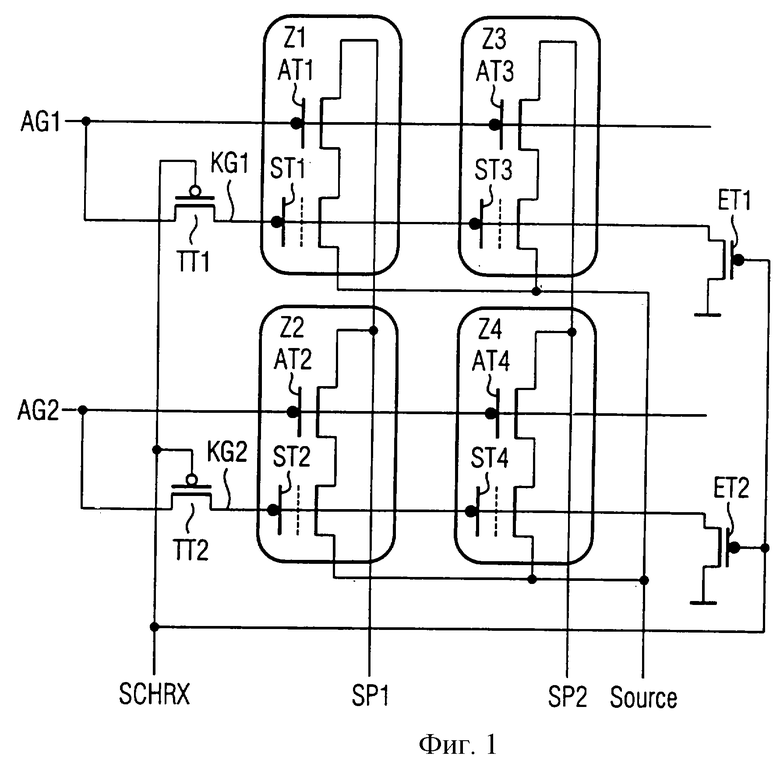

Фиг. 1 показывает принципиальную схему первого полупроводникового запоминающего устройства в соответствии с изобретением.

Фиг. 2 показывает принципиальную схему второго полупроводникового запоминающего устройства в соответствии с изобретением.

На фиг.1 показана принципиальная схема первого полупроводникового запоминающего устройства в соответствии с изобретением, которое выполнено на одной полупроводниковой подложке. На фиг.1 представлена только подобласть полупроводникового запоминающего устройства, которое имеет четыре ячейки памяти Z1, Z2, Z3 и Z4. Ячейки памяти Z1, Z2, Z3 и Z4 могут управляться по двум горизонтальным шинам AG1, AG2 и по двум вертикальным шинам SP1, SP2.

Для управления ячейками памяти Z1, Z2, Z3 и Z4 служит схема управления, которая имеет переходный транзистор ТТ1, разгрузочный транзистор ЕТ1, переходный транзистор ТТ2, а также разгрузочный транзистор ЕТ2, которые управляются через сигнальную шину записи SCHRX. На сигнальную шину записи SCHRX подается измененный на высокое напряжение сигнал, который сгенерирован из логического сигнала, управляющего процессом записи.

Переходный транзистор ТТ1 и переходный транзистор ТТ2 изготовлены как транзисторы с каналом типа р по технологии полевых транзисторов, тогда как разгрузочный транзистор ЕТ1 и разгрузочный транзистор ЕТ2 выполнены как транзисторы с каналом типа n по технологии полевых транзисторов.

Ячейка памяти Z1 имеет избирательный транзистор АТ1 и запоминающий транзистор ST1. Избирательный транзистор АТ1 изготовлен как обычный транзистор с каналом типа n по технологии полевых транзисторов, в то время как запоминающий транзистор ST1 выполнен как транзистор с каналом типа n с так называемым "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ1 соединяется с вертикальной шиной SP1, в то время как второй избирательный канальный выход избирательного транзистора АТ1 соединен с первым запоминающим канальным выводом запоминающего транзистора ST1. Второй запоминающий канальный вывод запоминающего транзистора ST1 соединен с общей шиной истоков SOURCE.

Вывод избирательного затвора избирательного транзистора АТ1 соединяется с горизонтальной шиной AG1. Также второй переходный канальный вывод переходного транзистора ТТ1 соединен с горизонтальной шиной AG1. Первый переходный канальный вывод переходного транзистора ТТ1 соединен с выводом запоминающего затвора KG1 запоминающего транзистора ST1. Принадлежащий выводу запоминающего затвора KG1 затвор запоминающего транзистора ST1 при этом выполнен как так называемый "плавающий затвор".

Вывод переходного затвора переходного транзистора ТТ1 соединен с сигнальной шиной записи SCHRX. Вывод разгрузочного затвора разгрузочного транзистора ЕТ1 также соединен с сигнальной шиной записи SCHRX. Первый разгрузочный канальный вывод разгрузочного транзистора ЕТ1 соединен с запоминающим выводом затвора KG1, в то время как второй разгрузочный канальный вывод разгрузочного транзистора ЕТ1 непосредственно заведен на массу.

Ячейка памяти Z3 относительно горизонтальной шины AG1 включена параллельно к ячейке памяти Z1. Ячейка памяти Z3 имеет к тому же избирательный транзистор АТ3, который выполнен по обычной технологии полевых транзисторов как транзистор с каналом типа n, а также запоминающий транзистор ST3, который выполнен как транзистор с каналом типа п с "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТЗ соединяется с вертикальной шиной SP2, в то время как второй избирательный канальный вывод избирательного транзистора АТЗ соединяется с первым запоминающим канальным выводом запоминающего транзистора ST3. Второй канальный вывод запоминающего устройства запоминающего транзистора ST3 соединен с общей шиной истоков SOURCE. Вывод избирательного затвора избирательного транзистора АТ3 включен параллельно выводу избирательного затвора избирательного транзистора АТ1 и соединен с горизонтальной шиной AG1.

Вывод запоминающего затвора запоминающего транзистора ST3 включен параллельно выводу запоминающего затвора запоминающего транзистора ST1 и соединяется со вторым переходным канальным выводом переходного транзистора ТТ1. Вследствие этого вывод запоминающего затвора запоминающего транзистора ST3 также соединяется с первым разгрузочным канальным выводом разгрузочного транзистора ЕТ1.

Ячейка памяти Z2 имеет избирательный транзистор АТ2 и запоминающий транзистор ST2. Избирательный транзистор АТ2 изготовлен как обычный транзистор с каналом типа n по технологии полевых транзисторов, в то время как запоминающий транзистор ST2 выполнен как транзистор с каналом типа n с так называемым "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ2 соединяется с вертикальной шиной SP2, в то время как второй избирательный канальный вывод избирательного транзистора АТ2 соединен с первым запоминающим канальным выводом запоминающего транзистора ST2. Второй запоминающий канальный вывод запоминающего транзистора ST2 соединен с общей шиной истоков SOURCE.

Вывод избирательного затвора избирательного транзистора АТ2 соединяется с горизонтальной шиной AG2. Также второй переходный канальный вывод переходного транзистора ТТ2 соединен с горизонтальной шиной AG2. Первый переходной канальный вывод переходного транзистора ТТ2 соединен с выводом запоминающего затвора KG2 запоминающего транзистора ST2. Принадлежащий к выводу запоминающего затвора KG2 затвор запоминающего транзистора ST2 при этом выполнен как так называемый "плавающий затвор".

Вывод переходного затвора переходного транзистора ТТ2 и вывод разгрузочного затвора разгрузочного транзистора ЕТ2 соединены с сигнальной шиной записи SCHRX. Первый разгрузочный канальный вывод соединен с выводом запоминающего затвора KG2, в то время как второй разгрузочный канальный вывод непосредственно заведен на массу. Ячейка памяти Z4 относительно горизонтальной шины AG2 включена параллельно ячейке памяти Z2. Ячейка памяти Z4 имеет, к тому же, избирательный транзистор АТ4, который выполнен по обычной технологии полевых транзисторов как транзистор с каналом типа n, а также запоминающий транзистор ST4, который выполнен как транзистор с каналом типа n с "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ4 соединяется с вертикальной шиной SP2, в то время как второй избирательный канальный вывод избирательного транзистора АТ4 соединяется с первым запоминающим канальным выводом запоминающего транзистора ST4. Второй запоминающий канальный вывод запоминающего транзистора ST4 соединен с общей шиной истоков SOURCE. Вывод избирательного затвора избирательного транзистора АТ4 включен параллельно выводу избирательного затвора избирательного транзистора АТ2 и соединен с горизонтальной шиной AG2. Вывод запоминающего затвора запоминающего транзистора ST4 включен параллельно выводу запоминающего затвора запоминающего транзистора ST2 и соединяется со вторым переходным канальным выводом переходного транзистора ТТ2. Вследствие этого вывод запоминающего затвора запоминающего транзистора ST4 также соединяется с первым разгрузочным канальным выводом разгрузочного транзистора ЕТ2.

Относительно вертикальной шины SP1 ячейки памяти Z1, Z2 включены параллельно, в то время как ячейки памяти Z3, Z4 относительно вертикальной шины SP2 включены параллельно.

Ниже поясняются три состояния: "стирание", "запись" и "чтение", для ячейки памяти Z1. При этом в состоянии "стирание" не подается сигнал на вертикальную шину SP1, так как он для этого не является необходимым. Только при записи и при считывании содержимого ячейки памяти Z1 вертикальная шина SP1 нагружается сигналом. Это не представлено подробнее, так как не имеет связанного с сутью изобретения значения.

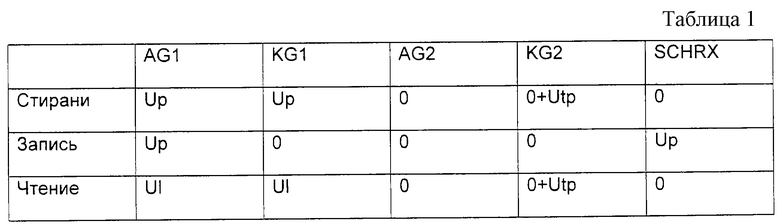

В таблице 1 представлены состояния горизонтальных шин AG1, AG2, выводов запоминающих затворов KG1, KG2 и сигнальной шины записи SCHRX для отдельных функциональных режимов.

При этом напряжение "Up" обозначает напряжение программирования (например, 18 В), напряжение "UI" обозначает напряжение считывания и напряжение "Upt" обозначает положительное абсолютное значение порогового напряжения транзистора с каналом типа р (около 1 В).

Как наглядно видно из таблицы, при стирании строки запоминающего устройства, в которой находится ячейка памяти Z1, на горизонтальную шину AG1 подается напряжение программирования Up. За счет этого первый переходный канальный вывод переходного транзистора ТТ1 также находится при уровне напряжения программирования Up. К сигнальной шине записи SCHRX прикладывается напряжение 0 В, так что переходный транзистор ТТ1 находится в проводящем состоянии, так как он выполнен как транзистор с каналом типа р. В противоположность этому разгрузочный транзистор ЕТ1 выполнен как транзистор с каналом n, так что поступающий на вывод разгрузочного затвора разгрузочного транзистора ЕТ1 сигнал 0 В сигнальной шины записи SCHRX переводит его в запертое состояние. Вследствие этого на вывод запоминающего затвора KG1 поступает напряжение программирования Up, что заставляет "плавающий затвор" запоминающего транзистора ST1 перейти в "стертое" состояние.

Ячейка памяти Z2 остается независимой от процессов на горизонтальной шине AG1, а также на сигнальной шине записи SCHRX, когда вывод запоминающего затвора KG2 постоянно находится в соответствии с потенциалом горизонтальной шины AG2 в определенном состоянии при 0 В+Utp.

Так как ячейки памяти Z3 и Z4 относительно горизонтальных шин AG1, AG2 включены параллельно ячейкам памяти Z1 и Z2, они ведут себя согласно этим ячейками памяти Z1 и Z2. Отсюда в режиме "стирание" стираются все те ячейки памяти, которые опрашиваются горизонтальной шиной AG1.

Стирание ячейки памяти Z2 и ячейки памяти Z4 происходит соответственно стиранию ячеек памяти Z1 и Z3.

При записи значения в ячейку памяти Z1 горизонтальная шина AG1 и сигнальная шина записи SCHRX нагружаются значением Up. На основании состояния сигнальной шины записи SCHRX разгрузочный транзистор ЕТ1 с каналом типа n проводит, в то время как переходный транзистор ТТ1 с каналом типа р заперт. За счет этого на вывод запоминающего затвора KG1 подается потенциал массы, а именно 0 В. За счет подачи надлежащего сигнала на вертикальную шину SP1 записывается запоминающий транзистор ST1, так как избирательный транзистор АТ1 на основе приложенного к выводу избирательного затвора сигнала Up находится в проводящем состоянии.

При этом следует заметить, что ячейка памяти Z2 остается независимой от процессов в ячейке памяти Z1, так как вывод запоминающего затвора KG2 постоянно в соответствии с потенциалом подключенной через разгрузочный транзистор ЕТ2 массы сохраняет определенное значение 0 В.

При считывании значения из ячейки памяти Z1 на горизонтальную шину AG1 подается значение UI, в то время как сигнальная шина записи SCHRX нагружается сигналом 0. За счет этого вывод запоминающего затвора KG1 находится определенно при потенциале UI, в то время как избирательный транзистор АТ1 находится в проводящем состоянии. За счет подачи надлежащего напряжения на вертикальную шину SP1 тогда может считываться состояние запоминающего транзистора ST1.

За счет подачи надлежащего напряжения на вертикальную шину SP2 в этом функциональном режиме может считываться запомненное состояние запоминающего транзистора ST3 ячейки памяти Z3, так как избирательный транзистор АТЗ также находится в проводящем состоянии. Ячейки памяти Z2 и Z4 остаются независимыми от состояния ячеек памяти Z1 и Z3, когда вывод запоминающего затвора KG2 постоянно находится в определенном состоянии при 0 В+Utp, так как вывод запоминающего затвора KG2 постоянно в соответствии с потенциалом подключенной через разгрузочный транзистор массы сохраняет определенное значение 0 В+Dtp.

Вертикальные шины SP1 и SP2, как при записи, так и при чтении, шунтируются соответствующими стандартными значениями.

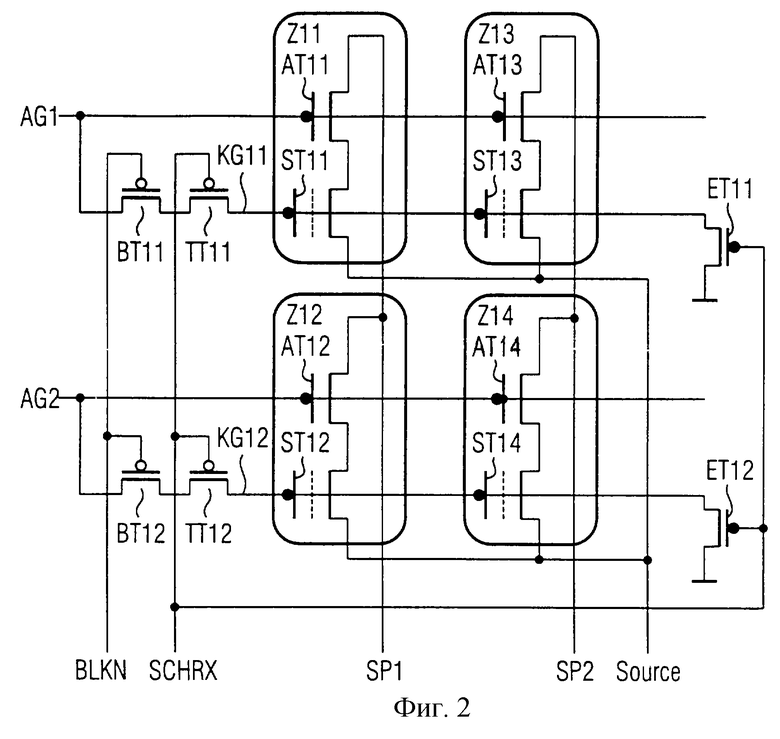

На фиг.2 показана принципиальная схема другого полупроводникового запоминающего устройства в соответствии с изобретением, которое выполнено на одной полупроводниковой подложке. На фиг.2 представлена только подобласть полупроводникового запоминающего устройства, которое имеет четыре ячейки памяти Z11, Z12, Z13 и Z14. Ячейки памяти Z11, Z12, Z13 и Z14 могут управляться по двум горизонтальным шинам AG1, AG2 и по двум вертикальным шинам SP1, SP2.

Для управления ячейками памяти Z11, Z12, Z13 и Z14 служит схема управления, которая имеет переходный транзистор ТТ11, разгрузочный транзистор ET11, переходный транзистор ТТ12, а также разгрузочный транзистор ЕТ12, которые управляются через сигнальную шину записи SCHRX. На сигнальную шину записи SCHRX поступает измененный на высокое напряжение сигнал, который сгенерирован из логического сигнала, управляющего процессом записи. Схема управления включает в себя далее транзистор выбора блока ВТ11, а также транзистор выбора блока ВТ12. Вывод затвора выбора блока транзистора выбора блока ВТ11, а также вывод затвора выбора блока транзистора выбора блока ВТ12 соединены с сигнальной шиной выбора блока BLKN. На сигнальную шину выбора блока BLKN поступает измененный на высокое напряжение сигнал, который сгенерирован из другого логического сигнала, управляющего поблочным процессом программирования.

Вставка

Переходные транзисторы ТТ11 и ТТ12 и транзисторы выбора блока ВТ11 и ВТ12 изготовлены как обычные транзисторы с каналом типа р по технологии полевых транзисторов.

Ячейка памяти Z11 имеет избирательный транзистор АТ11 и запоминающий транзистор ST11. Избирательный транзистор АТ11 изготовлен как обычный транзистор с каналом типа n по технологии полевых транзисторов, в то время как запоминающий транзистор ST11 выполнен как транзистор с каналом типа n с так называемым "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ11 соединяется с вертикальной шиной SP1, в то время как второй избирательный канальный вывод избирательного транзистора AT11 соединен с первым запоминающим канальным выводом запоминающего транзистора ST11. Второй запоминающий канальный вывод запоминающего транзистора ST11 соединен с общей шиной истоков SOURCE.

Вывод избирательного затвора избирательного транзистора AT11 соединяется с горизонтальной шиной AG1. Также второй канальный вывод выбора блока транзистора выбора блока ВТ11 соединен с горизонтальной шиной AG1. Второй переходный канальный вывод переходного транзистора ТТ11 соединен с первым канальным выводом выбора блока транзистора выбора блока ВТ11 и первый переходный канальный вывод первого переходного транзистора ТТ11 соединен с выводом запоминающего затвора KG11 запоминающего транзистора ST11. Принадлежащий к выводу запоминающего затвора KG11 затвор запоминающего транзистора ST11 при этом выполнен как так называемый "плавающий затвор". Вывод переходного затвора переходного транзистора ТТ11 соединен с сигнальной шиной записи SCHRX.

Вывод разгрузочного затвора разгрузочного транзистора ЕТ11 соединен с сигнальной шиной записи SCHRX. Первый разгрузочный канальный вывод соединен с выводом запоминающего затвора KG11, в то время как второй разгрузочный канальный вывод непосредственно заведен на массу.

Ячейка памяти Z13 относительно горизонтальной шины AG1 включена параллельно ячейке памяти Z11. Ячейка памяти Z13 имеет к тому же избирательный транзистор АТ13, который выполнен по обычной технологии полевых транзисторов как транзистор с каналом типа n, а также запоминающий транзистор ST13, который выполнен как транзистор с каналом типа n с "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ13 соединяется с вертикальной шиной SP2, в то время как второй избирательный канальный вывод избирательного транзистора АТ13 соединяется с первым запоминающим канальным выводом запоминающего транзистора ST13. Второй запоминающий канальный вывод запоминающего транзистора ST13 соединен с общей шиной истоков SOURCE. Вывод избирательного затвора избирательного транзистора AT 13 включен параллельно выводу избирательного затвора избирательного транзистора АТ11 и соединен с горизонтальной шиной AG1. Вывод запоминающего затвора запоминающего транзистора ST13 включен параллельно выводу запоминающего затвора запоминающего транзистора ST11 и соединяется со вторым переходным канальным выводом переходного транзистора ТТ11. Вследствие этого вывод запоминающего затвора запоминающего транзистора ST13 также соединяется с первым разгрузочным канальным выводом разгрузочного транзистора ЕТ11.

Ячейка памяти Z12 имеет избирательный транзистор АТ12 и запоминающий транзистор ST12. Избирательный транзистор АТ12 изготовлен как обычный транзистор с каналом типа n по технологии полевых транзисторов, в то время как запоминающий транзистор ST12 выполнен как транзистор с каналом типа n с так называемым "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ12 соединяется с вертикальной шиной SP2, в то время как второй избирательный канальный вывод избирательного транзистора АТ12 соединен с первым запоминающим канальным выводом запоминающего транзистора ST12. Второй запоминающий канальный вывод запоминающего транзистора ST12 соединен с общей шиной истоков SOURCE.

Вывод избирательного затвора избирательного транзистора АТ12 соединяется с горизонтальной шиной AG12. Также второй канальный вывод выбора блока транзистора выбора блока ВТ12 соединен с горизонтальной шиной AG2. Второй переходный канальный вывод переходного транзистора ТТ12 соединен с первым канальным выводом выбора блока транзистора выбора блока ВТ12 и первый переходный канальный вывод переходного транзистора ТТ12 соединен с выводом запоминающего затвора KG12 запоминающего транзистора ST12. Принадлежащий к выводу запоминающего затвора KG12 затвор запоминающего транзистора ST12 при этом выполнен как так называемый "плавающий затвор".

Вывод переходного затвора переходного транзистора ТТ12 соединен с сигнальной шиной записи SCHRX. Вывод затвора выбора блока транзистора выбора блока ВТ12 соединен с сигнальной шиной выбора блока BLKN.

Вывод разгрузочного затвора разгрузочного транзистора ЕТ12 соединен с сигнальной шиной записи SCHRX. Первый разгрузочный канальный вывод соединен с выводом запоминающего затвора KG12, в то время как второй разгрузочный канальный вывод непосредственно заведен на массу.

Ячейка памяти Z14 относительно горизонтальной шины AG2 включена параллельно ячейке памяти Z12. Ячейка памяти Z14 имеет к тому же избирательный транзистор АТ14, который выполнен по технологии полевых транзисторов как транзистор с каналом типа n, а также запоминающий транзистор ST14, который выполнен как транзистор с каналом типа n с "плавающим затвором". Первый избирательный канальный вывод избирательного транзистора АТ14 соединяется с вертикальной шиной SP2, в то время как второй избирательный канальный вывод избирательного транзистора АТ14 соединяется с первым запоминающим канальным выводом запоминающего транзистора ST14. Второй запоминающий канальный вывод запоминающего транзистора ST14 соединен с общей шиной истоков SOURCE. Вывод избирательного затвора избирательного транзистора АТ14 включен параллельно выводу избирательного затвора избирательного транзистора АТ12 и соединен с горизонтальной шиной AG2. Вывод запоминающего затвора запоминающего транзистора ST14 включен параллельно выводу запоминающего затвора запоминающего транзистора ST12 и соединяется со вторым переходным канальным выводом переходного транзистора ТТ12. Вследствие этого вывод запоминающего затвора запоминающего транзистора ST14 также соединяется с первым разгрузочным канальным выводом разгрузочного транзистора ЕТ12.

Относительно вертикальной шины SP1 ячейки памяти Z11, Z12 включены параллельно, в то время как ячейки памяти Z13, Z14 включены параллельно относительно вертикальной шины SP2.

Ниже объясняются три состояния "стирание", "запись" и "чтение" для ячейки памяти Z11. При этом в состоянии "стирание" не подается сигнал на вертикальную шину SP1, так как он для этого не является необходимым. Только при записи и при считывании содержимого ячейки памяти Z11 вертикальная шина SP1 нагружается сигналом. Это все же здесь не представлено подробнее, так как не имеет значения, затрагивающего суть изобретения.

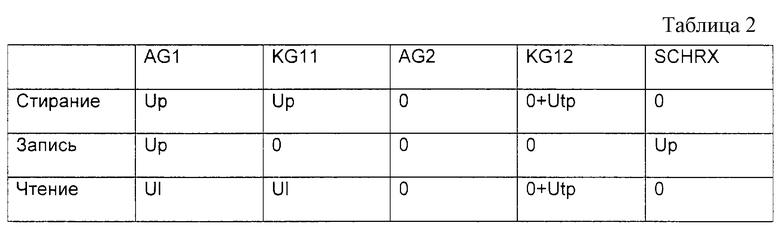

В таблице 2 представлены состояния горизонтальных шин AG1, AG2, выводов запоминающих затворов KG11, KG12 и сигнальной шины записи SCHRX для отдельных функциональных режимов.

Сигнал выбора блока BLKN в соответствии с тем, выбран ли блок полупроводникового запоминающего устройства, в котором находятся ячейки памяти Z1-Z4, или нет, принимает напряжения 0 В ("выбран") или же Up ("не выбран").

При этом напряжение "Up" обозначает напряжение программирования (например, 18 В), напряжение "UI" обозначает напряжение считывания и напряжение "Upt" обозначает положительное абсолютное значение порогового напряжения транзистора с каналом типа р (около 1 В).

Для последующего описания принципа действия полупроводникового запоминающего устройства принимается, что сигнал BLKN постоянно находится при 0 В, так что каналы транзисторов выбора блоков находятся в проводящем состоянии и сигналы на горизонтальных шинах передаются дальше на каналы переходных транзисторов ТТ11 и ТТ12.

Как наглядно видно из таблицы, при стирании строки запоминающего устройства, в которой находится ячейка памяти Z11, на горизонтальную шину AG1 подается напряжение программирования Up. За счет этого первый переходный канальный вывод переходного транзистора ТТ11 также находится на уровне напряжения программирования Up. На сигнальную шину записи SCHRX подается напряжение 0 В, так что переходный транзистор ТТ11 находится в проводящем состоянии, так как он выполнен как транзистор с каналом типа р. В противоположность этому разгрузочный транзистор ЕТ11 выполнен как транзистор с каналом n, так что поступающий на вывод разгрузочного затвора разгрузочного транзистора ЕТ11 сигнал 0 В сигнальной шины записи SCHRX переводит его в запертое состояние. Вследствие этого на вывод запоминающего затвора KG1 поступает напряжение программирования Up, что заставляет "плавающий затвор" запоминающего транзистора ST11 перейти в "стертое" состояние.

Ячейка памяти Z12 остается независимой от процессов на горизонтальной шине AG1, а также на сигнальной шине записи SCHRX, когда вывод запоминающего затвора KG 12 постоянно в соответствии с потенциалом горизонтальной шины AG2 находится в определенном состоянии при 0 В+Utp.

Так как ячейки памяти Z13 и Z14 относительно горизонтальных шин AG1, AG2 включены параллельно ячейкам памяти Z11 и Z12, они ведут себя соответственно этим ячейкам памяти Z11 и Z12. Отсюда при режиме "стирание" стираются все те ячейки памяти, которые опрашиваются горизонтальной шиной AG1.

Стирание ячейки памяти Z12 и ячейки памяти Z14 происходит соответственно стиранию ячеек памяти Z11 и Z13. При записи значения в ячейку памяти Z11 горизонтальная шина AG1 и сигнальная шина записи SCHRX нагружаются значением Up. На основании состояния сигнальной шины записи SCHRX разгрузочный транзистор ЕТ11 с каналом типа n проводит, в то время как переходный транзистор ТТ11 с каналом типа р заперт. За счет этого на вывод запоминающего затвора KG11 подается потенциал массы, а именно 0 В. За счет подачи надлежащего сигнала на вертикальную шину SP1 записывается запоминающий транзистор ST11, так как избирательный транзистор АТ11 на основе приложенного к выводу избирательного затвора сигнала Up находится в проводящем состоянии. При этом следует заметить, что ячейка памяти Z12 остается независимой от процессов в ячейке памяти Z11, так как вывод запоминающего затвора KG 12 постоянно в соответствии с потенциалом подключенной через разгрузочный транзистор ЕТ12 массы сохраняет определенное значение 0 В. При считывании значения из ячейки памяти Z11 на горизонтальную шину AG1 подается значение UI, в то время как сигнальная шина записи SCHRX нагружается сигналом 0. За счет этого вывод запоминающего затвора KG11 находится определенно при потенциале UI, в то время как избирательный транзистор АТ11 находится в проводящем состоянии. За счет подачи надлежащего напряжения на вертикальную шину SP1 в этом случае может считываться состояние запоминающего транзистора ST11. За счет подачи подходящего напряжения на вертикальную шину SP2 в этом функциональном режиме может считываться запомненное состояние запоминающего транзистора ST13 ячейки памяти Z13, так как избирательный транзистор АТ13 также находится в проводящем состоянии. Ячейки памяти Z12 и Z14 остаются независимыми от состояния ячеек памяти Z11 и Z13, когда вывод запоминающего затвора KG12 постоянно находится в определенном состоянии при 0 В + Dtp, а именно на основании подключенной через разгрузочный транзистор массы. Вертикальные шины SP1 и SP2 шунтируются как при записи, так и при чтении соответствующими стандартными значениями.

Изобретение относится к полупроводниковому запоминающему устройству. Техническим результатом является безошибочное программирование полупроводникового запоминающего устройства. Устройство содержит, по меньшей мере, одну ячейку помяти, включающую избирательный транзистор с каналом типа n, запоминающий транзистор с каналом типа n, переходной транзистор с каналом типа р, вертикальные и горизонтальные шины. 5 з.п.ф-лы, 2 ил., 2 табл.

| ЮТСКЛ [ | 0 |

|

SU317443A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ИМ | 1979 |

|

RU1110315C |

| Стенд для испытания гибких зубчатых колес волновых передач | 1978 |

|

SU750313A1 |

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1405575A1 |

Авторы

Даты

2003-09-27—Публикация

1998-07-14—Подача