Изобретение относится к радиотехнике и может найти применение в системах связи с псевдослучайной перестройкой рабочей частоты.

Известны устройства поиска по задержке сигналов с псевдослучайной перестройкой рабочей частота, описанное а монографии Р.К.Диксона "Широкополосные системы". Москва, Связь, 1979 г., стр.191-192, рис.6.9, а также в монографии В.И. Борисова и др. "Помехозащищенность систем радиосвязи с расширением спектра сигналов методом псевдослучайной перестройки рабочей частоты", Москва, "Радио и связь", 2000г., стр. 229, рис. 6.12, недостатком которых является большое время поиска.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в монографии Г.И.Тузова "Статистическая теория приема сложных сигналов", Москва, "Сов. радио", 1977 г., стр.326, рис.7.2в.

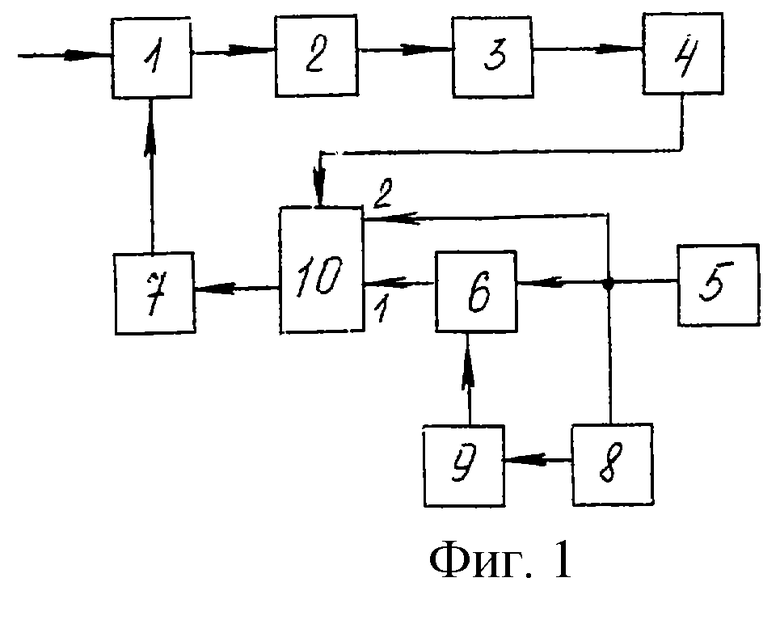

Структурная схема устройства-прототипа представлена на фиг.1, где обозначено:

1 - перемножитель (смеситель);

2 - полосовой фильтр;

3 - амплитудный детектор;

4 - блок сравнения с порогом;

5 - генератор тактовых частот;

6 - блок режекции тактовых импульсов;

7 - перестраиваемый синтезатор частот (генератор кода);

8 - счетчик;

9 - блок управления;

10 - коммутатор.

Устройство-прототип имеет следующие функциональные связи: последовательно соединенные перемножитель 1, первый сигнальный вход которого является входом устройства, полосовой фильтр 2, амплитудный детектор 3 и блок сравнения с порогом 4, выход которого соединен с третьим управляющим входом коммутатора 10; последовательно соединенные генератор тактовых частот 5, блок режекции тактовых импульсов 6, коммутатор 10 и перестраиваемый синтезатор частот (генератор кода) 7, выход которого соединен с вторым опорным входом перемножителя 1; кроме того, выход генератора тактовых частот 5 соединен с вторым сигнальным входом коммутатора 10 и с последовательно соединенными счетчиком 8 и блоком управления 9, выход которого соединен с вторым входом блока режекции тактовых импульсов 6.

Устройство-прототип работает следующим образом.

В блоке 5 формируются тактовые импульсы, поступающие на блоки 6, 8, 10. После заполнения емкости счетчика 8 он формирует команду, которая подается на блок 9. По этой команде блок 9 совместно с блоком 6 либо режектирует (бланкирует) заданное число тактовых импульсов, формируемых блоком 5 и поступающих на блок 7 через блок 10. За счет этого обеспечивается изменение задержки опорного сигнала, формируемого блоком 7, по отношению к входному сигналу.

Результат перемножения входного и опорного сигналов с выхода блока 1 поступает на блок 2, где он фильтруется. Накопленное в блоке 2 напряжение детектируется в блоке 3, выделенная огибающая сравнивается с порогом в блоке 4. В случае превышения порога блок 4 подает команду "1" на блок 10, по этой команде к выходу блока 10 (входу блока 7) подключается выход блока 5, а выход блока 6 отключается от первого входа блока 10. В этом случае на блок 7 поступают тактовые импульсы непосредственно от блока 5, на этом режим поиска по задержке завершается и, начиная с этого момента, опорный сигнал находится в синхронизме с входным сигналом.

Недостатком прототипа является большое время поиска по задержке.

Для устранения указанного недостатка в устройство поиска по задержке сигналов с псевдослучайной перестройкой рабочей частоты в устройство, содержащее последовательно соединенные перемножитель, первый сигнальный вход которого является входом устройства, и полосовой фильтр, а также амплитудный детектор, блок сравнения с порогом, генератор тактовой частоты и перестраиваемый синтезатор частот, выход которого соединен с вторым, опорным входом перемножителя, введены последовательно соединенные первый коммутатор, первый сигнальный вход которого соединен с выходом полосового фильтра, и ограничитель, выход которого соединен с входом амплитудного детектора. Введены накопитель и последовательно соединенные делитель тактовой частоты и второй коммутатор, первый сигнальный вход которого соединен с выходом генератора тактовой частоты и с входом делителя тактовой частоты. При этом выход амплитудного детектора через накопитель соединен с входом блока сравнения с порогом, выход которого соединен с вторыми управляющими входами первого и второго коммутаторов. Кроме того, выход второго коммутатора соединен с входом перестраиваемого синтезатора частот, а второй сигнальный выход первого коммутатора является выходом устройства.

Структурная схема предлагаемого устройства приведена на фиг.2, где обозначено:

1 - перемножитель (смеситель);

2 - полосовой фильтр;

3 - первый коммутатор;

4 - ограничитель;

5 - амплитудный детектор;

6 - накопитель;

7 - блок сравнение с порогом;

8 - второй коммутатор;

9 - перестраиваемый синтезатор частот;

10 - генератор тактовой частоты;

11 - делитель тактовой частоты.

Заявляемое устройство имеет следующие функциональные связи: последовательно соединенные перемножитель 1, первый сигнальный вход которого является входом устройства, полосовой фильтр 2, первый коммутатор 3, ограничитель 4, амплитудный детектор 5, накопитель 6, блок сравнения с порогом 7, выход которого соединен с вторыми управляющими входами первого коммутатора 3 и второго коммутатора 8, первый, сигнальный вход которого соединен с выходом генератора тактовой частоты 10 и с входом делителя тактовой частоты 11, выход которого соединен с третьим сигнальным входом второго коммутатора 8, выход которого через перестраиваемый синтезатор частот 9 соединен с вторым опорным входом перемножителя 1; кроме того, второй сигнальный выход первого коммутатора 3 является выходом устройства.

Устройство, представленное на фиг.2, работает следующим образом.

На сигнальный вход блока I, являющийся входом устройства, поступает сигнал с программной перестройкой рабочей частоты, представляющий собой периодическую последовательность из N радиоимпульсов длительностью τ0, частоты заполнения которых меняются в соответствии с заданной программой перестройки (кодом). На второй опорный вход блока I подается опорный сигнал с псевдослучайной перестройкой рабочей частоты, отличающийся от входного сигнала сдвигом всех частот программы перестройки на величину fпр, равную промежуточной частоте приемника.

В исходном режиме работы, когда устройство не вошло в синхронизм с входным сигналом, на выходе блока 7 формируется команда "0". По этой команде, поступающей на вторые, управляющие входы блоков 3 и 8, выход блока 2 через блок 3 соединяется с входом блока 4, а к входу блока 9 через блок 8 подключается выход блока 11, в результате чего на блок 9 подаются тактовые импульсы от блока 11, частота которых fт1 в (N+1) раз ниже тактовой частоты fт0, формируемой блоком 10, что достигается за счет деления тактовой частоты блока 10 в (N+1) раз в блоке 11.

За счет подачи на блок 9 тактовой частоты  fт0=fт, где fт - тактовая частота, используемая при формировании входного сигнала, в устройстве осуществляется режим поиска по задержке, при котором блок 9 стоит на каждой из N частот программы перестройки в течение времени τ1 = (N+1)τ0. За время τ1 входной сигнал успевает перестроиться по всем N частотам программы его перестройки, поэтому на выходе блока 1 в результате перемножения входного и опорного сигналов на каждом из N временных интервалов длительностью τ1 обязательно выделяется импульс совпадения длительностью τ0, занимающий одинаковое временное положение

fт0=fт, где fт - тактовая частота, используемая при формировании входного сигнала, в устройстве осуществляется режим поиска по задержке, при котором блок 9 стоит на каждой из N частот программы перестройки в течение времени τ1 = (N+1)τ0. За время τ1 входной сигнал успевает перестроиться по всем N частотам программы его перестройки, поэтому на выходе блока 1 в результате перемножения входного и опорного сигналов на каждом из N временных интервалов длительностью τ1 обязательно выделяется импульс совпадения длительностью τ0, занимающий одинаковое временное положение  относительно момента смены частоты. Значение θi(θ1 = θ2...θi...θN) определяется взаимной задержкой (фазой) входного и опорного сигналов.

относительно момента смены частоты. Значение θi(θ1 = θ2...θi...θN) определяется взаимной задержкой (фазой) входного и опорного сигналов.

Временной интервал между импульсами сигнала, выделяемыми на выходе блока 1 на соседних частотах, равен τ1 = (N+1)τ0, а временное положение импульса сигнала на интервале τ1 относительно смены (скачка) частоты несет информацию о начальной фазе (задержке) входного сигнала относительно опорного.

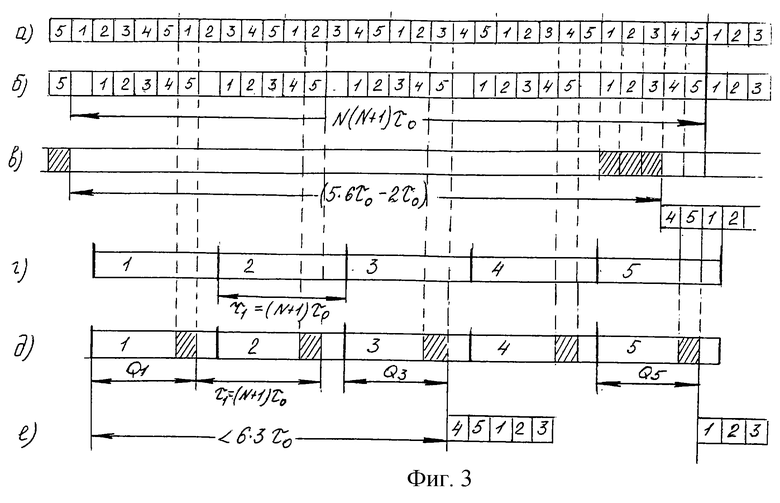

Сказанное поясняется на фиг.3, где на фиг.3а представлен входной сигнал с псевдослучайной перестройкой рабочей частоты, при этом цифрами обозначены порядковые номера частот в программе перестройки входного сигнала. С целью наглядности на фиг.3 принято N=5.

На фиг. 3г показана программа перестройки опорного сигнала с длительностью стояния на каждой из N частот, равной τ1 = (N+1)τ0, при этом на фиг.3 рассмотрен пример N=5, τ1 = 6τ0.

На фиг.3д показаны импульсы совпадения входного и опорного сигналов, на фиг. 3д, е показано, что временное положение импульса совпадения входного и опорного сигналов на каждой частотной позиции определяет задержку (фазу) входного сигнала относительно опорного. Из фиг.3д также видно, что при длительности опорного сигнала на каждой из N частотных позиций, равной τ1, появляется возможность вхождения в синхронизм с входным сигналом, то есть определения его начальной фазы по результатам накопления М импульсов совпадения входного и опорного сигналов М<<N. Эта возможность определяется тем, что каждый выделенный импульс полезного сигнала на каждом из N временных интервалах Δ несет информацию о фазе входного сигнала.

Указанное свойство обеспечивает возможность сокращения времени поиска сигналов с программной перестройкой частоты за счет накоплении не всех N импульсов программы перестройки, а только части их М<<N.

Результат перемножения входного сигнала, поступающего на первый сигнальный вход блока 1, и опорного сигнала, поступающего на его второй опорный вход, с выхода блока 1 подается на блок 2, где он фильтруется в полосе частот τ1 = (N+1)τ0,F, согласованной с длительностью  С выхода блока 2 напряжение через блок 3 поступает на блок 4, где производится нормирование уровня напряжения за счет ограничения. C выхода блока 4 напряжение подается на блок 5, где за счет амплитудного детектирование выделяются огибающие импульса сигнала, которые накапливаются в блоке 6. Накопленное напряжение сравнивается с порогом в блоке 7. Команда "I", свидетельствующая о превышении порога, подается на вторые управляющие входы блоков 3 и 8.

С выхода блока 2 напряжение через блок 3 поступает на блок 4, где производится нормирование уровня напряжения за счет ограничения. C выхода блока 4 напряжение подается на блок 5, где за счет амплитудного детектирование выделяются огибающие импульса сигнала, которые накапливаются в блоке 6. Накопленное напряжение сравнивается с порогом в блоке 7. Команда "I", свидетельствующая о превышении порога, подается на вторые управляющие входы блоков 3 и 8.

При поступлении этой команды блок 8 отключает от входа блока 9 выход блока 11 и подключает к нему выход блока 10. С этого момента блок 9 переходит от работы с тактовой частоты fт/(N+1) на работу с тактовой частотой fт, равной и синхронной с тактовой частотой, используемой при формировании входного сигнала. Сказанное поясняется на фиг.3е. Одновременно блок 3 отключает выход блока 2 от входа блока 4 и подключает его к выходу устройства. Процедура поиска на этом завершается и приемное устройство, в состав которого входит заявляемое устройство поиска, переходит в режим слежения за задержкой и приема информации.

Структурная схема блока 3 приведена на фиг.4, где обозначено:

31, 32 - первый и второй ключи;

33 - инвертор.

Блок 3 содержит первый ключ 31 и второй ключ 32, объединенные первые сигнальные входы которых являются первым сигнальным входом блока 3, выходы ключей 31 и 32 являются первым и вторым сигнальными выходами блока 3 соответственно. Второй управляющий вход блока 3 соединен с управляющим входом ключа 32 непосредственно, а с управляющим входом ключа 31 - через инвертор 33.

Блок 3 работает следующим образом. При наличии команды "0" на втором управляющем входе блока 3 ключ 32 закрыт, а ключ 31 открыт, так как на его управляющий вход подается команда "I", сформированная из команды "0" за счет ее инверсии в блоке 33. В этом случае первый сигнальный вход блока 3 соединен с его первым сигнальным выходом. При наличии команды "I" на втором управляющем входе блока 3 его первый сигнальный вход через открытый ключ 32 соединяется с вторым, сигнальным выходом блока 3, ключ 31 в этом режиме заперт.

Структурная схема блока 8 приведена на фиг.5, где обозначено:

81, 82 - первый и второй ключи;

83 - инвертор.

Блок 8 содержит первый ключ 81, второй ключ 82, а также инвертор 83, при этом первый сигнальный вход блока 8 соединен с сигнальным входом ключа 81, а третий сигнальный вход блока 8 соединен с сигнальным входом ключа 82, выход которого, объединенный с выходом блока 81, является сигнальным выходом блока 8, второй управляющий вход которого соединен с управляющим входом ключа 82 непосредственно, а с управляющим входом ключа 81 - через инвертор 83.

Блок 8 работает следующим образом.

При наличии команды "0" на втором, управляющем, входе блока 8 ключ 81 открыт, а ключ 82 закрыт, при этом к сигнальному выходу блока 8 подключается его первый, сигнальный, вход. При наличии на втором, управляющем, входе блока 8 команды "I" ключ 81 запирается, а ключ 82 отпирается, при этом к сигнальному выходу блока 8 подсоединяется его третий вход.

Блок 11 является делителем тактовой частоты, формируемой блоком 10, и может быть выполнен в виде счетчика так, как это указано в монографии "Цифровые радиоприемные системы", Справочник под ред. М.И.Жодзишского, Москва, "Радио и связь", 1990г., стр.46, рис.2.8.

Блок 9 может быть выполнен так, как это представлено на фиг.6, где обозначено:

91 - генератор сетки частот;

92 - цифровой коммутатор;

93 - генератор псевдослучайной последовательности.

Блок 9 содержит последовательно соединенные генератор сетки частот 91 и цифровой коммутатор 92, а также генератор псевдослучайной последовательности 93, вход которого объединен с входом блока 91 и является входом блока 9, а выход блока 93 соединен с управляющим входом блока 92, выход которого является выходом блока 9.

Тактовые импульсы, поступающие на вход блока 9, определяют частоту тактов генератора числовой последовательности 93, который может быть выполнен на основе регистра сдвига с обратными связями, состояние которого на каждом такте характеризуется двоичным числом, определяемым всеми триггерами регистра сдвига. Для регистра сдвига, вырабатывающего последовательность максимальной длины, существует N состояний, N=2n-1, где n - число, определяемое разрядностью регистра, что обеспечивает получение чисел от 1 до N. Блок 91 вырабатывает сетку гармонических сигналов.

Все сигналы сетки частот с выходов блока 91 поступают на сигнальные входы блока 92, на управляющий вход которого подается цифровой код с выхода блока 93. Блок 92 ставит в соответствие каждому из N псевдослучайных чисел, формируемых блоком 93, определенный сигнал сетки частот, и только этот сигнал пропускает на выход блока 9 в течение одного такта. При поступлении другого такта на выходе блока 9 появляется другой сигнал сетки частот и т.д.

Длительность пропускания на выход блока 9 каждого из сигналов сетки частот определяет длительность стояния каждой частоты на выходе блока 9.

При использовании устройства-прототипа в режиме поиска по задержке обеспечивается скольжение опорного сигнала относительно входного и периодическое их совпадение.

Время поиска по задержке (Т), определяемое как время, затрачиваемое на совмещение по времени входного и опорного сигналов, для устройства-прототипа зависит от задержки между входным и опорным сигналами.

Как видно из фиг.3б, максимальное время поиска сигналов с перестройкой рабочей частоты при использовании устройства-прототипа (Тпр) составляет: Tпр = N(N+1)τ0; при N=5 Tпр = 5(5+1)τ0 = 30τ0.

Для устройства-прототипа на временном интервале T = N(N+1)τ0 совпадение входного и опорного сигналов наблюдается только на интервале Nτ0. Поэтому стремление сократить время поиска за счет сокращения числа накапливаемых импульсов сигнала М<N для устройства-прототипа неэффективно. Действительно, для устройства-прототипа, как видно на фиг.3в, для максимального значения времени поиска имеем: Tпр = N(N+1)τ0-(N-M), при N=5, М=3 имеем Tпр = 3(5+1)τ0-2τ0 = 28τ0 (1).

В заявляемом устройстве при любом значении задержки между входным и опорным сигналами обеспечивается выделение импульса сигнала длительностью τ0 на каждом из N временных интервалах, длительностью τ1 = (N+1)τ0, соответствующих N частотам опорного сигнала.

При уменьшении числа накапливаемых импульсов сигнала в режиме поиска по задержке при М<N максимальное время поиска для заявляемого устройства в соответствии с фиг.3д определяется соотношением: Tз ≤ M(N+1)τ0, при N=5, М=3, Tз = 3(5+1)τ0 = 18τ0 (2)

Из сравнения (1) и (2) видим Т3≤Тпр.

Таким образом, заявляемое устройство обеспечивает существенное сокращение времени поиска по задержке для сигналов с псевдослучайной перестройкой рабочей частоты по сравнению с прототипом.

Устройство поиска по задержке относится к радиотехнике и может найти применение в системах связи с псевдослучайной перестройкой рабочей частоты. Достигаемый технический результат - существенное сокращение времени поиска сигналов по сравнению с прототипом. Устройство состоит из перемножителя (1), полосового фильтра (2), амплитудного детектора (5), блока сравнения с порогом (7), генератора тактовой частоты (10), перестраиваемого синтезатора частот (9), двух коммутаторов (3, 8), ограничителя (4), накопителя (6), делителя тактовой частоты (11). 6 ил.

Устройство поиска по задержке сигналов с псевдослучайной перестройкой рабочей частоты, содержащее последовательно соединенные перемножитель, первый, сигнальный вход которого является входом устройства, и полосовой фильтр, а также амплитудный детектор, блок сравнения с порогом, генератор тактовой частоты и перестраиваемый синтезатор частот, выход которого соединен с вторым, опорным входом перемножителя, отличающееся тем, что введены последовательно соединенные первый коммутатор, первый, сигнальный вход которого соединен с выходом полосового фильтра, и ограничитель, выход которого соединен с входом амплитудного детектора, введены накопитель и последовательно соединенные делитель тактовой частоты и второй коммутатор, первый, сигнальный вход которого соединен с выходом генератора тактовой частоты и с входом делителя тактовой частоты, при этом выход амплитудного детектора через накопитель соединен с входом блока сравнения с порогом, выход которого соединен с вторыми, управляющими входами первого и второго коммутаторов, кроме того, выход второго коммутатора соединен с входом перестраиваемого синтезатора частот, а второй сигнальный выход первого коммутатора является выходом устройства.

| ТУЗОВ Г.И | |||

| Статистическая теория приема сложных сигналов | |||

| - М.: Советское радио, 1977, с.326, рис.7.2в | |||

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПО ЗАДЕРЖКЕ | 2000 |

|

RU2166230C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПО ЗАДЕРЖКЕ | 1999 |

|

RU2165129C2 |

| US 4627080, 02.12.1986 | |||

| US 4726043, 16.02.1988. | |||

Авторы

Даты

2003-09-10—Публикация

2002-02-27—Подача