Изобретение относится к автоматике и вычислительной технике и может быть использовано в радиотехнических системах связи с шумоподобными сигналами, применяющих цифровые методы формирования больших систем сложных ортогональных сигналов (см. [1], с. 101-102).

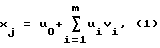

Известен ряд устройств, которые могут быть использованы для формирования систем ортогональных сигналов. Например, для формирования систем ортогональных сигналов Уолша может быть использован кодер для кода Рида-Маллера первого порядка R(1, m) (см. [2], с. 406, рис. 14.8) на основе матриц Адамара типа Сильвестра (см. [2], с. 52-53). Символы двоичной кодовой последовательности хj∈{ 0,1}, j∈{0,1,...,2m-1} (см. [2], с. 400, формула 14.7) математически описываются в операциях двоичной арифметики

где m - число разрядов двоичного счетчика;

vi∈{0,1} - выход i-го разряда двоичного счетчика;

ui∈{ 0,1} - двоичные входы устройства, определяющие номер ортогональной кодовой последовательности;

u0∈{ 0,1} - вход инверсии (дополнения по модулю два) системы ортогональных кодовых последовательностей.

Код Рида-Маллера первого порядка R(1, m) состоит из единичной весом 2m (состоящей из одних единиц "11...1"), нулевой весом 0 (состоящей из одних нулей "00...0") и 2m+1 - 2 кодовых последовательностей весом 2m-1.

Недостаток известного кодера R(1, m) заключается в том, что принадлежащие к одной ортогональной системе или к противоположной системе кодовые последовательности имеют одинаковый вес 2m-1.

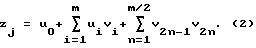

Как правило, при четном m системы ортогональных сигналов биплоскости Камерона (см. [2] , с. 414, следствие II, формула 14.29, упражнение 16.в) строились по формуле

Ортогональный код одной плоскости Камерона состоит из 2m кодовых последовательностей весом 2m-1-2(m-2)/2, а второй инверсной плоскости состоит из 2m кодовых последовательностей весом 2m-1+2(m-2)/2.

Недостаток известной формулы (2) построения ортогональной биплоскости заключается в сложности, так как требуется m+m/2-1 двухвходовых логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (сумматоров по модулю два) и m+m/2 логических элементов И. Целесообразно сократить избыточных m логических элементов И.

Наиболее близким к предлагаемому устройству является устройство кодирования [3], содержащее информационный регистр, контрольный регистр, первый и второй блоки памяти, блок сумматоров, причем входы информационного регистра являются информационными входами устройства, выходы информационного регистра соединены с входами блока сумматоров и с входами второго блока памяти и являются информационным выходом устройства, выходы блока сумматоров подключены к первым входам контрольного регистра и входам первого блока памяти, выходы первого и второго блоков памяти соединены с вторыми входами контрольного регистра, выходы контрольного регистра являются выходами контрольных признаков устройства.

Недостаток известного устройства кодирования [3] заключается в сложности.

Решаемая задача - упрощение устройства.

Поставленная задача достигается тем, что в устройство, содержащее входной регистр, дополнительно введены блок поразрядного сложения по модулю два с двумя m-разрядными входами из m логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок попарной конъюнкции нечетных и честных разрядов с одним m-разрядным входом из m/2 логических элементов И, сумматор по модулю два, блок инверсии знака, тактовый генератор, двоичный счетчик с четным числом разрядов, причем m-разрядный информационный вход входного регистра является входом номера сигнала кодера, а информационный одноразрядный вход входного регистра является входом инверсии полярно-манипулированных сигналов на противоположное значение кодера, m-разрядный выход входного регистра и информационный выход двоичного счетчика поразрядно соединены соответственно с входами первого и второго слагаемых блока поразрядного сложения по модулю два, а выход переполнения двоичного счетчика соединен с управляющим входом записи входного регистра, m-разрядный выход суммы блока поразрядного сложения по модулю два поразрядно соединен с входом блока попарной конъюнкции нечетных и четных разрядов, m/2-разрядный выход блока попарной конъюнкции нечетных и четных разрядов соединен с m/2-разрядным входом сумматора по модулю два, выход которого соединен с информационным входом блока инверсии знака, счетный вход двоичного счетчика соединен с выходом тактового генератора, одноразрядный выход входного регистра соединен с управляющим входом блока инверсии знака, выход блока инверсии знака является выходом кодера. Преимущество предлагаемого устройства по сравнению с прототипом [3] заключается в упрощении и исключении сложных и избыточных элементов. По сравнению с известным правилом (2) построения ортогональных сигналов биплоскости Камерона предлагаемое устройство использует на m меньше логических элементов И. По сравнению с известным описанием кодов Рида-Маллера первого порядка [2] в предлагаемом устройстве двоичные кодовые последовательности имеют свой собственный отличительный вес плоскости 2m-1±2(m-2)/2 вместо одного веса 2m-1. Кроме того, предлагаемое устройство позволяет практически реализовать формирование больших систем сложных сигналов с числом импульсов 103...106, так как в устройстве отсутствует блок памяти для хранения кодовых последовательностей. Таким образом, предлагаемое устройство существенно отличается от известных [1-3].

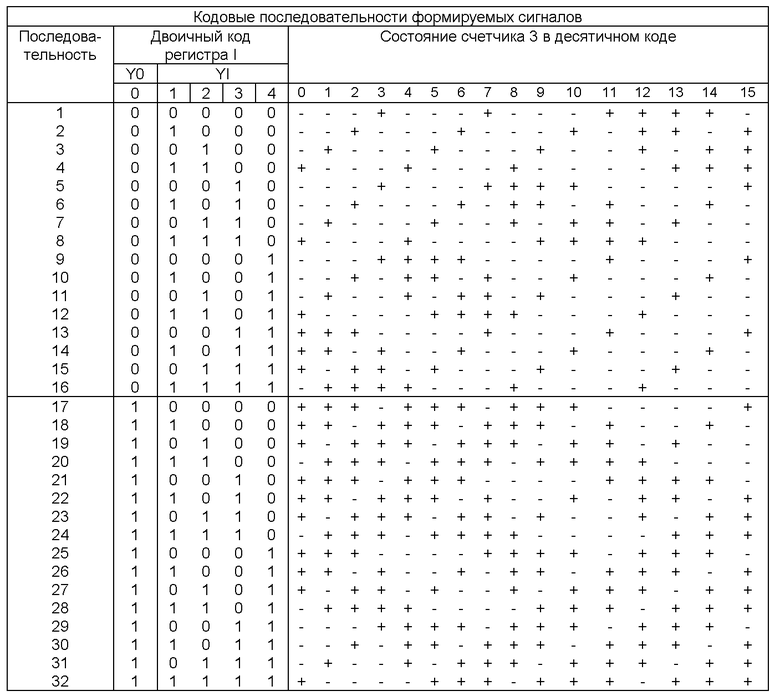

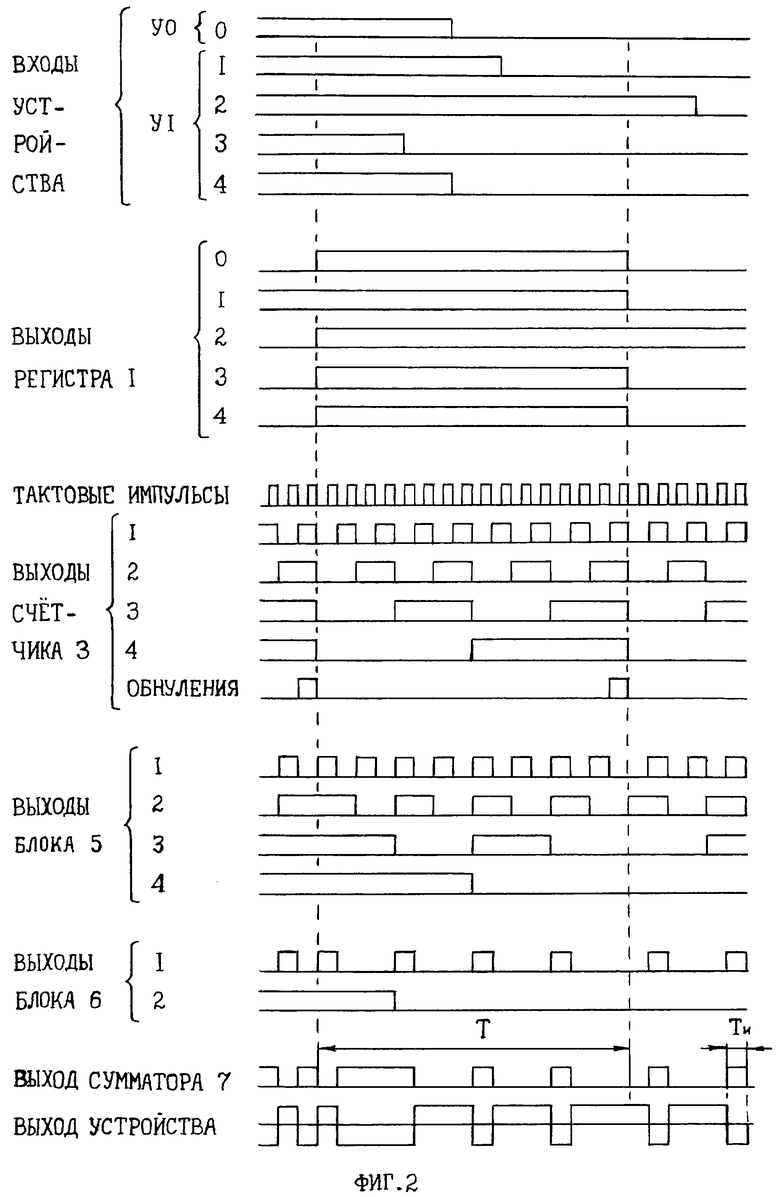

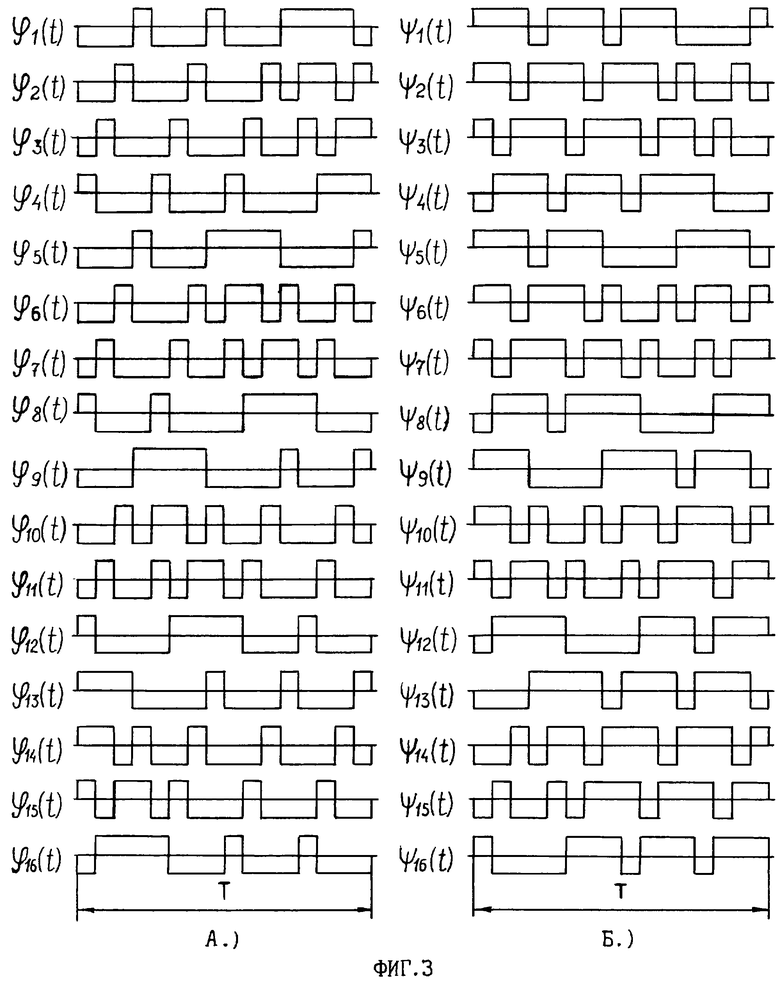

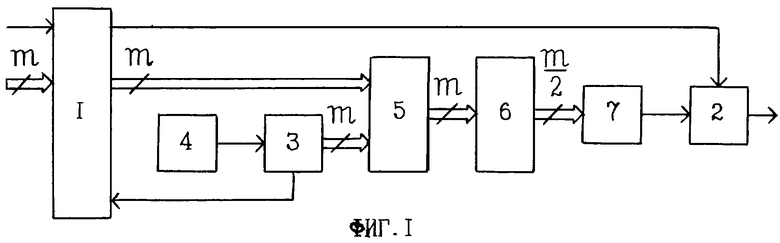

Функциональная схема кодера биплоскости ортогональных сигналов представлена на фиг.1, на фиг.2 - временные диаграммы работы устройства, на фиг.3 - вид формируемых сигналов. Работа генератора характеризуется таблицей.

Кодер биплоскости ортогональных сигналов содержит (см. фиг.1) (m+1)-разрядный входной регистр 1, блок 2 инверсии знака, двоичный счетчик 3, тактовый генератор 4, блок 5 поразрядного сложения по модулю два с двумя m-разрядными входами из m логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 6 попарной конъюнкции нечетных и четных разрядов с одним m-разрядным входом из m/2 логических элементов И, сумматор 7 по модулю два с m/2 входами, причем одноразрядный и m-разрядный информационные входы входного регистра 1 являются соответственно входом Y0 инверсии полярно-манипулированных сигналов на противоположное значение кодера и входом Y1 номера сигнала кодера, одноразрядный выход входного регистра 1 соединен с управляющим входом блока 2 инверсии знака, счетный вход двоичного счетчика 3 соединен с выходом тактового генератора 4, выход переполнения двоичного счетчика 3 соединен с управляющим входом записи входного регистра 1, m-разрядный выход входного регистра 1 и информационный выход двоичного счетчика 3 поразрядно соединены соответственно с входами первого и второго слагаемых блока 5 поразрядного сложения по модулю два, m-разрядный выход суммы блока 5 поразрядного сложения по модулю два поразрядно соединен с входом блока 6 попарной конъюнкции нечетных и четных разрядов, m/2-разрядный выход блока 6 попарной конъюнкции нечетных и четных разрядов соединен с входами сумматора 7 по модулю два, выход сумматора 7 по модулю два соединен с информационным входом блока 2 инверсии знака, выход блока 2 инверсии знака является выходом кодера.

Входной регистр 1 предназначен для приема и хранения цифровых кодов составного номера (Y0, Y1) на весь период времени формирования сложного сигнала:

- код Y0∈{0,1} определяет вид полярно-манипулированного сигнала в прямом или инверсном (противоположном) коде;

- код Y1∈{0,1,...,2m-1} задает двоичный номер кодовой последовательности ортогонального сигнала.

Прием двоичного кода с входной шины устройства осуществляется под воздействием логического уровня "1", поступающего на управляющий (синхронизирующий) вход записи входного регистра 1. Смена информации на выходной шине данных входного регистра 1 происходит по отрицательному перепаду на управляющем входе записи, то есть в начале каждого периода. При наличии на управляющем входе записи логического уровня "0" входной регистр 1 осуществляет хранение принятой информации на все время Т генерирования сложного сигнала.

Блок 2 инверсии знака позволяет получить выходной сигнал в прямом или инверсном (противоположном) коде в зависимости от управляющего логического уровня на одноразрядном выходе входного регистра 1. Кроме того, в функции блока 2 инверсии знака переход от логических уровней "1", "0" к аналоговым значениям "+1", "-1".

Двоичный счетчик 3, подсчитывающий импульсы от тактового генератора 4, задает период Т= 2mТи биортогональных сигналов. В конце каждого периода по логическому состоянию "11...1" двоичного счетчика 3 вырабатывается логический уровень "1" на выходе переполнения (обнуления) двоичного счетчика 3. Этот сигнал управляет приемом входной информации в входной регистр 1, причем запись осуществляется в начале каждого периода.

Блок 5 поразрядного сложения по модулю два с двумя m-разрядными входами состоит из m логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Для каждого i-го разряда из текущих состояний vi двоичного счетчика 3 и постоянного (в течение периода Т) смещения ui, заданного с m-разрядного выхода входного регистра 1, блок 5 поразрядного сложения по модулю два вычисляет поразрядную сумму

wi = ui + vi (mod 2),  (3)

(3)

Таким образом, в течение периода Т в зависимости от значения "0" или "1" i-го разряда m-разрядного выхода входного регистра 1 на выход i-го разряда блока 5 поразрядного сложения по модулю два поступает сигнал типа "меандр" с i-го разряда двоичного счетчика 3 в прямом или противоположном коде соответственно.

Блок 6 попарной конъюнкции нечетных и четных разрядов с одним m-разрядным входом и с m/2-разрядным выходом состоит из m/2 логических элементов И. Для каждого n-го выходного разряда из значений нечетных w2n-1 и четных w2n входных разрядов блок 6 попарной конъюнкции нечетных и четных разрядов вычисляет булеву операцию конъюнкция

gn=w2n-1•w2n,  (4)

(4)

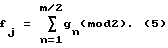

Сумматор 7 по модулю два с m/2 входами вычисляет значение логической операции

Таким образом, блок 6 попарной конъюнкции нечетных и четных разрядов и сумматор 7 по модулю два (см. [2], с. 414, следствие II, формула 14.29) вычисляют значение максимально-нелинейной "бент"-функции

fj=w1w2+w3w4+...+wm-1wm(mod 2) (6)

Кодер биплоскости ортогональных сигналов работает следующим образом.

При включении источника питания (на фиг.1 не показано) подается импульс на установку в логическое состояние "11...1" двоичного счетчика 3 и на установку в единичное состояние двухтактных D-триггеров входного регистра 1, поэтому с одноразрядного выхода входного регистра 1 логический уровень "1" поступает на управляющий вход блока 2 инверсии знака. С выхода переполнения двоичного счетчика 3 логический уровень "1" поступает на управляющий вход записи входного регистра 1, переводя его в режим приема (m+1)-разрядного цифрового кода составного номера сигнала. С m-разрядного выхода блока 5 поразрядного сложения по модулю два сигналы логического уровня "0" поступают на входы блока 6 попарной конъюнкции нечетных и четных разрядов. С выхода блока 6 попарной конъюнкции нечетных и четных разрядов сигналы логический уровень "0" поступают на входы сумматора 7 по модулю два. С выхода сумматора 7 по модулю два сигнал логический уровень "0" поступает на информационный вход блока 2 инверсии знака, поэтому на выходе устройства устанавливается положительный потенциал единичной амплитуды "+1".

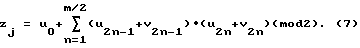

Тактовый генератор 4 вырабатывает импульсы с периодом следования Ти, которые поступают на счетный вход двоичного счетчика 3. По окончании первого тактового импульса двоичный счетчик 3 из состояния "11...1" переходит в нулевое состояние, при этом логический уровень "0" с выхода обнуления двоичного счетчика 3 поступает на управляющий вход записи входного регистра 1, переводя его в режим хранения входного кода составного номера (Y0, Y1) на все время Т = 2mТи формирования сложного сигнала. Логический уровень "0" или "1" в соответствии с входным кодом Y0 с одноразрядного выхода входного регистра 1 поступает на управляющий вход блока 2 инверсии знака для формирования полярно-манипулированного сигнала ортогональной системы (плоскости) в прямом или инверсном (противоположном) коде. С m-разрядного выхода входного регистра 1 на вход первого слагаемого блока 5 поразрядного сложения по модулю два поступает двоичный код Y1∈{0,1,...,2m-1} номера ортогонального сигнала в системе (плоскости). Под воздействием каждого тактового импульса двоичный счетчик 3 из предыдущего состояния переходит в последующее. Текущее состояние разрядов vi двоичного счетчика 3 поступает на вход второго слагаемого блока 5 поразрядного сложения по модулю два. С выхода блока 5 поразрядного сложения по модулю два вычисленная поразрядная сумма (3) поступает на вход блока 6 попарной конъюнкции нечетных и четных разрядов. Для каждого n-го разряда m/2-разрядного выхода блока 6 попарной конъюнкции нечетных и четных разрядов вычисляется логическая операция конъюнкция (4). На выходе сумматора 7 по модулю два вычисляется сумма (5). На выходе кодера кодовая последовательность ортогонального сигнала описывается выражением

При переходе двоичного счетчика 3 в состояние Т логический уровень "1" с выхода переполнения двоичного счетчика 3 поступает на управляющий вход записи входного регистра 1. Входной регистр 1 переходит в режим приема нового (m+1)-разрядного двоичного кода - номера биортогонального сигнала. Под воздействием следующих синхроимпульсов цикл работы устройства повторяется.

На временных диаграммах работы устройства (фиг.2) показано, что двоичный счетчик 3 (диаграммы сверху 12-15) осуществляет деление частоты следования тактовых импульсов, поступающих на его счетный вход с выхода тактового генератора 4 (диаграмма 11). Если счетчик 3 переходит в состояние Т, то на его выходе переполнения устанавливается логический уровень "1" (диаграмма 16) и регистр 1 осуществляет прием с входной шины данных устройства двойных цифровых кодов Y0, Y1 (диаграммы 1-5). По окончании следующего тактового импульса счетчик 3 переходит в нулевое состояние, на его выходе переполнения устанавливается логический уровень "0" и регистр 1 переходит в режим хранения входных кодов Y0, Y1 на все время Т формирования сложного сигнала (диаграммы 6-10). За время Т на входах регистра 1 подготавливаются новые цифровые коды Y0, Y1 (диаграммы 1-5). В зависимости от сигналов на соответствующих выходах блока 5 (диаграммы 7-20) формируются сигналы на выходах блока 6 (диаграммы 21, 22). В зависимости от выходного сигнала сумматора 7 (диаграмма 23) и от выходного сигнала одноразрядного выхода регистра 1 (диаграмма 6) формируется выходной полярно-манипулированный сигнал устройства (диаграмма 24) в прямом или в противоположном коде.

В таблице представлены кодовые последовательности биортогональных сигналов, формируемые предлагаемым устройством при пятиразрядной входной шине данных регистра 1 (m=4), где символы "+" и "-" обозначают импульсы единичной амплитуды положительной и отрицательной полярности соответственно. В зависимости от пяти бит входного кода (Y0, Y1) (в таблице колонки с 2-й по 6-ю) формируется 1 из 32 шестнадцатиимпульсных полярно-манипулированных сигналов (в таблице колонки с 7-й по 22-ю).

Первые шестнадцать сигналов (фиг.3 (А), строки 1-16 таблицы) образуют ортогональную систему, так как

Вторые шестнадцать сигналов (фиг. 3 (Б), строки 17-32 таблицы) также образуют ортогональную систему сигналов, так как

Сигналы ϕi(t) и ψi(t) противоположны,

Преимущество предлагаемого устройства по сравнению с аналогом и прототипом заключается в упрощении и исключении сложных и избыточных элементов. По сравнению с известным правилом (2) построения ортогональных сигналов биплоскости Камерона предлагаемое устройство использует на m меньше логических элементов И. По сравнению с прототипом в предлагаемом устройстве исключен блок памяти, а сумматор по модулю (Т-1) заменен на более простой в техническом исполнении блок 5 поразрядного суммирования по модулю два. По сравнению с известным описанием кодов Рида-Маллера первого порядка [2, 3, 4] в предлагаемом устройстве двоичные кодовые последовательности имеют свой собственный отличительный вес плоскости 2m-1±2(m-2)/2 вместо одного веса 2m-1. Кроме того, предлагаемое устройство позволяет практически реализовать формирование больших систем сложных сигналов с числом импульсов 103...106, так как в устройстве отсутствует блок памяти для хранения кодовых последовательностей.

Источники информации

1. Варакин Л.Е. Системы связи с шумоподобными сигналами. - М.: Радио и связь, 1985. - 383 с.

2. Мак-Вильямс Ф.Дж., Слоэн Н.Дж.А. Теория кодов, исправляющих ошибки. - М.: Связь, 1979. - 744 с.

3. Гриненко Н. И., Лысаковский А.Ф., Шевчук П.С. Генератор ортогонально-противоположных сигналов /Авторское свидетельство СССР 1697071 A1, кл. МКИ G 06 F 1/02.

4. Холл М. Комбинаторика. - М.: Мир, 1970. - 424 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР КВАЗИОРТОГОНАЛЬНО-ПРОТИВОПОЛОЖНЫХ СИГНАЛОВ | 1999 |

|

RU2187144C2 |

| Генератор ортогонально противоположных сигналов | 1989 |

|

SU1697071A1 |

| Генератор квазиортогональных сигналов | 1989 |

|

SU1755270A1 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| СПОСОБ КОМПРЕССИИ-ДЕКОМПРЕССИИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2488960C2 |

| Формирователь квазиоптимальных дискретно-частотных сигналов | 1988 |

|

SU1578836A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в радиотехнических системах связи с шумоподобными сигналами. Технический результат заключается в упрощении устройства. Устройство содержит входной регистр, блок поразрядного сложения по модулю два с двумя m-разрядными входами, m логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок попарной конъюнкции нечетных и четных разрядов с одним m-разрядным входом, m/2 логических элементов И, сумматор по модулю два, блок инверсии знака, тактовый генератор, двоичный счетчик с четным числом разрядов. 3 ил., 1 табл.

Кодер биплоскости ортогональных сигналов, содержащий входной регистр, отличающийся тем, что дополнительно введены блок поразрядного сложения по модулю два с двумя m-разрядными входами из m логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок попарной конъюнкции нечетных и четных разрядов с одним m-разрядным входом из m/2 логических элементов И, сумматор по модулю два, блок инверсии знака, тактовый генератор, двоичный счетчик с четным числом разрядов, причем m-разрядный информационный вход входного регистра является входом номера сигнала кодера, а информационный одноразрядный вход входного регистра является входом инверсии полярно-манипулированных сигналов на противоположное значение кодера, m-разрядный выход входного регистра и информационный выход двоичного счетчика поразрядно соединены соответственно с входами первого и второго слагаемых блока поразрядного сложения по модулю два, а выход переполнения двоичного счетчика соединен с управляющим входом записи входного регистра, m-разрядный выход суммы блока поразрядного сложения по модулю два поразрядно соединен с входом блока попарной конъюнкции нечетных и четных разрядов, m/2-разрядный выход блока попарной конъюнкции нечетных и четных разрядов соединен с m/2-разрядным входом сумматора по модулю два, выход которого соединен с информационным входом блока инверсии знака, счетный вход двоичного счетчика соединен с выходом тактового генератора, одноразрядный выход входного регистра соединен с управляющим входом блока инверсии знака, выход блока инверсии знака является выходом кодера.

| Устройство кодирования | 1989 |

|

SU1762412A1 |

| Генератор ортогонально противоположных сигналов | 1989 |

|

SU1697071A1 |

| US 5796776 А1, 18.08.1998 | |||

| Генератор квазиортогональных сигналов | 1989 |

|

SU1755270A1 |

| Автомат для сборки шариковых авторучек | 1984 |

|

SU1207811A1 |

Авторы

Даты

2003-07-27—Публикация

2001-06-09—Подача