Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания быстродействующих, специализированных и высокопроизводительных цифровых устройств, выполняющих логические операции: конъюнкцию, дизъюнкцию, инверсию, исключающее ИЛИ, эквиваленцию, арифметические операции суммирование и вычитание.

Известно "Устройство для вычислений" (Пат. RU № 2042186, от 20.08.1995 г.), позволяющее в специализированных процессорах для обработки нечеткой информации выполнять арифметические и логические операции.

Известен "Сумматор" (з-ка 94007826 от 27.02.1996 г.), который выполняет функции конъюнкции, дизъюнкции, равнозначности, констант “0” и единицы.

Известно “Устройство выполнения логических операций” Пат. № 2288500, Российская Федерация, МПК G06F 7/50, опубл. 27.11.2006, Бюл. № 33.

В качестве прототипа выбран “Вычислительный модуль логических операций” Пат. № 2716026, Российская Федерация, МПК G06F 17/00, опубл. 05.03.2020 г., Бюл. № 7.

Недостатком предложенных технических решений является низкая скорость выполнения логических операций, сложный алгоритм работы.

В представленном устройстве поразрядного вычисления логических и арифметических операций выполняются основные логические операции: конъюнкция, дизъюнкция, исключающее ИЛИ, эквиваленция, инверсия, арифметические операции: сложение и вычитание.

Технической задачей предлагаемого решения является расширение функциональных возможностей, повышение скорости выполнения логических операций, упрощение алгоритма работы устройства.

Решение задачи осуществляется тем, что устройство поразрядного вычисления логических и арифметических операций содержащие блок выполнения логических и арифметических операций, блок хранения результата, блок управления, отличающиеся тем, что дополнительно введены: блок ввода чисел, блок регистра первого числа, блок регистра второго числа, причем информационный выход блока ввода чисел соединены с первым информационным входом блока регистра второго числа и с первым информационным входом блока регистра первого числа, второй информационный вход которого соединен с четвертым информационным выходом блока управления, первый информационный выход которого соединен со вторым информационным входом блока регистра второго числа, информационный выход которого соединен с третьим информационным входом блока выполнения логических и арифметических операций, первый информационный вход которого соединен с информационным выходом блока регистра первого числа, управляющий выход блока ввода чисел соединен с управляющим входом блока выполнения логических и арифметических операций, информационный выход которого соединен с первым информационным входом блока хранения результата, второй информационный вход которого соединен со вторым информационным выходом блока управления, третий информационный выход которого соединен со вторым информационным входом блока выполнения логических и арифметических операций, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами устройства поразрядного вычисления логических и арифметических операций.

БВЧ - блок ввода чисел служит для ввода двоичных кодов операндов, знака операции и определения признака операции.

БРгПч - блок регистра первого числа служит для хранения двоичных кодов первого числа при выполнении логических и арифметических операций.

БВЛАО – блок выполнения логических и арифметических операций служит для выполнения логических операций: конъюнкции, дизъюнкции, инверсии, исключающее ИЛИ, эквиваленции, арифметических операций: суммирование и вычитание.

БРгВч - блок регистра второго числа служит для хранения двоичных кодов второго числа при выполнении логических и арифметических операций.

БХР – блок хранения результатов служит для записи и хранения результатов логических и арифметических операций.

БУ - блок управления служит для генерации информационных сигналов устройства поразрядного вычисления логических и арифметических операций.

В устройстве поразрядного вычисления логических и арифметических операций последовательность выполнения логических и арифметических операций определяется установкой управляющих сигналов на входах электронных ключей в единичное состояние. Ключи открываются, через которые значения переменных, и ранее полученные результаты других блоков, поступают на входы очередного блока устройства.

На фиг. 1 изображена структурная схема устройства поразрядного вычисления логических и арифметических операций.

На фиг. 2 представлен вариант технической реализации блока ввода чисел.

На фиг. 3 представлен вариант технической реализации блока регистра первого числа и блока регистра второго числа.

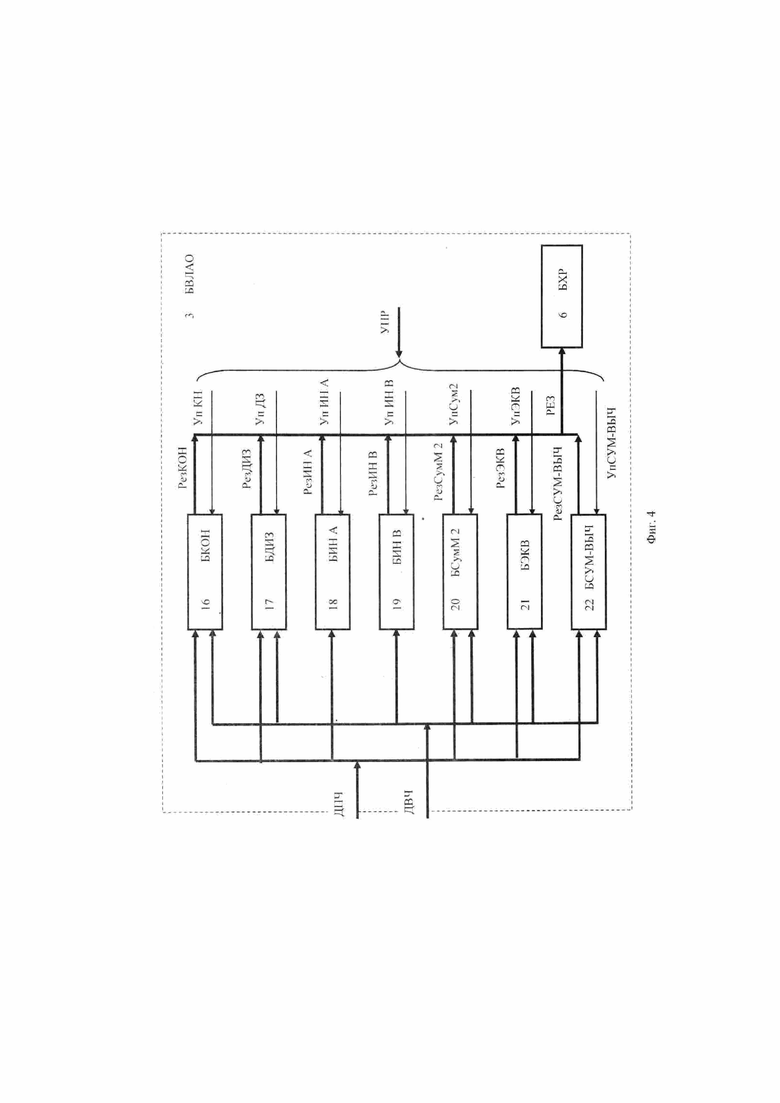

На фиг. 4 изображена структурная схема блока выполнения логических и арифметических операций.

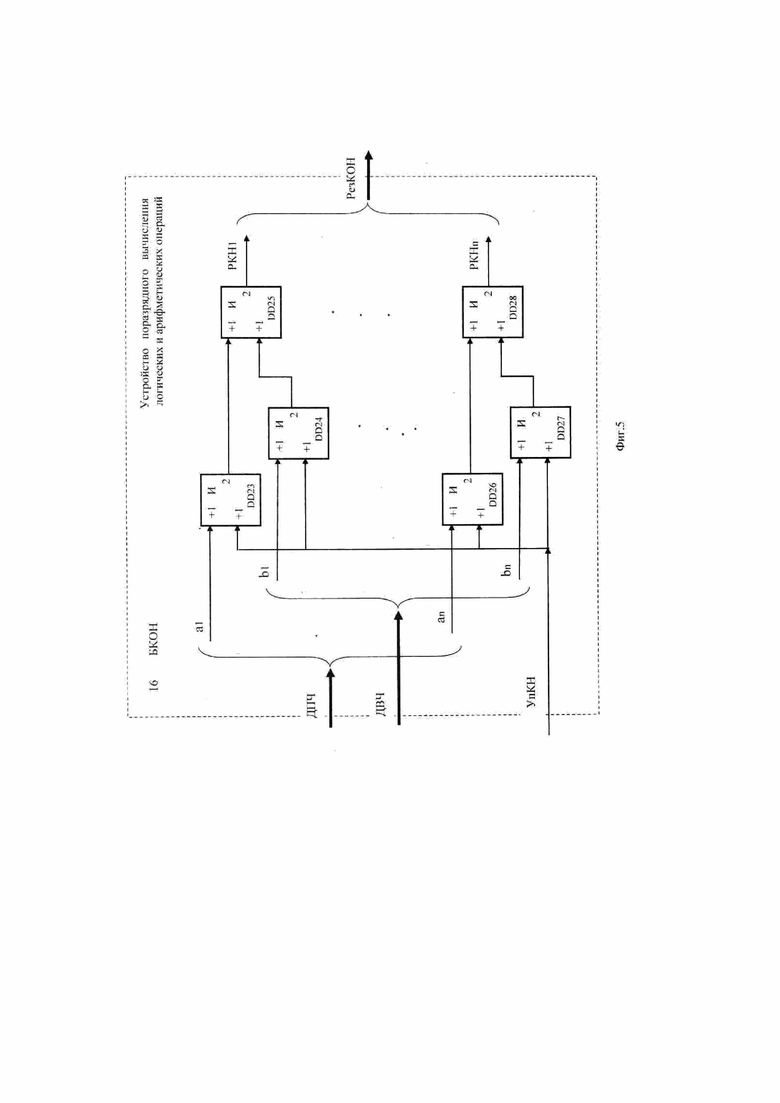

На фиг. 5 представлен вариант технической реализации блока выполнения логической операции конъюнкции.

На фиг. 6 представлен вариант технической реализации блока выполнения логической операции дизъюнкции.

На фиг. 7 представлен вариант технической реализации блока выполнения логической операции инверсии первого двоичного числа.

На фиг. 8 представлен вариант технической реализации блока выполнения логической операции инверсии второго двоичного числа.

На фиг. 9 представлен вариант технической реализации блока выполнения логической операции суммы по модулю два двоичных чисел.

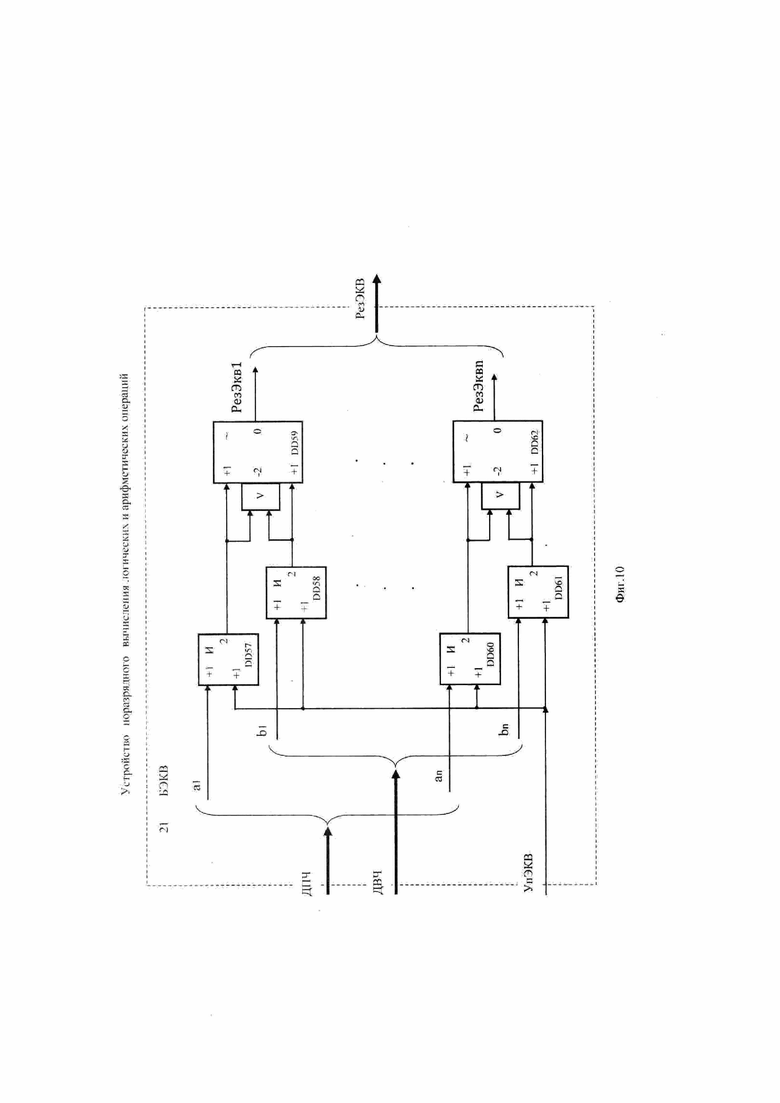

На фиг. 10 представлен вариант технической реализации блока выполнения логической операции эквиваленции двоичных чисел.

На фиг. 11 изображена структурная схема определения знака результата и схема сумматора-вычитателя.

На фиг. 12 изображена функциональная схема сумматора-вычитателя.

На фиг. 13 представлена функциональная схема определения знака результата.

На фиг. 14 представлены принципиальные схемы коммутации и сумматора-вычитателя.

На фиг. 15 представлен вариант технической реализации блока хранения результата.

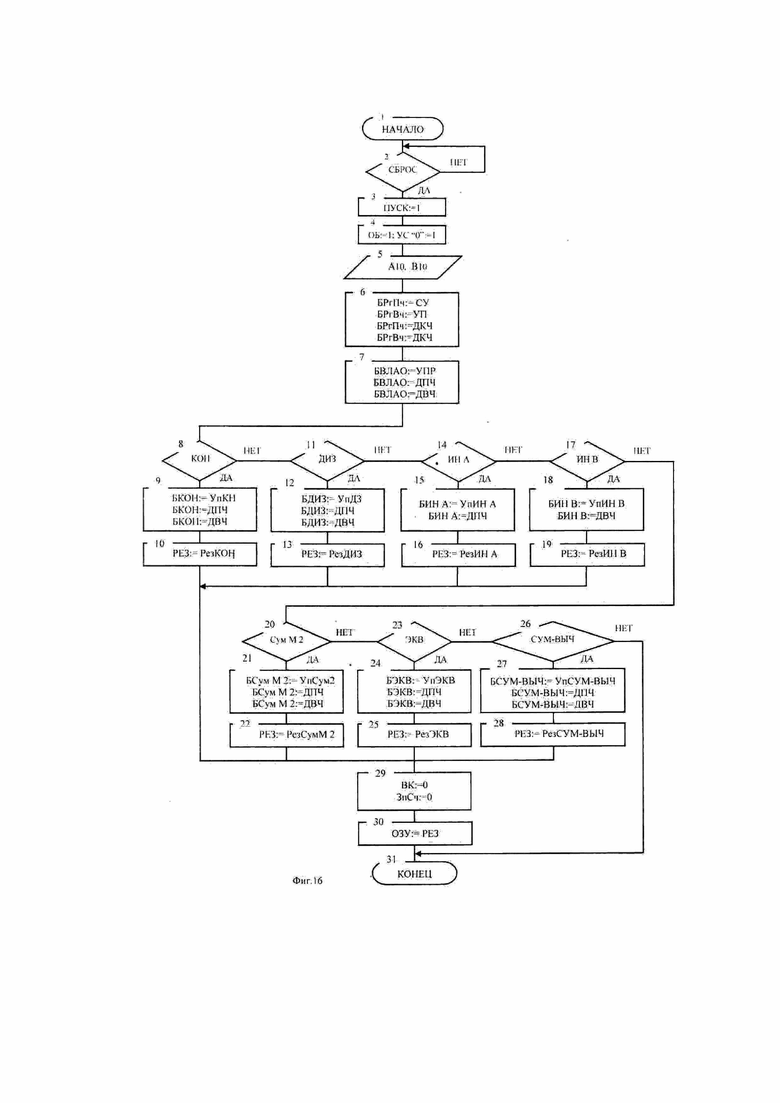

На фиг. 16 - содержательная ГСА работы модуля.

На фиг. 17 - размеченная ГСА работы устройства.

Устройство поразрядного вычисления логических и арифметических операций содержит: блок ввода чисел, блок регистра первого числа, блок выполнения логических и арифметических операций, блок регистра второго числа, блок хранения результатов, блок управления, пороговые элементы, нейроны (фиг.1).

Для описания алгоритма работы блока 6 управления используются следующие идентификаторы.

1. БВЧ – блок ввода чисел.

2. БРгПч - блок регистра первого числа.

3. БВЛАО - блок выполнения логических и арифметических операций.

4. БРгВч - блок регистра второго числа.

5. БХР - блок хранения результатов.

6. БУ - блок управления.

7. ДКЧ – двоичный код числа.

8. СВ – признак операции сигнал суммирования или вычитания.

9. ДПЧ - двоичный код первого числа.

10. ДВЧ – двоичный код второго числа.

11. РЕЗ – двоичные разряды результата.

12. УП – информационный сигнал управления блока регистра второго числа, включающий в себя сигналы: синхронизацию, обнуления, разрешения записи, выдачу.

13. СУП – информационный сигнал управления работой блока хранения результата, включающий в себя сигналы: синхронизацию, обнуления, разрешения записи, выдачу.

14. УПР – информационный сигнал управления блока выполнения логических и арифметических операций, включающий в себя сигналы: синхронизацию, обнуления, разрешения записи, выдачу.

15. СУ - информационный сигнал управления работой блока регистра первого числа, включающий в себя сигналы: синхронизацию, обнуления, разрешения записи, выдачу.

16. ЗнР А - знаковый разряд первого числа.

17. ЗнР В - знаковый разряд второго числа.

18. КОП - код операции.

19. СИНХ – сигнал синхронизации, поступающий на вход регистров блоков.

20. УСТ 0 - сигнал установки в нуль, поступающий на вход регистров блоков.

21. ЗАП - сигнал разрешения записи, поступающий на вход регистров блоков.

22. ВЫД - сигнал разрешения выдачи, поступающий на вход регистров блоков.

23. БКОН – блок выполнения логической операции конъюнкции.

24. БДИЗ - блок выполнения логической операции дизъюнкции.

25. БИН А - блок выполнения логической операции

26. БИН В - блок выполнения логической операции инверсии второго числа.

27. БСум М 2 – блок выполнения логической операции суммы по модулю два.

28. БЭКВ - блок выполнения логической операции эквиваленции.

29. БСУМ-ВЫЧ – блок выполнения арифметических операций суммирования и вычитания.

30. УпКН – управляющий сигнал блока выполнения логической операции конъюнкции.

31. УпДЗ - управляющий сигнал блока выполнения логической операции дизъюнкции.

32. УпИН А - управляющий сигнал блока выполнения логической операции инверсии первого числа.

33. УпИН В - управляющий сигнал блока выполнения логической операции инверсии второго числа.

34. УпСум 2 - управляющий сигнал блока выполнения логической операции суммы по модулю два.

35. УпЭКВ - управляющий сигнал блока выполнения логической операции эквиваленции.

36. УпСУМ-ВЫЧ - управляющий сигнал блока выполнения арифметических операций суммирования и вычитания.

37. РКН1 – первый результат выполнения логической операции конъюнкции блоком конъюнкции.

38. РКНn - результат выполнения логической операции конъюнкции младших разрядов двоичных чисел блоком конъюнкции.

39. РезКОН - результат выполнения логической операции конъюнкции блоком конъюнкции.

40. РДЗ1 - первый результат выполнения логической операции дизъюнкции блоком дизъюнкции.

41. РДЗn - результат выполнения логической операции дизъюнкции младших разрядов двоичных чисел блоком дизъюнкции.

42. РезДИЗ - результат выполнения логической операции дизъюнкции блоком дизъюнкции.

43. РезНЕ А - результат выполнения логической операции инверсии блоком инверсии первого числа.

44. РезНЕ B - результат выполнения логической операции инверсии блоком инверсии второго числа.

45. РезСум М21 - первый результат выполнения логической операции суммы по модулю два блоком суммы по модулю два.

46. РезСум М2n - результат выполнения логической операции суммы по модулю два младших разрядов двоичных чисел блоком суммы по модулю два.

47. РезСумМ 2 - результат выполнения логической операции суммы по модулю два блоком суммы по модулю два.

48. - первый результат выполнения логической операции эквиваленции блоком эквиваленции.

48. - первый результат выполнения логической операции эквиваленции блоком эквиваленции.

49. - результат выполнения логической операции эквиваленции младших разрядов двоичных чисел блоком эквиваленции.

49. - результат выполнения логической операции эквиваленции младших разрядов двоичных чисел блоком эквиваленции.

50. РезЭКВ – результат выполнения логической операции эквиваленции блоком эквиваленции.

51. ЗнРЕЗ – знаковый разряд результата.

52. ЗмЗнР – заём из знакового разряда при выполнении операции вычитании.

53. А1 …. Аn – двоичные разряды первого числа.

54. В1 …. Вn – двоичные разряды второго числа.

55. Pi+1/Zi+1 – сигнал переноса в старшие разряды при сложении или заёма из старших разрядов двоичных чисел при вычитании.

56. Si – разряд суммы.

57. Ri – разряд разности

58. Pi – перенос в старший разряд при суммировании.

59. Zi – заём из старшего разряда при вычитании.

60. РЕЗ1 – результат выполнения первого блока СУМ- ВЫЧ1.

61. РЕЗ2 – результат выполнения второго блока СУМ- ВЫЧ2.

62. РЕЗn – результат выполнения младшего блока СУМ- ВЫЧn.

63. РезСУМ-ВЫЧ - результат выполнения арифметических операций суммирование и вычитание.

64. СОЗР – схема определения знака результата.

65. ОБ - команда обнуления двоичного счетчика Сч1 блока хранения результата.

66. УС “0” - команда обнуления двоичного счетчика Сч2 блока хранения результата.

67. ГИ - генератор импульсов, поступающий из блока управления на суммирующий вход (+) двоичного счетчика Сч1 блока хранения результата.

68. ТИ - тактовые импульсы, поступающие из блока управления на суммирующий вход (+) двоичного счетчика Сч2 блока хранения результата.

69. ВК - команда выбора кристалла оперативного запоминающего устройства ОЗУ блока хранения результата.

70. Сч/Зп - команда считывания/записи оперативного запоминающего устройства ОЗУ блока хранения результата.

71. РЕО – информационный вход блока хранения результата.

72. СБРОС - сигнал сброса (обнуление) элементов памяти устройства поразрядного вычисления логических и арифметических операций.

73. ПУСК - сигнал начало работы устройства.

Работа блока упpавления устройства поразрядного вычисления логических и арифметических операций.

Содеpжательная ГСА упpавления пpиведена на фиг. 16 и она отpажает pаботу устройства поразрядного вычисления логических и арифметических операций (фиг.1).

В блоке 2 алгоритма осуществляется подача сигнала установки в нулевое состояние - СБРОС на входы всех элементов устройства.

В блоке 3 алгоритма происходит установка сигнала - пуск в единичное значение ПУСК:=1.

В блоке 4 алгоритма по командам: ОБ:=1, УС ”0”:=1 происходит установка в нулевое значение двоичных счетчиков Сч1 и Сч2 блока 5 хранения результатов, формирующих адреса строк и столбцов оперативного запоминающего устройства (фиг.15).

В блоке 5 алгоритма осуществляется ввод чисел в десятичной системе счисления А10, В10 и перевод чисел в двоичную систему счисления (фиг.2).

В блоке 6 алгоритма по командам: БРгПч:= СУ, БРгВч:=УП происходит подача информационных сигналов с выхода блока 6 управления на входы регистров блоков первого и второго числа для выполнения операций: обнуления, синхронизации, записи и выдачи. По командам: БРгПч:=ДКЧ и БРгВч:=ДКЧ на входы регистров первого и второго числа поступают двоичные коды входных чисел для записи и хранения.

В блоке 7 алгоритма по команде: БВЛАО:= УПР на вход блока выполнения логических и арифметических операций поступает информационный сигнал, который состоит из управляющих сигналов. Эти сигналы поступают на входы блоков, выполняющих логические и арифметические операции. По командам: БВЛАО:=ДПЧ, БВЛАО:=ДВЧ на входы блока выполнения логических и арифметических операций поступают двоичные коды первого и второго числа для выполнения операций (фиг.4).

В блоке 8 алгоритма анализируется признак выполнения логической операции конъюнкции КОН. Если блок выполнения логических и арифметических операций выполняет другую операцию, то осуществляется переход на блок 11 алгоритма. Если выполняется операции конъюнкция, то осуществляется переход на блок 9 алгоритма.

В блоке 9 алгоритма по команде БКОН:= УпКН на управляющие входы электронных ключей блока выполнения логической операции конъюнкции подаётся управляющий сигнал для разрешения выполнения логической операции И. По командам: БКОН:=ДПЧ, БКОН:=ДВЧ на вход блока выполнения логической операции конъюнкции подаются двоичные коды первого и второго числа (фиг.5).

В блоке 10 алгоритма по команде РЕЗ:= РезКОН на вход блока хранения результата поступает результата выполнения логической операции конъюнкции над входными числами для записи и хранения (фиг.5).

В блоке 11 алгоритма анализируется признак выполнения логической операции дизъюнкции ДИЗ. Если блок выполнения логических и арифметических операций выполняет другую операцию, то осуществляется переход на блок 14 алгоритма. Если выполняется операции дизъюнкция, то осуществляется переход на блок 12 алгоритма.

В блоке 12 алгоритма по команде БДИЗ:= УпДЗ на управляющие входы электронных ключей блока выполнения логической операции дизъюнкции подаётся управляющий сигнал для разрешения выполнения логической операции ИЛИ. По командам: БДИЗ:=ДПЧ, БДИЗ:=ДВЧ на вход блока выполнения логической операции дизъюнкции подаются двоичные коды первого и второго числа (фиг.6).

В блоке 13 алгоритма по команде РЕЗ:= РезДИЗ на вход блока хранения результата поступает результата выполнения логической операции дизъюнкции над входными числами для записи и хранения (фиг.6).

В блоке 14 алгоритма анализируется признак выполнения логической операции инверсии первого числа ИН А. Если блок выполнения логических и арифметических операций выполняет другую операцию, то осуществляется переход на блок 17 алгоритма. Если выполняется операции инверсии первого числа, то осуществляется переход на блок 15 алгоритма.

В блоке 15 алгоритма по команде БИН А:= УпИН А на управляющие входы электронных ключей блока выполнения логической операции инверсии первого числа подаётся управляющий сигнал для разрешения выполнения логической операции инверсии. По командам: БИН А:=ДПЧ на вход блока выполнения логической операции инверсии первого числа подаются двоичные разряды первого числа (фиг.7).

В блоке 16 алгоритма по команде РЕЗ:= РезИН А на вход блока хранения результата поступает результата выполнения логической операции инверсии первого числа для записи и хранения (фиг.7).

В блоке 17 алгоритма анализируется признак выполнения логической операции инверсии второго числа ИН В. Если блок выполнения логических и арифметических операций выполняет другую операцию, то осуществляется переход на блок 20 алгоритма. Если выполняется операции инверсии второго числа, то осуществляется переход на блок 18 алгоритма.

В блоке 18 алгоритма по команде БИН В:= УпИН В на управляющие входы электронных ключей блока выполнения логической операции инверсии второго числа подаётся управляющий сигнал для разрешения выполнения логической операции инверсии. По командам: БИН В:=ДВЧ на вход блока выполнения логической операции инверсии второго числа подаются двоичные разряды второго числа (фиг.8).

В блоке 19 алгоритма по команде РЕЗ:= РезИН В на вход блока хранения результата поступает результата выполнения логической операции инверсии второго числа для записи и хранения (фиг.8).

В блоке 20 алгоритма анализируется признак выполнения логической операции суммы по модулю два Сум М 2. Если блок выполнения логических и арифметических операций выполняет другую операцию, то осуществляется переход на блок 23 алгоритма. Если выполняется операции сумма по модулю два двоичных чисел, то осуществляется переход на блок 21 алгоритма.

В блоке 21 алгоритма по команде БСум М 2:= УпСум2 на управляющие входы электронных ключей блока выполнения логической операции суммы по модулю два подаётся управляющий сигнал для разрешения выполнения логической операции суммы по модулю два. По командам: БСум М 2:=ДПЧ, БСум М 2:=ДВЧ на входы блока выполнения логической операции суммы по модулю два подаются двоичные коды первого и второго числа (фиг.9).

В блоке 22 алгоритма по команде РЕЗ:= РезСумМ 2 на входы блока хранения результата поступает результата выполнения логической операции суммы по модулю два над входными числами для записи и хранения (фиг.9).

В блоке 23 алгоритма анализируется признак выполнения логической операции эквиваленции ЭКВ. Если блок выполнения логических и арифметических операций выполняет другую операцию, то осуществляется переход на блок 26 алгоритма. Если выполняется операции эквиваленция двоичных чисел, то осуществляется переход на блок 24 алгоритма.

В блоке 24 алгоритма по команде БЭКВ:= УпЭКВ на управляющие входы электронных ключей блока выполнения логической операции эквиваленции подаётся управляющий сигнал для разрешения выполнения логической операции эквиваленции. По командам: БЭКВ:=ДПЧ, БЭКВ:=ДВЧ на входы блока выполнения логической операции эквиваленции подаются двоичные коды первого и второго числа (фиг.10).

В блоке 25 алгоритма по команде РЕЗ:= РезЭКВ на входы блока хранения результата поступает результата выполнения логической операции эквиваленции над входными числами для записи и хранения (фиг.10).

В блоке 26 алгоритма анализируется признак выполнения арифметических операций суммирование или вычитание СУМ-ВЫЧ. Если блок выполнения логических и арифметических операций не выполняет ни каких вычислений, то осуществляется переход на конечный блок 31 алгоритма. Если выполняется операция суммирование или вычитание двоичных чисел, то осуществляется переход на блок 27 алгоритма.

В блоке 27 алгоритма по команде БСУМ-ВЫЧ:= УпСУМ-ВЫЧ на входы электронных ключей блока СУМ-ВЫЧ подаётся управляющий сигнал для разрешения выполнения арифметических операций суммирование или вычитание. По командам: БСУМ-ВЫЧ:=ДПЧ, БСУМ-ВЫЧ:=ДВЧ на входы блока выполнения арифметических операций суммирование или вычитание подаются двоичные коды первого и второго числа (фиг.13, 14).

В блоке 28 алгоритма по команде РЕЗ:= РезСУМ-ВЫЧ на входы блока хранения результата поступает результата выполнения арифметических операции суммирование или вычитание двоичных чисел для записи и хранения (фиг.13, 14).

В блоке 29 алгоритма по командам: ВК:=0, ЗпСч:=0 на управляющие входы оперативного запоминающего устройства ОЗУ блока хранения результатов подаются нулевые значения для создания режима записи результатов в память устройства (фиг.15).

В блоке 30 алгоритма по команде ОЗУ:=РЕЗ на информационные входы оперативного запоминающего устройства ОЗУ блока хранения результатов подаются результаты выполнения логических и арифметических операций для записи и хранения (фиг.15).

Блок 31 алгоритма является конечным.

Устройство поразрядного вычисления логических и арифметических операций выполняет логические поразрядные операции: конъюнкцию (И), дизъюнкцию (ИЛИ), исключающее ИЛИ (⊕), эквиваленцию (~), инверсию (НЕ) двоичных чисел, арифметические операции: суммирование и вычитание. Поразрядное выполнение логических операций применимо к каждой паре битов, которые стоят на одинаковых позициях в двоичном представлении чисел. Эти операции применяются при сравнении чисел, сложении и вычитании. Реализация поразрядных операций выполняется в арифметическом логическом устройстве (АЛУ) процессора. В большинстве процессоров реализованы в качестве инструкции регистровый НЕ; регистровые двухаргументные И, ИЛИ, исключающее ИЛИ; проверка равенства нулю; три типа битовых сдвигов, а также циклические битовые сдвиги. Регистровая операция И используется для: проверки бита на 0 или 1, установки 0 в указанный бит (сброса бита). Регистровая операция ИЛИ используется для: установки 1 в указанный бит. Регистровая операция исключающее ИЛИ используется для инвертирования битов регистра по маске. Сдвиги влево и вправо используются для умножения на 2 и целочисленного деления на 2 соответственно и выделения отдельных битов.

Работа устройства поразрядного вычисления логических и арифметических операций заключается в следующем.

Внешние упpавляющие сигналы "СБPОС" и "ПУСК" поступают в блок 6 упpавления.

Блок 1 ввода чисел содержит шифратор ШФ DD7, сумматоры по модулю два DD8 и DD9 (фиг.2). Этот блок позволяет вводить двоичные числа. С выхода шифратора формируются двоичные коды чисел ДКЧ со своими знаками: ЗнРА, ЗнРВ. Знаковые разряды чисел и код операции с выхода шифратора поступают на входы сумматоров по модулю два DD8 и DD9. Сигнал суммирования-вычитания СВ формируется на выходе элемента DD9. Сумматоры по модулю два выполнены на нейроподобных элементах. Выходной сигнал вычисляется по формуле:

(1)

(1)

Выходными сигналами блока 1 ввода чисел являются двоичные коды операндов ДКЧ, представленные в прямых кодах и признак операции суммирование-вычитание СВ (фиг.2).

Блок 2 регистра первого числа содержит n–двоичных триггеров Трn, где n - количество разрядов входного числа. Этот блок предназначен для хранения двоичного кода первого числа. Входным информационным сигналом блока является сигнал управления СУ. Параллельно на все входы триггеров поступают управляющие сигналы: синхронизации, установки в “0”, записи и выдачи результата. Перед началом работы сумматора-вычитателя по приходу из блока 6 информационного сигнала СУ происходит обнуление всех триггеров блока (фиг. 3).

Блок 3 выполнения логических и арифметических операций состоит из блоков: конъюнкции БКОН, дизъюнкции БДИЗ, инверсии первого числа БИН А, инверсии второго числа БИН В, операции суммы по модулю два БСумМ 2, эквиваленции БЭКВ, арифметических операций суммирования и вычитания БСУМ-ВЫЧ (фиг.4). Входными информационными сигналами блока являются двоичные числа: первое ДПЧ и второе ДВЧ. Эти сигналы поступают с выходов блоков регистров первого и второго числа соответственно. Двоичные числа поступают на входы всех блоков параллельно. Входной информационный сигнал управления УПР поступает с выхода блока управления. В структуру этого сигнала входят управляющие сигналы выполнения логических операций: конъюнкции УпКН, дизъюнкции УпДЗ, инверсии первого числа УпИН А, инверсии второго числа УпИН В, суммы по модулю два УпСум2, эквиваленции УпЭКВ, выполнения арифметических операций суммирования и вычитания УпСУМ-ВЫЧ. Выходным информационным сигналом является сигнал результата РЕЗ выполнения логических и арифметических операций блоками. Структурно информационный сигнал РЕЗ состоит из результатов выполнения логических операций: конъюнкции РезКОН, дизъюнкции РезДИЗ, инверсии первого числа РезНЕ А, инверсии второго числа РезНЕ B, суммы по модулю два РезСумМ 2, эквиваленции РезЭКВ, арифметической операции суммирование и вычитание РезСУМ-ВЫЧ. Сигнал результата РЕЗ блока поступает на вход блока 6 хранения результатов БХР (фиг.4).

Блок 16 выполнения логической операции конъюнкции БКОН состоит из пороговых элементов DD23 – DD28 (фиг.5). Входными информационными сигналами блока являются двоичные числа: первое ДПЧ и второе ДВЧ. Пороговые элементы DD23, DD24, DD26, DD27 выполняют функции электронных ключей. Двоичные переменные  поступают на первые входы пороговых элементов DD23 и DD24 соответственно. Двоичные переменные

поступают на первые входы пороговых элементов DD23 и DD24 соответственно. Двоичные переменные  поступают на первые входы пороговых элементов DD26 и DD27 соответственно. Управляющим сигналом пороговых элементов DD23, DD24, DD26, DD27 является сигнал управления выполнения логической операции конъюнкции УпКН. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD23, DD24, DD26, DD27, выполняющих функции электронных ключей. Если управляющий сигнал УпКН равен единице, то электронные ключи будут открыты, входные двоичные переменные

поступают на первые входы пороговых элементов DD26 и DD27 соответственно. Управляющим сигналом пороговых элементов DD23, DD24, DD26, DD27 является сигнал управления выполнения логической операции конъюнкции УпКН. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD23, DD24, DD26, DD27, выполняющих функции электронных ключей. Если управляющий сигнал УпКН равен единице, то электронные ключи будут открыты, входные двоичные переменные  поступают на входы пороговых элементов DD25 и DD28 соответственно, которые выполняют логическую операцию И. На выходе этих элементов формируются результаты выполнения логической операции И над входными переменными. На выходе порогового элемента DD25 определяется сигнал результата конъюнкции РКН1 над переменными

поступают на входы пороговых элементов DD25 и DD28 соответственно, которые выполняют логическую операцию И. На выходе этих элементов формируются результаты выполнения логической операции И над входными переменными. На выходе порогового элемента DD25 определяется сигнал результата конъюнкции РКН1 над переменными  , на выходе порогового элемента DD28 определяется сигнал результата конъюнкции РКНn над переменными

, на выходе порогового элемента DD28 определяется сигнал результата конъюнкции РКНn над переменными . Если управляющий сигнал УпКН равен нулю, то электронные ключи будут заперты. Логическая операция И на выходе блока выполняться не будет. Выходной информационный сигнал РезКОН является результатом выполнения логической операции И блоком конъюнкции БКОН (фиг.5).

. Если управляющий сигнал УпКН равен нулю, то электронные ключи будут заперты. Логическая операция И на выходе блока выполняться не будет. Выходной информационный сигнал РезКОН является результатом выполнения логической операции И блоком конъюнкции БКОН (фиг.5).

Блок 17 выполнения логической операции дизъюнкции БДИЗ состоит из пороговых элементов DD29 – DD34 (фиг.6). Входными информационными сигналами блока являются двоичные числа: первое ДПЧ и второе ДВЧ. Пороговые элементы DD29, DD30, DD32, DD33 выполняют функции электронных ключей. Двоичные переменные  поступают на первые входы пороговых элементов DD29 и DD30 соответственно. Двоичные переменные

поступают на первые входы пороговых элементов DD29 и DD30 соответственно. Двоичные переменные  поступают на первые входы пороговых элементов DD32 и DD33 соответственно. Управляющим сигналом пороговых элементов DD29, DD30, DD32, DD33 является сигнал управления выполнения логической операции дизъюнкции УпДЗ. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD29, DD30, DD32, DD33, выполняющих функции электронных ключей. Если управляющий сигнал УпДЗ равен единице, то электронные ключи будут открыты, входные двоичные переменные

поступают на первые входы пороговых элементов DD32 и DD33 соответственно. Управляющим сигналом пороговых элементов DD29, DD30, DD32, DD33 является сигнал управления выполнения логической операции дизъюнкции УпДЗ. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD29, DD30, DD32, DD33, выполняющих функции электронных ключей. Если управляющий сигнал УпДЗ равен единице, то электронные ключи будут открыты, входные двоичные переменные  поступают на входы пороговых элементов DD31 и DD34 соответственно, которые выполняют логическую операцию ИЛИ. На выходе этих элементов формируются результаты выполнения логической операции ИЛИ над входными переменными. На выходе порогового элемента DD31 определяется сигнал результата дизъюнкции РДЗ1 над переменными

поступают на входы пороговых элементов DD31 и DD34 соответственно, которые выполняют логическую операцию ИЛИ. На выходе этих элементов формируются результаты выполнения логической операции ИЛИ над входными переменными. На выходе порогового элемента DD31 определяется сигнал результата дизъюнкции РДЗ1 над переменными  , на выходе порогового элемента DD34 определяется сигнал результата дизъюнкции РДЗn над переменными

, на выходе порогового элемента DD34 определяется сигнал результата дизъюнкции РДЗn над переменными  . Если управляющий сигнал УпДЗ равен нулю, то электронные ключи будут заперты. Логическая операция ИЛИ на выходе блока выполняться не будет. Выходной информационный сигнал РезДИЗ является результатом выполнения логической операции ИЛИ блоком дизъюнкции БДИЗ (фиг.6).

. Если управляющий сигнал УпДЗ равен нулю, то электронные ключи будут заперты. Логическая операция ИЛИ на выходе блока выполняться не будет. Выходной информационный сигнал РезДИЗ является результатом выполнения логической операции ИЛИ блоком дизъюнкции БДИЗ (фиг.6).

Блок 18 выполнения логической операции инверсии первого числа БИН А состоит из пороговых элементов DD35 – DD42 (фиг.7). Входным информационным сигналам блока являются двоичные разряды первого числа ДПЧ. Пороговые элементы DD35, DD37, DD39, DD41 выполняют функции электронных ключей. Двоичные переменные  поступают на первые входы пороговых элементов DD35, DD37, DD39, DD41 соответственно. Управляющим сигналом пороговых элементов DD35, DD37, DD39, DD41 является сигнал управления выполнения логической операции инверсии первого числа УпИН А. Этот сигнал поступает на вторые управляющие входы пороговых элементов DD35, DD37, DD39, DD41 выполняющих функции электронных ключей. Если управляющий сигнал УпИН А равен единице, то электронные ключи будут открыты, входные двоичные переменные

поступают на первые входы пороговых элементов DD35, DD37, DD39, DD41 соответственно. Управляющим сигналом пороговых элементов DD35, DD37, DD39, DD41 является сигнал управления выполнения логической операции инверсии первого числа УпИН А. Этот сигнал поступает на вторые управляющие входы пороговых элементов DD35, DD37, DD39, DD41 выполняющих функции электронных ключей. Если управляющий сигнал УпИН А равен единице, то электронные ключи будут открыты, входные двоичные переменные  поступают на входы пороговых элементов DD36, DD38, DD40, DD42 соответственно, которые выполняют логическую операцию инверсию входных переменных, инвертируют двоичные разряды. На выходе этих элементов формируются результаты выполнения логической операции инверсии входных переменных

поступают на входы пороговых элементов DD36, DD38, DD40, DD42 соответственно, которые выполняют логическую операцию инверсию входных переменных, инвертируют двоичные разряды. На выходе этих элементов формируются результаты выполнения логической операции инверсии входных переменных  . Если управляющий сигнал УпИН А равен нулю, то электронные ключи будут заперты. Логическая операция инверсии первого числа на выходе блока выполняться не будет. Выходной информационный сигнал РезИН А является результатом выполнения логической операции инверсии блоком инверсии первого числа БИН А (фиг.7).

. Если управляющий сигнал УпИН А равен нулю, то электронные ключи будут заперты. Логическая операция инверсии первого числа на выходе блока выполняться не будет. Выходной информационный сигнал РезИН А является результатом выполнения логической операции инверсии блоком инверсии первого числа БИН А (фиг.7).

Блок 19 выполнения логической операции инверсии второго числа БИН В состоит из пороговых элементов DD43 – DD50 (фиг.8). Входным информационным сигналам блока являются двоичные разряды второго числа ДВЧ. Пороговые элементы DD43, DD45, DD47, DD49 выполняют функции электронных ключей. Двоичные переменные  поступают на первые входы пороговых элементов DD43, DD45, DD47, DD49 соответственно. Управляющим сигналом пороговых элементов DD43, DD45, DD47, DD49 является сигнал управления выполнения логической операции инверсии второго числа УпИН В. Этот сигнал поступает на вторые управляющие входы пороговых элементов DD43, DD45, DD47, DD49 выполняющих функции электронных ключей. Если управляющий сигнал УпИН В равен единице, то электронные ключи будут открыты, входные двоичные переменные

поступают на первые входы пороговых элементов DD43, DD45, DD47, DD49 соответственно. Управляющим сигналом пороговых элементов DD43, DD45, DD47, DD49 является сигнал управления выполнения логической операции инверсии второго числа УпИН В. Этот сигнал поступает на вторые управляющие входы пороговых элементов DD43, DD45, DD47, DD49 выполняющих функции электронных ключей. Если управляющий сигнал УпИН В равен единице, то электронные ключи будут открыты, входные двоичные переменные  поступают на входы пороговых элементов DD44, DD46, DD48, DD50 соответственно, которые выполняют логическую операцию инверсию входных переменных, инвертируют двоичные разряды. На выходе этих элементов формируются результаты выполнения логической операции инверсии входных переменных

поступают на входы пороговых элементов DD44, DD46, DD48, DD50 соответственно, которые выполняют логическую операцию инверсию входных переменных, инвертируют двоичные разряды. На выходе этих элементов формируются результаты выполнения логической операции инверсии входных переменных  . Если управляющий сигнал УпИН В равен нулю, то электронные ключи будут заперты. Логическая операция инверсии второго числа на выходе блока выполняться не будет. Выходной информационный сигнал РезИН В является результатом выполнения логической операции инверсии блоком инверсии второго числа БИН В (фиг.8).

. Если управляющий сигнал УпИН В равен нулю, то электронные ключи будут заперты. Логическая операция инверсии второго числа на выходе блока выполняться не будет. Выходной информационный сигнал РезИН В является результатом выполнения логической операции инверсии блоком инверсии второго числа БИН В (фиг.8).

Блок 20 выполнения логической операции суммы по модулю два БСумМ 2 состоит из пороговых элементов DD51, DD52, DD54, DD55 и нейроподобных элементов DD53 и DD56 (фиг.9). Входными информационными сигналами блока являются двоичные числа: первое ДПЧ и второе ДВЧ. Пороговые элементы DD51, DD52, DD54, DD55 выполняют функции электронных ключей. Двоичные переменные  поступают на первые входы пороговых элементов DD51 и DD52 соответственно. Двоичные переменные

поступают на первые входы пороговых элементов DD51 и DD52 соответственно. Двоичные переменные  поступают на первые входы пороговых элементов DD54 и DD55 соответственно. Управляющим сигналом пороговых элементов DD51, DD52, DD54, DD55 является сигнал управления выполнения логической операции суммы по модулю два УпСум 2. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD51, DD52, DD54, DD55, выполняющих функции электронных ключей. Если управляющий сигнал УпСум 2 равен единице, то электронные ключи будут открыты, входные двоичные переменные

поступают на первые входы пороговых элементов DD54 и DD55 соответственно. Управляющим сигналом пороговых элементов DD51, DD52, DD54, DD55 является сигнал управления выполнения логической операции суммы по модулю два УпСум 2. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD51, DD52, DD54, DD55, выполняющих функции электронных ключей. Если управляющий сигнал УпСум 2 равен единице, то электронные ключи будут открыты, входные двоичные переменные  поступают на входы нейроподобных элементов DD53 и DD56 соответственно, которые выполняют логическую операцию сумму по модулю два. На выходе этих элементов формируются результаты выполнения логической операции суммы по модулю два над входными переменными. На выходе нейроподобного элемента DD53 определяется сигнал результата суммы по модулю два РезСумМ 21 над переменными

поступают на входы нейроподобных элементов DD53 и DD56 соответственно, которые выполняют логическую операцию сумму по модулю два. На выходе этих элементов формируются результаты выполнения логической операции суммы по модулю два над входными переменными. На выходе нейроподобного элемента DD53 определяется сигнал результата суммы по модулю два РезСумМ 21 над переменными  , на выходе нейроподобного элемента DD56 определяется сигнал результата суммы по модулю два РезСумМ 2n над переменными

, на выходе нейроподобного элемента DD56 определяется сигнал результата суммы по модулю два РезСумМ 2n над переменными  . Если управляющий сигнал УпСум 2 равен нулю, то электронные ключи будут заперты. Логическая операция сумма по модулю два на выходе блока выполняться не будет. Выходной информационный сигнал РезСумМ 2 является результатом выполнения логической операции суммы по модулю два блоком суммы по модулю два БСумМ 2 (фиг.9).

. Если управляющий сигнал УпСум 2 равен нулю, то электронные ключи будут заперты. Логическая операция сумма по модулю два на выходе блока выполняться не будет. Выходной информационный сигнал РезСумМ 2 является результатом выполнения логической операции суммы по модулю два блоком суммы по модулю два БСумМ 2 (фиг.9).

Блок 21 выполнения логической операции эквиваленции БЭКВ состоит из пороговых элементов DD57, DD58, DD60, DD61 и нейроподобных элементов DD59 и DD62 (фиг.10). Входными информационными сигналами блока являются двоичные числа: первое ДПЧ и второе ДВЧ. Пороговые элементы DD57, DD58, DD60, DD61 выполняют функции электронных ключей. Двоичные переменные  поступают на первые входы пороговых элементов DD57 и DD58 соответственно. Двоичные переменные

поступают на первые входы пороговых элементов DD57 и DD58 соответственно. Двоичные переменные  поступают на первые входы пороговых элементов DD60 и DD61 соответственно. Управляющим сигналом пороговых элементов DD57, DD58, DD60, DD61 является сигнал управления выполнения логической операции эквиваленции УпЭКВ. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD57, DD58, DD60, DD61, выполняющих функции электронных ключей. Если управляющий сигнал УпЭКВ равен единице, то электронные ключи будут открыты, входные двоичные переменные

поступают на первые входы пороговых элементов DD60 и DD61 соответственно. Управляющим сигналом пороговых элементов DD57, DD58, DD60, DD61 является сигнал управления выполнения логической операции эквиваленции УпЭКВ. Этот управляющий сигнал поступает на вторые управляющие входы пороговых элементов DD57, DD58, DD60, DD61, выполняющих функции электронных ключей. Если управляющий сигнал УпЭКВ равен единице, то электронные ключи будут открыты, входные двоичные переменные  поступают на входы нейроподобных элементов DD59 и DD62 соответственно, которые выполняют логическую операцию эквиваленции. На выходе этих элементов формируются результаты выполнения логической операции эквиваленции над входными переменными. На выходе нейроподобного элемента DD59 определяется сигнал результата эквиваленции РезЭКВ1 над переменными

поступают на входы нейроподобных элементов DD59 и DD62 соответственно, которые выполняют логическую операцию эквиваленции. На выходе этих элементов формируются результаты выполнения логической операции эквиваленции над входными переменными. На выходе нейроподобного элемента DD59 определяется сигнал результата эквиваленции РезЭКВ1 над переменными  , на выходе нейроподобного элемента DD62 определяется сигнал результата эквиваленции РезЭквn над переменными

, на выходе нейроподобного элемента DD62 определяется сигнал результата эквиваленции РезЭквn над переменными  . Если управляющий сигнал УпЭКВ равен нулю, то электронные ключи будут заперты. Логическая операция эквиваленция на выходе блока выполняться не будет. Выходной информационный сигнал РезЭКВ является результатом выполнения логической операции эквиваленции блоком эквиваленции БЭКВ (фиг.10).

. Если управляющий сигнал УпЭКВ равен нулю, то электронные ключи будут заперты. Логическая операция эквиваленция на выходе блока выполняться не будет. Выходной информационный сигнал РезЭКВ является результатом выполнения логической операции эквиваленции блоком эквиваленции БЭКВ (фиг.10).

Блок 22 состоит из схемы определения знака результата СОЗР и схемы СУМ-ВЫЧ сумматоров-вычитателей. В структуру схемы СУМ-ВЫЧ входит схема коммутации и сумматоры-вычитатели (фиг.11). Схема СУМ-ВЫЧ сумматоров-вычитателей содержит схему определения знака результата СОЗР DD66, схемы сумматоров-вычитателей DD67 - DD69 (фиг.12). Этот блок выполняет арифметические операции суммирования и вычитания, определяет знаковый разряд результата. На вход блока поступают модули n-разрядных двоичных первого ДПЧ и второго ДВЧ чисел, признак операции суммирования-вычитания сигнал СВ, который поступает параллельно на все входы схем, сигнал управления работой сумматоров-вычитателей УпСУМ-ВЫЧ, поступающий параллельно на все входы схем. Если сигнал СВ равен нулю, то схемы блока выполняют суммирование двоичных чисел, если этот сигнал равен единице, то выполняется поразрядная операция вычитания. На входы каждой схемы сумматора-вычитателя СУМ-ВЫЧi поступают одноименные двоичные разряды чисел Ai и Bi, сигнал управления работой сумматоров-вычитателей УпСУМ-ВЫЧ, признак операции сигнал СВ, перенос Pi из младших разрядов в старшие и заём Zi из старших разрядов в младшие. На схему определения знака результата СОЗР поступают знаковые разряды первого ЗнР А и второго ЗнР В двоичных чисел, сигнал суммирования–вычитания СВ (фиг.12). Сигнал заёма из знакового разряда ЗмЗнР поступает на вход первого сумматора-вычитателя СУМ-ВЫЧ1, который выполняет операции со старшими разрядами входных чисел. Этот сигнал формируется при вычитании чисел. Если заём ЗмЗнР равен нулю, то первое двоичное число по модулю больше второго, в этом случае менять местами входные числа не надо. Если сигнал заёма равен единице, в этом случае происходит вычитание от меньшего числа по модулю большего, то для получения разности необходимо поменять местами входные числа. Информационный сигнал результата РЕЗ является выходным сигналом блока (фиг. 12).

Схема определения знака результата СОЗР определяет знаковый разряд результата. В структуру схемы входят пороговые элементы DD70 – DD74 (фиг.13). Входные сигналы: признак операции суммирования-вычитания СВ и заём из знакового разряда первого числа поступают на вход схемы СУМ-ВЫЧ1, на котором суммируются старшие разряды, поступают на вход порогового элемента ПЭ DD70, который выполняет функцию логической схемы И. Сигнал с выхода порогового элемента DD70 поступает на прямой управляющий вход порогового элемента ПЭ DD73, который выполняет функцию логической схемы И и на вход порогового элемента DD71, который выполняет функцию инвертора. Сигнал с выхода инвертора поступает на прямой управляющий вход порогового элемента ПЭ DD72, который выполняет функцию логической схемы И. Выходные сигналы пороговых элементов DD72 и DD73 поступают на входы порогового элемента ПЭ DD74, который выполняет функцию логической схемы ИЛИ. Если сигнал суммирования-вычитания СВ равен нулю, то выполняется арифметическая операция суммирование двоичных чисел. Входные числа An и Bn суммируются по модулю, знаку суммы присваивается знак первого числа. An. Выходной сигнал порогового элемента DD70 будет равен нулю. Пороговый элемент ПЭ DD73 будет запет, на выходе будет нулевое значение. Пороговый элемент DD72 будет открыт, так как сигнал с выхода DD70 поступит на управляющий вход через инвертор DD71. Первым входом порогового элемента DD72 является знаковый разряд первого числа ЗнР A, который через отрытый пороговый элемент DD72 поступит на первый вход порогового элемента DD74 – схемы ИЛИ. Знаковый разряд результата ЗнР РЕЗ – выход логической схемы ИЛИ элемента DD74, будет равен знаковому разрядe первого числа ЗнР A.

Если сигнал суммирования-вычитания СВ равен единице, то выполняется арифметическая операция вычитание двоичных чисел, от большего по модулю вычитается меньшее. Определяющим сигналом в сравнении модулей чисел является сигнал заёма из знакового разряда первого числа ЗмЗнР. Знаку разности присваивается знак большего числа. Если сигнал заёма ЗмЗнР равен нулю, то первое число по модулю больше второго, в этом случае вычисляется разность между числами An и Bn. Выходной сигнал порогового элемента DD70 будет равен нулю. Пороговый элемент ПЭ DD73 будет запет, на выходе будет нулевое значение. Пороговый элемент DD72 будет открыт, так как сигнал с выхода DD70 поступит на управляющий вход через инвертор DD71. Первым входом порогового элемента DD72 является знаковый разряд первого числа ЗнР A, который через отрытый пороговый элемент DD72 поступит на первый вход порогового элемента DD74 – схемы ИЛИ. Знаковый разряд результата ЗнР РЕЗ – выход логической схемы ИЛИ элемента DD74, будет равен знаковому разряду большего числа ЗнРA.

Если сигнал заёма ЗмЗнР равен единице, то первое число по модулю меньше второго, в этом случае вычисляется разность между числами Bn и An. Выходной сигнал порогового элемента DD70 будет равен единице. Пороговый элемент ПЭ DD73 будет открыт, на выходе будет единичное значение. Пороговый элемент DD72 будет заперт, так как сигнал с выхода DD70 поступит на управляющий вход через инвертор DD71. Вторым входом порогового элемента DD73 является знаковый разряд второго большего числа ЗнР B, который через отрытый пороговый элемент DD73 поступит на второй вход порогового элемента DD74 – схемы ИЛИ. Знаковый разряд результата ЗнР РЕЗ – выход логической схемы ИЛИ элемента DD74, будет равен знаковому разряду большего второго числа ЗнР B (фиг.13).

Схема коммутации меняет местами входные двоичные разряды при выполнении операции вычитания, если от меньшего по модулю числа вычитается большее, вследствие которого формируется сигнал заёма из знакового разряда первого числа ЗмЗнР. После анализа этого сигнала и выполнения перестановки чисел вследствие этого от большего второго числа по модулю вычитается меньшее первое.

В структуру схемы коммутации входят пороговые элементы DD75 – DD83 (фиг.14). Входные сигналы: управляющий сигнал суммирования и вычитания УпСУМ-ВЫЧ, заём из знакового разряда первого числа ЗмЗнР и двоичные разряды чисел Ai и Bi поступают на входы схем сумматоров-вычитателей СУМ-ВЫЧi, где выполняется арифметические операция: суммирование и вычитания от большего по модулю меньшее одноименных разрядов двоичных чисел.

Сигнал суммирования и вычитания УпСУМ-ВЫЧ параллельно поступает на управляющие входы пороговых элементов DD75 и DD80, которые выполняют функцию электронных ключей. Если сигнал управления УпСУМ-ВЫЧ равен нулю, то электронные ключи DD75 и DD80 будут заперты. Входные двоичные разряды Аi и Вi не поступают на входы схем сумматора-вычитателя. Если сигнал управления равен единице, электронные ключи DD75 и DD80 будут открыты, двоичные разряды Аi и Вi поступают на вход схем сумматора-вычитателя, в этом случае арифметические операции будут выполняться. Сигнал заёма заёма из знакового разряда первого числа ЗмЗнР параллельно поступает на входы пороговых элементов ПЭ DD76 и DD81, которые выполняют функции инверторов и на входы пороговых элементов ПЭ DD78 и DD82, которые выполняют функции логических схем И. Двоичные разряды первого числа Ai поступают на первые входы пороговых элементов ПЭ DD75 и DD82, второго числа Bi поступают на вторые входы пороговых элементов ПЭ DD80 и DD83, которые выполняют функции логических схем И. Пороговый элемент ПЭ DD79 выполняет функцию логической схемы ИЛИ. Если сигнал заёма из знакового разряда первого числа ЗмЗнР равен нулевому значению, то пороговые элементы DD78 и DD82 будут заперты. Пороговые элементы DD77 и DD83 будут открыты, т.к. на их входы нулевой управляющий сигнал поступает через инверторы DD76 и DD81. В этом случае двоичный разряд первого числа Ai через открытый элемент DD77 и пороговый элемент DD79 (логическую схему ИЛИ) поступит на первый вход нейроподобного элемента DD86, выполняющего логическую функцию суммы по модулю два. Двоичный разряд второго числа Bi через открытый элемент DD83 поступит на четвертый вход порогового элемента DD87, выполняющего логическую функцию И. Если сигнал заёма из знакового разряда первого числа ЗмЗнР равен единичному значению, то пороговые элементы DD77 и DD83 будут заперты, т.к. на их входы единичный управляющий сигнал поступает через инверторы DD76 и DD81. Пороговые элементы DD78 и DD82 будут открыты, В этом случае двоичный разряд второго числа Bi через открытый элемент DD78 и пороговый элемент DD79 поступит на первый вход нейроподобного элемента DD86. Двоичный разряд первого числа Ai через открытый элемент DD82 поступит на третий вход порогового элемента DD87. В итоге происходит перестановка двоичных разрядов первое меньшее становиться вторым, второе большее становиться первым для выполнения арифметической операции вычитания (фиг.14).

Полный одноразрядный сумматор предназначен для сложения трёх одноразрядных двоичных чисел (фиг.14). Устройство имеет три входа: двоичные разряды Ai, Bi, результат переноса Pi+1 предыдущего сумматора, и два выхода: результата сложения Si и сигнала переноса в старший разряд Pi.

Таблица 1 истинности отображает функционирования полного одноразрядного сумматора.

Из таблицы 1 сумма Si чисел определяется формулой

(1)

(1)

Перенос Pi из младшего разряда в старший при сложении чисел определяется формулой

(2)

(2)

Работа полного одноразрядного вычитателя описывается таблицей 2 истинности, в которой отображены: заём Zi+1, поступающий из соседнего более младшего разряда, уменьшаемое Аi, вычитаемое Вi, разность Ri, заём Zi, возникающий в данном i-том разряде.

Из таблицы 2 разность чисел  определяется формулой

определяется формулой

(3)

(3)

Заём Zi из старшего разряда в младший определяется формулой

(4)

(4)

Формулы, по которым вычисляются сумма  и разность

и разность  одинаковые, два сумматора по модулю два, выполнены на нейроподобных элементах DD84 и DD85 (фиг.14). При выполнении операции сложение перенос

одинаковые, два сумматора по модулю два, выполнены на нейроподобных элементах DD84 и DD85 (фиг.14). При выполнении операции сложение перенос  из младшего разряда в старший вычисляется на пороговом элементе DD87. При суммировании нейроподобный элемент DD86 выполняет функцию повторителя двоичного разряда

из младшего разряда в старший вычисляется на пороговом элементе DD87. При суммировании нейроподобный элемент DD86 выполняет функцию повторителя двоичного разряда  , который подаётся на первый вход элемента. На второй вход нейроподобного элемента D86 подаётся признак операции СВ. Если выполняется операция суммирование, то сигнал СВ равен нулю. На выходе нейроподобного элемента DD86 будет значение

, который подаётся на первый вход элемента. На второй вход нейроподобного элемента D86 подаётся признак операции СВ. Если выполняется операция суммирование, то сигнал СВ равен нулю. На выходе нейроподобного элемента DD86 будет значение  . При выполнении операции вычитание двоичных разрядов сигнал СВ равен единице. Нейроподобный элемент DD86 выполняет операцию инвертора, на выходе которого выполняется функция

. При выполнении операции вычитание двоичных разрядов сигнал СВ равен единице. Нейроподобный элемент DD86 выполняет операцию инвертора, на выходе которого выполняется функция  . Заём

. Заём  из старшего разряда в младший вычисляется на пороговом элементе DD87.

из старшего разряда в младший вычисляется на пороговом элементе DD87.

Работа сумматора-вычитателя заключается в следующем. На входы нейроподобного элемента DD84 подаются двоичные разряды  и

и  . Этот нейроподобный элемент выполняет операцию суммирования входных двоичных разрядов. На выходе сумматора DD84 вычисляется сумма двоичных разрядов

. Этот нейроподобный элемент выполняет операцию суммирования входных двоичных разрядов. На выходе сумматора DD84 вычисляется сумма двоичных разрядов  и

и  . Результат суммы поступает на первый вход нейроподобного элемента DD85. На второй вход этого элемента поступает двоичный разряд переноса

. Результат суммы поступает на первый вход нейроподобного элемента DD85. На второй вход этого элемента поступает двоичный разряд переноса  из младшего разряда в старший. На выходе нейроподобного элемента DD85 вычисляется сумма

из младшего разряда в старший. На выходе нейроподобного элемента DD85 вычисляется сумма  и разность

и разность  входных двоичных разрядов

входных двоичных разрядов  и

и  по формуле

по формуле  . На входы нейроподобного элемента DD86 подается двоичные разряды

. На входы нейроподобного элемента DD86 подается двоичные разряды  или

или и признак выполнения арифметической операции суммирования или вычитания сигнал

и признак выполнения арифметической операции суммирования или вычитания сигнал  . Если сигнал

. Если сигнал  равен нулю, то выполняется операция суммирование двоичных чисел. Если сигнал

равен нулю, то выполняется операция суммирование двоичных чисел. Если сигнал  равен единице, то выполняется операция вычитания двоичных чисел. При выполнении операции суммирование нейроподобный элемент DD86 выполняет операцию повторителя, на выходе формируется сигнал

равен единице, то выполняется операция вычитания двоичных чисел. При выполнении операции суммирование нейроподобный элемент DD86 выполняет операцию повторителя, на выходе формируется сигнал  по формуле

по формуле  . При выполнении операции вычитания нейроподобный элемент DD86 выполняет операцию отрицание, на выходе инвертора формируется сигнал

. При выполнении операции вычитания нейроподобный элемент DD86 выполняет операцию отрицание, на выходе инвертора формируется сигнал  по формуле

по формуле  . Пороговый элемент DD87 вычисляет перенос

. Пороговый элемент DD87 вычисляет перенос  из младшего разряда в старший по формуле

из младшего разряда в старший по формуле  . При выполнении операции вычитания на пороговом элементе DD87 вычисляется заём

. При выполнении операции вычитания на пороговом элементе DD87 вычисляется заём  из старшего разряда в младший по формуле

из старшего разряда в младший по формуле  (фиг.14).

(фиг.14).

Блок 4 регистра второго числа содержит n – двоичных триггеров Трn, где n - количество разрядов входного числа. Этот блок предназначен для хранения двоичного кода второго числа. Входным информационным сигналом блока является сигнал управления УП. Параллельно на все входы триггеров поступают управляющие сигналы: синхронизации, установки в “0”, записи и выдачи результата. Перед началом работы сумматора-вычитателя происходит обнуление всех триггеров блока по приходу из блока 6 информационного сигнала УП (фиг.3).

Блок 5 хранения результатов БХР содержит оперативное запоминающее устройство ОЗУ DD90 двоичный счетчик формирующий адреса столбцов ОЗУ – Сч1 DD88, двоичный счетчик формирующий адреса строк ОЗУ – Сч2 DD89 (фиг.15). Входным информационным сигналом блока является сигнал СУП, который поступает с выхода блока 6 управления. В структуру этого сигнала входят управляющие сигналы: обнуления ОБ, УС “0”, прямоугольные импульсы ГИ, ТИ, управления работой оперативного запоминающего устройства ВК, Сч/Зп. Двоичные счетчики вначале работы устройства обнулены управляющими сигналами ОБ, УС “0” соответственно. На входы счетчиков поступают прямоугольные импульсы ГИ, ТИ. Счетчики формируют адреса столбцов АД СТЛ и строк АД СТР, по которым записываются результаты логических и арифметических операций РЕЗ, поступающие на вход Вх оперативного запоминающего устройства ОЗУ DD90. Сигналы управления работой оперативного запоминающего устройства ОЗУ DD90 выбора кристалла и считывания/запись соответственно при записи принимают нулевые значения ВК=0, Сч/Зп=0 (фиг.15).

Блок 6 упpавления синтезиpуется на основе ГСА алгоpитма упpавления (фиг.16). Размеченная ГСА pаботы блока 6 упpавления пpиведена на фиг.17 где обозначено:

Логические условия:

Х1 : “СБРОС” Х5 : “ИН В”

Х2 : “КОН” Х6 : “Сум М 2”

Х3 : “ДИЗ ” Х7 : “ЭКВ ”

Х4 : “ИН А” Х8 : “СУМ-ВЫЧ ”

Опеpатоpы:

У1 : “ПУСК:=1” У22 : “БИН А:=ДПЧ”

У2 : “ОБ:=1” У23 : “РЕЗ:= РезИН А”

У3 : “УС “0”:=1” У24 : “БИН В:= УпИН В”

У4 : “А10” У25 : “БИН В:=ДВЧ”

У5 : “В10” У26 : “РЕЗ:= РезИН В”

У6 : “ БРгПч:= СУ” У27 : “БСумМ 2:= УпСум2”

У7 : “ БРгВч:=УП” У28 : “БСумМ 2:=ДПЧ”

У8 : “ БРгПч:=ДКЧ” У29 : “БСумМ 2:=ДВЧ”

У9 : “ БРгВч:=ДКЧ” У30 : “РЕЗ:= РезСумМ 2”

У10 : “ БВЛАО:= УПР ” У31 : “БЭКВ:= УпЭКВ”

У11 : “ БВЛАО:=ДПЧ” У32 : “БЭКВ:=ДПЧ”

У12 : “БВЛАО:=ДВЧ” У33 : “БЭКВ:=ДВЧ”

У13 : “БКОН:= УпКН” У34 : “РЕЗ:= РезЭКВ”

У14 : “БКОН:=ДПЧ” У35 : “БСУМ-ВЫЧ:= УпСУМ-ВЫЧ”

У15 : “БКОН:=ДВЧ” У36 : “БСУМ-ВЫЧ:=ДПЧ”

У16 : “РЕЗ:= РезКОН” У37 : “БСУМ-ВЫЧ:=ДВЧ”

У17 : “БДИЗ:= УпДЗ” У38 : “РЕЗ:= РезСУМ-ВЫЧ”

У18 : “БДИЗ:=ДПЧ” У39 : “ВК:=0”

У19 : “БДИЗ:=ДВЧ” У40 : “ЗпСч:=0”

У20 : “РЕЗ:= РезДИЗ” У41 : “ОЗУ:= РЕЗ”

У21 : “БИН А:= УпИН А”

Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Сумматор-вычислитель на элементах нейронной логики | 2019 |

|

RU2715177C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Вычислительный модуль логических операций | 2019 |

|

RU2716026C1 |

| УСТРОЙСТВО ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2288500C1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Арифметико-логическое устройство | 1974 |

|

SU509870A1 |

Изобретение относится к устройству поразрядного вычисления логических и арифметических операций. Технический результат заключается в повышении точности выполнения логических и арифметических операций. Устройство содержит соединенные между собой блок выполнения логических и арифметических операций, блок хранения результата, блок управления, блок ввода чисел, блок регистра первого числа, блок регистра второго числа. 2 табл., 17 ил.

Устройство поразрядного вычисления логических и арифметических операций, содержащее блок выполнения логических и арифметических операций, блок хранения результата, блок управления, отличающееся тем, что дополнительно введены: блок ввода чисел, блок регистра первого числа, блок регистра второго числа, причем информационный выход блока ввода чисел соединены с первым информационным входом блока регистра второго числа и с первым информационным входом блока регистра первого числа, второй информационный вход которого соединен с четвертым информационным выходом блока управления, первый информационный выход которого соединен со вторым информационным входом блока регистра второго числа, информационный выход которого соединен с третьим информационным входом блока выполнения логических и арифметических операций, первый информационный вход которого соединен с информационным выходом блока регистра первого числа, управляющий выход блока ввода чисел соединен с управляющим входом блока выполнения логических и арифметических операций, информационный выход которого соединен с первым информационным входом блока хранения результата, второй информационный вход которого соединен со вторым информационным выходом блока управления, третий информационный выход которого соединен со вторым информационным входом блока выполнения логических и арифметических операций, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами устройства поразрядного вычисления логических и арифметических операций.

| Вычислительный модуль логических операций | 2019 |

|

RU2716026C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| RU 94007826 A1, 27.02.1996 | |||

| УСТРОЙСТВО ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2288500C1 |

| СПОСОБ И УСТРОЙСТВО РАЗМЕЩЕНИЯ ГРУПП ЧИСЕЛ В ОДНОРОДНЫХ БЛОКАХ ЦИФРОВОГО РЕГИСТРА | 2015 |

|

RU2591009C1 |

| US 7840630 B2, 23.11.2010. | |||

Авторы

Даты

2020-12-23—Публикация

2020-09-04—Подача