п S

tfczH

Л

Л5

vj о го

Jk

К)

Изобретение относится к вычислительной технике и может быть использовано в цифровых ЭВМ повышенной информационной надежности, их устройствах хранения и обмена информацией и для повышения верности в системах передачи данных, системах шумопонижения цифровой, звуко-, видеозаписи и воспроизведения

Известно устройство для кодирования с исправлением пакетов ошибок, содержащее три блока регистров сдвига, три блока сумматоров, блок умножения и три блока переключения. Недостатком этого устройства являются значительные аппаратурные затраты, большое время обработки информации, а также низкая вероятность ее коррекции при кодировании способом

Наиболее близким к предлагаемому изобретению по технической сущности является устройство для кодирования,содержащее группу входов устройства, информационный и контрольный регистры, группу выходов устройства, регистр прямого кода, схему сравнения, две группы элементов И, элемент ИЛИ группу элементов НЕ, группу элементов ИЛИ, элемент НЕ и блок сумматоров, причем группа входов устройства соединена со входами информационного регистра, выходы элемента ИЛИ совместно с выходами блока сумматоров подключены ко входу контрольного регистра, входам элементов И мегпог. группы и через элемент НЕ ко входам элементов И второй группы, блока сумматоров подключены ко j/одам контрольного регистра, выходы информационного регистра соединены со входам 1 пеорой и второй группы элементов И, схемы сравнения и входами контролируемого запоминающего устройства, выхог.ы которо о связаны с ре гистром прямоте кода, входы схемы сравнения подключены, кроме того к выходам регистра прямого кода, входы блока сумматоров совместно с группой выходов подключены к выходам группы элементов ИЛИ, ня входы которой подключены выходы групп элементов И.

Недостатками этого устройства являются значительные временные затраты и возможность формирования контрольного признака только для информации контролируемого запоминающего устройств;1

Целью изобретения является увеличение быстродействия устройства.

Эта цель достигается тем, что в устройство введены блоки памяти, причем группа входов устройства соединена со входами информационного регистра, выходы которого подключены к входам всех блоков памяти, кроме первого входам модульных

сумматоров первого яруса блока сумматоров и совместно с выходами контрольного регистра к группе выходов устройства, выходы блоков памяти связаны, совместно с

выходом блока сумматоров, со входами контрольного регистра, выходы модульных сумматоров каждого яруса блока сумматоров, кроме последнего, соединены со входами соответствующих модульных сумматоров

последующих ярусов, а выход модульного сумматора последнего яруса является выходом блока сумматоров и подключен, кроме того, ко входу первого блока памяти

Устройство кодирует числа, поступающие на его входы, в соответствии с каскадируемым вырожденным кодом взвешенных групп (КВВГ-кодом), суть которого заключается в следующем.

Информационная часть кода числа сопровождается как и при известных способах контроля, контрольным признаком. Но в отличие от известных способов контрольный признак состоит из двух частей, каждая из которых вычисляется следующим образом Информационная часть кода числа разбивается на фиксированные группы определенной разрядности, например, на п групп по 5 разрядов в каждой. Разрядность групп S определяет максимальную кратность обнаруживаемых и исправляемых ошибок. Для расчета первой части контрольного признака используется вырожденный ВГ-код, который отличается от ВГ-кода величинами используемых весовых козффициентови контрольного модуля и получается из последнего, ссг.и в фоомупе для расчета контрольного признака

г(А) { J, (А С|}ч.

t -.. 1

(П

где о - код i-той группы, рассматриваемый как некоторое число;

Ci - весовой коэффициент i-той группы; С) - контрольный модуль,

n число S-разрядных групп, на которые разбит код исходного числа,

знак (X}q означает вычисление остатка от деления числа X на число q. е качестве весовых коэффициентов использевать Ci i для всех значений i, а в качестве контрольного модуля

.

В этом случае будет получен контрольный признак той же разрядности S, что и рззрядность групп, на которые разбито исходное число. Естественно, что при этом код теряет корректирующие свойства, так как он позволяет только определить факт наличия ошибки, но не позволяет определить ее место и величину

Однако если место ошибки определено каким-либо другим способом, то вырожденный ВГ-код позволяет величину этой ошибки определить. Действительно, при наличии ошибки в j-той группе величиной Д вели- чина контрольного признака в соответствии с (1) при Ci 1 будет равна.

J -1л,

r(A) {2 «+(r7 -fAaj) + X «}q. i iI -j + i

а разность контрольных признаков исходного и искаженного чисел, вычисленная по контрольному модулю

Ar {r(A)r(A) +

1 /1 1

+ (aj+Aq) + Ј я-,i j -И

- Z . (2)

1 1)

Поэтому, если место ошибки известно, то ее исправление осуществляется легко, т.к

а а + Arzjjq,

откуда

щ (а +

Дня определения еста ошибки используется вторая част - контрольного признака, которая ,че1ся как совокупность из п частнь-х контрольных признаков Каждый из частных контрольных признаков относится к соответствующей 1-й Фиксированной группе разрядов указанного выше разбиения и получается относительно величины ct применением любого обнаруживающего кода, например, контроля по модулю qi, где qi q, т.е

fi - { a} q.(3)

Если применить к исходному коду про- цедуры (1, 3), то контрольный признак числа будет представлен совокупностью

R(A) r(A). fi(rzi. f2 . fn(rth). И) которая сопровождает исходное число при его хранении, передаче и т г.

Совокупность исходного числа и его контрольного признака (4) образует информационную и контрольную части разрядов каскадируемого вырожденного ВГ-кода (КВВГ-кода), формируемого в предлагаемом устройстве. При декодировании числа в устройствах обнаружения и исправления ошибок применение процедуры (3) и сравнение величин fi с ранее вычисленными позволя- ет определить наличие ошибки и ее место, а применение процедур (1 2) - наличие ошибки и ее величину. Совместная обработка информации о наличии ошибки позволяет

обеспечить высо -л ю вероятность ее обнаружения, s значение величины ошибки - ее безусловную коррекцию

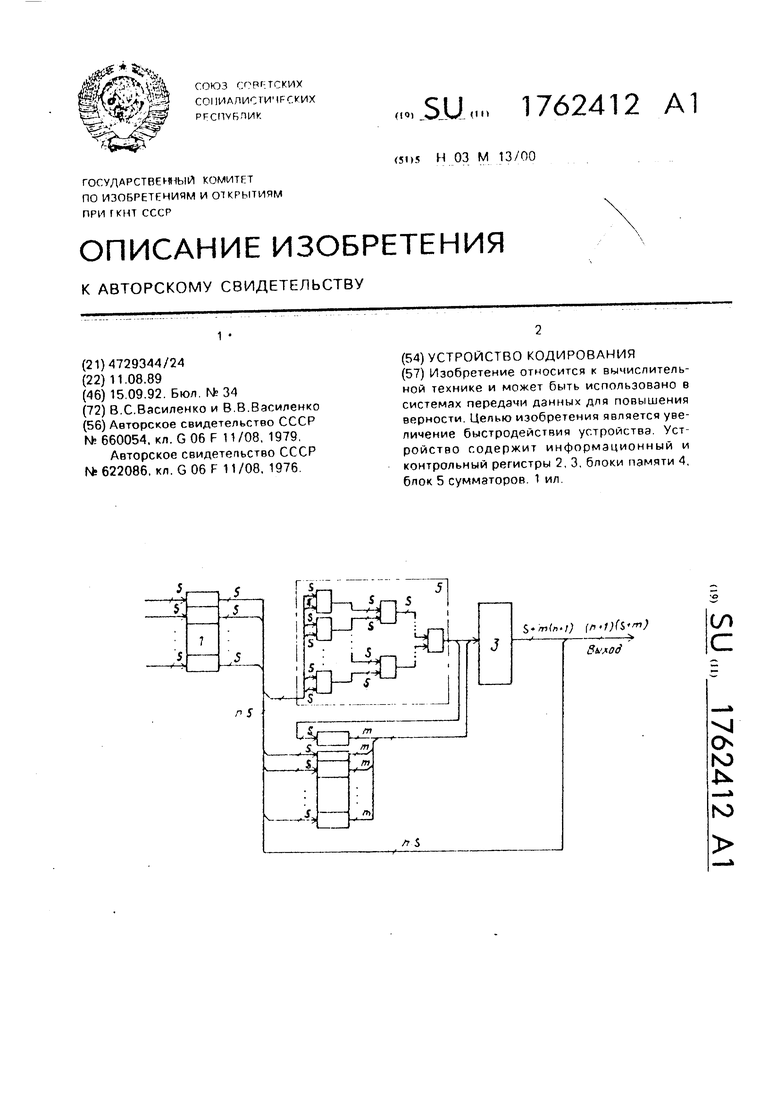

На чертеже представлена схема устройства кодирования

Устройство содержит группу входов 1 устройства, информационный и контрольный регистры 2, 3, блоки памяти 4, модульные сумматоры 5 блок сумматоров б. выход 7 устройства.

При этом группа входов 1 соединена со входами информационного регистра 2, выходы которого подключены ко входам всех блоков памяти 4, кроме первого, входам соответствующих модульных сумматоров 5 первого яруса блока сумматоров 6 и совме- ст чо с выходами контрольного регистра 3, - к группе выходов 7 устройства, выходы модульных сумматоров 5 каждого яруса, кроме последнего, блока сумматоров 6 соединены со входами соответствующих модульных сумматоров 5 последнего яруса является выходом блока сумматоров 6 и связан, со входом первого блока памяти 4 и, совместно с выходами блоков памяти 4, - со входом контрольного регистра 3

Регистр 2 предназначен для приема и „ . ic.-i т, г Р - -TCI, огг исходного числа, а регистр 3 - для приема и хранения формируемого устройством S + (п-М)т-разрядного контрольного признака кода числа.

Блоки памяти 4 предназначены для табличного расчета частных контрольных признаков f|(Oi ) для все групп разрядов исходного числа, а первый из них - для расчета частного контрольного признака от величины контрольного признака вырожденного ВГ-кода, т е для расчета величины f (r(A) Для этого в каждой ячейке с адресом «i или г(А) соответствующего блока памяти хранится вычисленная константа f,(«i ) или f(rfA)) Разрядность всех этих констант - т, емкость каждого из блоков памяти 2s

Модульные сумматоры 5 предназначены для сложения кодов, поступающих на их входы по модулю Cj Совокупность всех модульных сумматоров 5 образует пирамидальный блок сумматоров б для сложения п чисел, в первом ярусе которого используется п/2 модульных сумматоров 5, а в последнем - один модульный сумматор 5 Общее число ярусов модульных сумматоров 5 равно 1од2п, где знак Х означает вычисление ближайшего целого значения к величине X. При этом на выходе блока сумматоров 6 формируется величина

г(А) { Ј « }9

которая поступает в первый из блоков памяти 4 и, кроме того, вместе с частными контрольными признаками fi( rt ) записывается в контрольный регистр 3.

Устройство работает следующим образом.

Исходное, подлежащее кодированию число поступает на группу входов 1 и записывается в информационный регистр 2 и с его выходов поступает одновременно на вход блока сумматоров б и на второй из блоков памяти 4. При этом первая группа разрядов поступает на первый вход первого модульного сумматора 5 первою уровня, вторая - на второй вход первого модульного сумматора 5, и т.д. n-ная группа поступает на второй вход последнего из п/2 модульных сумматоров 5 первого уровня. После сложения в модульных сумматорах 5 первого уровня производится сложение полученных сумм в модульных сумматорах 5 второго и всех последующих из 1од2 п ярусов блока сумматоров 6 так. что нэ его выходе образуется контрольный признак вырожденного ВГ-кода

г(А)-{ Ј ОН }q,

I 1

Так как величина контрольного модуля q 2 , то для организации сложения по модулю в каждом из модульных сумматоров 5 достаточно применить в качестве таких сумматоров S-разрядные сумматоры без использования переносов из старшего S-ro разряда. Полученное значение г (А) записывается в контрольный регистр 3 и, кроме того, передается в первый из блоков памяти 4. По входному коду, являющемуся адресом ячейки, в каждом из блоков памяти 4 считываются частные контрольные признаки этого кода fj(«(.). Эти частные контрольные признаки также записываются R контрольный регистр 3. При этом на выход устройства 7 передаются nS разрядов исходного кода с выхода информационного регистра 2 и S 4 (пИ)т разрядов контрольного признака

R(A)r(A). fi(rn). r2(«s)fn(«7n)f ,(r(A)),

которые в совокупности образуют КВВГ-код исходного числа.

В предлагаемом устройстве по сравнению с прототипом снижены временные затраты, т.к. для кодирования потребуется время для записи информации в два регистра и ее сложения в блоке сумматоров, а у прототипа дополнительно к этому -- время для записи в регистр прямого кода, для сравнения кодов и передачи их через элементы И, НЕ и два элемента ИЛИ.

Кроме того, прототип обеспечивает кодирование информации только при его подключении к контролируемому запоминающему устройстйу. в то время как предлагаемое устройство обеспечивает кодирование любых чисел, поступающих на его входы в параллельном коде.

Формула изобретения Устройство кодирования, содержащее информационный регистр, входы которого являются информационными входами устройства, блок сумматоров, выходы которого подключены к первым входам контрольного регистра, выходы которого являются выходами контрольных признаков устройства, отличающееся тем. что. с целью увеличения быстродействия устройства, в него введены первый и второй блоки памяти, выходы которых соединены с вторыми входами контрольного регистра, входы первого блока памяти соединены с выходами блока сумматоров, выходы информационно0 го регистра - с входами блока сумматоров, второго блока памяти и являются информационным выходом устройства.

5

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1989 |

|

SU1780191A1 |

| Устройство для исправления ошибок | 1989 |

|

SU1654825A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| Арифметическое устройство в системе остаточных классов | 1980 |

|

SU881745A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных для повышения верности. Целью изобретения является увеличение быстродействия устройства. Устройство содержит информационный и контрольный регистры 2, 3, блоки памяти 4, блок 5 сумматоров. 1 ил.

| Устройство для определения вычетов | 1977 |

|

SU660054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1992-09-15—Публикация

1989-08-11—Подача