Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в отказоустойчивой аппаратуре.

Известно программируемое логическое устройство, содержащее g n-входовых элементов И (n - количество информационных входов устройства, 2≅g≅2n), t элементов ИЛИ (t - количество информационных выходов устройства), первую, вторую и третью группы D-триггеров, первую группу элементов И с тремя состояниями выхода, группу элементов И-НЕ с тремя состояниями выхода, g·t двухвходовых элементов И, счетчик и дешифратор, первый, второй и третий RS-триггеры, дополнительный элемент ИЛИ и вторую группу элементов И с тремя состояниями выхода (авт.св. СССР №1444892, кл. G11C 17/00, G06F 7/00, 1988 г.).

Недостатками известного устройства являются низкое быстродействие вычисления логических функций при наличии отказов и высокие аппаратурные затраты на реализацию систем логических функций вследствие использования стандартных логических базисов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторая группа m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, причем входом сброса D-триггеров первой, второй и третьей групп счетчика является вход сброса устройства, счетный вход счетчика является входом программирования устройства, а информационные выходы счетчика подключены к информационным входам дешифратора, неинверсные выходы D-триггеров второй группы подключены к управляющим входам соответствующих элементов И с тремя состояниями на выходе группы m·2n элементов И с тремя состояниями на выходе, неинверсные выходы D-триггеров третьей группы подключены ко вторым входам соответствующих элементов И группы m·2n элементов И, управляющие входы элементов второй группы m·2n элементов И с тремя состояниями на выходе подключены к инверсным выходам соответствующих D-триггеров второй группы D-триггеров, а информационные входы элементов второй группы m·2n элементов И с тремя состояниями на выходе являются соответствующими входами расширения соответствующей группы из m групп входов расширения, выходы элементов И с тремя состояниями на выходе объединены и подключены ко входам настройки соответствующего из m блоков вычисления функций, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы, четвертый выход дешифратора является выходом окончания программирования устройства, информационные входы D-триггеров первой и второй группы являются соответствующими входами расширения соответствующей из m групп входов расширения, информационные входы D-триггеров третьей группы являются 2(n-1) входами расширения соответствующей из m групп входов расширения, первые входы элементов И группы m(n-1) элементов И являются соответствующими из n-1 неинверсных входов группы 2n·m входов парафазных входных переменных (по 2m разрядов на каждый блок вычисления функций), первые входы элементов ИЛИ группы m(m-1) элементов ИЛИ являются соответствующими из n-1 инверсных входов группы 2n·m входов парафазных входных переменных (по 2m разрядов на каждый из m блоков вычисления функций), выходы элементов И группы m(n-1) элементов И подключены к соответствующим i-м инверсным входам парафазных входных переменных соответствующего из m блоков вычисления функций

Недостатком известного устройства, принятого за прототип, являются высокие аппаратурные затраты на реализацию систем логических функций большого числа переменных.

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию логических функций в совершенной дизъюнктивной нормальной форме (СДНФ). В связи с этим, каждый блок вычисления функций должен иметь 2n настроечных входов для задания всех возможных конституент функции n переменных, хотя некоторые из них могут повторяться в других функциях системы функций. Для реализации каждого блока вычисления функций в прототипе необходим 2n-1 элемент, что приводит к невозможности такой реализации даже для небольших n - порядка 8…10. В настоящее время в программируемых логических интегральных схемах (ПЛИС) переход на блоки вычисления функций (LUT) 6 переменных только начат, в основном используются блоки 4, 5 переменных.

Задачей изобретения является снижение аппаратных затрат на реализацию систем логических функций большого количества переменных.

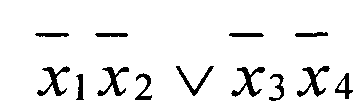

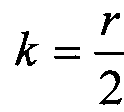

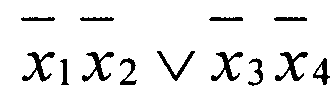

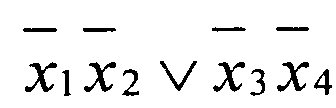

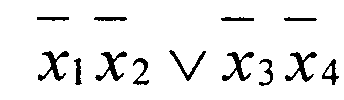

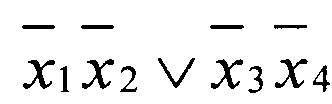

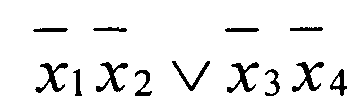

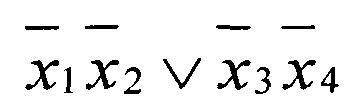

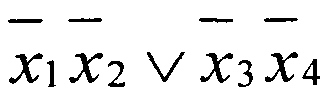

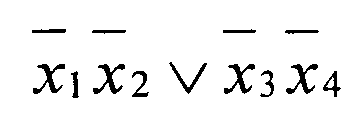

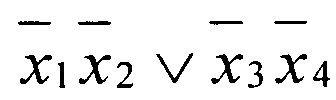

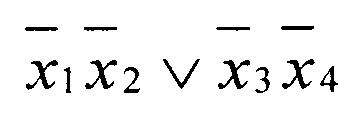

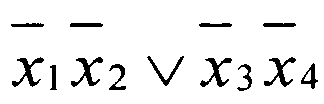

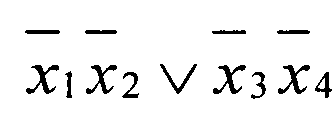

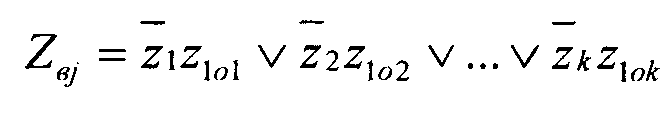

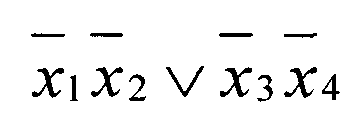

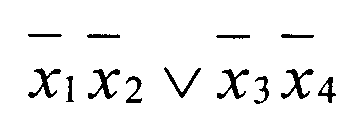

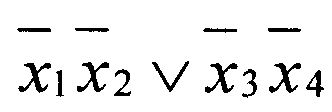

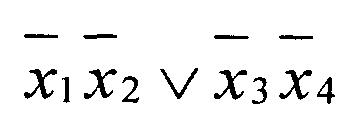

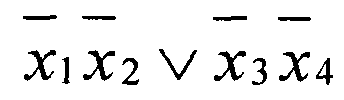

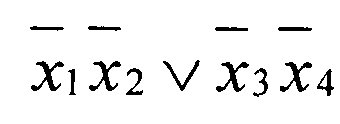

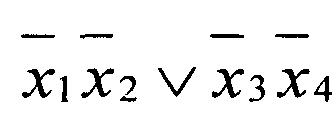

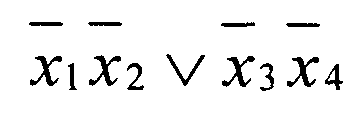

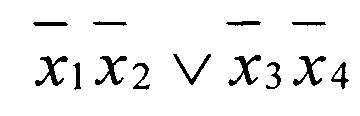

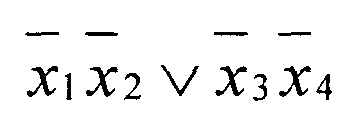

Поставленная задача была решена за счет того, что в известное программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций, где m - число вычисляемых логических функций, счетчик, дешифратор, причем информационные входы D-триггеров из групп D-триггеров подключены к соответствующим разрядам входов данных, входы сброса всех D-триггеров всех групп D-триггеров и вход сброса счетчика объединены и подключены ко входу сброса устройства, выход счетчика подключен ко входу дешифратора, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы D-триггеров, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы D-триггеров, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы D-триггеров, выходы группы m блоков вычисления функций являются выходами устройства, каждый блок вычисления функций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=int log2(n),(n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2НЕ-И-ИЛИ двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ дополнительно введены k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D-триггеров, вторых D-триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D-триггеров, вторых D-триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D-триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D-триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D-триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам функций блоков значений конъюнкций, причем нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2НЕ-И-ИЛИ, реализующих функцию

, где k=int log2(n),(n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2НЕ-И-ИЛИ двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ дополнительно введены k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D-триггеров, вторых D-триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D-триггеров, вторых D-триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D-триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D-триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D-триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам функций блоков значений конъюнкций, причем нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2НЕ-И-ИЛИ, реализующих функцию  , подключены к третьим входам соответствующих элементов второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

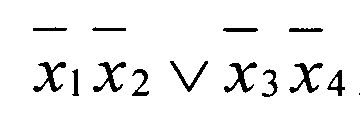

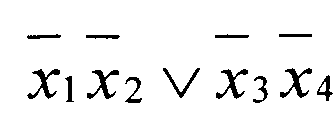

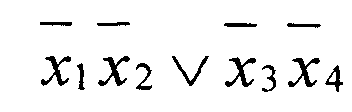

, подключены к третьим входам соответствующих элементов второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены ко вторым входам второй группы элементов 2·2НЕ-И-ИЛИ, выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ содержат два элемента 2·2НЕ-И-ИЛИ и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блока конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-ый блок значений конъюнкций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, где k=int log2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены ко вторым входам второй группы элементов 2·2НЕ-И-ИЛИ, выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ содержат два элемента 2·2НЕ-И-ИЛИ и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блока конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-ый блок значений конъюнкций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, где k=int log2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к четным входам четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

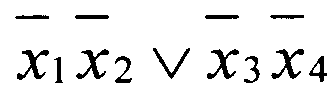

, подключены к четным входам четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ содержат два элемента 2·2НЕ-И-ИЛИ и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций.

, выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ содержат два элемента 2·2НЕ-И-ИЛИ и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций.

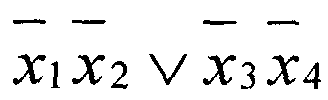

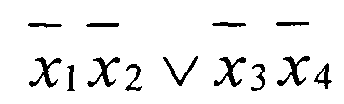

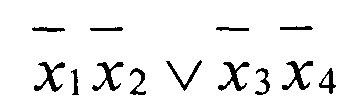

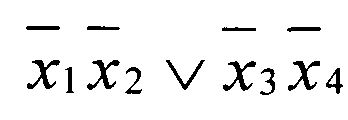

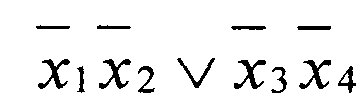

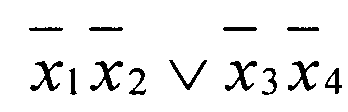

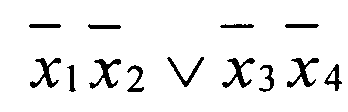

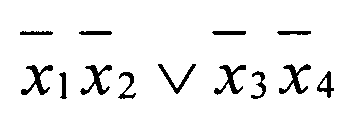

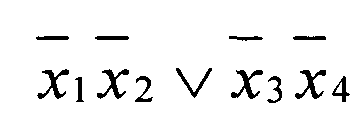

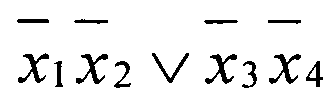

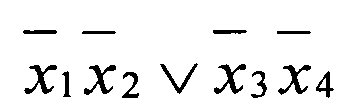

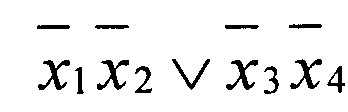

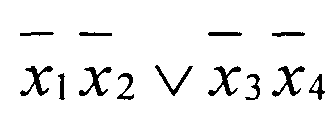

Введение процедуры вычисления логических функций в дизъюнктивной нормальной форме (ДНФ) на базе логических элементов, реализующих функцию 2·2НЕ-И-ИЛИ  , позволяет снизить аппаратные затраты на реализацию систем логических функций большого количества переменных.

, позволяет снизить аппаратные затраты на реализацию систем логических функций большого количества переменных.

Суть новой введенной процедуры заключается в следующем:

а) в задании для каждой конъюнкции вычисляемой системы логических функций трех констант - масок: основной, выделяющей существенные переменные, дополнительной, выделяющей не инверсные существенные переменные, выходных функций, указывающей, какие функции системы функций активирует данная конъюнкция;

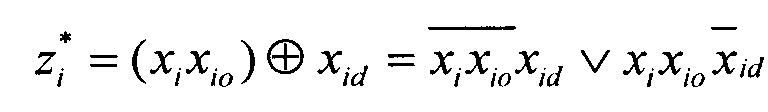

б) в вычислении каждого разряда данной конъюнкции по соответствующему разряду входного вектора с использованием логических элементов 2·2НЕ-И-ИЛИ;

в) в вычислении значений данной конъюнкции по соответствующим результатам вычисления всех ее разрядов с использованием логических элементов 2·2НЕ-И-ИЛИ;

г) в вычислении значений функций по результатам вычисления всех конъюнкций с использованием логических элементов 2·2НЕ-И-ИЛИ.

Введение дополнительных k-1 групп триггеров первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций позволяет хранить в процессе вычислений k-1 n-разрядную основную маску для выделения существенных переменных (ХО) для обеспечения вычислений в k-1 блоках конъюнкций.

Введение дополнительных k-1 групп вторых D-триггеров количеством n позволяет хранить в процессе вычислений k-1 n-разрядную дополнительную маску для выделения не инверсных существенных переменных (XD) для обеспечения вычислений в k-1 блоках конъюнкций.

Введение дополнительных k-1 групп третьих D-триггеров количеством n позволяет хранить в процессе вычислений k-1 n-разрядную маску выходных функций (ZB), указывающую, какие функции системы функций активирует данная конъюнкция для обеспечения вычислений в блоках вычисления функций.

Введение блоков конъюнкций с предлагаемой структурой и соответствующими связями позволяет вычислять каждый разряд данной конъюнкции по соответствующему разряду входного вектора с использованием логических элементов 2·2НЕ-И-ИЛИ.

Введение блоков значений конъюнкций с предлагаемой структурой и соответствующими связями позволяет вычислять значение данной конъюнкции по соответствующим результатам вычисления всех ее разрядов в блоках конъюнкций с использованием логических элементов 2·2НЕ-И-ИЛИ, при этом, если конъюнкция истинна, то есть равна единице (все существенные разряды входного вектора совпадают с соответствующими данной конъюнкции), то на выходе блока значений формируется нулевой сигнал.

Введение новых связей для m блоков вычисления функций позволяет вычислять значения функций в системе функций по результатам вычислений в блоках значений конъюнкций, используя настроечную информацию в k-1 группах третьих D-триггеров во время реализации новой введенной дисциплины.

Введение новых связей для D-триггеров первой группы позволяет хранить в процессе вычислений n-разрядную основную маску для выделения существенных переменных (ХО) для обеспечения вычислений в первом блоке конъюнкций.

Введение новых связей для D-триггеров второй группы позволяет хранить в процессе вычислений n-разрядную основную маску для выделения существенных переменных (ХО) для обеспечения вычислений в первом блоке конъюнкций.

Введение новых связей для дешифратора позволяет обеспечить программирование дополнительных k-1 групп D-триггеров первой, второй и третьей групп для последующего участия их в реализации вычислений логических функций.

Введение новых связей элементов в блоке вычисления функций позволяет вычислять значения функций в системе функций по результатам вычислений в блоках значений конъюнкций, используя настроечную информацию в k-1 группах третьих D-триггеров во время реализации новой введенной дисциплины.

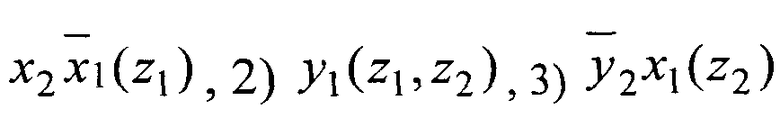

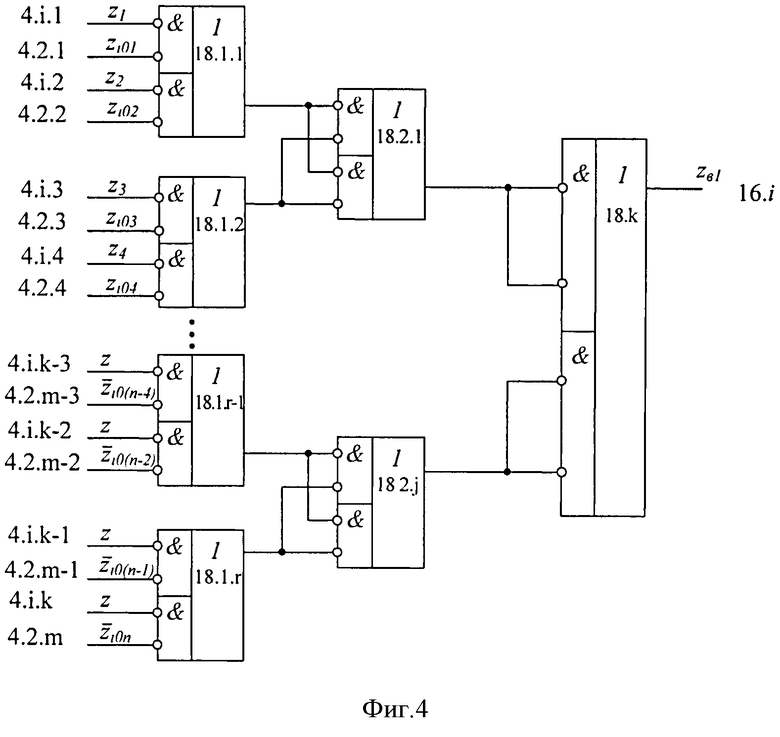

На фиг.1 изображена схема электрическая структурная программируемого логического устройства.

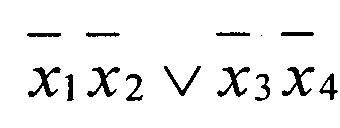

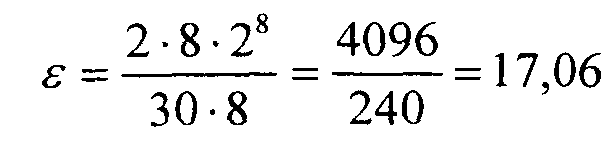

На фиг.2 - схема электрическая функциональная j-го разряда - i-го блока конъюнкции.

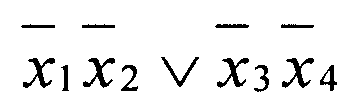

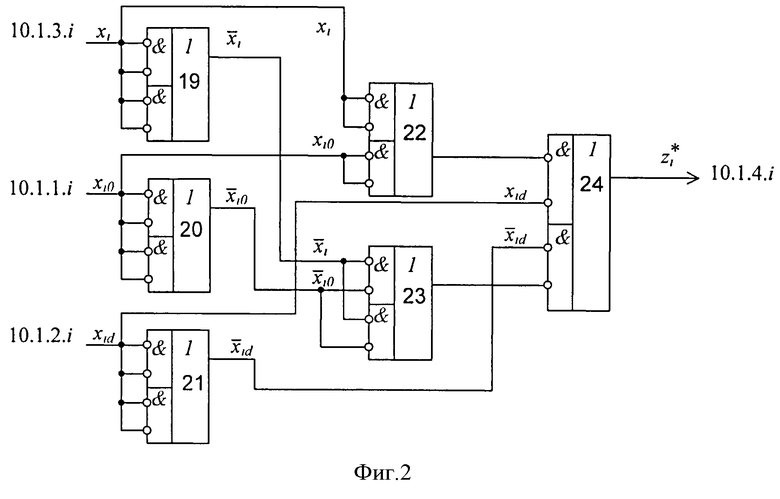

На фиг.3 - схема электрическая функциональная i-го блока значений конъюнкции.

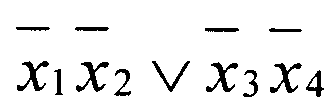

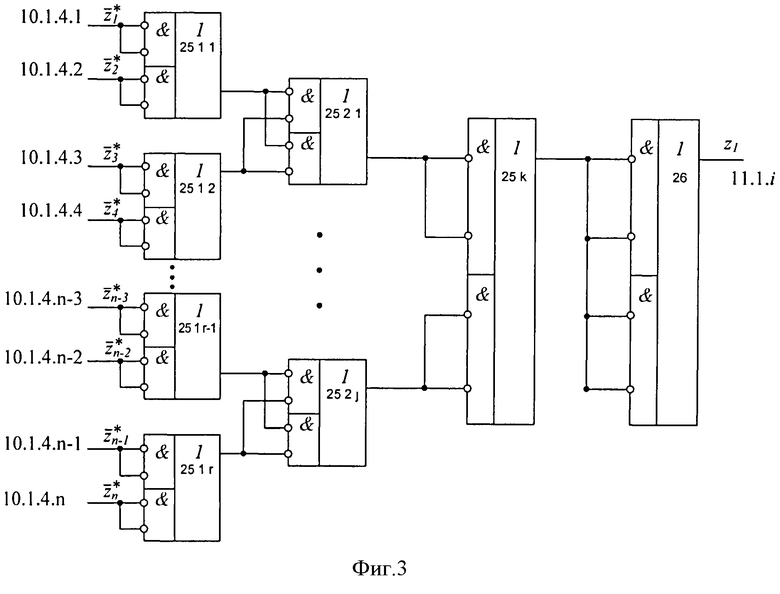

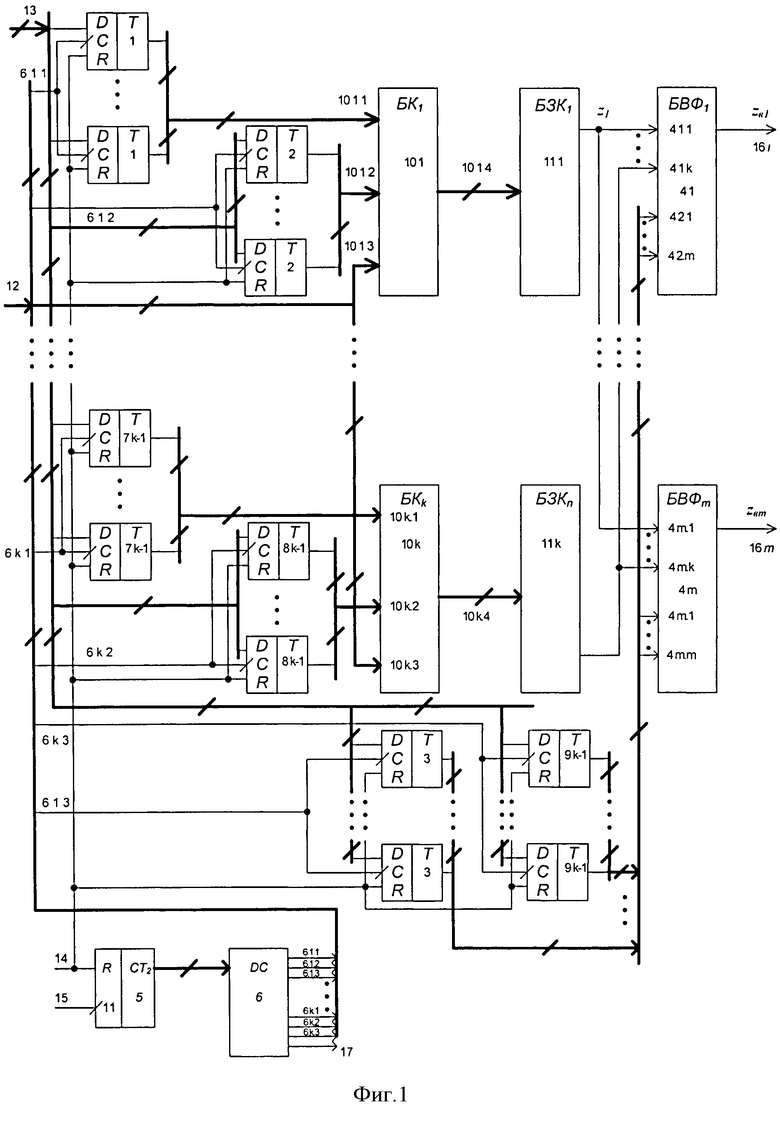

На фиг.4 - схема электрическая функциональная i-го блока вычисления функций.

Программируемое логическое устройство содержит первую 1, вторую 2 и третью 3 группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций 4, где m - число вычисляемых логических функций, счетчик 5, дешифратор 6, k-1 групп первых D-триггеров 7 количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров 8 количеством n, k-1 групп третьих D-триггеров 9 количеством n, группу k блоков конъюнкций 10, группу k блоков значений конъюнкций 11.

Устройство имеет входы задания переменных 12.

Информационные входы D-триггеров из групп 1, 2, 3, 7, 8, 9 D-триггеров подключены к соответствующим разрядам входов данных 13.

Входы сброса всех D-триггеров из групп 1, 2, 3, 7, 8, 9 D-триггеров и вход сброса счетчика 5 объединены и подключены ко входу сброса 14 устройства.

Выход счетчика 5 подключен ко входу дешифратора 6.

Первый выход 6.1.1 дешифратора 6 подключен ко входам синхронизации D-триггеров первой группы D-триггеров 1.

Второй выход 6.1.2 дешифратора 6 подключен ко входам синхронизации D-триггеров второй группы D-триггеров 2.

Третий выход 6.1.3 дешифратора 6 подключен ко входам синхронизации D-триггеров третьей группы D-триггеров 3.

Счетный вход счетчика 5 является входом программирования устройства 15.

Выходы группы m блоков вычисления функций 4 являются выходами устройства 16.

Информационные входы D-триггеров k-1 групп первых D-триггеров 7, вторых D-триггеров 8, третьих D-триггеров 9 подключены к соответствующим разрядам настроечных входов 13.

Входы сброса D-триггеров k-1 групп первых D-триггеров 7, вторых D-триггеров 8, третьих D-триггеров 9 объединены и подключены ко входу сброса 14 устройства.

Входы синхронизации D-триггеров i-ой из k-1 групп первых D-триггеров 7 подключены к соответствующим i-м из k-1 выходов 6.i.1 дешифратора 6 для k-1 групп первых D-триггеров 7.

Входы синхронизации D-триггеров i-ой из k-1 групп вторых D-триггеров 8 подключены к соответствующим i-м из k-1 выходов 6.i.2 дешифратора 6 для k-1 групп вторых D-триггеров 8.

Входы синхронизации D-триггеров i-ой из k-1 групп третьих D-триггеров 9 подключены к соответствующим i-м из k-1 выходов 6.i.3 дешифратора 6 для k-1 групп третьих D-триггеров 9.

Выходы группы первых D-триггеров 1 подключены к первой группе входов 10.1.1 первого блока конъюнкций 10.1.

Выходы группы вторых D-триггеров 2 подключены ко второй группе входов 10.1.2 первого блока конъюнкций 10.1.

Третьи группы входов 10.1.3 всех блоков конъюнкций подключены ко входу задания переменных 12 устройства.

Выходы k-1 групп первых D-триггеров 7 подключены к первым группам входов 10.i.1 соответствующих i-ых из k-1 блоков конъюнкций 10.i (i=2…k).

Выходы k-1 групп вторых D-триггеров 8 подключены ко вторым группам входов 10.i.2 соответствующих i-ых из k-1 блоков конъюнкций 10.i (i=2…k).

Выходы 10.1.4 i-ых блоков конъюнкций 10.i подключены ко входам соответствующих блоков значений конъюнкций 11.i.

Выходы j-ых блоков значений конъюнкций 11.i подключены ко входам конъюнкций 4.j каждого из блоков вычисления функций 4 (j=1…k).

Выходы i-ых D-триггеров из k-1 групп третьих D-триггеров 9 подключены к соответствующим i-ым входам функций 4.2.i (i=1…m) блоков вычисления функций 4.

Устройство имеет выходы значений функций 16.

Последний выход дешифратора 6 является выходом готовности 17 устройства.

Каждый блок i-ый вычисления функций 10.i содержат k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=int log2(n), (n=2k). В первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов.

, где k=int log2(n), (n=2k). В первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов.

Нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.1.j количеством r, где r=2n-1 подключены к соответствующим входам первой группы входов блока вычисления функций 4.1.1, 4.3.1…4.n-1.1. При этом предполагается, что

, 18.1.j количеством r, где r=2n-1 подключены к соответствующим входам первой группы входов блока вычисления функций 4.1.1, 4.3.1…4.n-1.1. При этом предполагается, что  .

.

Четные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.1.j подключены к соответствующим входам 4.2.1, 4.4.1…4.n.1 второй группы входов блока вычисления функций.

, 18.1.j подключены к соответствующим входам 4.2.1, 4.4.1…4.n.1 второй группы входов блока вычисления функций.

Выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.2.j.

, 18.2.j.

Выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.1 подключены к четным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, 18.1 подключены к четным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.2.

, 18.2.

Аналогично выходы нечетных элементов нечетной группы элементов 22·2НЕ-И-ИЛИ, реализующих функцию  , 18.k подключены к нечетным входам следующей группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, 18.k подключены к нечетным входам следующей группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.k+1.

, 18.k+1.

Выходы четных элементов нечетной группы 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.k подключены к четным входам следующей группы элементов ·2·2НЕ-И-ИЛИ, реализующих функцию

, 18.k подключены к четным входам следующей группы элементов ·2·2НЕ-И-ИЛИ, реализующих функцию  , 18.k+1.

, 18.k+1.

Выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 18.k-1.1, 18.k-1.2 содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию

, 18.k-1.1, 18.k-1.2 содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию  .

.

Выход первого элемента предпоследней группы 18.k-1.1 подключен к первому и второму входам единственного элемента последней группы 18.k.

Выход второго элемента предпоследней группы 18.k-1.2 подключен к третьему и четвертому входам единственного элемента последней группы 18.k, выход которого является выходом i-го блока вычисления функций 16.i.

Каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 19-24.

, 19-24.

Входы первых трех элементов 19, 20, 21 объединены, вход первого элемента 19 подключен к соответствующему i-му входу 10.1.3.i третьей группы входов соответствующего блока конъюнкций 10 и к первым двум входам четвертого элемента 22.

Вход второго элемента 20 подключен к соответствующему i-му входу 10.1.1.i первой группы входов данного блока конъюнкций 10 и к третьему и четвертому входам четвертого элемента 23.

Вход третьего элемента 21 подключен к соответствующему i-му входу 10.1.2.i второй группы входов блока конъюнкций 10 и ко второму входу шестого элемента 24, выход которого является i-м выходом 10.1.4.i i-го блока конъюнкций 10.

Выход первого элемента 19 подключен к первому и третьему входам пятого элемента 23.

Выход второго элемента 20 подключен ко второму и четвертому входам пятого элемента 23.

Выход третьего элементам 21 подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента 24.

Выход пятого элемента 23 подключен к четвертому входу шестого элемента 24. Каждый i-ый блок значений конъюнкций 11 содержит k групп n-1 пирамидально соединенных элементов 25, 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=int log2(n), (n=2k), и дополнительный элемент 26.

, где k=int log2(n), (n=2k), и дополнительный элемент 26.

Первый и второй входы элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 25.1 подключены к соответствующим нечетным входам блока значений конъюнкций 10.1.4.

, 25.1 подключены к соответствующим нечетным входам блока значений конъюнкций 10.1.4.

Третий и четвертый входы элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 25.1 подключены к соответствующим четным входам блока значений конъюнкций 10.1.4.

, 25.1 подключены к соответствующим четным входам блока значений конъюнкций 10.1.4.

Выходы нечетных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 25.k подключены к нечетным входам четной группы 24.k+1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, 25.k подключены к нечетным входам четной группы 24.k+1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  .

.

Выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 25.k подключены к четным входам четной группы 25.k+1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, 25.k подключены к четным входам четной группы 25.k+1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  .

.

Выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , 25.k-1 содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию

, 25.k-1 содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию  , 25.k-1.1, 25.k-1.2 и выход первого элемента предпоследней группы 25.k-1.1 подключен к первому и второму входам единственного элемента последней группы 25.k.

, 25.k-1.1, 25.k-1.2 и выход первого элемента предпоследней группы 25.k-1.1 подключен к первому и второму входам единственного элемента последней группы 25.k.

Выход второго элемента предпоследней группы 25.k-1.2 подключен к третьему и четвертому входам единственного элемента последней группы 25.k, выход которого подключен ко всем входам дополнительного элемента 26, выход которого является выходом данного i-го блока значений конъюнкций 11.1.i.

Первая группа D-триггеров 1 и k-1 групп первых D-триггеров 7 (фиг.1) количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций предназначены для записи и хранения в процессе вычислений информации настройки k n-разрядных основных масок для выделения существенных переменных (ХО) с целью обеспечения вычислений в k блоках конъюнкций 10.

Запись в j-e триггеры D-триггеров этих групп 1, 7 осуществляется с соответствующих j-x разрядов настоечных входов 13 по переднему фронту сигнала "1" на выходе 6.j.1 дешифратора 6 j=1…k.

D-триггеры этих групп 1, 7 обнуляются по входу обнуления 14. Настроечная информация, записанная в D-триггерах этих групп 1,7, управляет входами настройки 10.1.1-10.k.1 k блоков конъюнкций 10.1-10.k и определяет реализуемые в конъюнкциях существенные переменные.

D-триггеры этих групп 1, 7 могут быть реализованы, например, на интегральных микросхемах 155ТМ2 с дополнительными инверторами по входу R.

Вторая группа D-триггеров 2 и k-1 групп вторых D-триггеров 8 (фиг.1) количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций предназначены для записи и хранения в процессе вычислений информации настройки k n-разрядных дополнительных масок не инверсных существенных переменных (XD) с целью обеспечения вычислений в k блоках конъюнкций 10.

Запись в j-e триггеры D-триггеров этих групп 2, 8 осуществляется с соответствующих j-x разрядов настоечных входов 13 по переднему фронту сигнала "1" на выходе 6.j.2 дешифратора 6, j=1…k.

D-триггеры этих групп 2, 8 обнуляются по входу обнуления 14. Настроечная информация, записанная в D-триггерах этих групп 2, 8, управляет входами настройки 10.1.2-10.k.2 k блоков конъюнкций 10.1-10.k и определяет реализуемые в конъюнкциях существенные неинверсные переменные.

D-триггеры этих групп 2, 8 могут быть реализованы, например, на интегральных микросхемах 155ТМ2 с дополнительными инверторами по входу R.

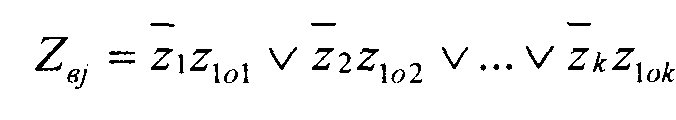

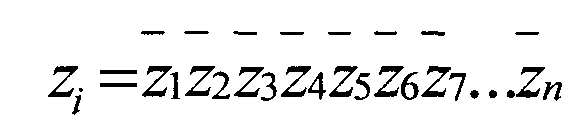

Третья группа D-триггеров 3 и k-1 групп третьих D-триггеров 9 (фиг.1) количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций предназначены для записи и хранения в процессе вычислений информации настройки k n-разрядных масок выходных функций (ZB), указывающих, какие функции системы функций активирует данная конъюнкция для обеспечения вычислений в блоках вычисления функций 4.

Запись в j-e триггеры D-триггеров этих групп 3, 9 осуществляется с соответствующих j-x разрядов настоечных входов 13 по переднему фронту сигнала "1" на выходе 6.j.3 дешифратора 6, j=1…k.

D-триггеры этих групп 3, 9 обнуляются по входу обнуления 14. Настроечная информация, записанная в D-триггерах этих групп 3, 9, управляет входами настройки 4.2.1-4.2.m m блоков вычисления функций 4, m≤n и указывает, какие функции системы функций активирует данная конъюнкция для обеспечения вычислений в блоках вычисления функций 4.

D-триггеры этих групп 3, 9 могут быть реализованы, например, на интегральных микросхемах 155ТМ2 с дополнительными инверторами по входу R.

Блоки вычисления функций 4 предназначены для вычисления значений логических функций в системе функций по результатам вычислений в блоках значений конъюнкций 11, используя настроечную информацию в D-триггерах групп 3, 9 по k входам конъюнкций 4.j.1…4.j.k, где j - номер блока вычисления функций 4 из блоков 4.1…4.j…4.m, m≤n.

Счетчик 5 предназначен для управления дешифратором 6 в режиме программирования. Предварительно счетчик 5 обнуляется по входу сброса 14. Счетчик 5 принимает импульсы со входа программирования 15. Счетчик 5 может быть реализован, например, на интегральной микросхеме 155ИЕ2.

Дешифратор 6 предназначен для управления входами синхронизации D-триггеров групп D-триггеров 1, 2, 3, 7, 8, 9 по информации со счетчика 5.

По первому импульсу программирования на выходе счетчика 5 устанавливается информация, приводящая к установлению "1" на выходе 6.1.1 дешифратора 6, по второму - на выходе 6.1.2, по третьему - на выходе 6.1.3 и так далее, за 3.k импульсов обеспечивается активирование всех 3.k выходов дешифратора, при этом информация записывается в D-триггеры групп 1, 2, 3, 7, 8, 9.

По последнему 3.k 1-му импульсу программирования устанавливается "1" на последнем выходе дешифратора 6, что приводит к возбуждению выхода окончания программирования 17 и означает готовность снятия значений функций с выходов 16.1…16.m.

Дешифратор 6 может быть реализован, например, на интегральной микросхеме 155ИД3, причем ее входы управления необходимо подключить к "0" В.

Блоки конъюнкций 10 в количестве k, где k - количество конъюнкций в вычисляемой системе логических функций, с предлагаемой структурой и соответствующими связями предназначены для вычисления каждого разряда данной конъюнкции по соответствующему разряду входного вектора с использованием логических элементов 2·2НЕ-И-ИЛИ, реализующих функцию  ,

,

Третья группа входов 10.i.3 каждого i-го блока конъюнкций 10.i является входами переменных устройства 12.

Блоки значений конъюнкций 11 в количестве k, где k - количество конъюнкций в вычисляемой системе логических функций, с предлагаемой структурой и соответствующими связями предназначены для вычисления значений конъюнкций по соответствующим результатам вычисления всех ее разрядов в блоках конъюнкций с использованием логических элементов 2·2НЕ-И-ИЛИ, реализующих функцию  ,

,

Входы 12 переменных разрядностью n предназначены для приема входных переменных (входного вектора) и передачи его на третью группу входов всех блоков конъюнкций.

Настроечные входы 13 (входы данных) разрядностью n предназначены для приема настроечной информации - k основных (XOi), дополнительных (XDi) масок и маски выходных сигналов (ZBi), i=1…k с целью записи этой информации в триггеры групп 1, 2, 3, 7, 8, 9 для обеспечения вычислений систем логических функций по соответствующим конъюнкциям.

Вход сброса 14 предназначен для приема импульса обнуления устройства для обнуления D-триггеров групп 1, 2, 3, 7, 8, 9 и счетчика 5.

Вход программирования 15 предназначен для приема импульсов программирования, управляющих счетчиком 5.

Группа m выходов значений функций 16.1-16.m предназначена для выдачи значений m логических функций, вычисленных в блоках вычисления функций 4.1-4.m.

Выход окончания программирования 17 предназначен для выдачи сигнала окончания программирования с последнего выхода дешифратора 6, по которому внешним устройствам разрешается принимать результаты вычислений.

В каждом j-м блоке 4.j вычисления функций k групп 18.1…18.k n-1 пирамидально соединенных элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=int log2(n), (n=2k), предназначены для вычисления соответствующей j-й выходной функции

, где k=int log2(n), (n=2k), предназначены для вычисления соответствующей j-й выходной функции

по результатам вычислений в блоках значений конъюнкций, когда результат вычисления соответствующей i-ой конъюнкции в i-м блоке значения конъюнкций равен нулю:

(zi=0),

конъюнкция равна единице, и эта конъюнкция входит в соответствующую функцию системы логических функций:

(zioo=1).

Эти элементы могут быть реализованы, например, так, как описано в патенте №2438234 от 27.12.2011 г.

В каждом блоке конъюнкций 10n элементов 19-24, 2·2НЕ-И-ИЛИ, реализующих функцию  , предназначены для вычисления функции

, предназначены для вычисления функции

Выделения путем конъюнкции с соответствующим разрядом основной маски (о) значащих бит во входном векторе, и суммирования по модулю два значения этого i-го бита, если он значащий, с дополнительной маской (d).

В каждом i-м блоке значений конъюнкций 11 k групп 25.1…25.k n-1 пирамидально соединенных элементов 25, 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=int log2(n),(n=2k), и дополнительный элемент 26 предназначены для вычисления функции

, где k=int log2(n),(n=2k), и дополнительный элемент 26 предназначены для вычисления функции

равной единице, когда по всем разрядам zi данной n-разрядной конъюнкции получены «нули», то есть соответствующая конъюнкция покрывает входной вектор (равна единице или истинна).

Программируемое логическое устройство работает в следующих режимах: 1) программирования (или запись); 2) вычисления при отсутствии отказов; 3) вычисления при наличии отказов.

В режиме программирования (или настройки) устройство работает следующим образом.

В исходном состоянии D-триггеры групп 1, 2, 3, 7, 8, 9, счетчик 5 обнулены по входу сброса 14 устройства (фиг.1).

По первому импульсу, поступающему на вход программирования 15 устройства, счетчик 5 переходит в первое состояние и на выходе 6.1.1 дешифратора 6 появляется сигнал "1". По этому сигналу информация программирования, предварительно поданная на входы данных 13 с помощью внешних по отношению к устройству технических средств, записывается в D-триггеры группы 1. Информация в D-триггеры группы 1 заносится с их входов D по фронту сигнала, поступающего с выхода 6.1.1 дешифратора 6.

После этого с помощью внешних по отношению к устройству технических средств на входы 13 подается информация программирования второй группы D-триггеров 2, в которые она и записывается по второму импульсу программирования, поступающему на вход 15 устройства, по фронту сигнала "1", возникающему на выходе 6.1.2 дешифратора 6.

По третьему импульсу программирования активируется выход 6.1.3 дешифратора 6 и настроечная информация с входов данных 13, предварительно поданная внешними техническими средствами, записывается по D входам в соответствующие D-триггеры третьей группы 3.

Аналогично происходит запись настроечной информации (информации программирования) в D-триггеры группы 7, 8, 9.

По последнему импульсу программирования на последнем, отдельном выходе дешифратора 6, то есть на выходе 17 окончания программирования, устанавливается "1", свидетельствующий о завершении режима программирования и готовности к вычислениям.

При очередном цикле программирования производится предварительное обнуление устройства по входу обнуления 14, вследствие чего счетчик 5 будет вновь установлен в нулевое, исходное состояние и на выходе 17 появится "0".

В режиме вычислений при отсутствии отказов устройство работает следующим образом.

После фиксации внешними по отношению к заявляемому устройству техническими средствами сигнала готовности на выходе 17 устройства, эти внешние технические средства подают на вход 12 задания переменных входной вектор и затем считывают с выходов 16 устройства значения вычисленных логических функций заданной настройкой системы функций.

Информация на входы 12 задания переменных может быть подана и во время программирования и до него, но считывание информации со входов 16 должно производиться внешними техническими средствами только после формирования устройством сигнала «1» на выходе 17.

При этом предполагается, что внешние технические средства начнут считывание вычисленных значений 16 после завершения переходных процессов в блоках 10, 11, 4.

Вычисления производятся путем реализации в блоках 10, 11, 4 соответствующих указанных выше логических функций.

Вычисления могут производиться и в тестовом режиме.

Например, путем сравнениям результатов вычислений с эталонными в процессе выполнения описываемых вычислений. Это может быть выполнено, например, по отдельным конъюнкциям - проверяя правильность вычисления каждой конъюнкции путем задания соответствующих констант, вызывающих активацию всех выходных функций. Например, целесообразны тесты «бегущая отдельная переменная, входящая во все функции», «бегущая инверсия отдельной переменной, входящая во все функции», «конъюнкция всех переменных, входящая во все функции», «конъюнкция инверсий всех переменных, входящая во все функции», «конъюнкция перемежающихся переменных, входящая во все функции». Здесь имеется некоторая аналогия с тестированием ОЗУ.

В режиме вычислений при наличии отказов устройство работает следующим образом.

В случае непрохождения теста по отдельным конъюнкциям или функциям может быть принято решение об их исключении с использованием соответствующей настроечной информации, при этом количество реализуемых конъюнкций (функций) снижается, что должно быть учтено внешним оборудованием.

В крайнем случае, вычисления могут производиться на работоспособном оборудовании одной конъюнкции (один блок 10 и соответствующий блок 11) и одной функции (блок 4). При этом внешнее оборудование обеспечивает чередование циклов программирования и вычислений с фиксацией и интерпретацией промежуточных результатов вычислений. Сначала вычисляется одна функция по отдельным соответствующим ей конъюнкциям, потом следующая и так далее.

Рассмотрим примеры конкретного выполнения вычислений систем логических функций в программируемом логическом устройстве.

1. Пример вычисления системы логических функций.

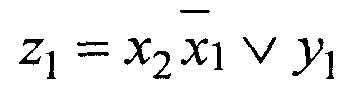

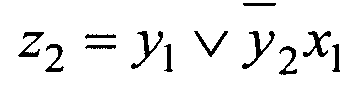

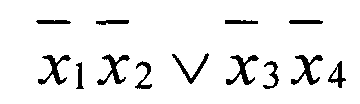

Пусть нужно вычислить следующую систему логических функций:

Составим список конъюнкций и возбуждаемых ими функций:

1)

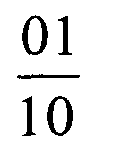

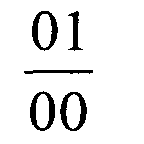

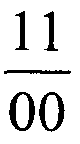

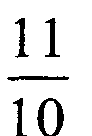

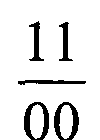

База (зафиксированная последовательность) входных переменных - y1 x2 x1, база выходных переменных - z1 z2. Получим список (массив) констант.

Основная константа X0i (i у нас от 1 до 3 - три конъюнкции) должна выделять существенные переменные, поэтому она содержит единицы в позициях существенных переменных i-й конъюнкции (позиции определяются базой полного входного слова).

Дополнительная константа XDi соответствует значениям истинности переменных в данной конъюнкции, поэтому она содержит единицы в позициях неинверсированных переменных и нули в остальных позициях.

Для возбуждения выходных функций необходима третья маска - маска выходов ZOi, которая содержит единицы в позициях логических функций, в которые входит соответствующая конъюнкция (позиции определяются базой выходных функций). Итак, получим таблицу 1:

Рассмотрим, как производятся вычисления. Это - усовершенствованная аппаратная реализация алгоритма PLA (Алексенко А.Г., Голицын А.А., Иванников А.Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах. - М.: Радио и связь, 1984. - С.109-111).

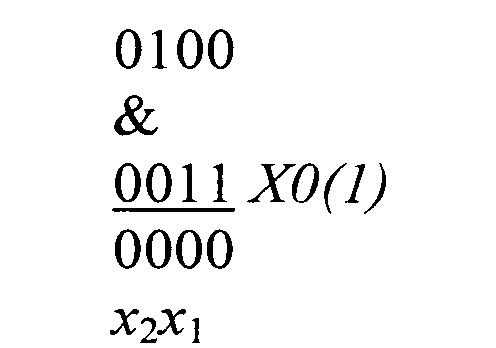

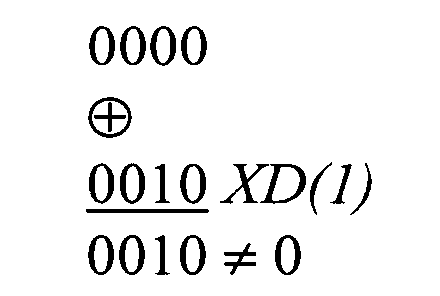

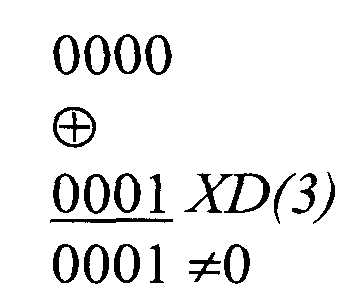

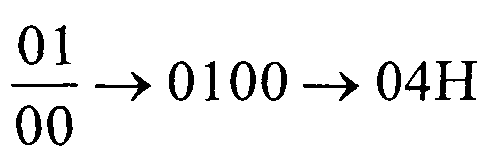

Пусть входное слово y2y1x2x1=0100. В первом блоке конъюнкций входное слово поразрядно маскируется первой, основной маской (константой):

И выполняется поразрядная операция сложения по модулю 2 с дополнительной маской:

Результат ненулевой: это значит, что конъюнкция  . Действительно, из входного слова видно, что, x2=0, x1=0. Это же видно и из результатов маскирования первой константы. А вторая константа показывает, что x1 должен быть равен 0, x2=1.

. Действительно, из входного слова видно, что, x2=0, x1=0. Это же видно и из результатов маскирования первой константы. А вторая константа показывает, что x1 должен быть равен 0, x2=1.

Поэтому на выходе первого блока значений конъюнкций будет ноль и соответствующий бит третьей маски (выходов) для этой конъюнкции игнорируется.

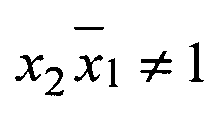

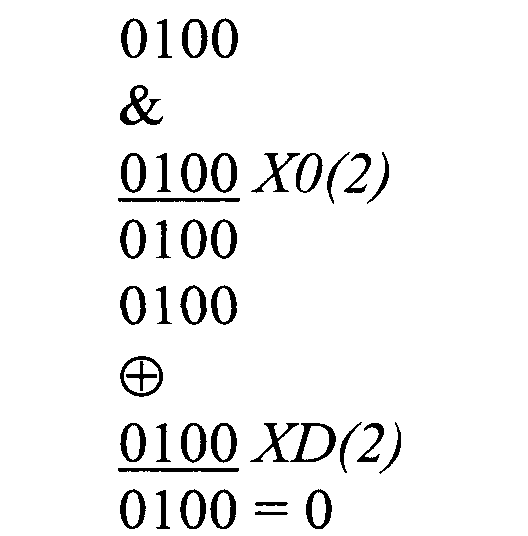

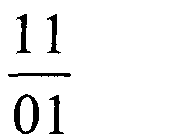

Во втором блоке конъюнкций:

Результат нулевой, значит, конъюнкция y1=1 и на выходе второго блока значений конъюнкций формируется единица.

Поэтому в двух последних блоках вычисления функций формируются единицы, так как значение маски Z(2)=0011, то есть вторая конъюнкция возбуждает и первую функцию, и вторую.

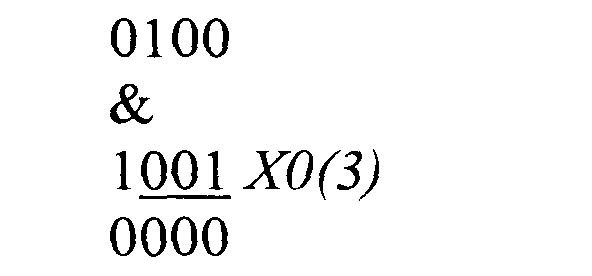

В третьем блоке конъюнкций:

Результат ненулевой, поэтому на выходе третьего блока значений конъюнкций - ноль и третья маска Z(3) в блоках вычисления функций игнорируется.

В шестнадцатеричном коде массив программирования устройства выглядит следующим образом:

03Н, 02Н, 02Н, 08Н, 08Н, 03Н, 06Н, 06Н, 02Н.

Этот массив загружается в D-триггеры групп 1, 2, 3, 7, 8, 9 в процессе программирования.

2. Пример реализации конечного автомата.

При реализации (вычислении) системы логических функций конечного автомата его код состояния необходимо хранить во внешнем по отношению к устройству оборудовании (необходимы внешние триггеры или регистр). Рассмотрим пример реализации такой системы функций, причем для простоты не будем производить минимизацию функций.

Пусть дана таблица переходов-выходов некоторого автомата-распознавателя Мили (таблица 2).

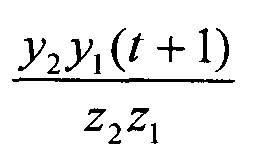

Пусть база входного слова имеет вид y2y1(t)ab(подаются на входы 12), база выходного слова y2y1(t+1)z2z1 (формируются на выходах 16).

Ниже приведена таблица констант, которая получена на основе таблицы переходов выходов TABL:

db 0FH,01H,04H,

db 0FH,02H,02H,

db 0FH,04H,06H,

db 0FH,05H,04H,

db 0FH,07H,0CH,

db 0FH,0DH,0EH,

db 0FH,0FH,0CH,

db 0FH,0EH,0DH.

Рассмотрим подробнее, как они получены, на примере первой тройки констант. Первая константа 00FH одинакова для всех конъюнкций: существенны младшие 4 разряда разряды, т.к. база входного слова y2y1(t)ab. Входные переменные ab - 2 младших разряда, затем идут два разряда, хранящие код состояния памяти автомата Y2Y1.

Следующие константы - код клетки с ненулевым содержимым (например 01Н). Последнюю константу получают следующим образом. Берут содержимое клетки, объединяют числитель и знаменатель и переводят его в шестнадцатеричный код:  . Аналогично получают остальные константы. Этот массив из троек констант загружается в D-триггеры групп 1, 2, 3, 7, 8, 9 в процессе программирования.

. Аналогично получают остальные константы. Этот массив из троек констант загружается в D-триггеры групп 1, 2, 3, 7, 8, 9 в процессе программирования.

В блоках 4 формируются значения y2y1(t+1)z2z1. Функции y2y1(t+1) записываются во внешний регистр, из которого переменные состояния y2y1 передаются на соответствующие входы 12.

3. Пример диагностирования устройства.

Рассмотрим для простоты устройство с n=4, m=4, k=4.

Предлагается тест «бегущая единица» - таблица 3:

Каждая конъюнкция, состоящая из одной переменной, активирует «свою» функцию. На выходах устройства 16 - все единицы. Предлагается тест «бегущий ноль» - таблица 4:

Каждая конъюнкция, состоящая из одной инверсной переменной, активирует «свою» функцию. На выходах устройства 16 - все единицы.

Предлагается тест «все единицы» - таблица 5:

Каждая конъюнкция, состоящая из всех переменных, активирует «свою» функцию. На выходах устройства 16 - все единицы.

Предлагается тест «все нули» - таблица 6:

Каждая конъюнкция, состоящая из инверсий всех переменных, активирует «свою» функцию. На выходах устройства 16 - все единицы.

Аналогично можно предложить тесты по каждой конъюнкции, проверяющие, как данная конъюнкция активирует все функции, например, для первой конъюнкции - таблицы 7-8:

Первая конъюнкция, состоящая из всех переменных, активирует все функции. На выходах устройства 16 - все единицы.

Первая конъюнкция, состоящая из инверсий всех переменных, активирует все функции. На выходах устройства 16 - все единицы.

Аналогично могут быть предложены и другие тесты.

4. Пример парирования отказов.

Устройство может парировать отказы вычисления конъюнкций - блоков 10, 11, выявленные путем вышеописанного диагностирования. Для этого дефектная конъюнкция, соответствующая, например, z1 в выражении

отключается путем задания, например, z1o1=0, при этом число реализуемых конъюнкций уменьшается на одну.

В крайнем случае, когда остаются технические средства для всего одной работоспособной конъюнкции, устройство может быть использовано для программно-аппаратного вычисления за несколько тактов, используя внешние технические средства, путем чередования циклов программирования каждой очередной конъюнкции и вычислений соответствующих ей функций.

Устройство может парировать отказы вычисления функций в блоках 4 путем исключения этой функции, при этом число выходных функций уменьшается.

В крайнем случае, когда остаются технические средства для всего одной работоспособной функции (всего один блок 4), устройство может быть использовано для программно-аппаратного вычисления за несколько тактов, используя внешние технические средства, путем чередования циклов программирования конъюнкций и вычисления соответствующей им функции. То есть за один цикл вычисляться будет только одна функция, возможно, зависящая от многих конъюнкций.

Возможна также работа на одной из двух оставшихся работоспособных доль блоков 4, путем отключения отказавшей (не формирующей необходимую единицу) сигналами zioi=0, zi.

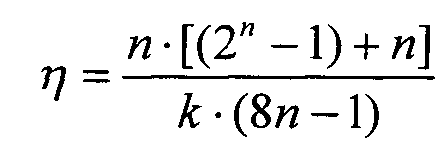

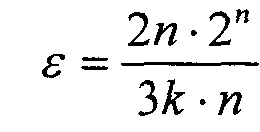

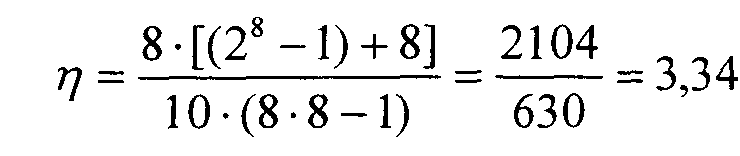

Оценим технико-экономическую эффективность предлагаемого устройства.

В прототипе для реализации n блоков функций (берем n=m) необходимо n·[(2n-1)+n], где (2n-1) - количество элементов для реализации мультиплексора на 2n каналов, (+n) - количество элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , для инверсий переменных элементов. Кроме того, необходимо по 2n·2n триггеров настройки.

, для инверсий переменных элементов. Кроме того, необходимо по 2n·2n триггеров настройки.

В предлагаемом устройстве для реализации n-разрядного блока конъюнкции необходимо 6 элементов на одну переменную 6 n, n-1 элемент для блока значений конъюнкции n элементов для блока вычисления функции.

Если имеется k конъюнкций (берем n=m), то всего будет:

k(6n+n-1+n)=k(8n-1)

Триггеров настройки необходимо 3 kn.

Таким образом, выигрыш в количестве элементов описывается выражением:

Выигрыш в количестве триггеров описывается выражением:

.

.

Так, если n=m=8, k=10, получаем:

Достижение технического результата изобретения подтверждается приведенными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

| Матричное устройство для быстрого поиска вхождений и обработки данных | 2022 |

|

RU2787742C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2020 |

|

RU2726497C1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в отказоустойчивой аппаратуре. Техническим результатом является сокращение аппаратных затрат при реализации систем логических функций большого количества переменных. Устройство содержит группы D-триггеров, блоки вычисления функций, счетчик, дешифратор, блоки конъюнкций, блоки значений конъюнкций, при этом блоки вычисления функций, блоки конъюнкций, блоки значений конъюнкций реализованы на базе логических элементов 2·2НЕ-И-ИЛИ, реализующих функцию  . 4 ил., 8 табл.

. 4 ил., 8 табл.

Программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций, где m - число вычисляемых логических функций, счетчик, дешифратор, причем информационные входы D-триггеров из групп D-триггеров подключены к соответствующим разрядам входов данных, входы сброса всех D-триггеров всех групп D-триггеров и вход сброса счетчика объединены и подключены ко входу сброса устройства, выход счетчика подключен ко входу дешифратора, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы D-триггеров, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы D-триггеров, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы D-триггеров, выходы группы m блоков вычисления функций являются выходами устройства, каждый блок вычисления функций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=intlog2(n),(n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, где k=intlog2(n),(n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , отличающееся тем, что дополнительно введены k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам блоков значений функций, причем нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, отличающееся тем, что дополнительно введены k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам блоков значений функций, причем нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2НЕ-И-ИЛИ, реализующих функцию  , подключены к третьим входам соответствующих элементов второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к третьим входам соответствующих элементов второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены ко вторым входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены ко вторым входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию

, содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию  , и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-й блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-й блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блок а конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-й блок значений конъюнкций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блок а конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-й блок значений конъюнкций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , где k=intlog2(n),(n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, где k=intlog2(n),(n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , подключены к четным входам четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к четным входам четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию

, содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию  , и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций.

, и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Программируемое логическое устройство | 1987 |

|

SU1444892A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Способ монтажа ротора турбогенератора на электростанции | 1983 |

|

SU1162747A1 |

| Плазменная горелка | 1980 |

|

SU1046982A1 |

| US 6188240 B1, 13.02.2001. | |||

Авторы

Даты

2014-01-10—Публикация

2012-04-26—Подача