Изобретение относится к электросвязи и может использоваться в узлах коммутации пакетов (сообщений) сети передачи данных (сети ПД) автоматизированной децентрализованной системы управления (АСУ).

Заявленное изобретение расширяет арсенал средств данного назначения.

Известен аналог децентрализованного управления коммутируемой сетью связи (см. , например, а.с. СССР 756670, Н 04 М 9/00, заявл. 1978 г., опубл. 1980 г.).

Известное устройство децентрализованного управления коммутируемой сетью связи содержит регистр приема-передачи, блок выбора направлений и блок памяти. Однако аналог имеет недостатки. Система динамического управления сетью связи, созданная с использованием аналога, недостаточно адаптирована к изменениям структуры сети.

Известен аналог децентрализованного управления коммутируемой сетью связи (см. , например, а.с. СССР 756670, Н 04 М 9/00, заявл. 1978 г., опубл. 1980. А.с. СССР 794775, H 04 q 9/00, заявл. 1979 г., опубл. 1981 г.).

Известный аналог построен с использованием регистра приема-передачи, блока сравнения, блока анализа длины пакета, блока коррекции и адресного блока. Однако известное устройство имеет невысокое быстродействие.

Наиболее близким по технической сущности к заявленному является устройство децентрализованного управления коммутируемой сетью связи а.с. СССР 555558, МПК 6 Н 04 М 9/00, заявл. 16.10.75, опубл. 25.04.77. Известное устройство содержит регистр приема-передачи, блок выбора направлений, блок памяти, адресный блок, блок управления, блок анализа длины пути, блок коррекции и блок сравнения.

Блок выбора направлений последовательно соединен с блоком памяти, второй вход которого соединен с адресным блоком, а выход с вторым входом блока выбора направлений. К управляющему входу блока выбора направлений своим выходом подключен блок управления, который также соединен с входом адресного блока. Блок коррекции последовательно соединен с блоком сравнения, к второму входу которого подключен блок анализа длины пути, соединенный с выходом регистра приема-передачи. Второй выход регистра приема-передачи подключен к блоку коррекции, при этом выход блока сравнения соединен с вторым входом блока выбора направлений. Второй выход блока выбора направлений подключен к третьему входу блока сравнения, а второй выход блока коррекции соединен с вторым входом регистра приема-передачи, первый вход которого является информационным.

При использовании нового устройства уменьшается объем служебной информации между станциями коммутации в процессе управления, повышается пропускная способность информационных каналов в сравнении с рассмотренными аналогами.

Недостатком прототипа является относительно низкая пропускная способность сети из-за значительного объема передаваемой служебной информации для обеспечения возможности коррекции маршрутно-адресной таблицы.

Целью изобретения является разработка устройства децентрализованного управления распределением пакетов сообщений в сети передачи данных, обеспечивающего повышение пропускной способности сети за счет уменьшения объемов служебной информации, которая будет передаваться только при структурных изменениях сети и снижении качества каналов передачи данных от узла коммутации к смежным узлам, и повышение степени адаптации сети при ее структурных и качественных изменениях.

Для достижения сформулированной цели в известное устройство децентрализованного управления коммутируемой сетью связи, содержащее регистр приема-передачи, блок выбора направлений, блок памяти, адресный блок, блок сравнения, где вход регистра приема-передачи является информационным входом устройства, выход блока памяти соединен с входом блока выбора направлений, сигнальный выход блока сравнения соединен с входом считывания блока памяти, дополнительно введены блок анализа пакета, первый и второй элементы ИЛИ, первая группа N элементов И, где N≥2. Информационный вход блока анализа пакета соединен с информационным входом регистра приема-передачи, вход записи которого соединен с управляющим выходом блока анализа пакета, первый и второй адресные выходы которого соединены соответственно с первым и вторым входами первого элемента ИЛИ. Первый адресный выход блока анализа пакета соединен с первым адресным входом блока сравнения, второй адресный вход которого соединен с выходом адресного блока. Сигнальный выход блока сравнения соединен с вторым входом второго элемента ИЛИ и первым входом первого элемента И, а управляющий выход блока сравнения соединен с первым входом второго элемента ИЛИ и вторым входом второго элемента И. Сигнальный и информационный выходы блока анализа пакета соединены соответственно с сигнальным и информационным входами блока памяти, выход первого элемента ИЛИ соединен с адресным входом блока памяти. Выход второго элемента ИЛИ соединен с входом считывания регистра приема-передачи и сигнальным входом блока анализа пакета. Выход регистра приема-передачи соединен с вторым входом первого элемента И и первым входом второго элемента И, выход которого является выходом устройства в направлении оконечного оборудования данных. Выход первого элемента И соединен со вторыми входами первой группы элементов И, первые входы которых соединены с соответствующими N выходами блока выбора направлений. Выходы первой группы N элементов И являются соответствующими N выходами устройства.

Блок анализа пакета включает в себя первый и второй электронные коммутаторы, соединенные входы которых являются информационным входом блока анализа пакета. Информационный и тактовый выходы первого электронного коммутатора являются соответственно информационным и тактовым входами первого регистра сдвига. Информационный и тактовый выходы второго электронного коммутатора являются соответственно информационным и тактовым входами второго регистра сдвига. Адресный выход первого регистра сдвига является вторым адресным выходом блока анализа пакета и одновременно является входом третьего элемента ИЛИ. Информационный выход первого регистра сдвига является информационным выходом блока анализа пакета. Выход третьего элемента ИЛИ является управляющим выходом блока анализа пакета, а также входом элемента задержки и второго входа второго элемента ИЛИ, первый вход которого является сигнальным входом блока анализа пакета. Адресный выход второго регистра сдвига является первым адресным выходом блока анализа пакета. Информационный выход второго регистра сдвига является входом декодера, выход которого является сигнальным выходом блока анализа пакета и первым входом первого элемента ИЛИ. Вторым входом первого элемента ИЛИ является выход элемента задержки. Выход первого элемента ИЛИ является R входом первого регистра сдвига, а выход второго элемента ИЛИ является R-входом второго регистра сдвига.

Благодаря новой совокупности существенных признаков за счет использования при коммутации пакетов текущего значения весовых коэффициентов каждого маршрута, хранящихся в блоке памяти маршрутно-адресной таблицы, изменяющейся только при структурных изменениях сети и снижении качества каналов передачи данных, достигается сокращение объема служебной информации, передаваемой при корректировке маршрутно-адресных таблиц, и сокращается время на обработку информационных и служебных пакетов, что ведет к увеличению пропускной способности сети.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявленное устройство поясняется чертежами:

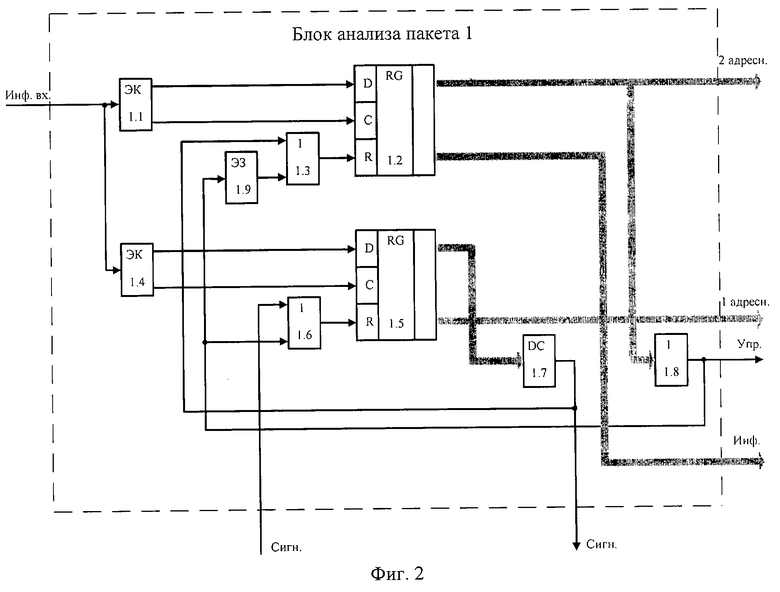

фиг.1 - функциональная схема устройства;

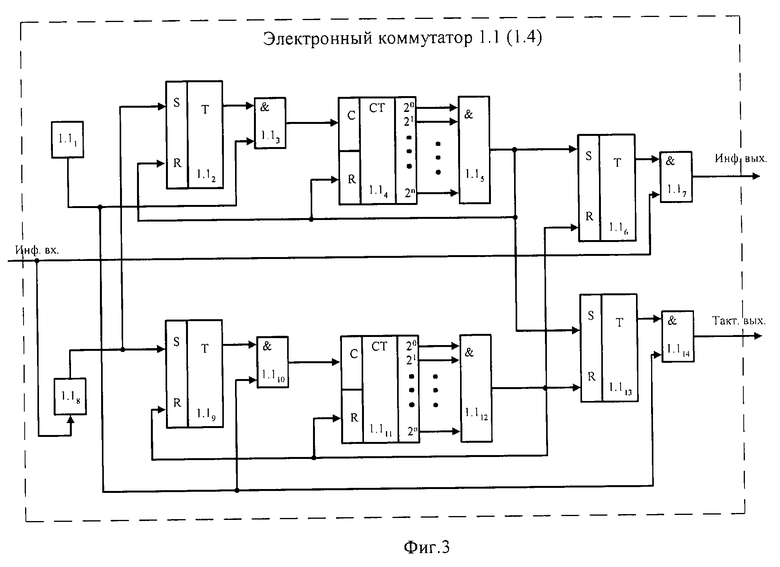

фиг.2 - схема блока анализа пакетов;

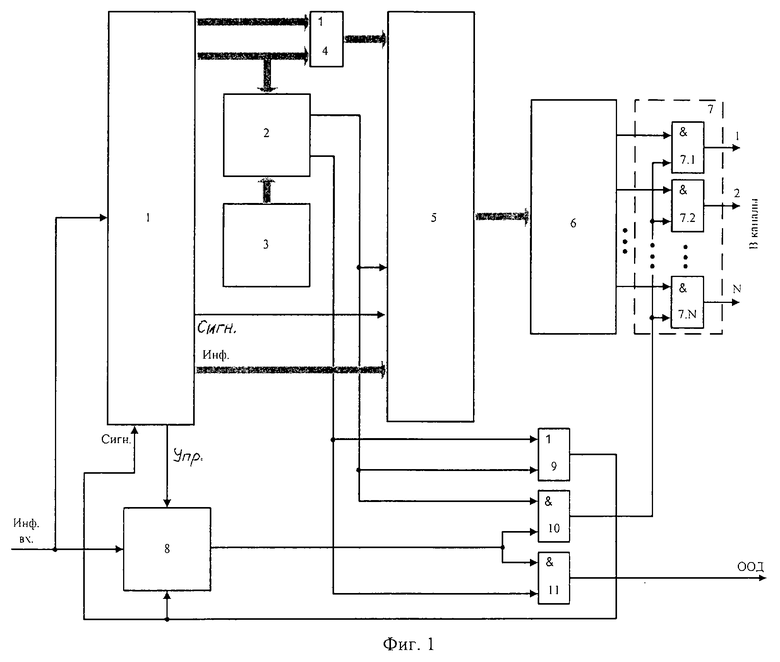

фиг.3 - схема электронного коммутатора.

Устройство децентрализованного управления распределением пакетов сообщений в сети передачи данных, показанное на фиг.1, состоит из блока анализа пакета 1, блока сравнения 2, адресного блока 3, первого 4 и второго 9 элементов ИЛИ, блока памяти 5, блока выбора направлений 6, первой группы N элементов И 7, регистра приема передачи 8, первого 10 и второго 11 элементов И.

Вход регистра приема-передачи 8 является информационным входом устройства, выход блока памяти 5 соединен с входом блока выбора направлений 6, сигнальный выход блока сравнения 2 соединен с входом считывания блока памяти 5. Информационный вход блока анализа пакета 1 соединен с информационным входом регистра приема-передачи 8, вход записи которого соединен с управляющим выходом блока анализа пакета 1, первый и второй адресные выходы которого соединены соответственно с первым и вторым входами первого элемента ИЛИ 4. Первый адресный выход блока анализа пакета 1 соединен с первым адресным входом блока сравнения 2, второй адресный вход которого соединен с выходом адресного блока 3. Сигнальный выход блока сравнения 2 соединен с вторым входом второго элемента ИЛИ 9 и первым входом первого элемента И 10, а управляющий выход блока сравнения 2 соединен с первым входом второго элемента ИЛИ 9 и вторым входом второго элемента И 11. Сигнальный и информационный выходы блока анализа пакета 1 соединены соответственно с сигнальным и информационным входами блока памяти 5. Выход первого элемента ИЛИ 4 соединен с адресным входом блока памяти 5. Выход второго элемента ИЛИ 9 соединен с входом считывания регистра приема-передачи 8 и сигнальным входом блока анализа пакета 1. Выход регистра приема-передачи соединен с вторым входом первого элемента И 10 и первым входом второго элемента И 11, выход которого является выходом устройства в направлении оконечного оборудования данных. Выход первого элемента И 10 соединен со вторыми входами первой группы элементов И 7, первые входы которых соединены с соответствующими N выходами блока выбора направлений 6. Выходы первой группы N элементов И 7 являются соответствующими N выходами устройства.

Блок анализа пакета 1 (фиг.2), входящий в данное устройство, предназначен для определения принадлежности пакета к служебной или информационной категории и выдачи команд соответственно на изменение маршрутно-адресной информации или передачи информационного пакета к получателю. Он состоит из первого 1.1 и второго 1.4 электронного коммутатора, первого 1.2 и второго 1.5 регистров сдвига, первого 1.3 второго 1.6 и третьего 1.8 элементов ИЛИ, декодера 1.7 и элемента задержки 1.9.

Объединенный вход первого 1.1 и второго 1.4 электронного коммутаторов является информационным входом блока анализа пакета. Информационный и тактовый выходы первого электронного коммутатора 1.1 являются соответственно информационным и тактовым входами первого регистра сдвига 1.2. Информационный и тактовый выходы второго электронного коммутатора 1.4 являются соответственно информационным и тактовым входами второго регистра сдвига 1.5. Адресный выход первого регистра сдвига 1.2 является вторым адресным выходом блока анализа пакета и также входом третьего элемента ИЛИ 1.8. Информационный выход первого регистра сдвига 1.2 является информационным выходом блока анализа пакета 1. Выход третьего элемента ИЛИ 1.8 является управляющим выходом блока анализа пакета 1, а также входом элемента задержки 1.9 и второго входа второго элемента ИЛИ 1.6, первый вход которого является сигнальным входом блока анализа пакета 1. Адресный выход второго регистра сдвига 1.5 является первым адресным выходом блока анализа пакета 1. Информационный выход второго регистра сдвига 1.5 является входом декодера 1.7, выход которого является сигнальным выходом блока анализа пакета 1 и первым входом первого элемента ИЛИ 1.3. Вторым входом первого элемента ИЛИ 1.3 является выход элемента задержки 1.9. Выход первого элемента ИЛИ 1.3 является R-входом первого регистра сдвига 1.2, а выход второго элемента ИЛИ 1.6 является R-входом второго регистра сдвига1.5.

Электронные коммутаторы 1.1 (1.4), входящие в блок анализа пакета 1, предназначены для выделения адреса из заголовка пакета. Одним из вариантов реализации может быть схема, показанная на фиг.3, которая состоит из формирователя импульсов 1.11 (1.41), триггеров 1.12, 1.16, 1.19, 1.113 (1.42, 1.46, 1.49, 1.413), элементов И 1.13, 1.15, 1.17, 1.110, 1.112, 1.114 (1.43, 1.45, 1.47, 1.410, 1.412, 1.414), счетчиков 1.14, 1.111 (1.44, 1.411), причем объединенные входы формирователя импульсов 1.18 (1.48) и элемента И 1.17 (1.47) являются информационно-адресным входом электронного коммутатора 1.1 (1.4), выход формирователя импульсов 1.18 (1.48) соединен с S-входами первого и третьего триггеров 1.12 (1.42) и 1.19 (1.49), выход генератора тактовых импульсов 1.11 (1.41 соединен с тактовыми входами элементов И 1.13, 1.110, 1.114 (1.43, 1.410, 1.414), выход триггера 1.12 (1.42) связан с сигнальным входом элемента И 1.13 (1,43), а выход элемента И 1.13 0.43) соединен со счетным входом счетчика 1.14 (1.14). Выходы счетчика 1.14 (1.44) подключены к соответствующим входам элемента И 1.15 (1.45), выход которого соединен с S-входами триггеров 1.16 (1.46) и 1.113 (1.413) и R-входами триггера 1.12 (1.42), счетчика 1.14 (1.44). Выход триггера 1.16 (1.46) подключен к управляющему входу элемента И 1.17 (1.47), выход которого является информационным выходом электронного коммутатора 1.1 (1.4).

Выход триггера 1.19 (1.49) связан с сигнальным входом элемента И 1.110 (1.410), выход которого подключен к счетному входу счетчика 1.111 (1.411), выходы которого соединены с соответствующими входами элемента И 1.112 (1.412), выход которого соединен с R-входами триггеров 1.16, 1.19, 1.113 (1.46, 1.49, 1.413) счетчика 1.111 (1.411). Выход триггера 1.113 (1.113) подключен к сигнальному входу элемента И 1.114 (1.114), выход которого является тактовым выходом электронного коммутатора 1.1 (1.4).

Блок сравнения 2 предназначен для сравнения кодовых комбинаций. Может быть реализован по схеме, описанной - Импульсные цифровые устройства. / И.О. Лебедев, А. М. Сидоров. - Л.: ВАС, 1980, с.51, рис.2.33, 2.34, на ИМС серий 133, 564.

Адресный блок 3 и блок памяти 5 предназначены для долговременного хранения информации и могут быть реализованы как перепрограммируемое постоянное запоминающее устройство, известное и описанное - Лебедев О.Н. Микросхемы памяти и их применение -М.: Радио и связь, 1990. -160 с. Могут быть реализованы на ИМС серий КР 558 PP.

Блок выбора направлений 6 предназначен для формирования сигнала логической единицы на одном из выходов в соответствии с кодом, представляет собой демультиплексор и может быть реализован по схеме, описанной - Цифровые интегральные микросхемы: Справочник. / П. П. Мальцев, Н.С. Долидзе, М.И. Критенко и др. - М: Радио и связь, 1994, с.32, на ИМС серий 555.

Регистр приема-передачи 8 предназначен для хранения информации и может быть реализован как оперативное запоминающее устройство, известное и описанное - Популярные цифровые микросхемы: справочник. /В.Л. Шило - Челябинск: Металлургия, 1989, с.161.

Первый 1.2 и второй 1.5 регистры сдвига, входящие в блок анализа пакета 1, предназначены для преобразования информации путем ее сдвига под воздействием сдвигающих (тактовых) импульсов. Может быть реализован по схеме, описанной - Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова -СПВВИУС, 1995, рис.5.28, с.158-159.

Декодер 1.7, входящий в блок анализа пакета 1, предназначен для формирования сигнала логического уровня при поступлении на его вход соответствующей кодовой комбинации, известен и описан - Основы цифровой техники. / Л. А. Мальцева - М.: Радио и связь, 1986, - рис.21, с.30.

Элемент задержки 1.9, входящий в блок анализа пакета 1, предназначен для задержки сигнала. Может быть реализован на базе регистра сдвига, известен и описан - Цифровые интегральные микросхемы: Справочник. / П.П.Мальцев и др. -М.: Радио и связь 1994, с.52.

Генератор тактовых импульсов 1.11, входящий в электронный коммутатор 1.1 (1.4), описан в работе "Микросхемы и их применение". Справ. пособие. (1984, - с. 213, рис.7.6). Может быть реализован на интегральных микросхемах (ИМС) серий 16.101, 176.

Счетчики 1.14, 1.111 (1.44, 1-411), входящие в электронный коммутатор 1.1 (1.4), описаны в работе "Основы импульсной и цифровой техники". (Под общей ред. А. М. Сидорова СПВВИ-УС, 1995, - рис.5.38, с.169-172).

RS-триггеры 1.12, 1.16, 1.19, 1-113 (1-42, 1.46, 1.49, 1.413), входящие в электронный коммутатор 1.1 (1.4), известны и описаны, например, в книге: Батушев В. А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение: Справ. пособие. - М.: Радио и связь 1984, - с.122, рис.4.16. Могут быть реализованы на ИМС серий 133, 564.

Формирователь импульсов 1.18 (1.48), входящий в электронный коммутатор 1.1 (1.4), предназначен для формирования из логического уровня короткого импульса. Может быть реализован по схеме, описанной - Мальцева Л.А. и др. Основы цифровой техники. - М.: Радио и связь, 1986, - рис.21, с.30.

Логические элементы ИЛИ 4, 9, 1.3, 1.6, 1.8, входящие в описываемое устройство, блок анализа пакета 1, идентичны, известны и описаны, например, в книге: Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова. -СПВВИУС, 1995, - рис.2.4, с.39-41.

Логические элементы И 7.1-7.N, 10, 11, 1.13, 1.15, 1.17, 1.110, 1.112, 1.114 (1.43, 1.45, 1.47, 1.410, 1.412, 1.414), входящие в описываемое устройство, блок анализа пакета 1, электронный коммутатор 1.1 (1.4), идентичны, известны и описаны в книге: Мальцева Л.А., Фромберг Э.М. Основы цифровой техники - М. : Радио и связь, 1986. - с.21. Могут быть реализованы на ИМС серий 133 и 564.

Устройство работает следующим образом. При поступлении пакета на информационный вход устройства (фиг.1) данный пакет поступает одновременно на информационные входы блока анализа пакета 1 и регистр приема-передачи 8. Если поступивший в устройство пакет информационный (это становится известным в результате анализа первого символа заголовка пакета в блоке анализа пакета 1), то с управляющего выхода блока анализа пакета 1 сигнал с уровнем логической единицы поступает на вход записи регистра приема-передачи 8 (при этом данный пакет записывается в регистр приема-передачи 8 до принятия решения о выборе направления его дальнейшей передачи). Одновременно в блоке анализа пакета 1 осуществляется выделение адреса получателя, находящегося в заголовке поступившего пакета. Выделенная кодовая комбинация адреса с первого адресного выхода блока анализа пакета 1 поступает одновременно на первый адресный вход блока сравнения 2 и (через первый элемент ИЛИ 4) на адресный вход блока памяти 5. Если выделенный адрес совпадает с адресом данного устройства (то есть кодовая комбинация адреса в заголовке поступившего пакета совпадает с кодовой комбинацией собственного адреса данного устройства, хранящейся в адресном блоке 3), то сигнал с уровнем логической единицы с управляющего выхода блока сравнения 2 открывает второй элемент И 11, а также через второй элемент ИЛИ 9 поступает на вход считывания регистра приема-передачи 8 (в результате пакет в последовательном коде считывается через открытый второй элемент И 11 в направлении оконечного оборудования данных собственного для данного устройства абонента) и на сигнальный вход блока анализа пакета 1 для перевода его в исходное состояние.

Если адрес, содержащийся в заголовке поступившего пакета, не совпадает с собственным адресом данного устройства, то сигнал с уровнем логической единицы с сигнального выхода блока сравнения 2 поступает на вход считывания блока памяти 5, а также открывает первый элемент И 10 и, кроме того, через второй элемент ИЛИ 9 поступает на вход считывания регистра приема-передачи 8 (при этом пакет в последовательном коде считывается через открытый первый элемент И 10 и поступает одновременно на вторые входы первой группы элементов И 7) и на сигнальный вход блока анализа пакета 1 для перевода его в исходное состояние.

По сигналу считывания блок памяти 5 преобразует адрес получателя, поступивший на его адресный вход, в кодовую комбинацию дальнейшего направления передачи пакета, которая с выхода блока памяти 5 поступает на вход блока выбора направлений 6. При этом сигнал с уровнем логической единицы, появляющийся на соответствующем выбранному (i-му) направлению выходе блока выбора направлений 6, открывает соответствующий элемент И первой группы элементов И 7, при этом пакет по i-му каналу передачи данных передается следующему устройству, включенному в маршрут доведения данного пакета.

Если поступивший в устройство пакет не информационный, а служебный, то пакет в регистр приема-передачи 8 не записывается. При этом в блоке анализа пакета 1 осуществляется обработка текстовой части служебного пакета (выделение оптимального вектора). Выделенный из текстовой части адрес устройства-отправителя оптимального вектора с второго адресного выхода блока анализа пакета 1 поступает на адресный вход блока памяти 5. Одновременно с сигнального выхода блока анализа пакета 1 сигнал с уровнем логической единицы поступает на вход записи блока памяти 5, при этом принятый оптимальный вектор с информационного выхода блока анализа пакета 1 поступает на информационный вход блока памяти 5 и записывается в него по адресу, указанному в принятом служебном пакете (то есть осуществляется корректировка маршрутно-адресной информации, касающейся устройства, отославшего служебный пакет соседним с ним устройствам).

Блок анализа пакета 1, функциональная схема которого приведена на фиг.2, работает следующим образом.

При появлении в канале пакета включаются два электронных коммутатора 1.1 и 1.4. При этом электронный коммутатор 1.4 обеспечивает запись в регистр сдвига 1.5 кодовых комбинаций признака информационного пакета и адреса получателя, выделяемых из заголовка пакета. Если пакет информационный, то кодовая комбинация признака информационного пакета, поступающая на вход декодера 1.7, вызывает появление на выходе последнего сигнала с уровнем логической единицы, поступающего на сигнальный выход блока анализа пакета 1 и (через первый элемент ИЛИ 1.3) на вход R регистра сдвига 1.2 (тем самым запрещается запись в регистр сдвига 1.2 текстовой части пакета). При этом кодовая комбинация адреса получателя поступает на первый адресный выход блока анализа пакета 1, также с этого выхода (через блок сравнения 2, второй элемент ИЛИ 9) сигнал с уровнем логической единицы (через второй элемент ИЛИ 1.6) поступает на вход R регистра сдвига 1.5 (переводя регистр сдвига 1.5 в исходное состояние).

Если пакет служебный, то выделяемая электронным коммутатором 1.1 текстовая часть пакета записывается в регистр сдвига 1.2, при этом на второй адресный выход блока анализа пакета 1 поступает адрес отправителя служебного пакета, который, кроме того, через третий элемент ИЛИ 1.8 в виде сигнала с уровнем логической единицы поступает на управляющий выход блока анализа пакета 1, на вход R регистра сдвига 1.5 (через второй элемент ИЛИ 1.6) и через элемент задержки 1.9 и первый элемент ИЛИ 1.3 на вход R регистра сдвига 1.2. Одновременно на информационный выход блока анализа пакета 1 поступает новый вектор от отправителя служебного пакета.

Электронный коммутатор 1.1 (1.4), функциональная схема которого приведена на фиг.3, работает следующим образом.

При поступлении пакета на информационный вход блока анализа пакета 1 он поступает на информационный вход первого 1.1 и второго 1.4 электронного коммутатора, показанных на фиг.3. При этом импульс с генератора тактовых импульсов открывает элементы И 1.13, 1.110, 1.114, а импульсы с выхода формирователя импульсов 1.18 (1.48) переводят RS-триггеры 1.12, 1.19 (1.42, 1.49) в единичное состояние. В результате последовательность тактовых импульсов через открытые элементы И 1.13, 1.110 (1.43, 1.410) поступает на счетные входы С счетчиков 1.14 1.111 (1.44 1.411). Счетчик 1.14 (1.44) отсчитывает количество символов заголовка, предшествующих символам адреса, затем сигналом с уровнем логической единицы через элемент 1.15 (1.45) переводит RS-триггер 1.12 (1.42) в нулевое состояние (поступление тактовых импульсов на вход счетчика 1.14 (1.44) прекращается), а RS-триггеры 1.16, 1.113 (1.46, 1.413) - в единичное, при этом через открытый элемент И 1.17 (1.47) на информационный выход первого 1.1 и второго 1.4 электронного коммутатора поступает последовательность символов заголовка пакета, а через открытый элемент И 1.114 (1.414) на тактовые выходы блоков поступает последовательность тактовых импульсов.

Счетчик 1.111 (1.411), закончив отсчет количества символов, предшествующих символам адреса, и количества символов самого адреса, выдает сигнал с уровнем логической единицы через элемент 1.112 (1.412) на выходы R RS-триггеров 1.16, 1.19, 1.111, 1.113 (1.46, 1.49, 1.411, 1.413) и переводит их в нулевое состояние. При этом поступление информации и тактовых импульсов на выходы первого 1.1 и второго 1.4 электронного коммутатора прекращаются.

Для корректировки маршрутно-адресной таблицы в прототипе используются служебные пакеты, включающие в себя адрес отправителя, данные о количестве транзитов, информацию об изменении в маршрутно-адресной таблице и адрес получателя, при этом пакеты передаются от узла отправителя к узлам, в направлении которых произошло изменение порядка выбора маршрута передачи. В предлагаемом устройстве при изменении маршрутно-адресной таблицы служебный пакет включает в себя признак "служебный", координаты изменяемого показателя в таблице маршрутов и величину данного показателя и передается только смежным узлам коммутации, при этом объем служебной информации сокращается в 1,5-2 раза. При получении служебного пакета сравниваются новый (полученный после коррекции маршрутно-адресной таблицы) и старый оптимизационные вектора данной таблицы, если они идентичны, то информация об изменении выбора маршрутов передачи в сети от данного узла не передается. Тем самым достигается сокращение объема информации служебного пакета и уменьшается нагрузка на маршруты от узла отправителя (обнаружившего изменение).

Предлагаемое устройство при приеме служебного пакета не производит сравнение адреса для определения принадлежности данному узлу, так как передача осуществляется между смежными узлами коммутации и необходимость их адресования отпадает, при этом происходит изменение показателя выбора маршрута по указанным координатам, что значительно снижает время и упрощает процесс обработки служебных пакетов.

Таким образом, совокупность блоков и их взаимосвязанная работа позволяют предлагаемому устройству в отличие от прототипа увеличить пропускную способность сети за счет сокращения объема заголовка и информационной части служебных пакетов, используемых для корректировки маршрутно-адресной таблицы, а также сокращения времени и упрощения процесса их обработки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2001 |

|

RU2211540C2 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2001 |

|

RU2199148C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168870C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2216869C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2148294C1 |

Изобретение относится к вычислительной технике и может использоваться в узлах коммутации пакетов (сообщений) сети передачи данных автоматизированной децентрализованной системы управления. Достигаемый технический результат - увеличение пропускной способности сети, а также сокращение времени и упрощение процесса обработки пакетов. Заявляемое устройство состоит из блока анализа пакета 1, блока сравнения 2, адресного блока 3, двух элементов ИЛИ 4, 9, блока памяти 5, блока выбора направлений 6, первой группы N элементов И 7, регистра приема-передачи 8, двух элементов И 10, 11. 1 з.п. ф-лы, 3 ил.

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| УСТРОЙСТВО КОММУТАЦИИ КАДРОВ | 1991 |

|

RU2048707C1 |

| УСТРОЙСТВО И СПОСОБ КОММУТАЦИИ В РЕЖИМЕ АСИНХРОННОЙ ПЕРЕДАЧИ ДЛЯ ОБЕСПЕЧЕНИЯ ОБСЛУЖИВАНИЯ РЕЧЕВЫХ ВЫЗОВОВ | 1998 |

|

RU2153231C2 |

| Сырьевая смесь для получения теплоизоляционного строительного материала | 1975 |

|

SU539016A1 |

| US 5732080 А, 24.03.1998 | |||

| US 5781549 А, 14.07.1998 | |||

| Крестовидная муфта | 1977 |

|

SU624017A1 |

Авторы

Даты

2003-09-27—Публикация

2002-04-29—Подача