Интегральный каскадный модуль динамической памяти относится к области вычислительной техники и интегральной электроники, а именно к логическим схемам, отличающимся по реализуемой логической операции, в частности к схемам, в которых сигнал на выходе появляется при наличии входного сигнала, только на одном входе.

Известен базовый усилительный элемент дифференциальной динамической логики - триггерный усилитель (см. патент США 4843264, МПК G 01 R 19/00 от 1989 г. ), содержащий триггер на двух инверторах, выполненный на КМОП транзисторах с перекрестными связями, подключенных одноименными выводами пары транзисторов одного типа проводимости к первой шине источника питания, одноименными выводами пары транзисторов другого типа проводимости соединенных с соответствующими первым и вторым входами узла активизации триггера, выход которого подключен ко второй шине источника питания, узел восстановления исходного состояния триггера на двух транзисторах, выводы сток-исток которых объединены с одноименными выводами соответствующих транзисторов того же типа проводимости, инверторов триггера, подключенных к первой шине источника питания, парафазные информационные шины, подключенные к одноименным входам узла активизации триггера, шину синхронизации, подключенную к управляющим входам узла восстановления исходного состояния триггера, выходы инверторов триггера являются парафазными выходами устройства.

Недостатком известного базового усилительного элемента дифференциальной динамической логики - триггерного усилителя являются низкие функциональные возможности, в частности нагрузочная способность, сложность автоматизированного проектирования узлов на основе данного элемента, а также низкое быстродействие и высокое потребление мощности.

Известен также принятый за прототип базовый усилительный элемент дифференциальной динамической логики (см. патент РФ 2154338, МПК Н 03 К 19/06, опубл. 10.08.2000), содержащий триггер на двух инверторах, выполненный на КМОП транзисторах с перекрестными связями, подключенных одноименными выводами пары транзисторов одного типа проводимости к первой шине источника питания, одноименными выводами пары транзисторов другого типа проводимости соединенных с соответствующими первым и вторым входами узла активизации триггера, выход которого подключен ко второй шине источника питания, узел восстановления исходного состояния триггера на двух транзисторах, выводы сток-исток которых объединены с одноименными выводами соответствующих транзисторов того же типа проводимости, инверторов триггера, подключенных к первой шине источника питания, парафазные информационные шины, подключенные к одноименным входам узла активизации триггера, шину синхронизации, подключенную к управляющим входам узлов активизации триггера и восстановления исходного состояния триггера, выходы инверторов триггера являются парафазными выходами устройства, а также введен дополнительный МОП транзистор, а узел активизации триггера выполнен на двух парах последовательно соединенных N-канальных МОП транзисторов, образующих первую и вторую разрядную цепи, входные выводы которых являются соответствующими входами узла активизации триггера, а их выходы подключены к выходу узла активизации триггера, выводы сток-исток дополнительного N-канального МОП транзистора подключены ко входам узла активизации триггера, а его затвор подключен к первой шине источника питания, общие выводы последовательно соединенных транзисторов узла активизации триггера подключены к соответствующим парафазным информационным шинам, а затворы N-канальных МОП транзисторов разрядных цепей соединены с управляющим входом узла активизации триггера.

Недостатком известного базового усилительного элемента дифференциальной динамической логики являются низкие функциональные возможности, в частности нагрузочная способность, сложность автоматизированного проектирования узлов на основе данного элемента, а также низкое быстродействие и высокое потребление мощности.

Технической задачей предлагаемого изобретения является упрощение автоматизированного проектирования узлов, повышение функциональных возможностей с целью использования его для управления различными процессами любой протяженности, увеличение быстродействия при одновременном снижении помехоустойчивости и потерь тока.

Поставленный технический результат достигается тем, что интегральный каскадный модуль динамической памяти, выполненный в виде триггера, согласно изобретению, содержит связанные между собой каскадные звенья, например три, из которых первое и последнее каскадные звенья являются соответственно входным и выходным каскадными звеньями, среднее каскадное звено является промежуточным каскадным звеном, причем входное каскадное звено содержит один модуль динамической памяти, состоящий из двух исполняемых полупроводниковых ключей, снабженных одной общей промежуточной входной шиной управляемого сигнала, двумя выходными промежуточными шинами управляемого сигнала и двумя раздельными шинами управляющего сигнала, каждая из которых связана с одним из упомянутых исполняемых полупроводниковых ключей, количество модулей динамической памяти каждого последующего каскадного звена равно количеству выходных промежуточных шин управляемого сигнала предыдущего каскадного звена, при этом каждое каскадное звено содержит по одной раздельной шине управляющего сигнала на каждый исполняемый полупроводниковый ключ, а исполняемые полупроводниковые ключи выходного каскадного звена коммутируются с помощью выходных промежуточных шин управляемого сигнала к дополнительно установленному устройству, считывающему один из вариантов динамической памяти, например к дешифратору, причем каждая из выходных промежуточных шин управляемого сигнала очередного модуля динамической памяти в каждом каскадном звене соединена с входной промежуточной шиной управляемого сигнала последующего модуля динамической памяти последующего каскадного звена.

Между отличительными признаками и достигнутым техническим результатом существует следующая причинно-следственная связь.

Предлагаемое изобретение "Интегральный каскадный модуль динамической памяти", в отличие от известных аналогов и прототипа, позволит значительно упростить автоматизированное управление узлов и снизить себестоимость за счет уменьшения количества модулей динамической памяти, выполненных в виде триггера, по сравнению со стандартными и известными устройствами представленной памяти и за счет однородности модулей динамической памяти. Кроме того, предлагаемое изобретение позволяет повысить функциональные возможности интегрального каскадного модуля динамической памяти за счет возможности каскадного наращивания интегральных модулей динамической памяти, а также использовать его для управления различными процессами любой протяженности за счет разделения управляемого и управляющего сигналов. За счет однородности интегральных каскадных модулей динамической памяти и их низкого сопротивления, выраженного в сопротивлении исполняемых полупроводниковых ключей, увеличивается быстродействие при одновременном снижении помехоустойчивости и потерь тока.

Повышенные функциональные возможности интегрального каскадного модуля динамической памяти позволяют использовать его для управления различными процессами любой протяженности при незначительной потере тока и большой помехоустойчивости, поскольку независимо от каскадности (количества каскадных звеньев) в предлагаемом каскадном интегральном модуле динамической памяти используются однородные элементы - интегральные модули динамической памяти, что также снижает сложность изделия и упрощает автоматизированное проектирование узлов, не повышает себестоимость.

По имеющимся у заявителя сведениям, совокупность существенных признаков заявляемого изобретения "Интегральный каскадный модуль динамической памяти" не известна из уровня техники, что позволяет сделать вывод о соответствии изобретения критерию "новизна".

По мнению заявителя, сущность заявляемого изобретения не следует явным образом из известного уровня техники, так как из него не выявляется вышеуказанное влияние на достигаемый технический результат - новое свойство объекта - совокупности признаков, которые отличают от прототипа заявляемое изобретение, что позволяет сделать вывод о соответствии изобретения "Интегральный каскадный модуль динамической памяти" критерию "изобретательский уровень".

Совокупность существенных признаков, характеризующих сущность изобретения, может быть многократно использована в производстве интегральных каскадных модулей динамической памяти с получением технического результата, заключающегося в снижении себестоимости за счет упрощения автоматизированного проектирования узлов, повышении функциональных возможностей, улучшении его эксплуатационных качеств и повышении надежности, увеличении быстродействия, что позволяет сделать вывод о соответствии заявляемого изобретения критерию " промышленная применимость".

Сущность заявляемого изобретения поясняется примером конкретного выполнения.

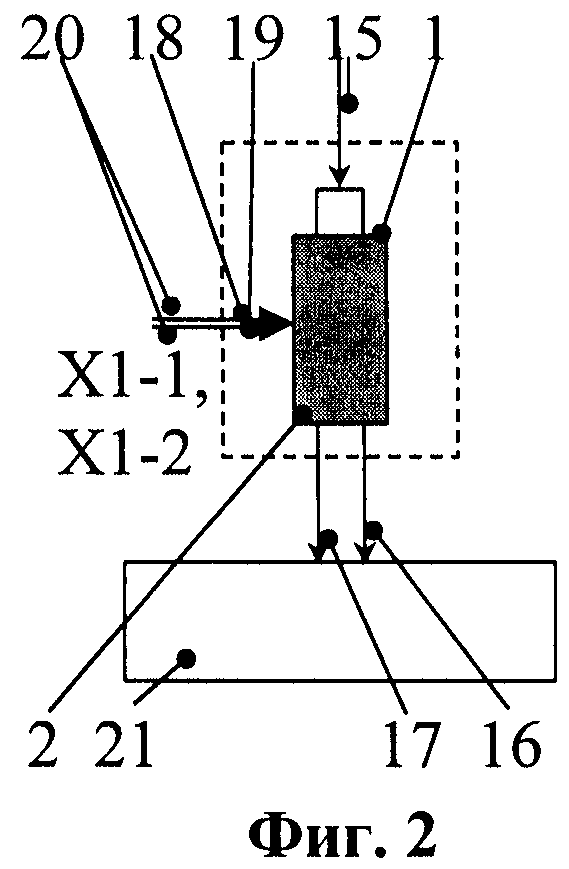

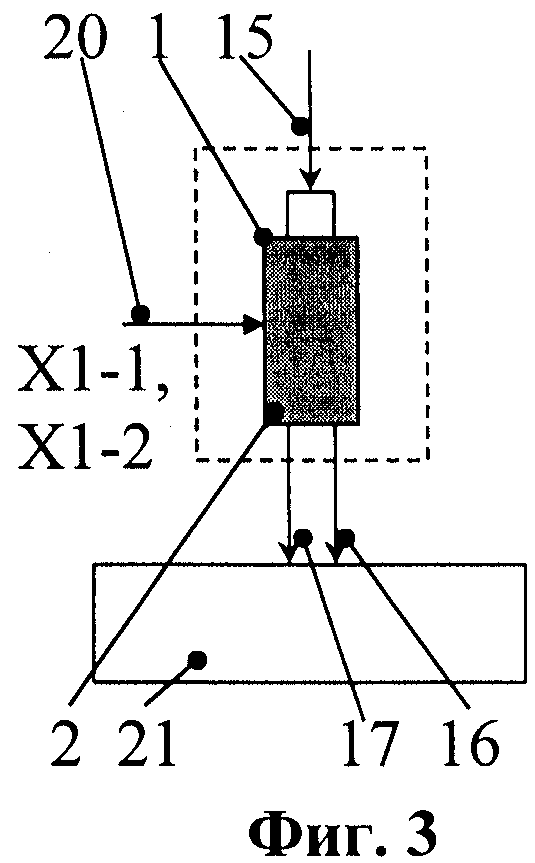

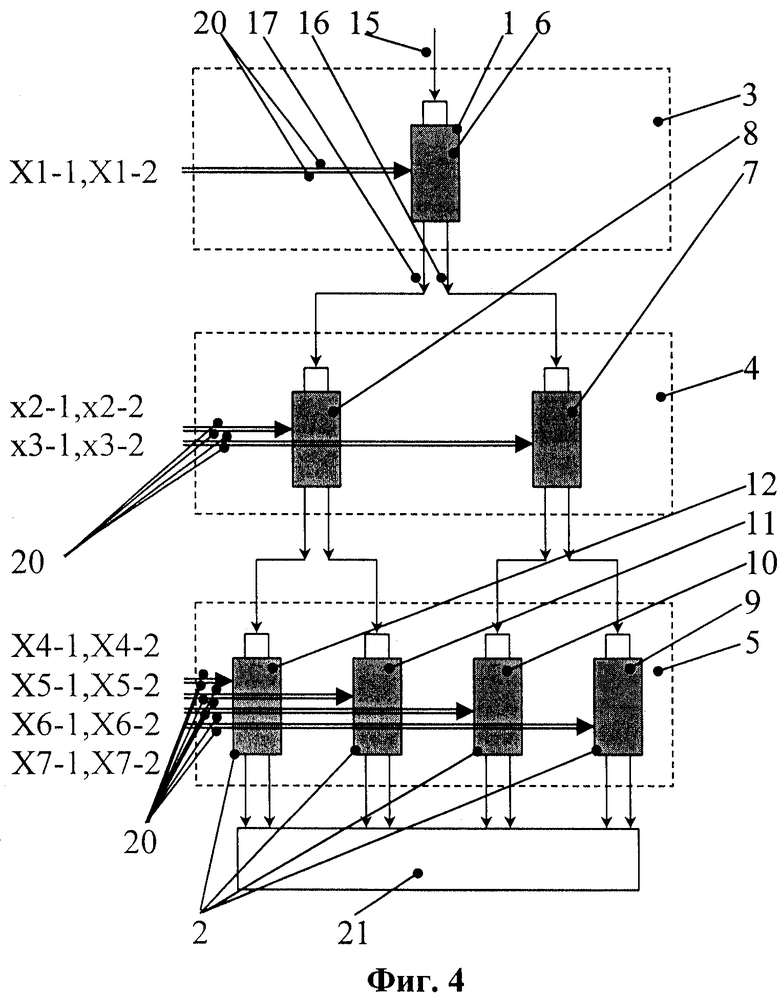

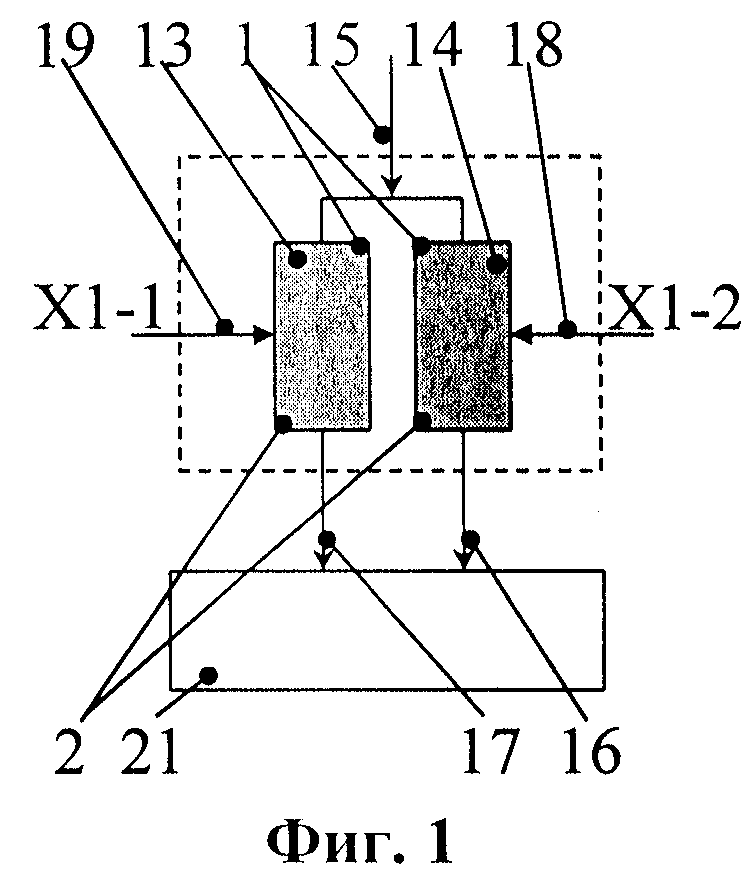

На Фиг. 1, 2, 3 изображен модуль динамической памяти, где фиг.2 и 3 представлены с сокращением изображения фиг. 1 для удобства представлений фигур 4 и 5 соответственно.

На Фиг. 4 изображен интегральный каскадный модуль динамической памяти, состоящий из трех каскадных звеньев, построенный по фиг.2.

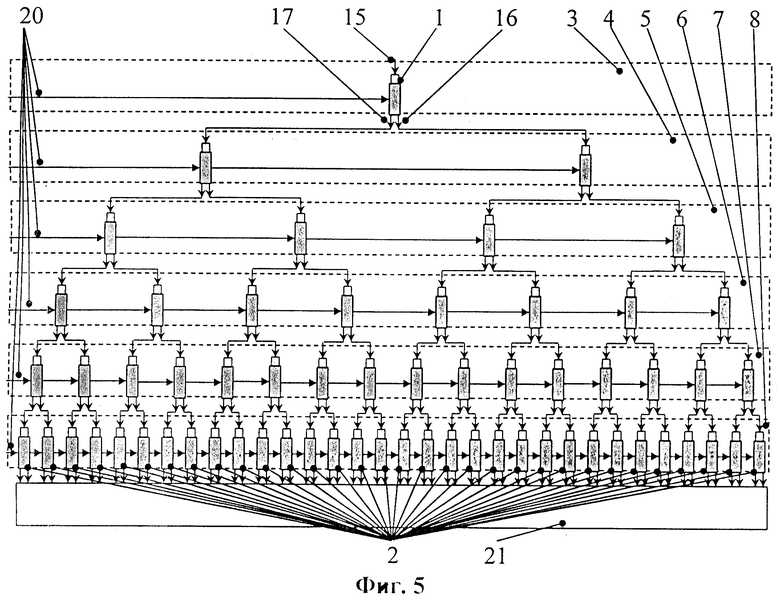

На Фиг. 5 изображен интегральный каскадный модуль динамической памяти, состоящий из шести каскадных звеньев, построенный по фиг.3.

Интегральный каскадный модуль динамической памяти по первому примеру (Фиг. 4) выполнен в виде триггера (А.С. Партин, Популярно о цифровых микросхемах. Свердловск: Средне-уральское книжное издательство, 1989 г., с.40) и содержит одно входное каскадное звено 1 и одно выходное каскадное звено 2. Данный интегральный каскадный модуль динамической памяти состоит из трех каскадных звеньев 3, 4, 5. Первое каскадное звено является одновременно входным каскадным звеном 1, а последнее каскадное звено 5 является одновременно выходным каскадным звеном 2. В данном примере интегральный каскадный модуль динамической памяти состоит из трех упомянутых выше каскадных звеньев 3, 4, 5, которые содержат семь модулей динамической памяти 6, 7, 8, 9, 10, 11, 12, состоящих из однородных модулей, т.е. имеющих одинаковую структуру. Первое каскадное звено 3 содержит один модуль динамической памяти 6, во втором каскадном звене 4 расположены два модуля динамической памяти 7 и 8. В третьем каскаде 5 расположены четыре модуля динамической памяти 9, 10, 11, 12. Каждый из модулей динамической памяти 6, 7, 8, 9, 10, 11, 12 содержит два исполняемых полупроводниковых ключа 13 и 14, одну промежуточную входную 15 и две промежуточные выходные шины 16, 17 управляемого сигнала и две раздельные шины 18 и 19 управляющих сигналов, каждая из которых связана с одним из упомянутых исполняемых полупроводниковых ключей 13 и 14 модуля динамической памяти в каскадном звене. Каждое из каскадных звеньев (фиг.4) 3, 4, 5 содержит (для удобства обозначенных одной позицией 20) раздельные шины 20 управляющих сигналов на все исполняемые полупроводниковые ключи интегральных элементов данных каскадных звеньев.

В первом каскадном звене 3 по раздельной шине 20 управляющего сигнала на исполняемые полупроводниковые ключи 13 и 14 поступают управляющие токи Х1-1 и X1-2. Во втором каскадном звене 4 по раздельной шине 20 управляющего сигнала на исполняемые полупроводниковые ключи 13 и 14 поступают управляющие токи Х2-1, Х2-2, Х3-1 и Х3-2. В третьем каскадном звене 5 по шине 20 управляющего сигнала на исполняемые полупроводниковые ключи 13 и 14 поступают управляющие токи Х4-1, Х4-2, Х5-1, Х5-2, Х6-1, Х6-2, Х7-1 и Х7-2. Исполняемые полупроводниковые ключи 13 и 14 коммутируются в выходном звене 2 к дешифратору 21 (Интегральные микросхемы - справочник под редакцией Б.В. Тарабрина, М. : Радио и связь, 1984 г., стр. 493-494), обеспечивая работу модуля динамической памяти. Каждая из выходных промежуточных шин управляемого сигнала, 16 и 17 очередного модуля динамической памяти в каждом каскадном звене соединена с входной промежуточной шиной управляемого сигнала последующего интегрального модуля динамической памяти следующего каскадного звена.

Работа описанного выше интегрального каскадного модуля динамической памяти осуществляется следующим образом.

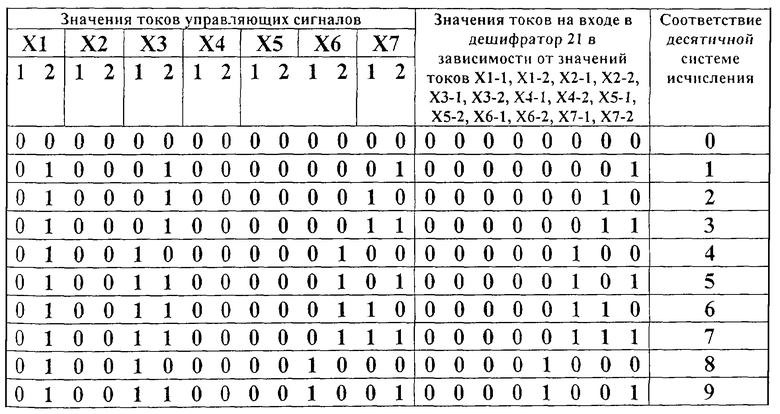

Обозначим наличие управляющих токов в шине 20 первого, второго и третьего каскадных звеньев соответственно логической единицей Х1-1=1 и т.д. до Х7-2=1, а отсутствие управляющих токов в раздельной шине 20 управляющего сигнала первого, второго и третьего каскадных звеньев соответственно логическим нулем Х1-1= 0 и т.д. до Х7-2=0. Таким образом, при наличии управляющего сигнала хотя бы на одном из Х1-1 или Х1-2, управляющий ток поступает хотя бы на один исполняемый полупроводниковый ключ модуля динамической памяти 6 первого каскадного звена 3, а управляемый ток движется в цепи шин 16 и/или 17, и так далее при рассмотрении работы исполняемых полупроводниковых ключей следующих каскадных звеньев. Способы подачи управляющих сигналов в раздельных шинах 20 на исполняемые полупроводниковые ключи модулей динамической памяти всех каскадных звеньев позволяют получить все 256 комбинаций значений динамической памяти, отраженные в таблице 1.

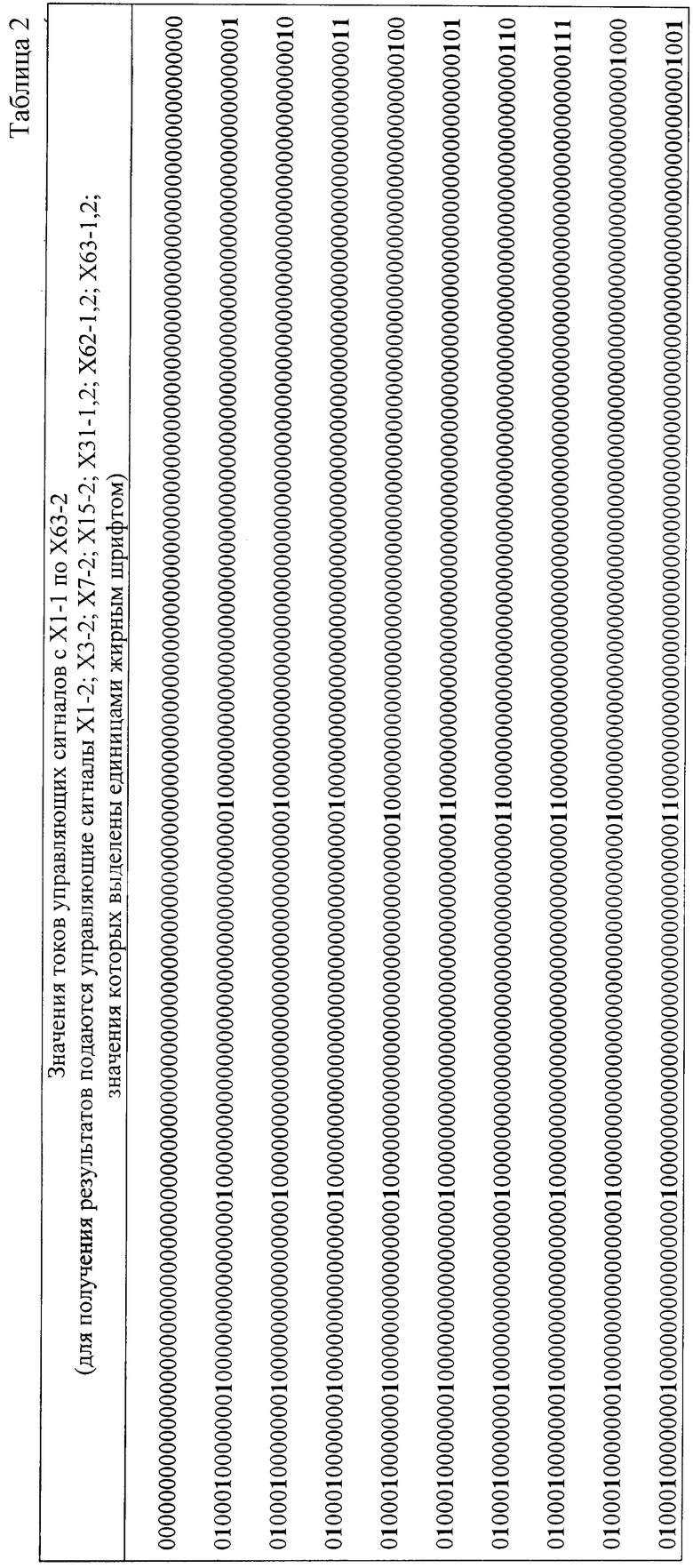

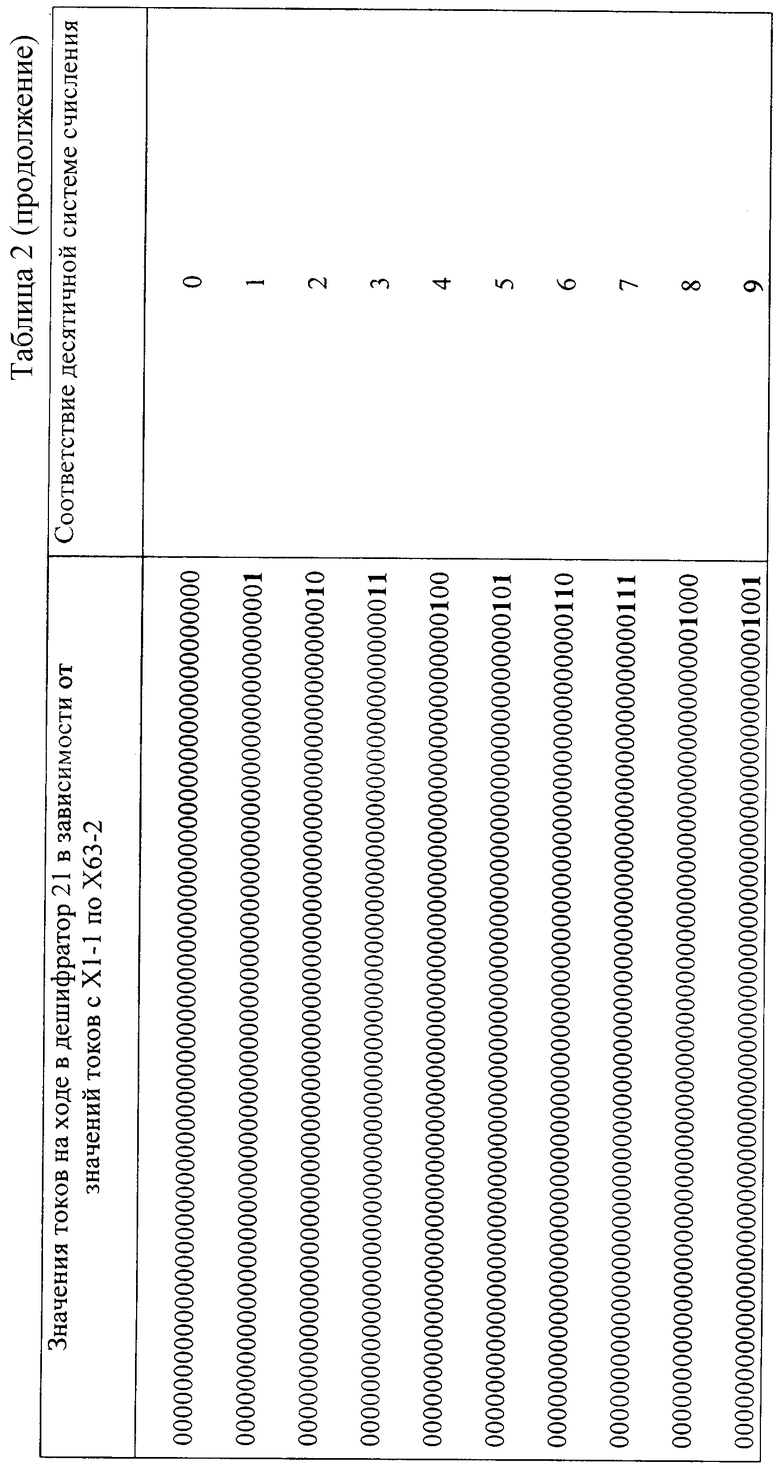

Интегральный каскадный модуль динамической памяти по второму примеру (фиг. 5) содержит одно входное каскадное звено 1 и одно выходное каскадное звено 2 соответственно первого каскадного звена и последнего каскадного звена. В данном примере интегральный каскадный модуль динамической памяти состоит из шести каскадных звеньев 3, 4, 5, 6, 7, 8, которые содержат шестьдесят три модуля динамической памяти, состоящих из однородных элементов, т.е. имеющих одинаковую структуру. Первый каскадный модуль 3 содержит один модуль динамической памяти. Второе каскадное звено 4 содержит два модуля динамической памяти. Третье каскадное звено 5 содержит четыре модуля динамической памяти. Четвертое каскадное звено 6 содержит восемь модулей динамической памяти. Пятое каскадное звено 7 содержит шестнадцать модулей динамической памяти. Шестое каскадное звено 8 содержит тридцать два модуля динамической памяти. Каждый из шестидесяти трех модулей динамической памяти содержит два исполняемых полупроводниковых ключа 13 и 14, а также связанные с ними одну промежуточную входную шину управляемого сигнала, две промежуточные выходные шины 16 и 17 управляемого сигнала и раздельные шины 18 и 19 управляющих сигналов, каждая из которых связанна с одним из упомянутых исполняемых полупроводниковых ключей 13 и 14 модуля динамической памяти в каскадном звене. Каждое каскадное звено 3, 4, 5, 6, 7, 8 содержит раздельные шины 20 управляющих сигналов по одной на каждый исполняемый полупроводниковый ключ всех модулей динамической памяти. Способы подачи управляющих сигналов в раздельных шинах 20 на исполняемые полупроводниковые ключи модулей динамической памяти всех каскадных звеньев позволяют получить все 1,8•1019 комбинаций значений динамической памяти, отраженныx в таблице 2 (1 часть - начало и 2 часть - продолжение).

Работа описанного выше интегрального каскадного модуля динамической памяти осуществляется аналогично первому примеру.

Предлагаемое изобретение "Каскадный интегральный модуль динамической памяти" позволит значительно упростить автоматизированное проектирование узлов и снизить себестоимость, повысить функциональные возможности модуля, использовать его для управления различными процессами любой протяженности, увеличить быстродействие при одновременном снижении помехоустойчивости и потерь тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ КАСКАДНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ "ЯЙЛЕТКАН" | 2001 |

|

RU2215368C2 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| КОМПЛЕМЕНТАРНЫЙ МИКРОЭЛЕКТРОМЕХАНИЧЕСКИЙ ИНВЕРТОР | 2005 |

|

RU2290753C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| СПОСОБ ПОСТРОЕНИЯ МОДУЛЬНОГО ИСТОЧНИКА ПИТАНИЯ ПОВЫШЕННОЙ НАДЕЖНОСТИ И МОДУЛЬНЫЙ ИСТОЧНИК ПИТАНИЯ | 2017 |

|

RU2663238C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| Многопортовая ячейка оперативного запоминающего устройства | 2017 |

|

RU2665248C1 |

| РЕЗЕРВИРОВАННЫЙ ИСТОЧНИК ТОКА | 2013 |

|

RU2512890C1 |

Изобретение относится к вычислительной технике. Технический результат: упрощение автоматизированного проектирования, повышение функциональных возможностей. Интегральный каскадный модуль динамической памяти выполнен в виде триггера и содержит каскадные звенья (КЗ) из интегральных модулей динамической памяти (МДП) и дешифратор (Д), а также содержит входное КЗ, состоящее из одного МДП, выполненного из двух исполняемых полупроводниковых ключей (ИПК), имеющего одну промежуточную входную шину (Ш) управляемого сигнала, две выходные промежуточные Ш управляемого сигнала и две раздельные Ш управляющего сигнала, каждая из которых связана с одним из упомянутых ИПК. Каждая из выходных промежуточных Ш управляемого сигнала очередного МДП в каждом КЗ соединена с входной промежуточной Ш управляемого сигнала МДП последующего КЗ, а ИПК выходного КЗ коммутируются к Д. 5 ил. 2 табл.

Интегральный каскадный модуль динамической памяти, выполненный в виде триггера, содержащий каскадные звенья из интегральных модулей динамической памяти и дешифратор, отличающийся тем, что он содержит входное каскадное звено, состоящее из одного модуля динамической памяти, выполненного из двух исполняемых полупроводниковых ключей, имеющий одну промежуточную входную шину управляемого сигнала, две выходные промежуточные шины управляемого сигнала и две раздельные шины управляющего сигнала, каждая из которых связана с одним из упомянутых исполняемых полупроводниковых ключей, причем каждая из выходных промежуточных шин управляемого сигнала очередного модуля динамической памяти в каждом каскадном звене соединена с входной промежуточной шиной управляемого сигнала модуля динамической памяти последующего каскадного звена, а исполняемые полупроводниковые ключи выходного каскадного звена коммутируются к дешифратору.

| Устройство динамической памяти с фазоимпульным представлением информации | 1970 |

|

SU455373A1 |

| US 4996445, 26.02.1991 | |||

| DE 4024295 А1, 07.02.1991 | |||

| АЛЕКСЕНКО А.Г | |||

| и др | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982,с | |||

| Железнодорожный снегоочиститель на глубину до трех сажен | 1920 |

|

SU263A1 |

| БУКРЕЕВ И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Радио и связь, 1990, с 286. | |||

Авторы

Даты

2003-12-10—Публикация

2001-08-14—Подача