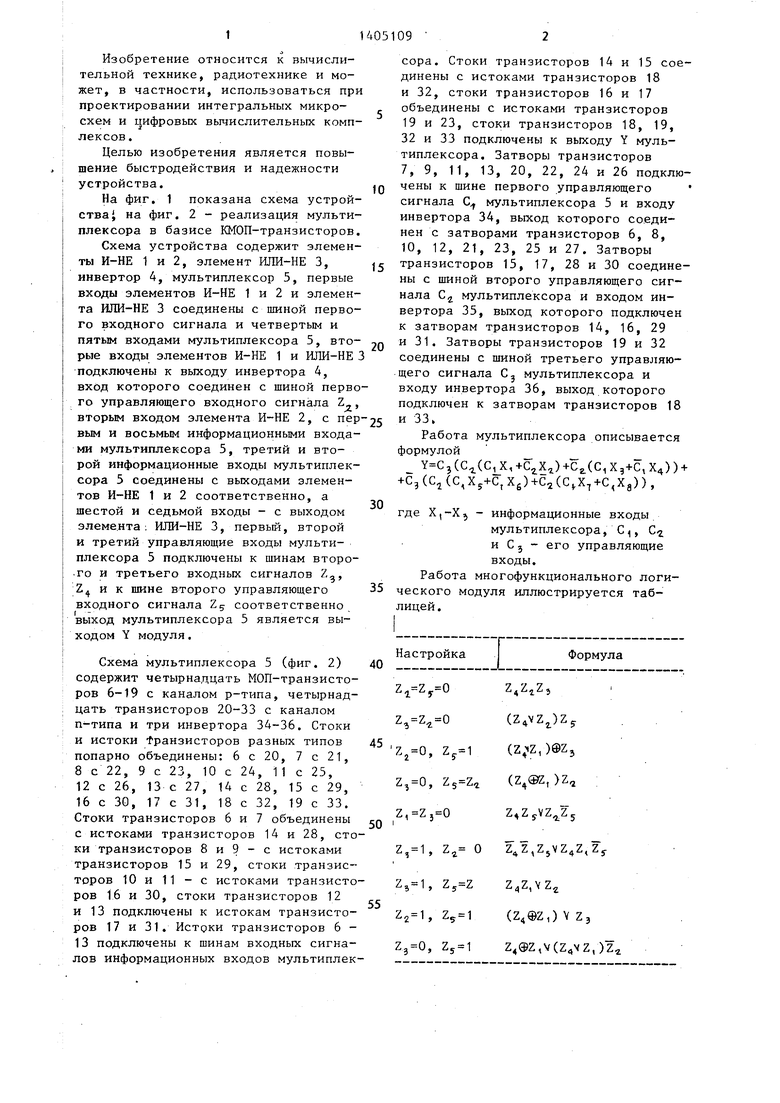

Фиг.1

Изобретение относится к вычислительной технике, радиотехнике и может, в частности, использоваться при проектировании интегральных микросхем и 1 ифровых вычислительных комплексов.

Целью изобретения является повышение быстродействия и надежности устройства.

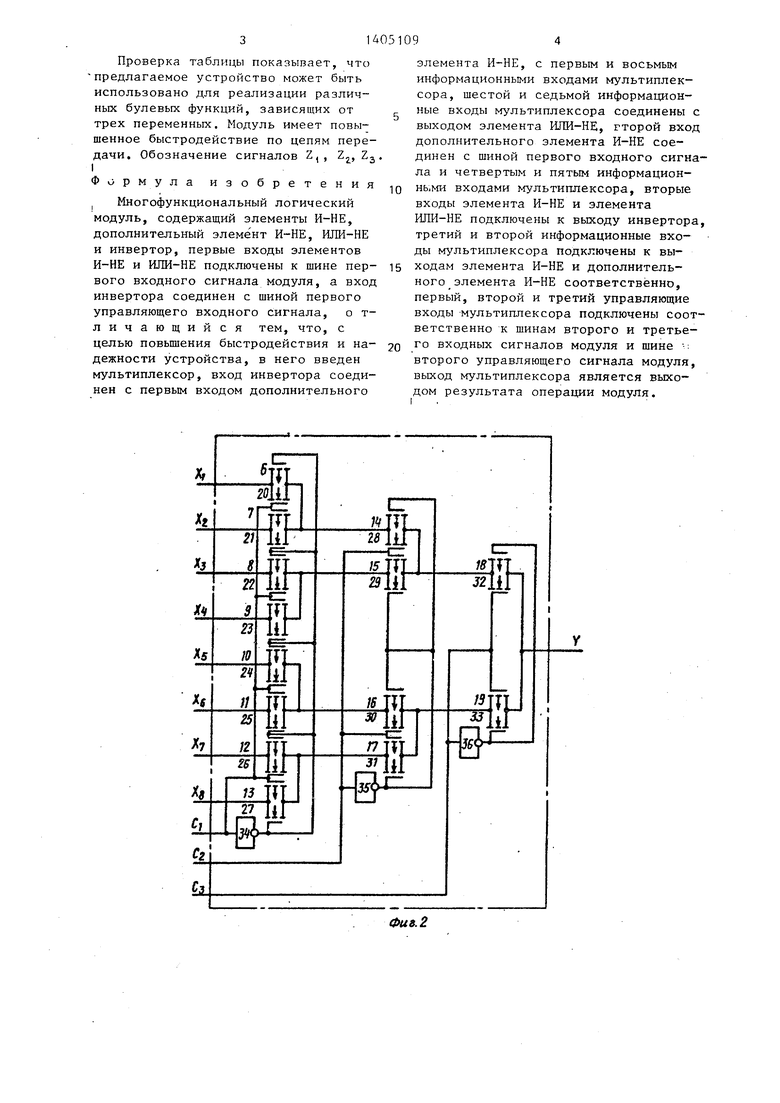

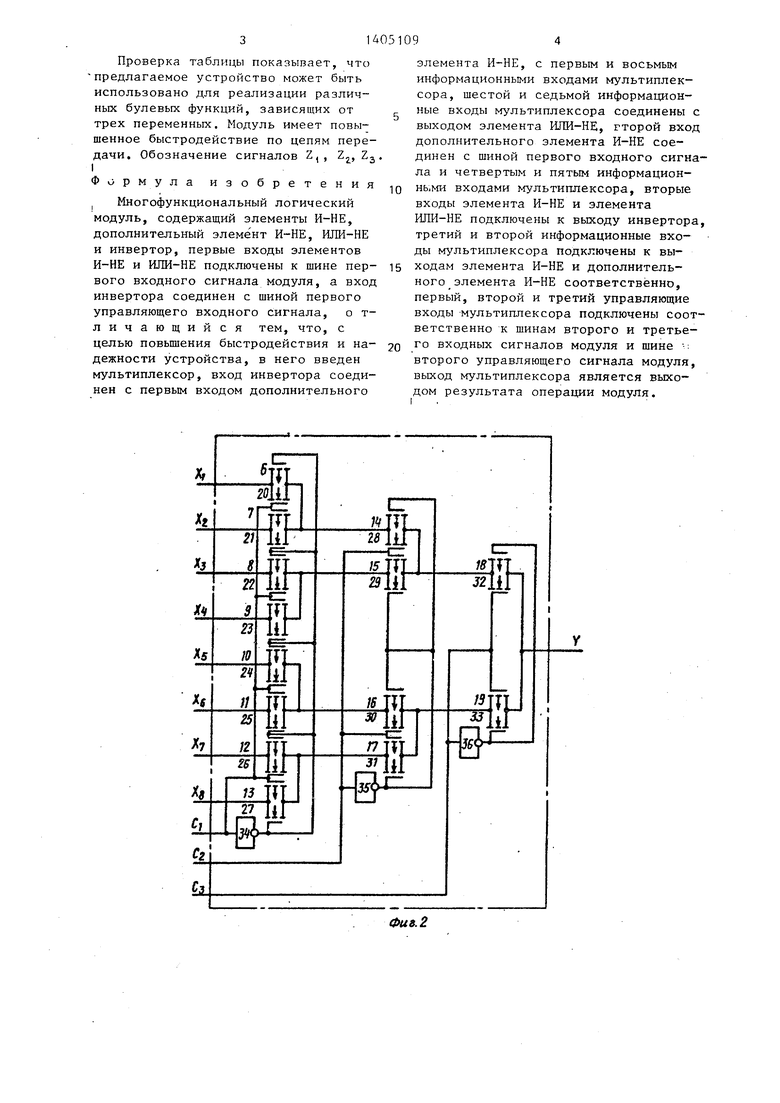

На фиг. 1 показана схема устройства i на фиг. 2 - реализация мультиплексора в базисе КМОП-транзисторов

Схема устройства содержит элементы И-НЕ 1 и 2, элемент ИЛИ-НЕ 3, инвертор 4, мультиплексор 5, первые входы элементов И-НЕ 1 и 2 и элемента ИЛИ-НЕ 3 соединены с шиной первого входного сигнала и четвертым и пятым входами мультиплексора 5, вто- рые входы элементов И-НЕ 1 и ИЛИ-НЕ подключены к выходу инвертора 4, вход которого соединен с шиной первого управляющего входного сигнала Z вторым входом элемента И-НЕ 2, с пер вым и восьмым информационными входами мультиплексора 5, третий и второй информационные входь мультиплексора 5 соединены с выходами элементов И-НЕ 1 и 2 соответственно, а шестой и седьмой входы - с выходом элеме.нта : ИЛИ-НЕ 3, первый, второй и третий управляющие входы мультиплексора 5 подключены к шинам второ- го и третьего входных сигналов Z, Z и к шине второго управляющего входного сигнала Z соответственно выход мультиплексора 5 является выходом Y модуля.

Схема мультиплексора 5 (фиг. 2) содержит четырнадцать МОП-транзисторов 6-19 с каналом р-типа, четырнадцать транзисторов 20-33 с каналом п-типа и три инвертора 34-36. Стоки и истоки транзисторов разных типов попарно объединены: 6 с 20, 7 с 21, 8 с 22, 9 с 23, 10 с 24, 11 с 25,

12с 26, 13 с 27, 14 с 28, 15 с 29, 16 с 30, 17 с 31, 18 с 32, 19 с 33. Стоки транзисторов 6 и 7 объединены с истоками транзисторов 14 и 28, стоки транзисторов 8 и 9 - с истоками транзисторов 15 и 29, стоки транзисторов 10 и 11 - с истоками транзисторов 16 и 30, стоки транзисторов 12

и 13 подключены к истокам транзисторов 17 и 31. Истоки транзисторов 6 13подключены к шинам входных сигналов информационных входов мультиплек

Q

о 5

0

5

сора. Стоки транзисторов 14 и 15 соединены с истоками транзисторов 18 и 32, стоки транзисторов 16 и 17 объединены с истоками транзисторов 19 и 23, стоки транзисторов 18, 19, 32 и 33 подключены к выходу Y мультиплексора. Затворы транзисторов 7, 9, 11, 13, 20, 22, 24 и 26 подключены к шине первого управляющего сигнала С мультиплексора 5 и входу инвертора 34, выход которого соединен с затворами транзисторов 6, 8, 10, 12, 21, 23, 25 и 27. Затворы транзисторов 15, 17, 28 и 30 соединены с шиной второго управляющего сигнала Cj мультиплексора и входом инвертора 35, выход которого подключен к затворам транзисторов 14, 16, 29 и 31. Затворы транзисторов 19 и 32 соединены с шиной третьего управляющего сигнала Cj мультиплексора и входу инвертора 36, выход которого подключен к затворам транзисторов 18 и 33.

Работа мультиплексора описывается формулой

(С(С,Х,)+С(С1Хэ+С,Х4)) + +C,(C,j(C,X5+C,Xg)+C2(C,,Xg)),

где Xj-X - информационные входы

мультиплексора, С , С- и С 5 - его управляющие входы.

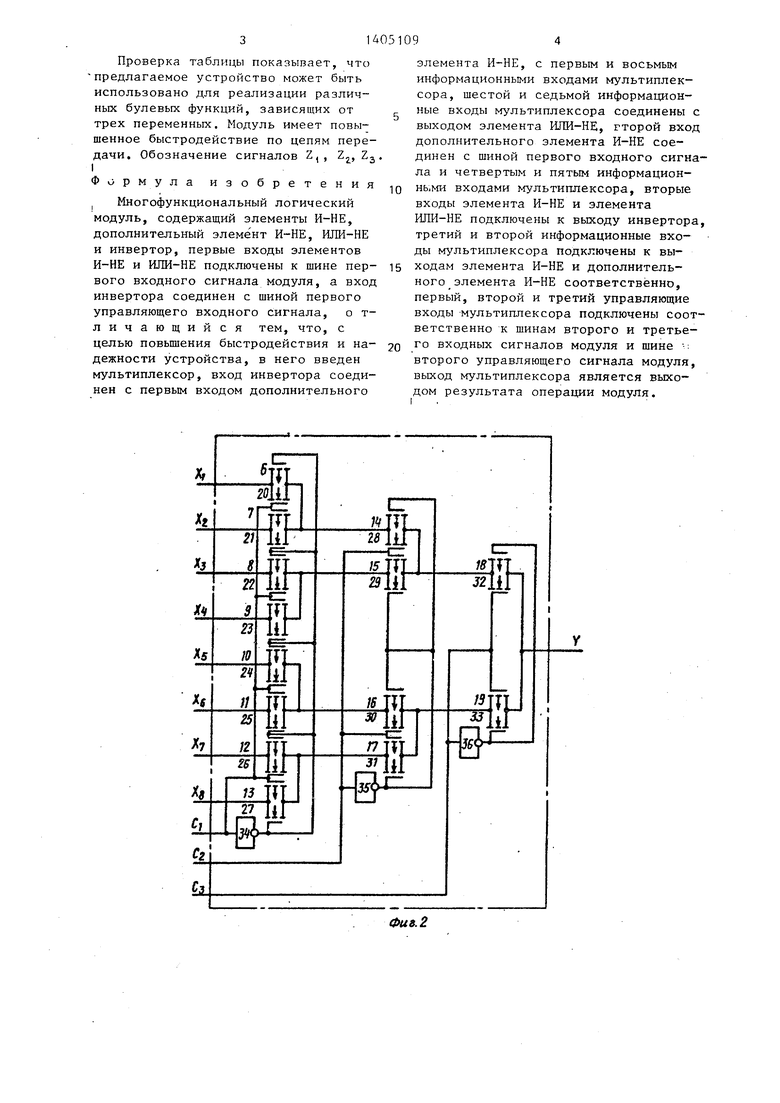

Работа многофункционального логического модуля иллюстрируется таблицей .

Настройка

I

Формула

(Z4VZ)Zj (Z,.Z,)@Z5 (, )Z,j

,г (,) V Zj

,V(Z4VZ,)Ii

Проверка таблицы показывает, что предлагаемое устройство может быть использовано для реализации различных булевых функций, зависящих от трек переменных. Модуль имеет повышенное быстродействие по цепям передачи. Обозначение сигналов Z

1

Zj, Zj,

Ф

р м у ла изобретения Многофункциональный логический модуль, содержащий элементы И-НЕ, дополнительный элеме нт И-НЕ, ИЛИ-НЕ и инвертор, первые входы элементов И-НЕ и ИЛИ-НЕ подключены к шине первого входного сигнала модуля, а вход инвертора соединен с шиной первого управляющего входного сигнала, о тцелью повышения быстродействия и надежности устройства, в него введен мультиплексор, вход инвертора соединен с первым входом дополнительного

элемента И-НЕ, с первым и восьмым информационными входами мультиплексора, шестой и седьмой информацион- ные входы мультиплексора соединены с выходом элемента ИЛИ-НЕ, гторой вход дополнительного элемента И-НЕ соединен с шиной первого входного сигнала и четвертым и пятым информацион-

0 нь.ми входами мультиплексора, вторые входы элемента И-НЕ и элемента ИЛИ-НЕ подключены к выходу инвертора, третий и второй информационные входы мультиплексора подключены к вы5 ходам элемента И-НЕ и дополнительного элемента И-НЕ соответственно, первый, второй и третий управляющие входы мультиплексора подключены соответственно к шинам второго и третье0 го входных сигналов модуля и шине ; второго управляющего сигнала модуля, выход мультиплексора является выходом результата операции модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| СИММЕТРИЧНЫЙ МУЛЬТИПЛЕКСОР НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК (КМОП) ТРАНЗИСТОРАХ | 2018 |

|

RU2689820C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| Схема сквозного переноса на КМОП-транзисторах | 1988 |

|

SU1529440A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| КОМПЛЕМЕНТАРНЫЙ МИКРОЭЛЕКТРОМЕХАНИЧЕСКИЙ ИНВЕРТОР | 2005 |

|

RU2290753C1 |

| УПРАВЛЯЕМЫЙ ФУНКЦИОНАЛЬНЫЙ МОДУЛЬ | 0 |

|

SU257867A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональный логический модуль | 1982 |

|

SU1077052A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 760451, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-23—Публикация

1986-10-23—Подача