Изобретение относится к аномальному декодированию последовательностей двоичных величин, которые, например, могут встречаться в каналах записи магнитных запоминающих устройств или в оптических подсистемах связи, где ошибки, разрушение информации в результате стирания или сбои приводят к появлению двоичных подпоследовательностей, характеризующихся кодовыми комбинациями с высоким коэффициентом заполнения (последовательности импульсов) или характеризующихся повторениями некоторых кодовых комбинаций. В частности, изобретение относится к способу и устройству, позволяющим либо предотвратить многократное повторение подобных кодовых комбинаций, либо исключить их.

Предпосылки создания изобретения

Хорошо известно, что последовательность двоичных величин, такая, например, как 1000011011, может неправильно интерпретироваться декодирующими устройствами из-за наличия в таких последовательностях непредусмотренных кодовых комбинаций или атрибутов. Так, например, последовательность 1010101010. . . характеризуется исключительно высоким коэффициентом заполнения. С электронной точки зрения высокий коэффициент заполнения приводит к увеличению повторяющейся нагрузки на электрические или механические элементы. Такое увеличение нагрузки в свою очередь часто приводит к повышенному нагреву деталей и компонентов оборудования и повышению уровня шумов в средах передачи сигналов, что сопровождается увеличением частоты ошибок и частоты отказов и сокращением срока службы деталей и компонентов оборудования.

В контексте настоящего изобретения понятие "коэффициент заполнения" означает число двоичных единиц, встречающихся в кодовой комбинации или интервале повторяющейся подпоследовательности. Так, например, для кодовой комбинации 101010 коэффициент заполнения равняется 50 процентам, поскольку единица встречается в каждом двухбитовом интервале. Если повторяющаяся кодовая комбинация имеет вид двух двоичных слов по 4 бита каждое, например 1001, 1000, то ее коэффициент заполнения будет равен 3/8=37,5 процента.

В каналах магнитной записи и оптической связи возникает эффект размывания или уширения импульсов. Так, в частности, в результате "размывания" два двоичных 4-битовых слова 0001, 0010 могут иметь на входе декодера вид 0001, 1010. В этом случае двоичная единица, находящаяся в положении 4-го бита первого слова, электрически или оптически "растягивается", принимая вид двух последовательных двоичных единиц. Такой эффект уширения или размывания наиболее распространен в системах связи с фазоимпульсной модуляцией (ФИМ) и иных аналогичных системах. Связано это с тем, что в системах с ФИМ, как известно, неэффективно используется полоса пропускания.

Из патента US 4413251, выданного 1 ноября 1983 г. на имя Adler и др. и озаглавленного "Method and Apparatus for Generating a Noiseless Sliding Block Code for a (1,7) Channel with Rate 2/3", известно, что конечный автомат (КА) может обратимо преобразовывать двоичную последовательность, на которую не наложено каких-либо ограничений, в двоичную последовательность, на которую наложены определенные ограничения. Кроме того, в указанном патенте на имя Adler говорится, что не зависящий от состояния конечный автомат с функцией упреждения может выполнять декодирование. Функция упреждения позволяет декодеру преобразовывать n<m битов текущего RLL-кодового слова (от англ. "Run Length Limited", кодирование с ограничением длины поля записи или кодирование с ограничением расстояния между переходами) в m битов не имеющей ограничений последовательности с использованием для этой цели предварительно заданного количества последующих RLL-кодовых слов. Тем не менее функция упреждения такого декодера усиливает отрицательное влияние ошибок или стирания в RLL-кодовом слове.

В соответствии с вышеуказанным патентом на имя Adler и др. для заданного отношения кодирования R=m/n при преобразовании m битов двоичной последовательности, не имеющей ограничений, в n битов последовательности, имеющей ограничения, необходимое условие удается частично соблюсти за счет использования кодирующего КА, который имеет 2m ветвлений на одно состояние и для которого ограничения (d, k) проявляются в разделении и объединении некоторых состояний КА с целью получения нового КА. Ограничения (d, k) означают, что между любой парой последовательных двоичных единиц должно быть вставлено не менее d и не более к нулей. При d<k d определяет частоту переходов и тем самым источник межсимвольных помех (МСП). Значение k используется для повторной синхронизации задающего генератора.

Краткое описание изобретения

В настоящем изобретении предлагается конечный автомат (КА), предназначенный для преобразования последовательности двоичных величин без наложенных на нее ограничений в последовательность с наложенными на нее ограничениями, выбранную из группы кодов RLL (d, k) с фиксированным отношением 2/3, включающих коды RLL (1, 9) и (1, 13), при этом КА позволяет подавить многократное повторение заданных последовательностей, полученных с помощью RLL-кодирования, как это имеет место в случае RLL-кодов (1, 9) и (1, 10), или исключить появление подобных последовательностей, как это имеет место в случае RLL-кода (1, 13). Кроме того, не зависящий от состояния декодер с функцией опережения обеспечивает необходимую обратимость при считывании RLL-кодированных последовательностей из подсистемы хранения данных или при их получении по каналу оптической связи и т.п.

В частности, для решения описанных выше проблем в изобретении предлагается способ, осуществляемый на базе процессора или на базе эквивалентных комбинационных логических схем с жесткими соединениями и обеспечивающий обратимое преобразование двоичных последовательностей в последовательности, кодированные с ограничением расстояния между переходами (RLL) (1, k), с отношением 2/3 и с ограничением максимальной плотности переходов. Такой способ включает две основных стадии, первая из которых состоит в определении и сохранении конечного автомата, используемого в качестве кодера, а вторая заключается в последующем преобразовании двоичной последовательности.

На первой стадии определяют и сохраняют в памяти процессора таблицу перехода состояний для упорядоченных пар, включающих последующее состояние (n1n2n3) и текущий RLL-кодированный трехбитовый символ (c1c2c3). Каждая из этих упорядоченных пар в указанной таблице индексирована по первой табличной координате в соответствии с текущим состоянием, а по второй табличной координате - в соответствии с вектором (b1b2b3b4) текущей пары битов (b1b2) и заданного количества упреждающих пар битов (b3b4) из двоичной последовательности. Каждая текущая пара битов представляет собой распознаваемую двоичную величину (00, 01, 10, 11). Каждая пара битов из заданного количества пар битов выбрана из группы, включающей распознаваемую двоичную величину и безразличное значение (хх). Существенная особенность состоит в том, что переходы между состояниями ограничены таким образом, чтобы коэффициент заполнения любой соответствующей длительной последовательности RLL-кодированных трехбитовых величин составлял менее 50 процентов. На второй стадии с помощью процессора осуществляют обращение к таблице в соответствии с последовательностью векторов пар битов и извлечение из таблицы последовательности RLL-кодированных трехбитовых величин. Логические зависимости, используемые для преобразования двоичных слов в RLL-кодированные слова и соответствующего обратного преобразования, показаны на чертежах и подробно рассмотрены в последующем описании предпочтительного варианта осуществления изобретения.

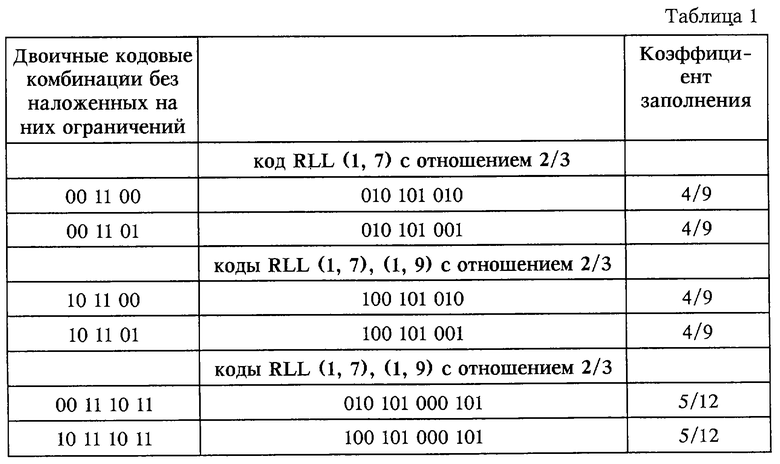

Для использования кодирования RLL (1, k) с отношением 2/3 с целью снизить коэффициент заполнения потока двоичных величин необходимо оценить тот эффект, который будет проявляться при преобразовании выбранных двоично-кодированных кодовых комбинаций без наложенных на них ограничений в стандартном кодере RLL (1, 7) или (1, 9) с отношением 2/3. Фактически эти выбранные кодовые комбинаций приводили к получению двоично-кодированных кодовых комбинаций с наложенными на них ограничениями, характеризующихся исключительно высоким коэффициентом заполнения. Примеры таких кодовых комбинаций представлены в таблице 1.

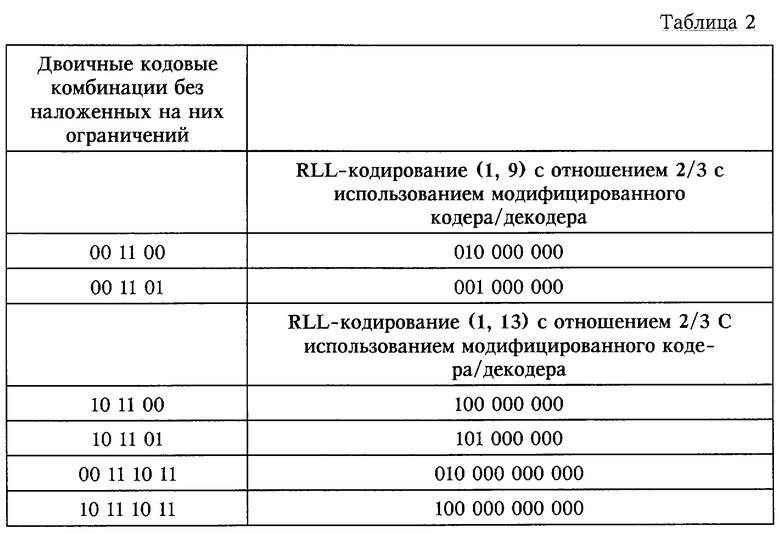

Помимо этого было также установлено, что кодеры RLL (1, 9) и (1, 13) с отношением 2/3 того типа, который описан в патенте US 4413251 на имя Adler, можно эвристически модифицировать либо (а) с целью подавления неограниченного повторения RLL-кодированных последовательностей с высоким коэффициентом заполнения для указанных выше заданных кодовых комбинаций без наложенных на них ограничений, либо (б) с целью их эффективного подавления, как это проиллюстрировано в таблице 2.

Краткое описание чертежей

На прилагаемых к описанию чертежах показано:

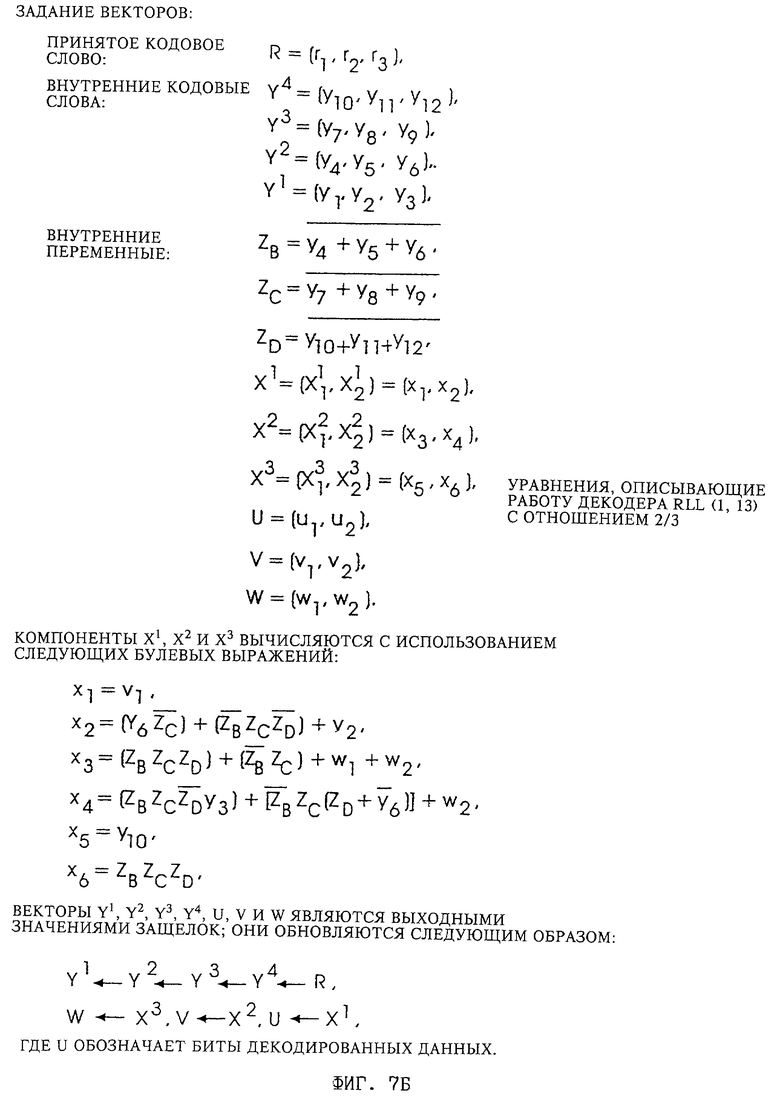

на фиг.1 - расположение канального кодера, в котором на кодируемую двоичную последовательность накладываются ограничения, и декодера по изобретению относительно среды для хранения или передачи информации,

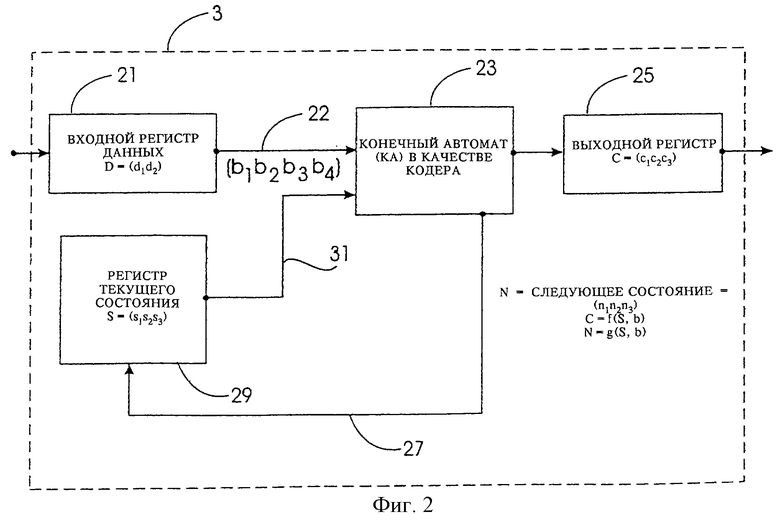

на фиг. 2 - конечный автомат (КА), предназначенный для использования в качестве кодера, набор двоичных разрядов, на выходе которого является функцией текущего внутреннего состояния и набора входных двоичных разрядов, а следующее внутреннее состояние является другой функцией текущего внутреннего состояния и набора входных двоичных разрядов,

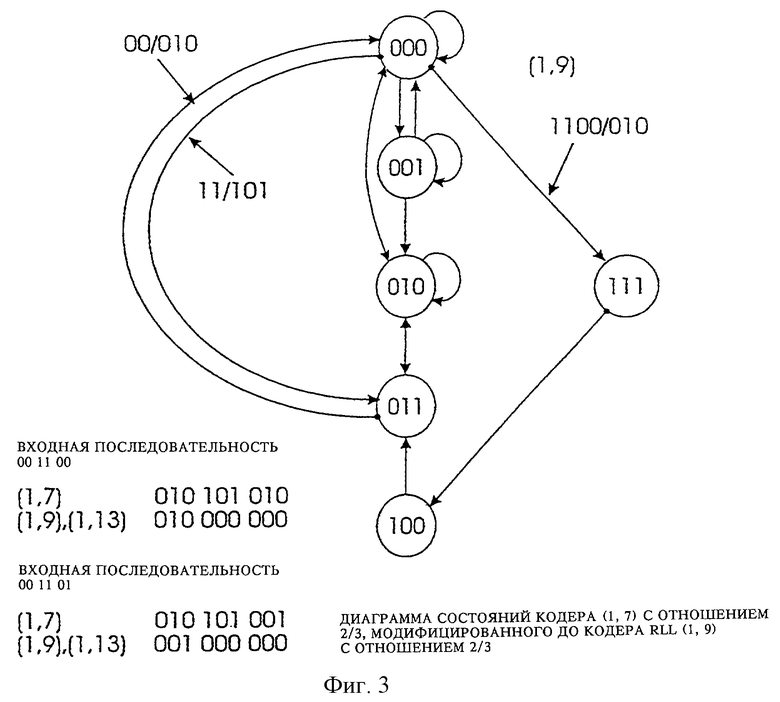

на фиг.3 - схема состояний кодера RLL (1, 7) с отношением 2/3, который в ответ на поступление на его вход двоичной последовательности без наложенных на нее ограничений формирует выходную последовательность с высоким коэффициентом заполнения, при этом в результате изменения (модификации) состояния кодер преобразуется в кодер RLL (1, 9) с отношением 2/3, формирующий выходную последовательность с низким коэффициентом заполнения,

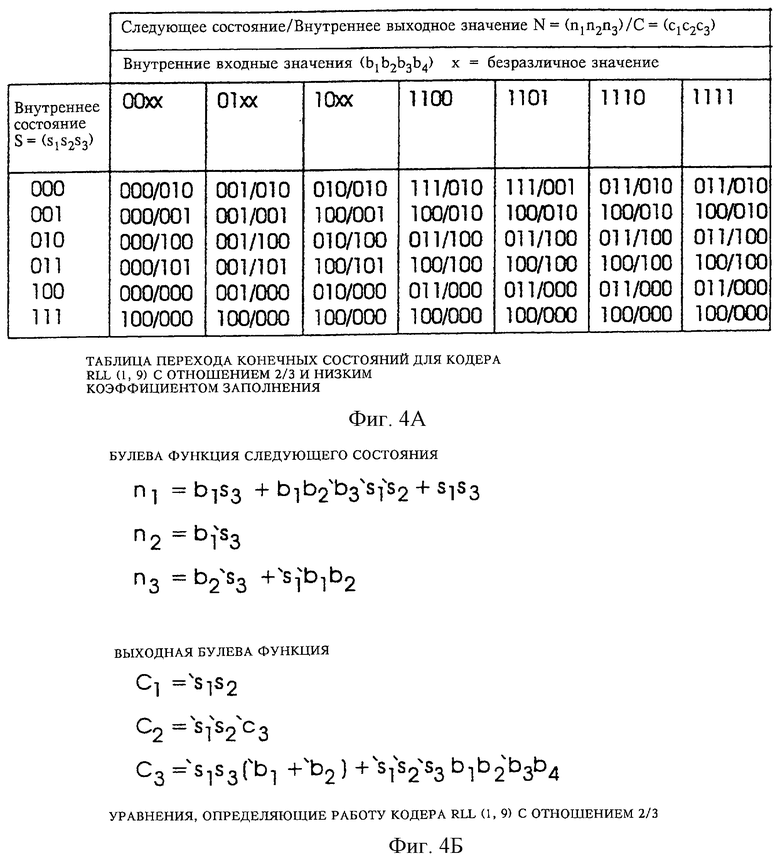

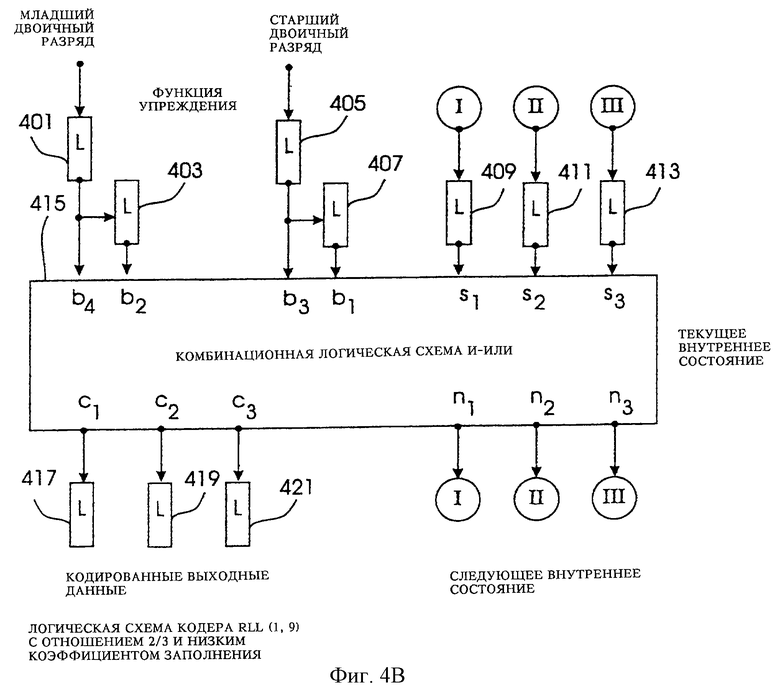

на фиг.4А-4В - соответственно таблица перехода состояний для кодера RLL (1, 9) с отношением 2/3, модифицированного в соответствии с изобретением, булевы уравнения, определяющие взаимосвязь между входными двоичными данными без наложенных на них ограничений и выходными двоичными данными с наложенными на них ограничениями, а также кодер, реализованный на базе высокоуровневых логических вентильных схем,

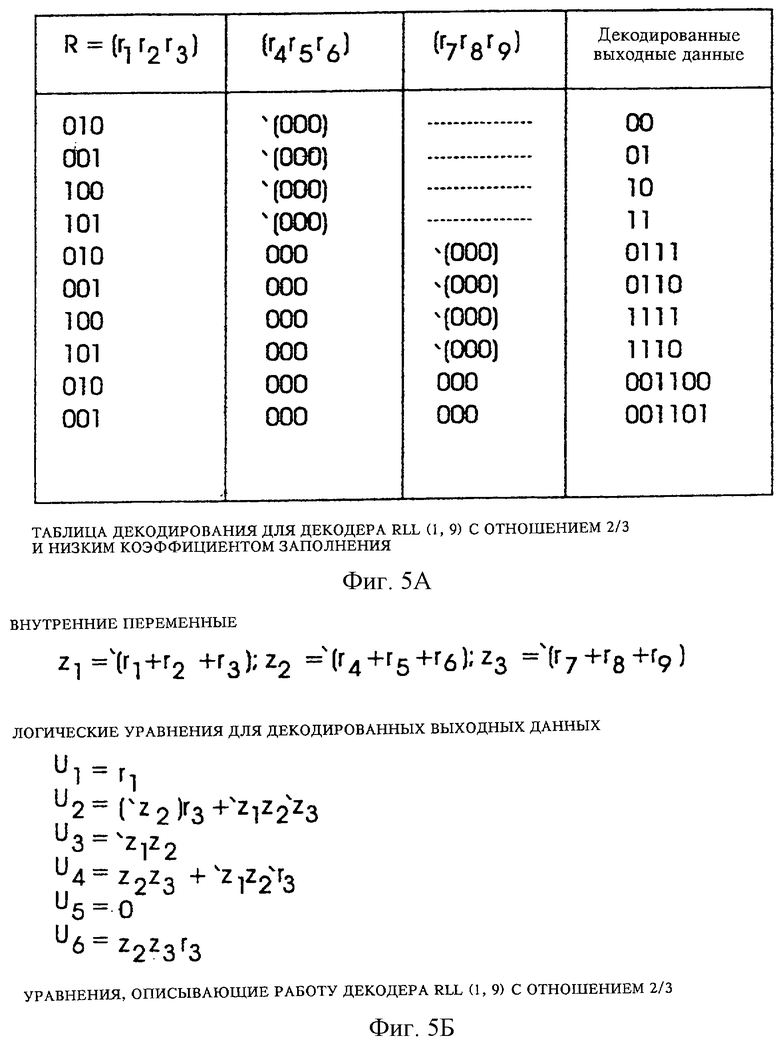

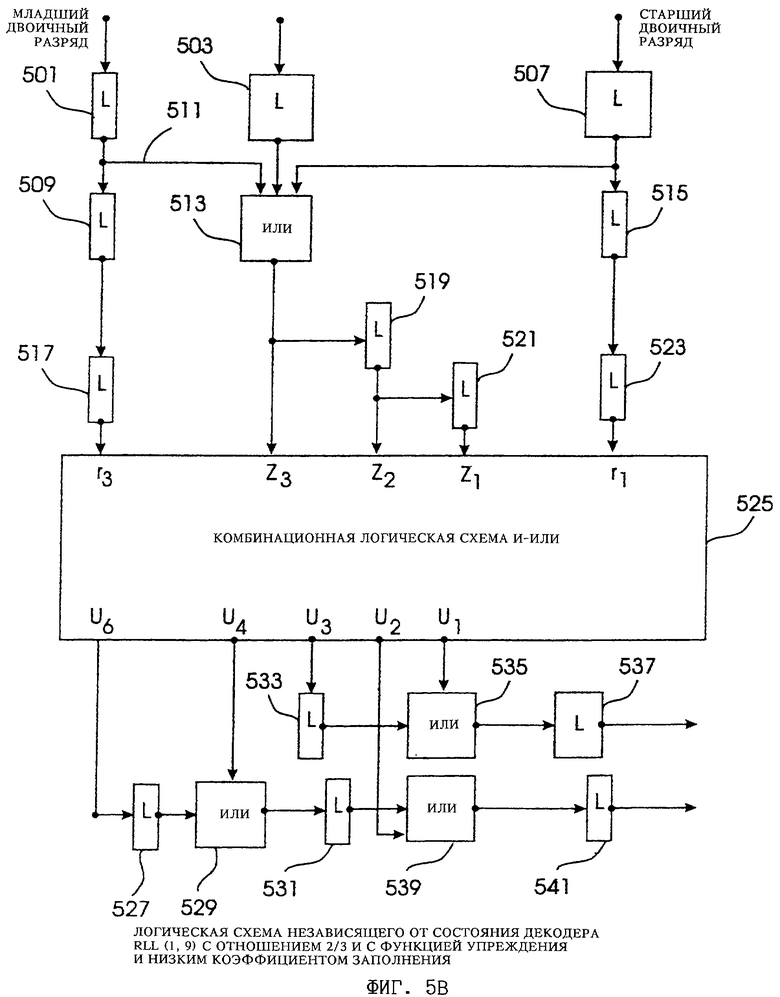

на фиг.5А-5В - соответственно таблица декодирования для декодера RLL (1, 9) с отношением 2/3, модифицированного в соответствии с изобретением, булевы уравнения, определяющие взаимосвязь между входными двоичными данными с наложенными на них ограничениями и выходными двоичными данными без наложенных на них ограничений, а также декодер, реализованный на базе высокоуровневых логических вентильных схем,

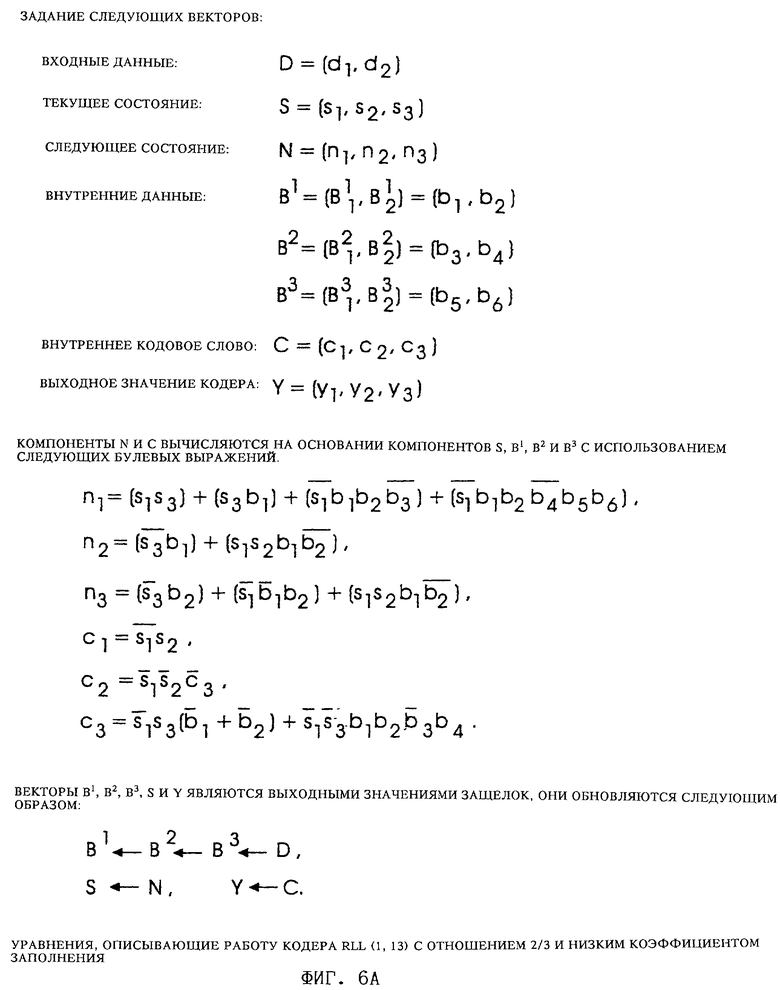

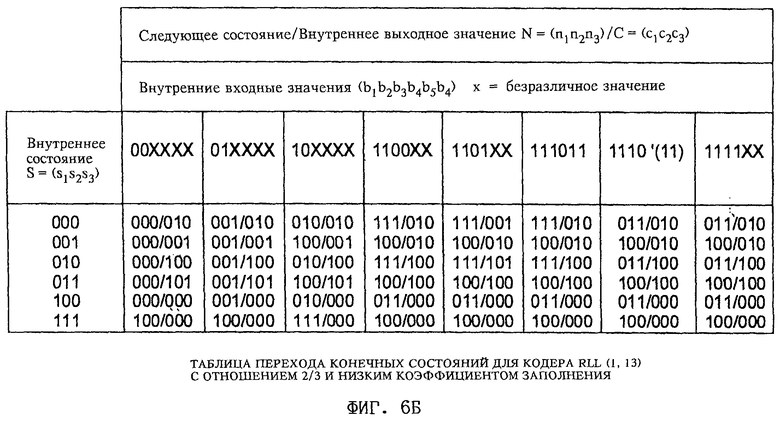

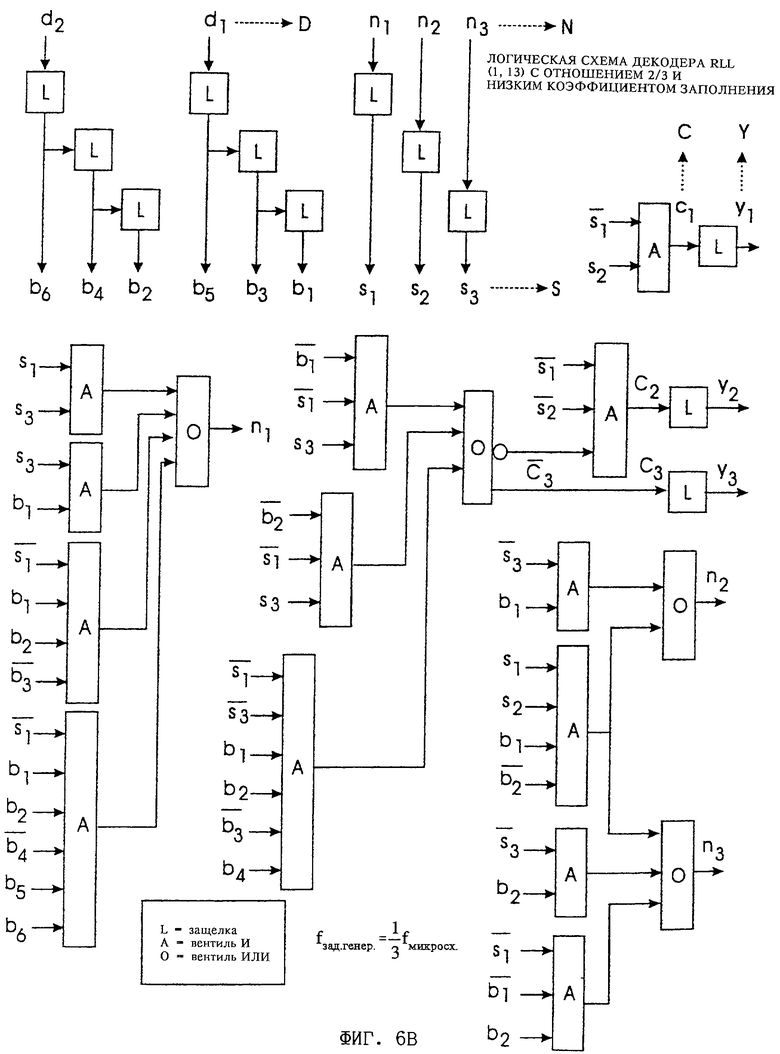

на фиг.6А-6В - соответственно булевы уравнения, определяющие взаимосвязь между входными двоичными данными без наложенных на них ограничений и выходными двоичными данными с наложенными на них ограничениями для кодера RLL (1, 13) с отношением 2/3, модифицированного в соответствии с изобретением, таблица перехода состояний, а также кодер, реализованный на базе высокоуровневых логических вентильных схем, и

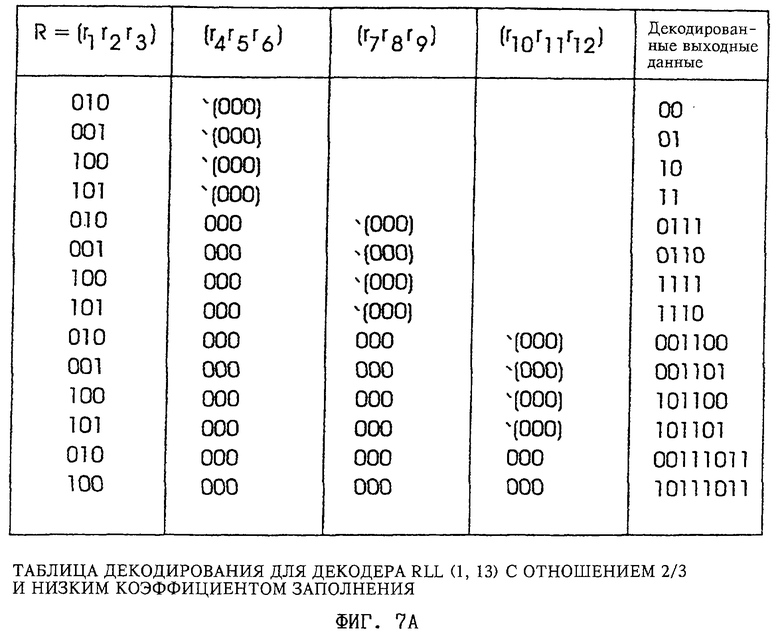

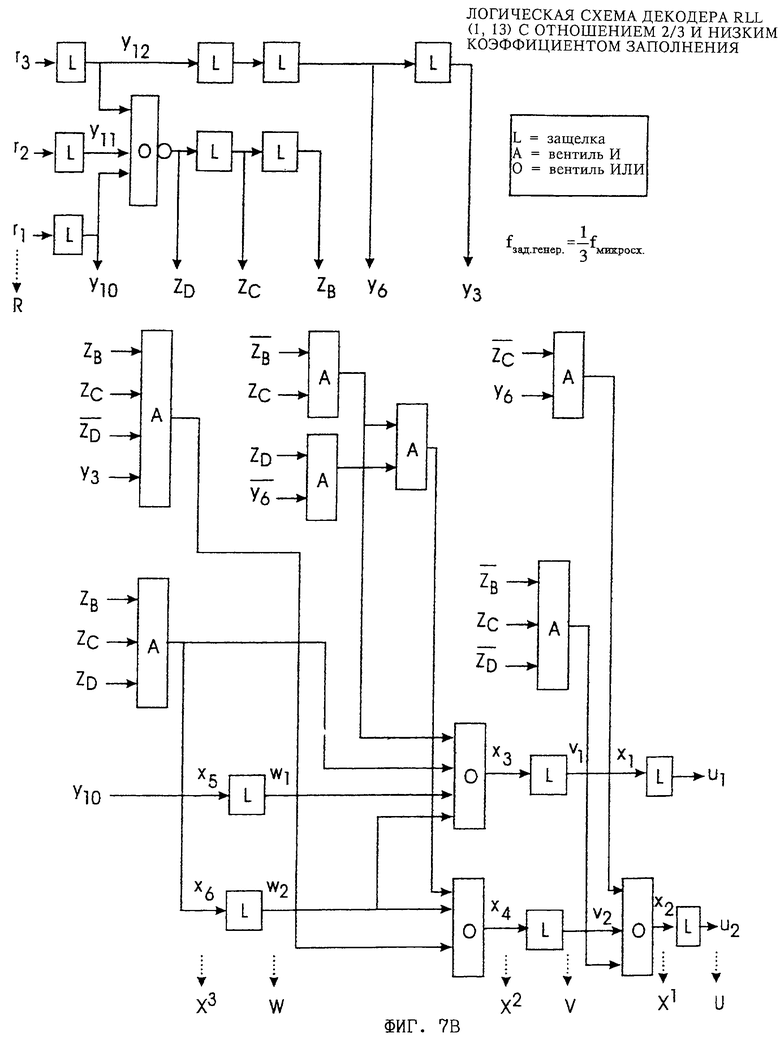

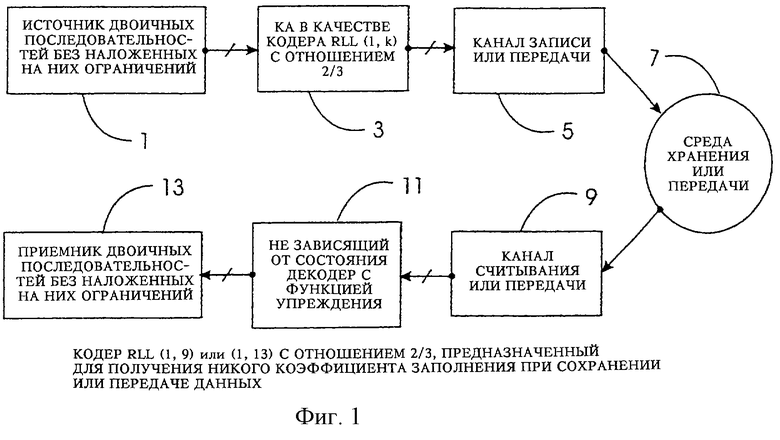

на фиг.7А-7В - соответственно таблица декодирования для декодера RLL (1, 13) с отношением 2/3, модифицированного в соответствии с изобретением, булевы уравнения, определяющие взаимосвязь между входными двоичными данными с наложенными на них ограничениями и выходными двоичными данными без наложенных на них ограничений, а также декодер, реализованный на базе высокоуровневых логических вентильных схем.

Подробное описание изобретения

На фиг.1 показан канальный кодер 3, в котором на кодируемую двоичную последовательность накладываются определенные ограничения и который расположен перед каналом 5 записи или передачи и средой 7 хранения или передачи информации. Соответствующий декодер 11 расположен между каналом 9 считывания или приема и приемником 13 двоичной последовательности без наложенных на нее ограничений. Источником 1 двоичных последовательностей может служить генератор случайных чисел, который формирует единицы и нули с равномерным, гауссовым или иным статистическим распределением и который периодически выдает повторяющиеся кодовые комбинации с высоким коэффициентом заполнения. Подобный коэффициент заполнения может изменяться от максимального значения, составляющего 50 процентов для последовательности 10101010..., до более приемлемых значений, которые значительно меньше 50 процентов. Поскольку в общем случае двоичная последовательность без наложенных на нее ограничений подается на кодер RLL (1, k), работающий с отношением 2/3, сам этот кодер характеризуется минимальным коэффициентом заполнения выдаваемых им двоичных последовательностей.

Двоичные последовательности с наложенными на них ограничениями в свою очередь поступают с выхода кодера 3 в канал 5 записи или передачи, где они соответствующим образом модулируются и направляются в среду 7 хранения или передачи информации. После этого модулированная последовательность с наложенными на нее ограничениями поступает в канал 9 считывания или приема и преобразуется в двоичную последовательность единиц и нулей с наложенными на нее ограничениями. Эта преобразованная двоичная последовательность затем поступает в не зависящий от состояния декодер 11 с функцией упреждения. Декодер 11 использует предварительно заданное количество последующих символов (функция упреждения) и снимает наложенные на последовательность ограничения, в результате чего в приемник 13 поступает исходная двоичная последовательность без наложенных на нее ограничений.

На фиг. 2 показан конечный автомат (КА), используемый в качестве кодера 3. Для определенного набора параметров (d, к)=(1, 9) или (1, 13) предварительно заданное количество текущих входных битов (b1b2) и будущих (упреждающих) входных битов (b3b4) поступает в виде набора бит (b1b2b3b4) по линии 22 из входного регистра 21 в КА 23. Данные с выхода КА 23 подаются в регистр 25. Выходной набор двоичных разрядов С=(c1c2c3) является функцией f входных битов (b1b2b3b4) и текущего состояния S=(s1s2s3) конечного автомата. Одновременно с этим определяется следующее состояние N конечного автомата как функция входных битов (b1b2b3b4) и текущего состояния S конечного автомата. Таким образом, для следующего цикла следующее состояние N конечного автомата записывается в регистр 29 текущего состояния, и это состояние становится новым текущим состоянием S конечного автомата. В этом отношении КА можно также представить в виде ориентированного графа, узлы которого соответствуют состояниям S конечного автомата, а его направленные ребра определяют переходы между состояниями для любого заданного входного вектора, причем при этом генерируется соответствующий выходной вектор. Ориентированный граф, представленный в табличной форме, называется "таблицей перехода состояний".

На фиг.3 показана диаграмма частичных состояний или ориентированный граф для кодера RLL (1, 7) с отношением 2/3, который в ответ на входной поток двоичных данных без наложенных на него ограничений выдает выходной поток двоичных данных с высоким коэффициентом заполнения. Внутренние состояния кодера (1, 7) представлены узлами 000, 001, 010, 011 и 100. Поскольку этот кодер представляет собой кодер с отношением 2/3, для входной кодовой комбинации с двумя битами на период, т.е. для кодовой комбинации 001100, в выходной кодовой комбинации кодера будет присутствовать три бита на период, т. е. эта выходная кодовая комбинация будет иметь вид 010101010. Аналогичным образом для входной кодовой комбинации 001101 выходная кодовая комбинация будет иметь вид 010101001. Если в диаграмму состояний добавить дополнительное состояние 111 и соединить его показанным на чертеже образом с состояниями 000 и 100, то кодер будет представлять собой кодер (d, k)=(1, 9) с отношением 2/3. Такое дополнительное состояние обеспечивает наличие достаточного вычислительного ресурса для использования функции упреждения на несколько входных символов и позволяет генерировать выходную последовательность с уменьшенным коэффициентом заполнения, а именно 010000000 для входной кодовой комбинации 001100 и 001000000 для входной кодовой комбинации 001101.

На фиг.4А-4В показаны соответственно таблица перехода состояний для кодера RLL (1, 9) с отношением 2/3, модифицированного в соответствии с изобретением, логические (булевы) уравнения, определяющие взаимосвязь между входными двоичными данными без наложенных на них ограничений и выходными двоичными данными с наложенными на них жесткими ограничениями, а также кодер, реализованный на базе высокоуровневых логических вентильных схем. Согласно фиг.4А в качестве кодера используется КА, имеющий шесть внутренних состояний S. Поскольку кодер работает с отношением 2/3, он обрабатывает текущую входную пару бит и одну упреждающую пару бит, т.е. битовую комбинацию b= (b1b2b3b4). Каждая строка в таблице индексируется одним из внутренних состояний S, а каждый столбец индексируется одной из семи комбинаций пар двух битов. Для каждого заданного индекса таблицы (S, b) соответствующий элемент таблицы имеет вид (следующее состояние N/выходное значение С=(c1c2c3)). Из семи входных комбинаций пар двух битов в трех из них, а именно 00 хх, 01 хх и 10 хх, имеются две позиции с безразличными разрядами. Так, например, если кодер (1, 9) находится в состоянии 100, а на его вход поступает значение 00 хх, то происходит переход от состояния 100 к состоянию 000 и формируется выходное значение С=000.

На фиг. 4Б показан набор булевых уравнений, определяющих булеву функцию следующего состояния N=(n1n2n3)=g(S, b) и булеву функцию выходного значения С=(с1c2c3)=f(S, b). Эти уравнения являются аналитическими выражениями, полученными на основании таблицы перехода состояний, показанной на фиг.4А. В этих булевых выражениях отрицание булевой переменной С обозначается как 'С. Таким образом, отрицание выражения 111 будет обозначаться как '(111). Необходимо отметить, что булевы уравнения, показанные на фиг.4Б, полностью отвечают комбинационной логической схеме И-ИЛИ (415 на фиг.4В).

На фиг. 4В показана соответствующая логическая схема для кодера RLL (1, 9) с отношением 2/3 и низким значением коэффициента заполнения. В рассматриваемом варианте реализации на логическом уровне текущая входная пара битов (b1b2) поступает через защелки 407 и 403 в комбинационную логическую схему 415. Аналогичным образом упреждающая входная пара битов (0304) поступает в логическую схему 415 через защелки 405 и 401 (на чертеже обозначены как L). Кодированное выходное значение С выдается логической схемой 415 на защелки 417, 419 и 421. Следующее внутреннее состояние N выдается логической схемой 415 по линиям обратной связи I, II и III в соответствующие входные защелки 409, 411 и 413.

На фиг. 5А-5В показаны соответственно таблица декодирования для декодера RLL (1, 9) с отношением 2/3, модифицированного в соответствии с изобретением, логические (булевы) уравнения, позволяющие вновь преобразовать входные данные с наложенными на них ограничениями в выходные данными без наложенных на них ограничений, а также декодер, реализованный на базе высокоуровневых логических вентильных схем. Показанная на фиг.5А таблица декодирования, обеспечивающая упреждение на несколько RLL-символов, является не зависящей от состояния. Иными словами, она, в отличие от кодера, не представляет собой КА. В трех первых слева направо столбцах таблицы расположены двоично-кодированные RLL-символы. К ним относятся текущий символ (r1r2r3) и два упреждающих символа (r4r5r6) и (r7r8r9). Четвертый столбец обозначается как "декодированные выходные данные". Для декодирования в последовательности или цепочке RLL-символов предусмотрен перемещаемый блок из 3-битовых символов, в котором текущий символ декодируется в результате логического комбинирования текущего символа с двумя упреждающими символами на основании булевых уравнений, представленных на фиг.5Б.

Как показано на фиг. 5В, каждый RLL-кодированный символ представляет собой 3-разрядный байт, биты (двоичные разряды) которого подаются соответственно в защелки 501, 503 и 507. Эти биты обрабатываются с помощью вентиля ИЛИ 513 и защелок 519 и 521 с получением трех промежуточных внутренних переменных z1, z2 и z3. Эти переменные одновременно подаются на входы комбинационной логической схемы 525. Помимо этого, на вход логической схемы 525 в качестве входных величин через соответствующие защелки 509, 517, 515 и 523 параллельно подаются первый и третий биты r1 и r3 текущего RLL-кодированного символа.

Работа логической схемы 525 полностью описывается показанными на фиг.5Б логическими уравнениями для декодированных выходных данных. Поскольку логическими уравнениями задаются 6-битовые выходные значения (u1u2u3u4u5u6), выходная переменная u5 задается равной нулю. В рассматриваемом варианте используется дополнительная логическая схема для преобразования декодированных выходных данных U в 2-разрядные байты исходной двоичной последовательности без наложенных на нее ограничений. Таким образом, первый бит 2-разрядного байта вычисляется в вентиле ИЛИ 529 путем активного комбинирования величины u4 и полученного на выходе защелки 527 значения величины u6, а также в вентиле ИЛИ 539 путем активного комбинирования выходной величины вентиля ИЛИ 529, поступающей с выхода защелки 531, и величины u2 с выхода логической схемы 525. Второй бит 2-разрядного байта вычисляется в вентиле ИЛИ 535 путем активного комбинирования величины u1 и полученного на выходе защелки 533 значения величины u3. Первый из двух битов поступает в защелку 541, а второй из двух битов поступает в защелку 537.

На фиг. 6А-6В показаны соответственно таблица перехода состояний для кодера RLL (1, 13) с отношением 2/3, модифицированного в соответствии с изобретением, логические (булевы) уравнения, определяющие взаимосвязь между входными данными без наложенных на них ограничений с выходными данными с наложенными на них ограничениями, а также кодер, реализованный на базе высокоуровневых логических вентильных схем. На фиг.6Б показана диаграмма перехода состояний, представленная в виде таблицы (вектора) упорядоченных пар внутренних состояний и кодированных выходных данных, элементы которой проиндексированы текущим внутренним состоянием S и составной входной величиной (b1b2b3b4b5b6). Составная входная величина для кодера (1, 13) представляет собой текущую двоично-кодированную входную пару битов и две упреждающих двоично-кодированных пары битов. Если на вход кодера будут непрерывно поступать значения 00 хх хх, то он в конечном итоге перейдет в состояние 000, и в этом состоянии будет циклически выдавать последовательность 010010010010.. . с коэффициентом заполнения 1/3. Такой коэффициент все еще значительно меньше, чем коэффициент заполнения, равный одной второй для последовательности 010101...

Булевы уравнения для кодера (1, 13), показанные на фиг.6А, по своей общей структуре очень схожи с уравнениями для кодера (1, 9), приведенными на фиг. 4Б. Иными словами, эти уравнения также получены на основании диаграммы перехода состояний и являются ограничительными для получения выходной последовательности с низким коэффициентом заполнения. Кроме того, в этих уравнениях для обозначения отрицания используется горизонтальная черта над булевыми переменными.

На фиг. 6В показана логическая схема кодера (1, 13), аналогичная логической схеме кодера (1, 9) по фиг.4Б, за исключением того, что кодер (1, 13) представлен в виде схемы с отдельными, т.е. не соединенными друг с другом, контактами. Подобные схемы с отдельными контактами первоначально предназначались для графического изображения сетей с коммутацией каналов, используемых, например, в телефонии. Согласно рассматриваемой схеме три входных пары битов d1d2 подаются на защелки L, а входные биты b1...b6 вместе с внутренними состояниями подаются в комбинационную логическую схему по существу аналогично тому, как это описано выше для кодера (1, 9).

На фиг.7А-7В показаны соответственно таблица декодирования для декодера RLL (1, 13) с отношением 2/3 в соответствии с изобретением, логические (булевы) уравнения, определяющие взаимосвязь между входными данными с наложенными на них ограничениями и выходными данными без наложенных на них ограничений, а также декодер, реализованный на базе высокоуровневых логических схем. На фиг.7А показана не зависящая от состояний таблица декодирования, в которой текущий RLL-символ и три упреждающих RLL-символа используются для преобразования текущего RLL-символа в двоичные последовательностей пар битов без наложенных на них ограничений. Соответствующие булевы уравнения, описывающие работу декодера, показаны на фиг.7Б, а логическая схема декодера, представленная в виде схемы с отдельными контактами, приведена на фиг.7Б, при этом декодер работает аналогично декодеру, показанному на фиг.4В.

Изобретение относится к преобразованию двоичных последовательностей, передаваемых по каналам записи запоминающих устройств или оптических подсистем связи. Преобразуются двоичные последовательности, кодированные с ограничением расстояния между переходами (RLL) (1, k), с отношением 2/3 и с ограничением максимальной плотности переходов. Определяют и сохраняют в памяти процессора таблицу перехода состояний для упорядоченных пар. Каждая индексирована по первой табличной координате в соответствии с текущим состоянием, а по второй табличной координате - в соответствии с вектором текущей пары битов и заданного количества упреждающих пар битов. Переходы между состояниями ограничены таким образом, чтобы коэффициент заполнения любой соответствующей длительной последовательности RLL-кодированных трехбитовых величин составлял менее 50%. С помощью указанного процессора обращаются к таблице в соответствии с последовательностью векторов. Определяют и сохраняют в памяти указанного процессора не зависящую от состояния таблицу декодирования, содержащую список пар битов двоичной последовательности и индексированную с помощью вектора, сформированного на основании текущих RLL-кодированных трехбитовых величин и предварительно заданного количества упреждающих RLL-кодированных трехбитовых величин. Устройство содержит конечный автомат (КА), предназначенный для формирования RLL-кодированных трехбитовых символов как первой функции текущего состояния из множества внутренних состояний КА и упомянутого вектора. Технический результат - снижение уровня шумов, частоты ошибок и отказов. 2 с. и 2 з.п. ф-лы, 7 ил., 2 табл.

n1= b1s3+b1b2'b3's1's2+s1s3;

n2= b1's3;

n3= b2's3+'s1'b1b2;

c1= 's1s2;

c2= 's1's2'c3;

c3= 's1s3('b1+'b2)+'s1's2's3b1b2'b3b4.

| US 4413251 A, 01.11.1983 | |||

| Механизм управления скважиннымигидРАВличЕСКиМи уСТРОйСТВАМи | 1976 |

|

SU829854A1 |

| УСТРОЙСТВО для ПОДВОДА СМАЗЫВАЮЩЕ-ОХЛАЖДАЮЩЕЙЖИДКОСТИ | 0 |

|

SU319441A1 |

| Устройство для управления магнитофоном | 1971 |

|

SU472375A1 |

| Прерывистый абразивный круг | 1974 |

|

SU517478A2 |

| US 4878136 A, 31.10.1989 | |||

| US 5271016 A, 14.12.1993 | |||

| US 52742243 A, 21.04.1998 | |||

| JP 61227431 А, 09.10.1986 | |||

| JP 63020920 A, 24.08.1995 | |||

| Шевкопляс Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения | |||

| - М.: Радио и связь, 1990, с.88-96. | |||

Авторы

Даты

2003-11-20—Публикация

1999-07-01—Подача