ССЫЛКИ НА РОДСТВЕННЫЕ ЗАЯВКИ

Эта заявка связана с находящейся на рассмотрении заявкой на патент, озаглавленной "Способ и устройство для определения скорости передачи данных, передаваемых с переменной скоростью в приемнике", поданной с серийным 08/079.196 18 июня 1993 года, Батлером (Butler) и др., и принадлежащей настоящему заявителю. Эта заявка включена сюда как ссылка.

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

1. Область применения настоящего изобретения

Настоящее изобретение относится, в общем, к системам для декодирования последовательных потоков данных в канале с шумом и, более конкретно, к декодеру сверточных кодов Витерби для последовательного декодирования при различных, заранее определенных скоростях передачи данных.

2. Описание области техники

В области техники цифровой связи хорошо известно, что данные могут передаваться последовательно как непрерывным образом, так и в циклах с постоянной длительностью Т во времени, каждый цикл содержит фиксированное количество битов N, которое ограничено произведением скорости последовательной передачи и длительностью цикла Т. Однако в конкретных системах связи необходимо передавать меньше, чем N данных, в течение выбранных циклов. Одна из таких систем это система передачи с многостанционным доступом с кодовым делением (СDМА), в которой используется техника расширения спектра последовательности для непосредственной модуляции несущей.

В патенте США 5103459 настоящего заявителя на имя Klein S.Gilhousen и др. описана подобная СDМА система для использования в сотовой связи. Патент 5103459 упомянут в качестве ссылки, полностью относящейся к области техники. В системе СDМА объем системы ограничен общими помехами в пределах передаваемой полосы частот. Общие помехи состоят из сигналов других пользователей, которые состоят в основном из данных вокодера (речи, преобразованной в цифровую форму). Для уменьшения уровня пользовательских помех как можно в большей степени в системе СDМА, описанной Gilhousen и др., используются данные вокодера, передаваемые с переменной скоростью и приспособленные для передачи в циклах данных с фиксированной длительностью во времени.

При некоторых сниженных скоростях передачи данных вокодера предоставляется некоторый запас в цикле данных для поддержки передачи данных посредством всего цикла. Таким образом, для цикла, в котором уменьшена полная скорость передачи данных, количество повторяемых символов исходных данных меньше, чем N, что необходимо для заполнения цикла N символами. Хотя повторение данных, передаваемых с меньшей скоростью, вызывает помехи того же уровня, что и при полной скорости передачи данных при одинаковой мощности передачи, но вспомогательная информация в цикле позволяет уменьшить передаваемую мощность в соответствии с эквивалентной "информационной мощностью" или энергией на символ. Эта техника позволяет уменьшить уровень помех, тем самым увеличивая емкость системы настолько, насколько позволяют резервы вокодера.

В качестве альтернативы повторения данных при меньшей мощности данные могут передаваться с меньшей скоростью один раз в пределах одного цикла без уменьшения мощности передачи. Эта техника позволяет осуществить передачу полной мощности во время разделения цикла и не осуществлять передачу во время неиспользуемой части цикла. Блок данных, который должен передаваться в цикле, может просто помещаться в начало цикла или в любую другую заранее определенную позицию цикла. Однако в многопользовательской системе CDMA необходима более сложная процедура помещения блоков для равномерного распределения помех со стороны многих других пользователей во всем цикле. Ненужное перехлестывание при передаче данных многими пользователями неприемлемо повышает уровень помех системы сверх оптимального среднего уровня.

В патентной заявке США с серийным номером 07/846.312, поданной 5 марта 1992 года и озаглавленной "Рандомизатор пакета данных" на имя Gilhousen и др. , принадлежащей настоящему заявителю описана усложненная процедура расположения блока для гарантии минимальных уровней помех в пределах полного цикла, и эта заявка на патент включена в качестве ссылки, полностью относящейся к области техники.

Пример системы СDМА может быть понят после рассмотрения "ПРЕДЛАГАЕМОГО EIA/TIA ВРЕМЕННОГО СТАНДАРТА: СТАНДАРТ СОВМЕСТИМОСТИ СТАНЦИИ, ОСНОВАННОЙ НА ДВУМОДНОЙ ПОДВИЖНОЙ СТАНЦИИ ШИРОКОПОЛОСНОЙ, С РАСШИРЕННЫМ СПЕКТРОМ ЦИФРОВОЙ СОТОВОЙ СИСТЕМЫ" Qualcomm, Inc., San Diego, California, апрель 21, 1992 год. Этот стандарт CDMA системы определяет пять основных режимов передачи данных канала для трафика связи как в прямом, так и в обратном направлении. Здесь имеется три режима прямой связи и два режима обратной связи. В зависимости от конкретного режима канала передачи данных определяется один из двух разных алгоритмов сверточного кодирования. Два из этих режимов непрерывные режимы, а три из них это пакетные режимы, где последовательные данные организуются в фиксированные интервалы цикла. Три режима работают только при одной из нескольких заранее определенных скоростях передачи данных, а два режима работают от цикла к циклу при одной из четырех различных заранее определенных скоростях.

Это разнообразие скоростей передачи данных и режимов каналов порождает потребность в какой-либо единой аппаратуре декодирования. Проблема становится более сложной из-за того, что последовательное кодирование в канале с широким спектром происходит в реальном времени. То есть принятый сигнал должен быть продетектирован, перекомпонован и декодирован в реальном времени. Не имеется пространства цикла, пригодного для передачи информации о исходной скорости передачи данных вокодера. Имеется весьма небольшая возможность рассмотрения принятого сигнала для нескольких возможных скоростей передачи данных для определения, какая из конкретных скоростей должна быть декодирована для каждого нового цикла. Кроме этого, желательно использовать одно и то же устройство декодирования во всех режимах канала системы для предотвращения быстрого возрастания количества компонентов. В CDМА системе, описанной в упомянутом выше патенте на имя Gilhousen и др. используется ортогональное псевдослучайное шумовое (PN) кодирование, временное уплотнение, двухпозиционная фазовая модуляция (ВРSК) с ортогональным покрытием каждого BPSK символа с одновременным расширением покрытых символов посредством фазовой манипуляции с четвертичными сигналами (QРSК) и сверточного кодирования для исправления ошибок. Каждый из этих многих способов кодирования требует определенного усилия для декодирования на принимающей стороне в каждом режиме канала. Поэтому имеется огромная конкуренция на обладание ресурсами реального времени для последовательного декодирования закодированных сверточных символов, передаваемых для исправления ошибок.

Способы декодирования для сверточных кодов хорошо известны в технике и включают алгоритм Витерби коррекции ошибок, разработанный A.J. Viterbi ("Границы ошибок для сверточных кодов и асимптотический оптимальный алгоритм кодирования", IEE Trans. Ihform. Theory, Vol. 11-13, 2, pp. 260-269, апрель 1967 год) и рассмотренный профессионалами, такими как G.D. Forney, Jr. ("Алгоритм Витерби", Proc. of the IEEE, Vol.16, pp. 268-278, 1973) и J.A. Heller и др. ("Декодирование Витерби для спутниковой и космической связи", IEEE trans. Соmmun. Technol., Vol. 11-19, 5, pp. 835-348, октябрь 1971 года).

Профессионалы уже усовершенствовали алгоритм Витерби в ответ на различные конкретные требования. Например, Hirosuke Yamamoto и др. ("Алгоритм декодирования Витерби для сверточных кодов с повторным запросом" IEEE Trans. Inform. , Theory, Vol. 11-26, 5, pp. 540-547, сентябрь 1980 года) рассматривает алгоритм декодирования Витерби с метрикой качества для повторного запроса. Их система предоставляет те же характеристики, когда приемник может использовать канал обратной связи для запроса повторной передачи, что и в случае более длинного сверточного кода, ограниченной длины без обратной связи. Yamamoto и др. добавили одиночный бит качества к выходу декодера, который указывает на "качество цикла". Если оно плохое, то запрашивается повторная передача. Они показали, что функция надежность работы их алгоритма асимптотически в два раза лучше, чем для известного алгоритма Витерби без повторного запроса.

Аналогично, N. Seshadri и др. ("Обобщенный алгоритм Витерби для определения ошибок посредством сверточных кодов", GLOBECOM 89 Dallas, Texas, pp. 1534-1538, Nov. 1989) представили два обобщенных алгоритма Витерби с полезным использованием для речи, закодированной в циклы с фиксированной длительностью. Высокая степень взаимного влияния смежных циклов речи позволяет осуществить полезную оценку содержания цикла на основании смежных циклов в ситуации, когда содержание этого цикла имеет неприемлемые уровни ошибок. Seshadri и др. показали, что может быть получено очень надежное межцикловое резервирование путем добавления битов четности к данным речи для определения ошибок при помощи высокоскоростного внешнего циклического кода блока. Увеличенный цикл затем кодируется внутренним сверточным кодом и весь блок затем модулируется и передается по шумящему каналу. Внутренний обобщенный декодер Витерби передает заранее определенное количество кандидатов для закодированного цикла, только один из которых должен иметь правильную информацию о четности. Если ни один из них не имеет правильную информацию о четности и если информационные биты представляют цикл дискретизированной речи, то может осуществляться внутрицикловая повторная оценка, либо если доступна обратная связь, то осуществляется автоматический запрос на повтор. Если имеется правильная альтернатива среди заранее определенного количества кандидатов, то повторной передачи можно избежать.

К сожалению, ни в одном из указанных выше описаний не предлагается способ декодирования в реальном времени для передачи последовательности циклов, имеющих одну из заранее определенных скоростей передачи данных, которая может меняться от цикла к циклу без передачи информации о скорости. Соответствующие неразрешенные проблемы и оставшиеся очевидные недостатки соответствующей области техники разрешаются в этом изобретении, описанном ниже.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Настоящее изобретение разрешает указанные выше проблемы путем предоставления последовательного декодера Витерби (SVD), имеющего специальные буферы входа и выхода, выполненные как устройство со сверхвысокой степенью интеграции (VLSI). Процедура Витерби используется для декодирования потока синхронизированных и дискретизированных кодовых символов в непрерывном режиме. Предоставляется несколько выходных метрик качества ("метрики ошибок") для определения скорости передачи данных. Предпочтительное исполнение SVD настоящего изобретения может осуществлять декодирование передаваемых с различными скоростями данных без предварительного предоставления информации о скорости передачи данных.

Целью настоящего изобретения является осуществление автоматического декодирования каждого цикла при одной из совокупности заранее заданных скоростей передачи данных без передачи информации о скорости. SVD настоящего изобретения осуществляет эту цель для каждого из совокупности режимов канала путем создания многократных путей для декодирования каждого цикла при каждой из всевозможных заранее определенных скоростей передачи данных и путем обеспечения "метриками ошибок", для определения исходной скорости передачи данных. Преимуществом SVD настоящего изобретения является то, что с его помощью можно осуществлять декодирование при неизвестной скорости передачи данных цикла из совокупности заранее определенных скоростей передачи данных цикла при условии, что известен сверточный код и известен также режим пакета данных (цикловой или непрерывный). Другим преимуществом SVD настоящего изобретения является то, что получается несколько "метрик ошибок" для всех декодируемых циклов при каждой гипотетической заранее определенной скорости передачи данных для использования при получении исходной скорости передачи данных.

SVD настоящего изобретения предоставляет одну из таких метрик ошибок, путем записи выходного потока декодированных данных, сравнения его с потоком входных кодовых символов для оценки коэффициента ошибок в символах (SER) входного потока. SVD настоящего изобретения может содержать другие метрики ошибок, такие как результаты контроля избыточным циклическим кодом (CRC), а также метрику качества Yamamoto (YQM). Метрика SER осуществляет оценку коэффициента ошибок в принятых кодовых символах. Результаты CRC позволяют определять ошибки в исходных двоичных данных. YQM указывает, что условия оцениваемой ошибки в декодируемом цикле превышают заранее определенный порог. Преимуществом SVD настоящего изобретения является то, что приемник предоставляет одну или более этих "метрик ошибок" в качестве средств для определения исходной скорости данных без приема информации о скорости передачи от передатчика.

Другой целью настоящего изобретения является обеспечение декодирования в одиночном SVD устройстве для всех необходимых режимов канала. SVD настоящего изобретения допускает использование одиночного VLSI устройства для обоих режимов канала как для прямой, так и обратной связи системы CDMA, приведенной в качестве примера. Например, предпочтительное исполнение этого SVD обеспечивает высокую эффективность декодирования, которая приближается к теоретическому пределу для скоростей 1/2 и 1/3 сверточных кодов, имеющих ограниченную длину 9, где данные кодового символа обрабатываются в пакетах данных с N=384 символами (скорость•1/2) или N=576 символами (1/3). Пакеты циклов начинающиеся и заканчивающиеся в любом фиксированном состоянии либо непрерывный поток информационных кодовых символов может декодироваться посредством SVD настоящего изобретения. Например, в режиме повтора каналы CDMA действуют так, что каждый символ повторяется по необходимости для заполнения цикла и повторенные символы накапливаются в одиночном символе в SVD настоящего изобретения для уменьшения скорости передачи двоичной информации и мощности. В режиме рандомизатора пакета данных (DBR) и обратной связи CDMA передается только один символ из каждого набора повторяемых символов посредством использования техники расположения псевдослучайного цикла, которая описана в приведенной выше заявке на патент на имя Gilhousen и др. Используя возможность выбора скорости передачи кодов и режимов повтора, SVD настоящего изобретения обрабатывает поток кодовых символов с любой заранее определенной эффективной скоростью передачи данных как в режиме повтора посланного сообщения, так и в обратном режиме DBR.

Еще одной целью настоящего изобретения является отделение внутренней процедуры декодирования от тактирования внешнего канала. SVD настоящего изобретения осуществляет это посредством предоставления устройства для посылки прерывания на микропроцессор канала и посредством предоставления буфера для изолирования микропроцессора от синхронизации цикла системы и для удержания декодированных данных и данных метрики качества. Кроме этого SVD настоящего изобретения содержит входной буфер, который позволяет либо принимать кодовые символы в SVD непрерывно со скоростью приема символов канала, либо передавать их на SVD в виде пакетов в качестве пакетов циклов. Специальные входные и выходные буферы позволяют SVD настоящего изобретения работать независимо от внешнего канала и тактирования микропроцессора. Гибкий интерфейс микропроцессора позволяет использовать SVD с различными системами микропроцессоров.

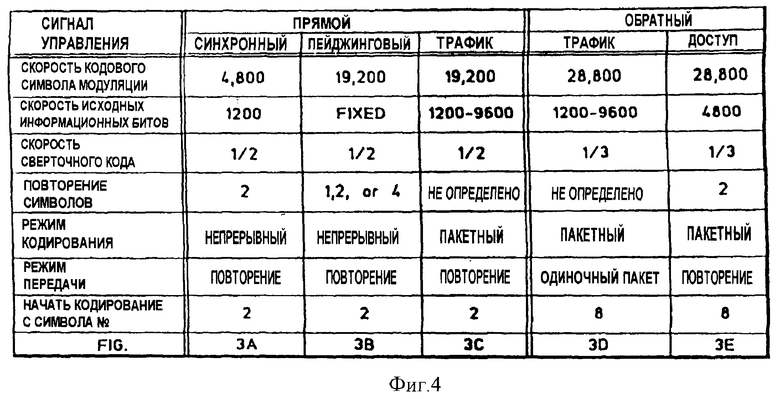

SVD настоящего изобретения содержит пять основных элементов, как показано на фиг.5. Входной буфер (IB) хранит более одного цикла данных кодового символа. В режиме блокировки это позволяет SVD осуществлять повторную обработку данных столько раз, сколько это необходимо для определения действительной скорости передачи данных в режиме повтора или DBR, используемой для этого цикла канала. Декодер Витерби (VD) принимает кодовые символы мягкого решения от IВ и обрабатывает их в логике добавления-сравнения-выбора, известной в технике. Результаты процесса ACS сохраняются в памяти внутреннего пути внутри VD. Посредством процесса обратного звена, использующего память обратного пути, получается одиночный бит данных каждого набора кодовых символов после осуществления обратного просмотра во времени посредством многих слов решений. Каждый из этих битов одиночных данных совместно с метриками качества такими, как метрика качества Yamamoto (YQM), запоминаются в выходном буфере (OВ), который является третьим элементом SVD настоящего изобретения. В режиме пакета цикла кодовые символы декодируются для четырех различных скоростей и четыре конечных декодированных пакета данных (включая информацию о качестве) запоминаются в OВ и удерживаются в течение примерно половины фиксированной длительности цикла, чтобы позволить микропроцессору осуществить их чтение. Четвертым элементом является блок управления (СВ), который создает все внутренние сигналы синхронизации, необходимые для работы SVD настоящего изобретения. Эти внутренние сигналы синхронизации получаются посредством генератора тактовой частоты CDMA системы и посредством стробирующего сигнала синхронизации внешнего декодера. DVD настоящего изобретения запускается и управляется посредством пятого элемента - интерфейса микропроцессора (MI), который связан с четвертым элементом СВ настоящего изобретения. Данные могут приниматься также и посредством MI.

Вышеупомянутые, а также другие цели, признаки и преимущества настоящего изобретения станут более очевидными после рассмотрения следующего описания, формулы изобретения и прилагаемых чертежей.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более полного понимания настоящего изобретения обратимся теперь к следующему детальному описанию исполнений, как это описано на прилагаемых чертежах, на которых:

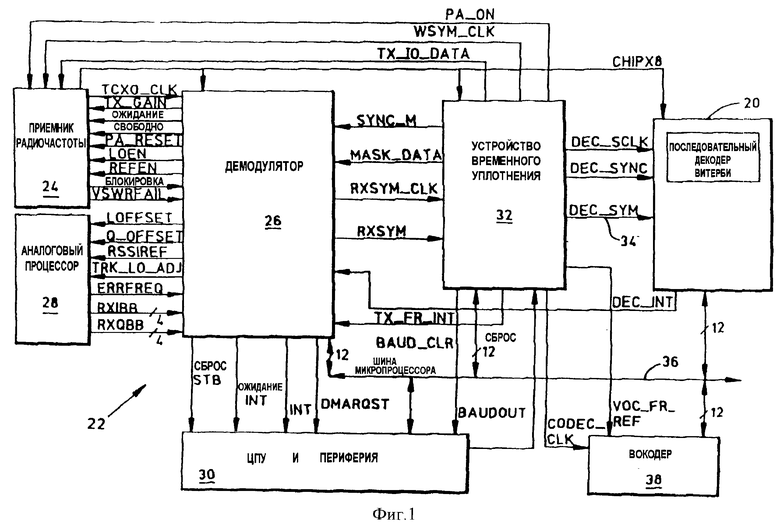

на фиг. 1 представлена функциональная блок-схема подвижного приемника CDMA;

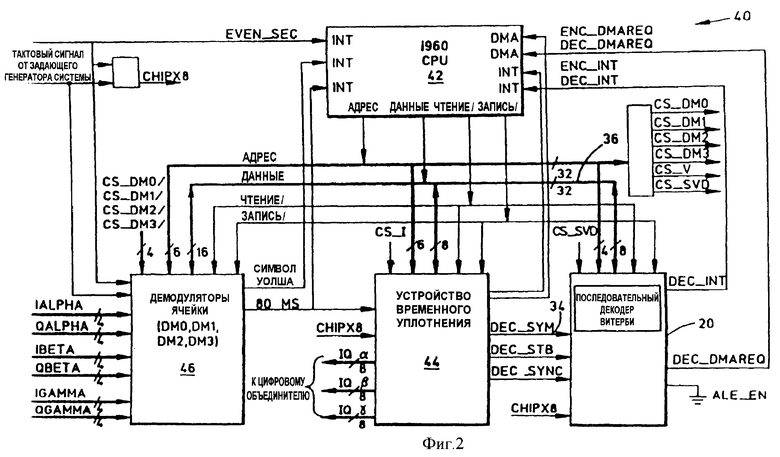

на фиг. 2 представлена функциональная блок-схема приемника платы канала ячейки CDMA;

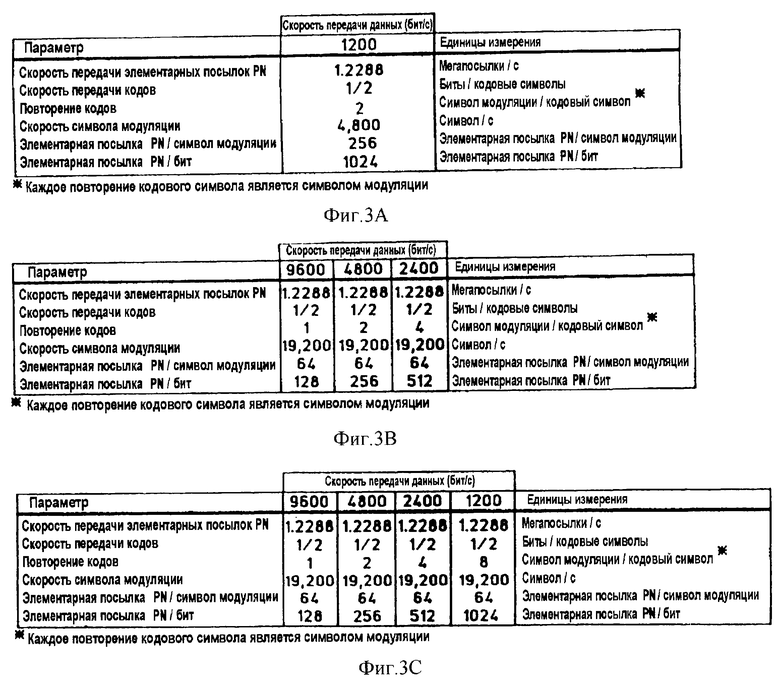

на фиг. 3, которая содержит фиг.3А-3Е, представлено описание пяти типов каналов CDMA;

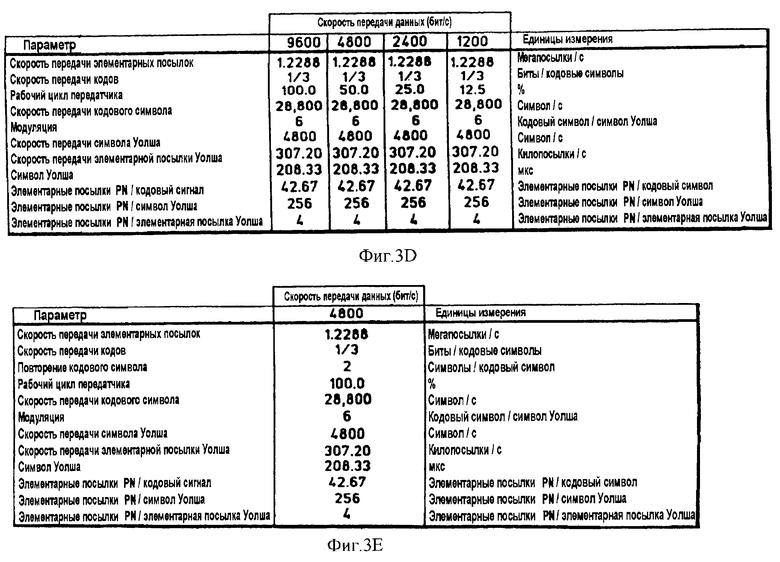

фиг.4 является описанием параметров установки нормального режима CDMA;

фиг.5 является функциональной блок-схемой последовательного декодера Витерби (SVD) настоящего изобретения;

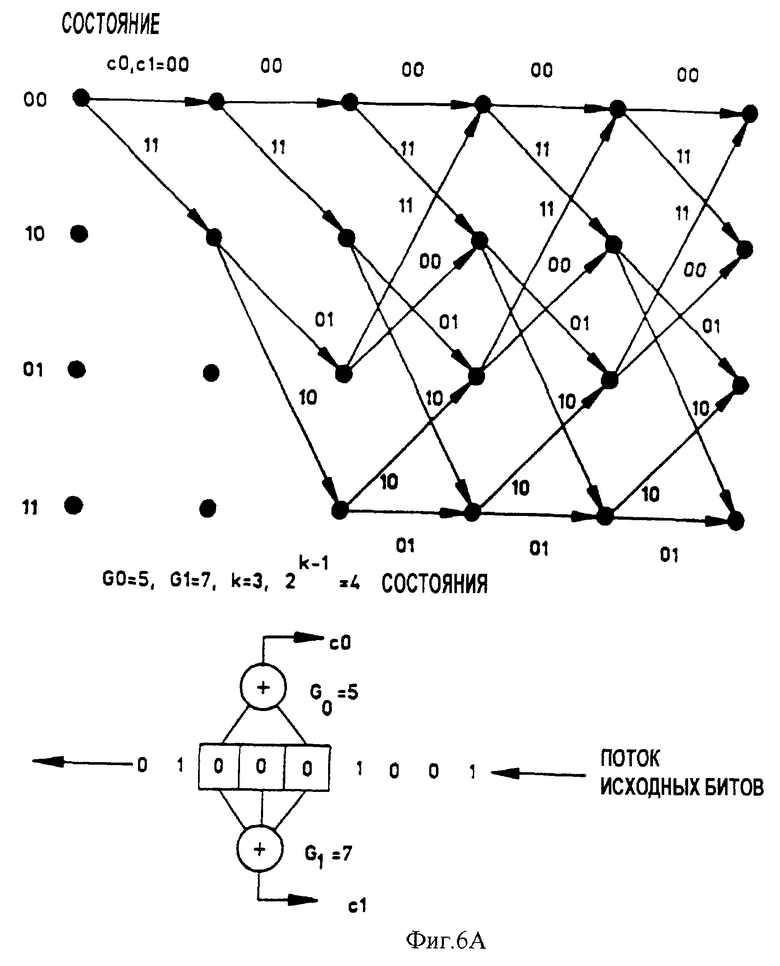

на фиг. 6, которая содержит фиг.6А-6В, показана теоретическая работа декодера Витерби;

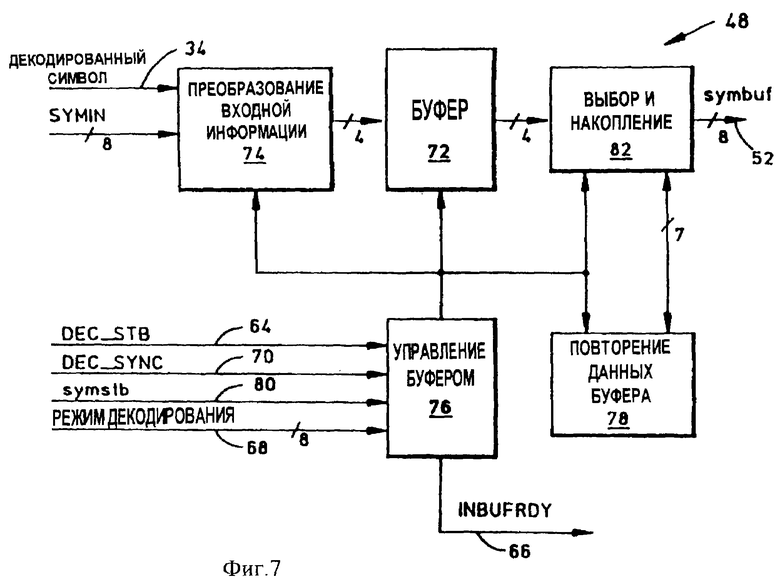

фиг. 7 является функциональной блок-схемой входного буфера (1В) настоящего изобретения;

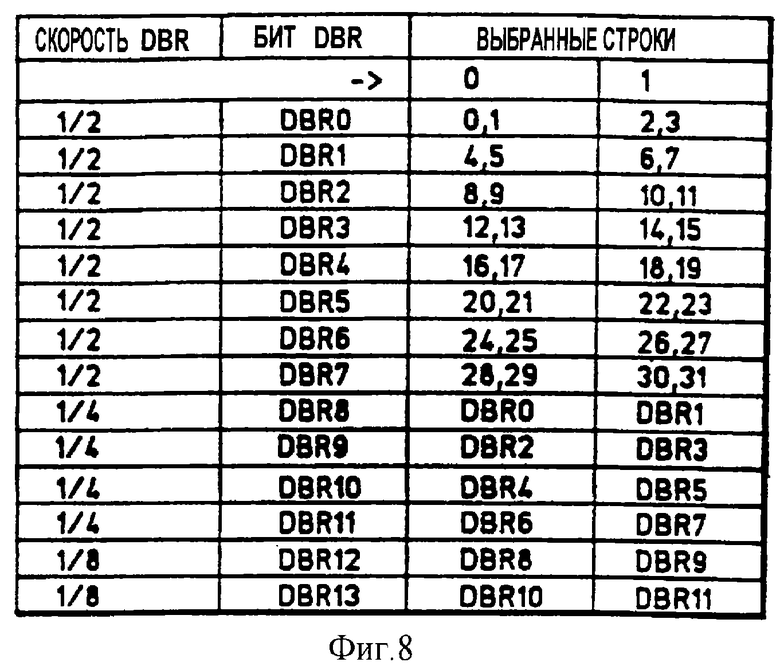

на фиг. 8 показано описание выбора символов рандомизатора пакета данных (DBR) для CDMA системы;

фиг.9 является функциональной блок-схемой элемента декодера Витерби (VD) настоящего изобретения;

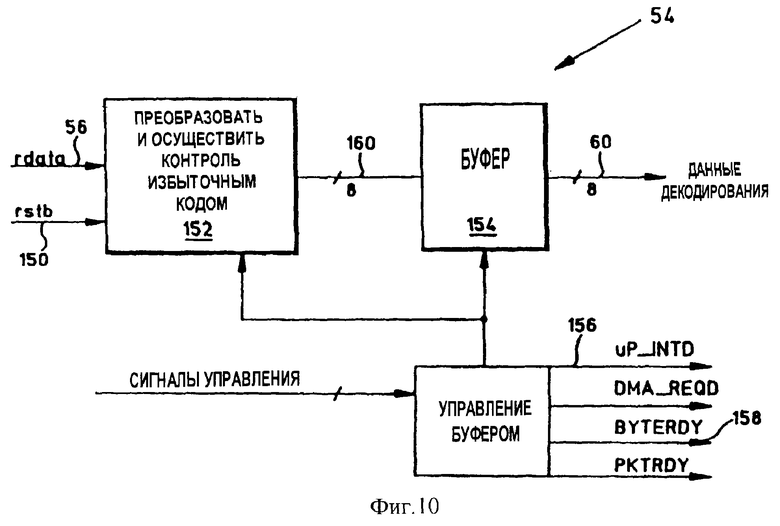

фиг. 10 является функциональной блок-схемой выходного буфера (OВ) настоящего изобретения;

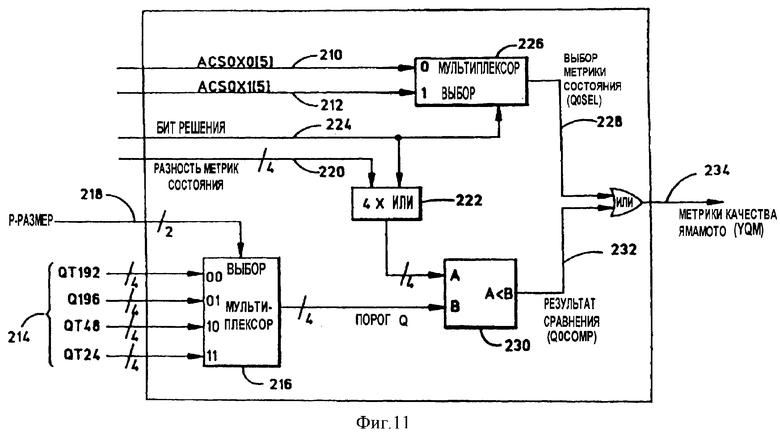

фиг. 11 является функциональной блок-схемой логики метрики качества Yamamoto (YQM) настоящего изобретения.

ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ИСПОЛНЕНИЙ

Проблема декодирования системы CDMA

Для описания и рассмотрения настоящее изобретение описано в контексте примера исполнения подвижной системы CDMA, которая описана в патенте на имя указанных выше авторов: Gilhousen и др. Однако необходимо учитывать, что настоящее изобретение можно использовать и для других типов систем связи таких, как системы частной связи (PCS), беспроводная локальная сеть, учрежденческая телефонная станция (PBX) или для других полезных систем связи. Более того, другие системы, использующие другие известные способы модуляции передачи, такие как многостанционный доступ с разделением времени (TDMA), тоже могут использовать настоящее изобретение. Как описано в упомянутом выше патенте на имя авторов: Gilhousen и др. в примере исполнения системы подвижной связи CDMA налагаются некоторые требования на аппаратуру декодирования и соответствующие процедуры, этим требованиям до сих пор не может эффективно удовлетворять известная в технике единая конструкция декодера. Эти требования приведены в сокращенном виде для пояснения.

На фиг. 1 показана блок-схема модема подвижного приемника, предназначенного для системы CDMA. Последовательный декодер Витерби (SVD) 20 настоящего изобретения показан совместно с другими элементами подвижного модема 22. Во время работы RF приемником 24 принимаются сигналы радиочастоты и демодулируются в демодуляторе 26 с участием аналогового процессора 28 и под управлением центрального блока обработки (CPU) 30. Демодулированный поток данных повторно уплотняется в аппаратуре временного уплотнения импульсных сигналов 32, которая вырабатывает поток последовательных символов на входе SVD 34. Сигналы синхронизации, тактирования и сигналы тактового генератора передаются на SVD 20 по соответствующим сигнальным линиям. SVD 20 связан с шиной микропроцессора 36 для связи с вокодером 38, который перекомпоновывает сигналы речи, которые были декодированы посредством SVD 20.

На фиг.2 показан тот же самый SVD 20, связанный с логикой канальной платы модема приемника 40 на стороне ячейки. CPU 42, устройство временного уплотнения импульсных сигналов 44 и демодуляторы 46 с функциональной точки зрения схожи с их соответствующими частями, изображенными на фиг.1. Так же, как и на фиг.1, SVD 20 принимает поток последовательных кодовых символов на входе декодера 34 и передает поток параллельных данных в шину 36 микропроцессора для передачи другим элементам (не показаны) логики 40.

Для CDMA системы, описанной в упомянутом выше патенте авторов Gilhouse и др. , SVD 20 должен работать в любом из пяти основных режимов канала для того, чтобы осуществить все необходимое декодирование данных как прямой, так и обратной линии связи. Эти режимы описаны на фиг.3А-3Е. Во время прямой связи ячейки с подвижным пользователем используются три режима, показанные на фиг. 3А-3С (синхронизации, пэйджинговый и режим трафика). Обратная связь подвижного пользователя с ячейкой использует два режима, показанные на фиг. 3D-3Е (доступ и трафик).

Фиг. 3А описывает параметры модуляции канала синхронизации прямой связи взятого в качестве примера примера. Данные канала синхронизации декодируются из канала, который кодируется сверточным образом при скорости 1/2 (ограниченной длины К=9) и каждый кодовый символ повторяется один раз. Данные передаются со скоростью 4800 символов модуляции в секунду и SVD 20 принимает сверхцикл, содержащий 384 символа модуляции за каждые 80 миллисекунд. Таким образом SVD 20 может быть согласован с фиксированной скоростью 1200 бит/с для этого канала. Исходные информационные биты кодируются как непрерывный поток без контроля избыточными циклическими кодами (CRC) на границах цикла. Эквивалентная скорость передачи двоичных данных равна 1200 бит/с.

На фиг.3В описаны параметры модуляции канала прямого пэйджинга в качестве примера. Данные пэйджингового канала кодируются из канала, который кодируется сверточным образом при скорости 1/2 (К=9) и каждый кодовый символ передается один раз, дважды или четыре раза, в зависимости от исходной скорости передачи двоичных данных. Исходная скорость передачи двоичных данных для этого канала задана и не изменяется от цикла к циклу. Таким образом SVD 20 может быть согласован с фиксированной скоростью передачи двоичных данных для этого канала. Данные передаются со скоростью 19200 символов в секунду и SVD 20 принимает цикл, содержащий 384 символов модуляции в каждые 20 милисекунд. Данные кодируются в непрерывный поток без CRC кодов на границах цикла.

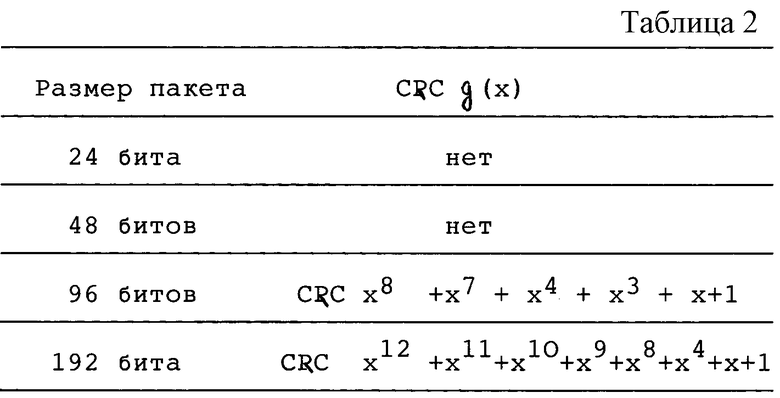

На фиг.3С представлены параметры модуляции канала прямого трафика в качестве примера. Данные канала трафика прямой связи декодируются из канала, который сверточно кодируется при скорости 1/2 (К=9) и каждый кодовый символ передается до девяти раз, в зависимости от исходной скорости передачи двоичных данных, выбранной для каждого цикла вызывающим вокодером. Исходная скорость передачи двоичных данных может изменяться от цикла к циклу под управлением вызывающего вокодера и SVD 20 должен декодировать при любых возможных скоростях для всех циклов, так как эта данная скорость передачи данных не может быть задана. Данные передаются со скоростью 19200 символов модуляции в секунду (сим/с) и SVD 20 принимает новый цикл с 384 символами модуляции в каждые 20 милисекунд. Эти данные кодируются в пакеты, которые начинаются и заканчиваются в нулевом состоянии ("0" биты добавляются в конец каждого цикла до кодирования) и ожидается CRC код в конце каждого пакета из 96 исходных битов и 192 исходных битов. Никакой код CRC не ожидается для более коротких (48 и 24 бита) пакетов, так как ограничение пространства делает CRC довольно дорогим.

На фиг. 3D даны параметры модуляции канала обратного трафика в качестве примера. Данные канала трафика обратной линии декодируются из канала, который сверточно кодируется со скоростью 1/3 (К=9). Каждый кодовый символ повторяется до семи раз (что порождает восемь вариантов), но только один из повторяемых кодовых символов передается в пакете. Синхронизация пакета определяется случайным числом, которое выбирается из последних нескольких битов кода PN для предыдущего цикла. Скорость повторения кодового символа зависит от скорости передачи данных вызывающего вокодера для каждого цикла. SVD 20 должен осуществлять декодирование одновременно для всех скоростей и для каждого цикла, так как исходная битовая скорость передачи двоичных данных может изменяться от цикла к циклу вызывающим вокодером. Хотя SVD 20 не знает исходную скорость передачи двоичных данных для конкретного цикла, но синхронизация пакета для каждого цикла повторяемых символов осуществляется на основании последних нескольких битов кода PN предыдущего цикла. Данные передаются со скоростью 28800 кодовых символов в секунду и SVD 20 принимает цикл, содержащий 576 возможных кодовых символов кода в каждые 20 милисекунд. Данные кодируются в пакеты, которые начинаются и заканчиваются в нулевом состоянии, так как "0" биты добавляются в конец каждого пакета. Код CRC ожидается на конце каждого пакета 96 исходных битов и 192 исходных битов (сразу же после последовательности "0" битов). Циклы, содержащие меньше, чем 96 исходных битов, пропускают код CRC для сохранения пространства.

На фиг. 3Е в качестве примера представлены параметры модуляции канала доступа обратной линии. Данные канала доступа обратной линии декодируются из канала, который сверточно кодируется со скоростью 1/3 (К=9) и каждый кодовый символ передается дважды. Исходная скорость передачи двоичных данных зафиксирована на 4800 бит/с и SVD 20 для этого канала приспособлен для работы на этой одной фиксированной скорости. Данные передаются со скоростью 28800 кодовых символов в секунду и SVD 20 принимает цикл, содержащий 576 кодовых символов за каждые 20 милисекунд. Данные кодируются в пакеты, которые начинаются и заканчиваются в "0" состоянии (добавляется "0" биты к концу каждого пакета) но CRC код не предоставляется.

SVD настоящего изобретения пригоден для любого из пяти описанных примеров канала, представленных на фиг.3, из-за его возможности непрерывного декодирования для многих скоростей возможности переключения из непрерывного режима в пакетный режим и возможности переключения (1/2 и 1/3) скоростей сверточного кодирования. Что наиболее важно, SVD настоящего изобретения может осуществлять декодирование данных канала как прямого, так и обратного трафика. Такое разделение канала прямого и обратного трафика можно лучше оценить после рассмотрения вышеупомянутого патента авторов Gilhousen и др. и заявки на изобретение.

На фиг.4 представлена таблица, в которую сведены все функции управляющих сигналов, необходимые для SVD настоящего изобретения в случае каждого из пяти каналов, рассмотренных выше в качестве примеров со ссылкой на фиг.3. Необходимо учитывать, что исходные скорости передачи двоичных данных канала прямого пэйджинга и sync канала зафиксированы.

ИСПОЛНЕНИЕ МОНОЛИТНОГО SVD

Предпочтительно, чтобы SVD настоящего изобретения был выполнен как схема со сверхвысокой степенью интеграции, (VLSI). На фиг.5 показаны пять основных элементов примера исполнения примера SVD 20. Входной буфер (IB) 48 запоминает 1.5 цикла данных, тем самым допуская несколько путей декодирования для одиночного цикла, что позволяет позже определить правильное повторение или скорость передачи данных в режиме рандомизатора пакета данных (DBR) для цикла. Декодер Витерби (VD) 50 принимает символ мягкого решения от IB 48 по 7-битной шине symbuf 52. Эти кодовые символы обрабатываются логикой добавить-сравнить-выбрать (ACS) и результаты запоминаются в качестве метрик состояний во внутренней оперативной памяти (ОЗУ). Решения после ACS обработки запоминаются во внутренней памяти путей. Процесс по обратной цепи посредством этой памяти путей определяет одиночные выходные информационные биты для каждой группы кодовых символов после обратного просмотра во времени 64 уровней слов решений для гарантии, что рассматриваемый путь совпадает с наиболее вероятным глобальным путем. Эти выходные двоичные данные совместно с информацией о метрике качества (QM) запоминаются в выходном буфере (OВ) 54 посредством линии данных 56. После завершения декодирования посредством VD 50, OB 54 возвращает декодиророванные информационные биты для осуществления доступа со стороны интерфейса микропроцессора 58 по шине decdata 60. В пакетном режиме кодовые символы декодируются на четырех исходных различных скоростях передачи двоичных данных и четыре результирующих выходных пакета данных запоминаются в OВ 54 совместно с дополнительными данными QМ. Это приготовление предоставляет процессору (не показан) примерно 10 милисекунд на считывание данных в OВ 54. SVD 20 запускается и управляется посредством интерфейса микропроцессора 58 и контроллера 62, которые создают все необходимые сигналы синхронизации для SVD 20. Сигналы синхронизации получаются на основании сигналов задающего генератора системы и стробирующего сигнала декодера (не показан).

АЛГОРИТМ ДЕКОДИРОВАНИЯ ВИТЕРБИ

Общая теория работы декодера Витерби хорошо известна в технике и может быть оценена после обращения к одной из вышеупомянутых ссылок. Теперь эта теория будет кратко описана для облегчения оценки настоящего изобретения.

Сверточные кодер преобразует последовательность исходных двоичных данных (поток входных битов) в последовательность кодовых символов (входной поток символов). Для каждого входного бита имеется несколько выходных кодовых символов, которые определяются этим входным битом и предыдущими (К-1) входными битами, где К ограниченная длина для кодера. Количество кодовых символов, создаваемых для каждого двоичного символа, определяется скоростью кодирования; то есть, например, два символа для скорости 1/2 и три символа для скорости 1/3. Каждый кодовый символ создается путем сдвига и осуществления операции XOR над входным потоком в соответствии со специальным полиномиальным кодом, таким как код скорости 1/2 G1, представленный последовательностью х8+х6+х5+х4+1 (октальное значение 05618). Количество битов в полиномиальном коде такое же, как и значение ограниченной длины, которое зафиксировано на девяти для предпочтительного исполнения SVD настоящего изобретения. Действительные коды (G0, G1) или (G0, G1, G2) выбираются на основании моделирования несистематических кодов, создаваемых для получения кодов с наилучшими свойствами с точки зрения ошибок в подвижном окружении. Предпочтительные сверточные коды, используемые в приведенной в качестве примера системе CDMA, которые обсуждались выше, имеют следующие значения для прямой линии G0= 07538, и G1=05618): а для обратной линии G0=05578, G1=06638 и G2=07118. Эти сверточные коды обеспечивают минимальную свободную дистанцию Хамминга, равную 12 для скорости кодирования 1/2, и минимальную свободную дистанцию Хамминга, равную 18 для скорости кодирования 1/3.

Алгоритм декодирования Витерби работает путем определения наиболее вероятной последовательности декодирования для входного потока кодовых символов. Прежде всего вычисляются метрики состояний или весы соответствующих вероятностей для каждого возможного пути. Наиболее вероятные преобразования для каждого состояния сохраняются в памяти путей для всех состояний и затем декодер осуществляет просмотр или образует обратную цепь во времени посредством наиболее вероятной последовательности для выбора каждого выходного бита. Основными шагами этого процесса являются создание метрики ветки, создание метрики состояния и определение пути обратного звена. Характеристики декодера для конкретной ограниченной длины и скорости определяются тремя параметрами: величиной шага и количеством уровней квантования входных кодовых символов, процедурой нормализации метрики состояния и глубиной действующего обратного звена памяти путей.

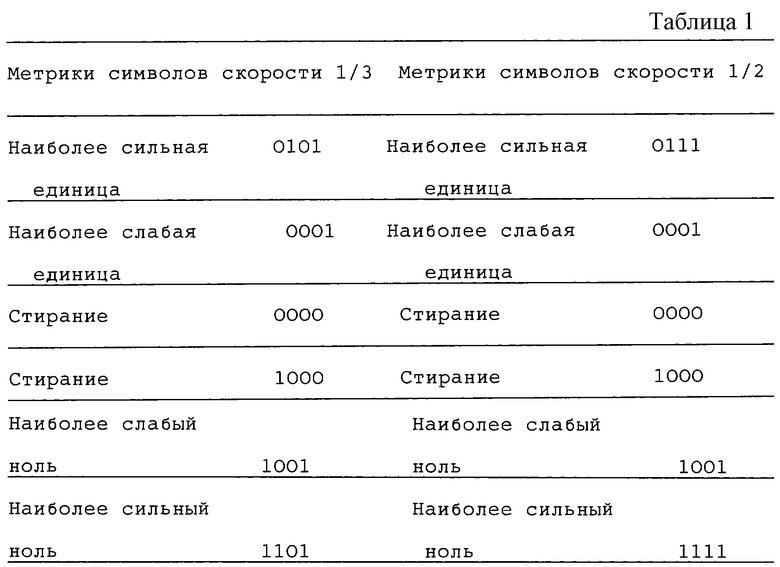

Метрики веток являются функциями цен, которые соответствуют логарифму вероятностей того, что во время преобразования каждое возможное преобразование битов входные кодовые символы данного мягкого решения. Информация о знаке и величине в мягких решениях масштабируется и объединяется для создания метрики каждой ветки. Для скорости 1/2 имеется четыре возможных метрики. Для скорости 1/3 имеется восемь, а для произвольной скорости 1/n имеется 2n возможных метрик. Используемые для подсчета и масштабирования метрик веток уравнения выбираются так, чтобы получить наилучшие характеристики декодера для оконечного канала, используя опыт и моделирование. Эти уравнения используются в SVD логике настоящего изобретения. Входы метрики масштабируются величинами символьной метрики, которые хранятся в таблице символьной метрики (SMT) в VD 50. Уровень "стирания" вызывает игнорирование кодового символа при вычислении метрики ветки. Стирание может использоваться для "протыкания" кода, когда необходима более высокая скорость канала для передачи данных. Кроме этого, стирание может быть использовано для удаления некоторых кодовых символов канала, которые являются частью "укрытых" данных или канала управления. Так как стертый кодовый символ не влияет на значение метрики, то разумная степень стирания не имеет ощутимого воздействия на характеристики декодирования.

Сверточные коды могут создавать неограниченную последовательность кодовых символов, но определенные свойства кодов дают возможность уменьшить количество последовательностей символов. Первое свойство состоит в том, что интерес представляет наилучший (наиболее возможный) путь к состоянию, так как любой глобальный путь через состояние должен следовать некоторому наилучшему локальному пути. Второе свойство заключается в том, что структура сверточного кода повторяется и имеет симметричное кодовое дерево. Последовательности кодов поэтому должны преобразовываться в эквивалентные последовательности, создаваемые конечным числом образцов потока уникальных битов. Для данной ограниченной длины К имеется 2К-1 возможных образцов двоичных данных (названных здесь "состояниями"), которые необходимо оценить для выделения наиболее вероятного глобального пути.

На фиг.6 показано типичное представление совпадающих последовательностей или путей в виде решетчатой диаграммы для примера кода К=3 (1/2), основанного на G0= 58 и G0=78. Необходимые для преобразования состояний символы показаны на этой диаграмме. Для каждого состояния вычисляется метрика состояний (не показана), которая представляет относительную вероятность того, что данный путь следует через это состояние. Расчет метрики состояния осуществляется посредством процесса добавления-сравнения-выбора (ACS). Метрика состояния для каждого возможного состояния предшествующего настоящему состоянию добавляется к метрике ветки для преобразования из этого предыдущего состояния в настоящее состояние. Эти суммы сравниваются и выбирается наиболее вероятное преобразование, которое соответствует наименьшей сумме, и назначается настоящему состоянию в качестве метрики состояния. Бит решения для каждого ACS является величиной самого младшего разряда (самый последний разряд) для предыдущего состояния с которого начинается выбранное преобразование. Решения для всех состояний в столбце решетки становятся словом памяти путей.

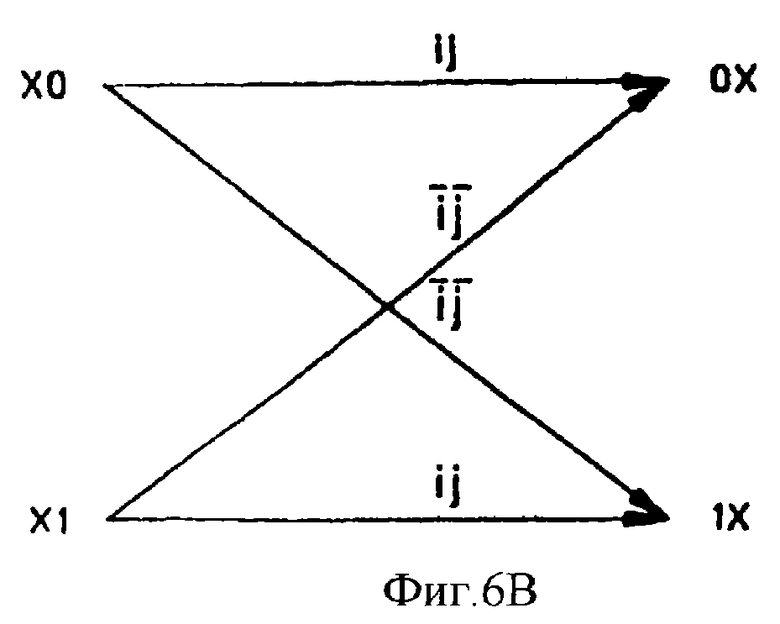

Так как первый и последний члены в формирователе полиномов (G0 и G1) являются единицами, то гипотезы (i, j) для передаваемых символов (G0, G1), по двум путям входящим или покидающим любое состояние, являются взаимодополняющими в двоичной системе. Это взаимоотношение состояний ACS изображается графически в виде диаграммы бабочки на фиг.6В. Разумеется, в бесшумном канале величины кодовых символов (G0, G1) свободны от ошибок и их метрики состояний либо нулевые, либо сосредоточены на максимальной величине, причем нулевая метрика состояния представляет состояние на наиболее возможном глобальном пути.

Как показано на фиг. 6В, метрика ветки от состояния х0 к состоянию 0х добавляется к метрике состояния х0 для определения первой из двух возможных метрик 0х состояния. Вторая возможная метрика 0х состояния определяется путем добавления метрики ветки от состояния х1 к величине х1 метрики состояния. Последняя из этих возможных величин затем назначается в качестве новой величины 0x метрики состояния. Этот процесс повторяется для х1 состояния и для всех других состояний в этом столбце решетки. Для каждого нового набора кодовых символов создается новый столбец в соответствии с одиночным исходным битом. Разность между каждой парой метрик состояния сравнивается с заранее определенной предельной величиной качества (QT) для получения метрики качества Yamamoto (YQM) или "q-бита" для нового состояния способом, предложенным Yamamoto и др. в упомянутом выше труде и, как описано ниже, в соответствии с фиг.12.

Как только матрица локальных АСS решений запоминается в памяти путей, процесс обратного звена следует некоторому пути, идущему в обратном направлении в соответствии с этой матрицей. Обратное звено начинается в "наилучшем состоянии", указанном массивом ACS, и затем использует решение для этого состояния (двоичные адреса) из слова памяти путей для определения предыдущего наилучшего состояния (наиболее вероятного). Обратное звено проходит через, по крайней мере, пять или шесть решений с ограниченной длиной для того, чтобы гарантировать, что путь следования сольется с наиболее вероятным глобальным путем. Для ограниченной длины, равной 9, достаточна глубина пути обратного звена, равная 63 состояниям. Последнее решение в конце обратного звена принимается в качестве наилучшего решения для этого выходного бита, полученного от декодера Витерби. Для каждых следующих исходных двоичных данных создается новое слово решения и новое наилучшее состояние на основании массива ACS и осуществляется повторение процесса обратного звена от нового столбца решетки с той же самой длиной пути. Таким образом, каждый новый двоичный символ проходит вперед окно в 64 состояния обратного звена из памяти путей в соответствии с одним столбцом решетки.

В рассмотренном выше примере, описывающем цикл в соответствии с фиг.3, для всех режимов работы, где данные помещены в пакеты, кодирование начинается и заканчивается во всех "нулевых" состояниях путем включения хвоста из восьми "0" битов в конец данных. При многократном декодировании SVD заставляет вводить биты решения в память путей, когда первые восемь столбцов решетки каждого цикла равны нулю. Это гарантирует, что выбранный путь для каждого цикла начинается и заканчивается в общем "нулевом" состоянии для всех возможных скоростей передачи данных.

ОПИСАНИЕ ВХОДНОГО БУФЕРА (IB)

Дальнейшее описание функционирования SVD 20 настоящего изобретения основано на этих иллюстративных определениях для различных циклов обработки.

Внутренний тактовый генератор CHIPX8: он является основным тактовым генератором для работы внутреннего устройства и его частота предпочтительно равна 9.8304 МГц.

Цикл вычислений: это время на обработку метрики ветки и каждой пары предыдущих метрик состояний посредством АСS пары 108 (фиг.9) и эквивалентов двум внутренним циклам тактового генератора CHIPX8.

Цикл обработки: это время на обработку одного исходного двоичного данного посредством обратного звена и эквивалентно 128+3 циклам вычислений, необходимым на полную обработку метрики 64 веток посредством ACS логики 106.

Цикл блока: это время обработки пакета цикла, имеющего один из четырех возможных размеров и эквивалентно одному из следующих циклов обработки: 192, 96, 48 или 24.

Цикл буфера: это время на обработку всех возможных четырех скоростей передачи пакетов для цикла и время на осуществление конечных операций скачка обратного звена и очистки VD 50. Это эквивалентно 432 циклам обработки (192+96+48+24+72).

Цикл: это временное окно, необходимое для посылки всех кодовых символов в пакет и обычно равно 29 милисекундам за исключением случая sync канала, где хранятся циклы длительностью в 16.67 милисекунд, для формирования одного сверхцикла длительностью в 80 милисекунд.

На фиг. 7 изображена схематическая блок-схема, иллюстрирующая предпочтительное исполнение входного буфера (IB) 48 настоящего изобретения. IB 48 принимает кодовые символы по входной линии декодера 34 и передает эти кодовые символы, выбранные и накопленные для всех возможных скоростей данных вокодера на symbuf шину 52. Как показано на фиг.4, IВ 48 работает в режиме повтора для каналов прямой линии и либо в режиме повтора, либо в произвольном режиме пакетов данных (DBR) для каналов обратной линии. В режиме повтора IB 48 накапливает кодовые символы для их передачи на шину symbuf 52 со скоростями передачи накопленных символов, равными 1/2, 1/4 и 1/8 скоростей передачи выходных кодовых символов, для последующей передачи с исходной полной скоростью. В режиме DBR IВ 48 выбирает кодовые символы для составления пакетов данных с размерами 1/2, 1/4 и 1/8, которые помещаются в цикл в соответствии с рандомизированным кодовым словом, получаемым из последних нескольких битов последовательности РN предыдущего цикла, для последующего формирования пакета блока полного цикла. Входные кодовые символы, передаваемые по входной линии декодера 34, одинаковы, что и для обоих режимов IB. Двоичные кодовые символы запоминаются посредством линии DECSTB 64 и затем, после того как IВ 48 принимает достаточное количество кодовых символов для осуществления процесса декодирования VD 50, передается стробирующий сигнал готовности на VD 50 по линии INBUFRDY 66. Затем IB 48 передает кодовые символы в последовательности по требованию VD 50 по symbuf шине 52.

Режим декодера управляется посредством слова управления режимом по шине DECMODE 68, которое содержит несколько битов управления, влияющих на работу IB 48. Различные режимы работы IB 48 можно оценить после рассмотрения фиг.4. Несколько сигналов шины DECMODE 68 кроме этого определяют сигнал тактирования для стробирующего сигнала по линии inbufrdy 66 к VD 50. Один из этих битов определяет границы кодового символа для каждого из четырех различных размеров пакетов в соответствии с четырьмя альтернативными скоростями передачи битов данных, описанных выше со ссылкой на фиг.3. Другие биты в шине DECMODE 68 определяют были ли повторенные кодовые символы накоплены IВ 48 до передачи на шину sumbuf 52 или были ли они просто выбраны в соответствии с позиционным кодом DBR.

Каждый входной цикл для SVD 20 начинается стробирующим сигналом линии DECSYNC 70. Стробирующий сигнал линии DECSYNC 70 передается в течение по крайней мере 15 циклов внутреннего генератора тактовых сигналов (CHITPX8) до приема стробирующего сигнала по линии DECSТВ 64, чтобы до получения первого кодового символа пакета осуществить выдержку по времени, необходимую для запуска IВ 48. После каждого стробирующего сигнала линии 70 IB 48 ожидает приема либо 384, либо 576 кодовых символов, передаваемых в буфер 72, по линии DECSTB 64. Скорость сверточного кода (фиг.4) определяет ожидаются ли 384 (= 2•192) или 576 (=3•192) кодовых символа. Двоичные кодовые символы на входе декодера 34 непрерывно и последовательно тактируются, начиная от самого старшего разряда (МSВ) и кончая самым младшим разрядом (LSВ), внутренним задающим генератором СНIРХ8 (не показан). LSВ каждого символа помечается стробирующим сигналом в линии DECSTB 64 и весь кодовый символ фиксируется в параллельный регистр символов 74. Если символы кода пришли от аппарата временного разуплотнения импульсных сигналов, то входные символы тактируются линией decstb 64 со скоростью 384 символа на цикл. Во время работы в канале обратной линии кодовые символы, полученные от аппарата временного разуплотнения блока, и входные кодовые символы объединяются в пакет в IB 48 со скоростью, доходящей до максимальной (один кодовый символ за каждые семь циклов внутреннего генератора тактовых сигналов СНIРХ8). Максимальная скорость передачи пакета ограничивается логикой проверки (не показана),

которая допускает считывание кодовых символов из буфера 42 после его заполнения. Логика управления буфером 76 создает сигнал в линии INBUFRDY 66, чтобы информировать контроллер 62, когда можно начать использовать шину symbuf 52.

Стробирующим сигналом INBUFRDY по линии 66 сбрасывается двухбитовый "р-размерный" счетчик (не показан) в устройстве управления буфером 76. Содержимое счетчика р-размера показывает размер пакета для кодового символа шины symbuf 52, который может содержать 24, 48, 96 или 192 исходных битов. Стробирующий сигнал по линии 66 запускает VD 50 и двумя битами шины DECMODE 68 (см. фиг.4) указывается некоторое количество кодовых символов, которые должны быть приняты IВ 48 до запуска линии 66. Такая выборочная задержка стробирующего сигнала линии INBUFRDY 66 позволяет оптимизировать обработку задержки в SVD 20.

После осуществления стробирования линии INBUFRDY 66 сбрасываются адреса считывания из буфера 72 и адреса записи в буфер повтора 78. После этого первый кодовый символ буфера 72 выбирается с упреждением и фиксируется в шине symbuf 52. Указатель адреса считывания для буфера 72 затем увеличивается и после предварительного выбора фиксируется следующий кодовый символ в шине 52, которая отвечает за стробирующий сигнал линии symstb 80. Считывание IB стробирующего сигнала по линии symstb 80 ограничено одним циклом чтения на каждые семь циклов внутреннего генератора тактового сигнала CHIPX8 для осуществления выдержки времени, необходимого на поочередное выполнение операций чтения и записи для буфера 72. Количество кодовых символов, которые должны быть считаны для текущего цикла, указывается сигналами по шине DEVMODE 68. После того как кодовые символы, представляющие 192 исходных информационных битов, считываются из буфера 72 для первого цикла, пакеты, содержащие 96, 48 и 24 битов, считываются затем из буфера повтора 78 в соответствии с выбранной и накопленной логикой 82. Адреса чтения и записи буфера повтора 78 сбрасываются и увеличивается счетчик р-размера (не показан) в устройстве управления буфером 76 после считывания последнего кодового символа каждого пакета. Содержимое счетчика р-размера определяет адрес кодового слова, выбираемого из буфера 72 или буфера повтора 78, а также управляет выбором и накоплением логики 82 для представления правильного кодового символа шины symbuf 52. Указатель адреса считывания для буфера повтора 78 увеличивается после каждого чтения, когда счетчик р-размера ненулевой. Указатель записи для буфера повтора 78 увеличивается на единицу после любого другого считывания либо из буфера 72, либо из или буфера повтора 78. Кодовые символы выдаются из IB 50 в той же последовательности без учета режима работы SVD 20, но VD 50 пропускает неиспользуемые пакеты во время работы при постоянной скорости повтора в непрерывном режиме.

По мере считывания кодовых символов из буфера 72 в режиме повтора каждая пара кодовых символов суммируется в соответствии с логикой 82 и запоминается в буфере повтора 78. Накапливающий сумматор устанавливается в нулевое состояние, когда осуществляется стробирование линии INBUFRDY 66 и после записи суммы каждой пары в буфер повтора 78. По мере считывания кодовых символов из буфера повтора 78 они также суммируются парами и записываются обратно в буфер повтора 78. Эта же операция повторяется над каждой парой символов из пакетов с 192, 96 и 48 символами. 7-битная длина слова буфера повтора 78 позволяет запоминать без разделения сумму до 8 таких кодовых символа. Во время работы в режиме DBR запомненный кодовый символ, передаваемый в накапливающий сумматор в соответствии с логикой 82, обнуляется так, что выходом логики 82 является символ, переданный из буфера 72. Запись в буфер повтора 78 допустима только для символов, выбранных в соответствии с двоичными кодами RBR (не показаны). Содержимое регистра р-размера и адрес строки (номер переданного интервала) управляют выбором двоичного кода DBR, используемого для выбора символов. Набор двоичных кодов DBR выбирается таким образом, чтобы двоичные коды DBR для любой меньшей скорости были бы подмножеством двоичных кодов DBR для более высокой скорости.

Канал синхронизации прямой линии использует циклы длительностью в 26.67 милисекунд с 128 символами и эти символы передаются непрерывным потоком с постоянной скоростью 4800 символов в секунду. IB 48 принимает три цикла синхронизации от аппаратуры временного разуплотнения за 80 милисекунд для создания одного пакета декодера, содержащего 384 символа, но необходим только один стробирующий сигнал по линии decsync 70 от аппаратуры временного разуплотнения для этого "сверхцикла". Каждый кодовый символ канала синхронизации повторяется дважды и циклы длительностью в 80 милисекунд этого 1200 бит/с канала декодируются как 96-битовые пакеты с коэффициентом повтора символов, равным двум. Канал синхронизации работает в непрерывном режиме, но выходные данные задерживаются на 71 бит из-за задержки в SVD 20. Первый бит в каждом пакете это двадцать шестой бит пакета синхронизации длительностью в 26.67 милисекунд, который принял 6 пакетов перед текущим пакетом. Эти детали синхронизации поддерживаются контроллером 62 и микропроцессорным интерфейсом 58 (фиг.5).

В каналах обратной линии 576 символьные циклы могут передаваться в IВ 48 с частичной, доходящей до частоты передачи элементарных посылок, которая составляет одну восьмую частоты внутреннего генератора тактовых сигналов CHIPX8. Кодовые символы записываются последовательно в буфер 72, который может быть рассмотрен как 32 строки в массиве из 18 столбцов. Кодовые символы считываются и записываются по столбцам. То есть кодовые символы считываются из буфера 72 в том же порядке, в котором они были записаны. После получения шестого символа пакета IB 48 может начать посылку на VD 50 тройку кодовых символов (представляющих единый исходный информационный бит) в течение всех циклов обработки до окончания обработки всего пакета. После сбрасывания и окончания цикла каждого буфера, биты, выбранные DBR на входе декодера 34, непрерывно тактируются внутренним задающим генератором в регистр DBR кода (не показан). Четырнадцать битов, оканчивающихся DBR-13 в стробирующем сигнале в линии DECSYNC 70, фиксируются в качестве слова DBRCODE для следующего цикла буфера. Эти биты DBR CODE, от DBR-0 до DBR-13, используются для выбора кодовых символов, которые необходимо записать в буфер повтора 78, из символов, имеющих полную скорость передачи посылаемых на VD 50 по шине 52. После обработки полного пакета оставшийся в буфере повтора 78 пакет с половинным размером обрабатывается аналогичным образом. По мере пересылки символов пакета с половинной длиной на VD 50 по шине 52 те символы, которые были выбраны DBRCODE, повторно записываются в буфер повтора в качестве пакета с четвертым размером. Пакет с четвертым размером и последующий пакет с восьмым размером обрабатываются аналогично.

На фиг.8 показан алгоритм выбора символов DBRCODE, который используется для определения, какие из 16 интервалов (пары строчек) выбираются из буфера 72. Для полноскоростной работы передаются все 16 интервалов (32 строки). Независимо от того, был ли отключен передатчик во время времени передачи некоторых промежутков при меньших скоростях. Например, с четвертой скоростью передается только один из четырех интервалов в качестве первых 36 кодовых символов. Кодовые символы передаются по строкам, но аппаратура временного разуплотнения посылает их на SVD 20 по столбцам. Так как алгоритм передачи DBR перескакивает строки в аппаратуре временного разуплотнения, то для дробных скоростей в сущности имеется меньшее количество строк. Для 1/4 скорости DBR буфер 72 содержит только восемь строк данных и символы шума в оставшихся строках. В отличие от трафика обратной линии, канал доступа обратной линии (фиг. 3Е) работает в режиме повтора при 1/3 скорости сверточного кода с повторением символов кода дважды для обеспечения коэффициента, равного примерно 2.5 дБ по каналу обратного трафика. Алгоритм передач DBR можно лучше оценить после обращения к указанной выше заявке на патент авторов Gilhousen и др.

Кроме функциональной логики, показанной на фиг.7, IB 48 также содержит логику тестирования для проверки работоспособности посредством самотестирования.

Элемент декодера Витерби (VD) настоящего изобретения

На фиг. 9 показана функциональная блок-схема для VD 50, который обрабатывает кодовые символы, получаемые по шине 52 от IВ 48. VD 50 передает декодированный поток двоичной информации по линии rdata 56 совместно с информацией о качестве. Эти функции осуществляются в шести субмодулях, показанных на фиг. 9. Два бита, полученные по шине DECMODE 68, управляют работой VD 50 по линии DECRATE 84 и линии PACKET 86. Таблица данных, хранимая в таблице символьной метрики (SМТ) 88, является программируемой таблицей для просмотра, которая преобразует символы 7-битного кода шины 52 в соответствующую 4-битовую шкалу для правильной работы логики метрики ветки 90. SМТ 88 обеспечивает гибкостью, необходимой для осуществления различных режимов работы. Информация управления для VD 50 обычно посылается вначале вызова обработки пакета и не изменяется в течение приема трафика. Сигнал DECRATE по линии 84 определяет сколько кодовых символов содержится в вычислениях метрики ветки, а сигнал РАКСЕТ, передаваемый по линии 86, вызывает создание величин метрик состояний вначале каждого пакета. Содержимое SMT 88 используется для преобразования 4, 5, 6, и 7-битовых входных кодовых символов, полученных по шине 52 в масштабированные входные кодовые четырехбитные символы для логики метрики ветки 90 внутренней SMTSYM шины 92. Эти преобразования включают необходимую компенсацию удваивания, возведения в квадрат и возведения в четвертую степень кодовых символов, накопленных в IB 48 для пакетов данных меньшей скорости. Каждый кодовый символ, введенный по шине 52 предоставляет адресные биты более низкого порядка для SMт 88 и данные по этим адресам затем выдаются в качестве SMTSYM величин по шине 92. SMT 88 запоминает отдельные данные для каждой из четырех скоростей как в режиме повтора, так и в режиме DBR.

Для каждого пакета VD 50 запоминает след бита качества, представляющего метрику качества Yamamoto (YQМ). Бит качества для наилучшего состояния (нулевого по определению) последнего цикла обработки для каждого размера пакета запоминается в регистре YQМ 93 и используется позже при определении исходной скорости передачи данных.

Логика 94 коэффициента ошибок по символам (SЕR) сравнивает приблизительные решения i-го и j-го символа с величинами с0 и с1, получаемыми от повторно закодированных выходных данных для создания байта SЕR для каждого пакета шины SERROR 96. Эта величина для шины 96 достигает предела при 255 и также используется позже при определении исходной скорости передачи данных.

SMT 88 содержит оперативную память (RAM) и хранимую логику управления для уплотнения адреса записи и стробов записи в RAM. 7-битный входной символ шины SYMBUF 52 используется для LSB адреса для величины 4-битных данных, вид которых принимает выходной символ шины SMTSYM 92. Величина р-размера по шине р-размера 98 формирует два MSВ адреса RАМ и может выбирать различные преобразования для различных пакетов для компенсации сумм накопления, введенных посредством IВ 48.

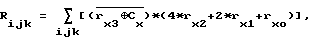

Ветки решеток (фиг.6А), по которым работает декодер Витерби, отмечаются парами (с0, с1) для скорости 1/2 кода и тройками (c0, с1, с2) для скорости 1/3 сверточного кода. Таким образом, до работы любого ACS должна быть рассчитана метрика ветки для каждой из двух возможных величин (c0, c1) или для трех возможных величин (c0, с1, с2) для скоростей 1/2 и 1/3 соответственно. Эти метрики веток рассчитываются в соответствии с приведенным ниже уравнением 1. Например, в течение каждого цикла вычисления, логика метрики ветки 90 создает новую пару метрик Rijk по шине ВМЕТR81С 100. Все это рассчитывается на основании входного символа (r1, r2, r0) шины SMTSYM 92 и гипотезы для передаваемого символа (с2, с1, с0) по шине hyp 102 от синхронизирующей логики управления 104.

(1)

(1)

где С является i-, j- или k-гипотезой шины 102 для целевого АСS состояния, rx3 является знаком каждого кодового символа шины 92 и rx2, rx1, rx0 являются тремя LSВ метрики каждого символа шины SMTSYM 92.

Каждая из трехсимвольных метрик шины 92, представляющая единый исходный информационный бит, запоминается в наборе входных защелок (не показаны) логики метрики ветки 90. Пара (или тройка) кодовых символов входной информации приспосабливаются к скорости декодирования 1/2 (или 1/3) для предоставления четырехбитных пар метрики ветки шины 100. Третий символ шины 92 устанавливается в нулевое состояние, если линия DECRATE 84 определит скорость сверточного кодирования равной 1/2. Пары метрики ветки шины 100 передаются логике добавить-сравнить-выбрать (ACS) 106, где выбирается одна из двух метрик веток во время каждого цикла вычислений ACS. Для каждой гипотезы о входных данных вычисляется 4-битная метрика ветки шины 100 в соответствии с уравнением 1. 4-битная метрика ветки также создается в качестве дополнения гипотезы. В этой формуле величина кодового символа добавляется к метрике Rijk, если знак символа кода соответствует гипотезе, в противном случае к метрике добавляется ноль. Ожидается, что значения метрики ветки со скоростью 1/2 будут изменяться от нуля до 14, а значения метрики ветки со скоростью 1/3 будут изменяться от нуля до 15. Сумматор метрики ветки ASС логики переполняется при 15.

Метрики шины 92 от SМТ 88 до логики метрики ветки 90 представляются в формате величины-знака и определяются стирания посредством величины символа в соответствии с табл.1.

Если метрики символа за пределами ожидаемого диапазона для скорости 1/3 переполнят сумматоры, то метрики ветки шины 100 переполняются при 15 (11112).

Логика ACS 106 обрабатывает метрику входной ветки шины 100 в течение любого цикла вычисления, для которого она действует. Пара блоков АSС логики 108 обрабатывает 4-битовую метрику ветки шины 100 и пятибитные метрики состояний из RАМ состояний 110 для получения пары битов решения по внутренней шине 112 и новой пары метрики состояний по другой внутренней шине 114. Биты решения шины 112, которые являются LSВ наилучшего предыдущего состояния для каждой пары АSС 108, сдвигаются на 8-битовую выходную защелку 116. 8-битовый байт решения каждой четверки пар решений выдается по шине решений 118 на логику обратного звена 120.

В течение первого цикла обработки для каждого пакета метрика для нулевого состояния устанавливается в нуль и все другие метрики устанавливаются в их предельные значения во время их считывания из RAM состояний 110. Решения шины 118 и наилучшие состояния шины 122 устанавливаются в нулевое состояние в пакетном режиме для первых восьми циклов обработки каждого цикла. Метрики новых состояний, наименьшие суммы метрики предыдущего состояния и метрика связывающей ветки записываются обратно в RАМ состояний 110 в место, которое рассчитывается посредством сдвига текущего состояния из МSВ в LSВ. Решение нулевой гипотезы выбирается для равных метрик. В защелку наилучшего состояния 124 записывается новая метрика для нулевого состояния вначале каждого цикла обработки. Все другие метрики нового состояния в текущем цикле обработки сравниваются с текущим наилучшим состоянием из защелки 124 и наименьшая метрика заменяет прежнюю метрику наилучшего состояния в защелке 24. Метрика наилучшего состояния предыдущего цикла обработки вычитается из каждой метрики состояний после ее считывания из RAM состояний 110 в течение текущего цикла обработки. Логика ACS 106 продолжает накапливать и нормализовать метрики до обработки всех четырех пакетов кодовых символов.

Метрика качества Yamamoto (YQМ) или "q-бит" присоединяется к каждой метрике состояния. Бит YQМ для исходного нулевого состояния устанавливается "хорошим" или верным (0), а все другие YQМ биты устанавливаются "плохими" или неверными (1) в течение первого цикла обработки IВ. Бит VQМ устанавливается в состояние неверно (1) для каждой новой метрики состояния вычисляемой посредством логики ACS 106, если бит YQМ для выбранной предыдущей метрики состояния был неверным или если разность метрик при ACS вычислении меньше либо равна заранее определенной граничной величине качества (QТ), описываемой в регистре предельной величины качества (см. MUX216 на фиг.11).

Важным элементом настоящего изобретения является набор "метрик ошибок", создаваемый во время декодирования и содержащий три типа информации о качестве. Для нескольких гипотез скоростей передачи данных (например, 9600, 4800 и т.д.) SVD 20 создает один или более независимых элементов метрики качества. Это включает контроль избыточным циклическим кодом (СRС), коэффициент ошибок по символам (SER) и метрику качествa Yamamoto (YQМ). YQМ здесь названа "q-битом". Некоторые метрики ошибок пропускаются на более низких скоростях передачи данных. CRC и SER, метрики хорошо известны в технике. Метрика YQM может стать понятной после рассмотрения указанного выше труда Yamamoto и др. и нижеприведенного рассуждения со ссылкой на фиг.11. Эти метрики ошибок используются для выбора наиболее вероятной исходной скорости передачи данных посредством способа, описанного в упомянутой выше заявке на патент авторов Butler и др.

Декодированные символьные данные предоставляются для каждой гипотезы скорости передачи данных и запоминаются в OВ 54. Данные цикла для каждой гипотезы содержат три элемента метрики качества. Элемент CRC обсуждается ниже со ссылкой на фиг.10. Элемент SER обсуждается ниже со ссылкой на фиг.9, где изображен SER 140. На фиг.11 показана блок-схема части пары АСS 108 (фиг.9), которая создает YQМ бит.

Как показано на фиг. 6В, метрика ветки от состояния х0 к состоянию 0х добавляется к метрике состояния х0 для определения первой из двух возможных метрик состояния 0х. Метрика второго возможного состояния 0x находится путем добавления метрики ветки от состояния х1 к значению метрики состояния x1. Последняя из этих двух возможных величин затем назначается как значение метрики нового состояния 0х. Этот процесс продолжается для состояния 1х и для всех других состояний в этом столбце решетки. Бит YQМ является меткой, показывающей, что разность между парой величин метрик состояний 0х меньше, чем заранее определенная граничная величина (QТ), или что имеется следующее состояние, которое меньше, чем заранее определенная QT. На фиг.11 LSB для АСSOх0 состояния представлена на линии 210 и бит YQМ для АСSОх1 состояния представлен на линии 212. Группа граничных величин QТ 214 показана для совокупности 4-битных шин к мультиплексору МUХ 216. Шина р-размера 218 выбирает одну из QT групп 214, в зависимости от текущей гипотезы скорости передачи данных. Важным элементом настоящего изобретения является то, что каждая граничная величина качества (QТ) в группе 214 является программируемой и может настраиваться индивидуально или совместно для приспособления к различным режимам работы. Так как различные гипотезы скорости передачи данных могут иметь различные QT, то MUХ 216 осуществляет коммутацию альтернативных членов QТ группы 214.

Обратимся теперь к фиг.11, здесь вычисляется разность между парой метрик состояний ACS и передается по шине 220 на ХОR, логическую ветку с четырьмя ветками 222. Бит решения для линии 224 используется для выбора наиболее вероятного из двух метрик в мультиплексоре 226 для запуска МЕТОDIF по шине 220. Выход линии 228 от MUX 226 является битом метрики состояния, выбранным из шин 210 и 212. Выходная линия 228 подвергается операции OR на выходе компаратора 230 в линию 232 для получения и передачи бита YQМ в линию 234. Компаратор 230 сравнивает выбранное из группы 214 QТ с разностью метрик состояний шины 220 (после учета знака вентиля ХOR 222). Бит YQМ 234 передается на регистр YQМ 93 (фиг.9).

Полученный таким образом бит YQМ передается для учета текущего состояния в решетку Витерби (фиг.6А). Процедура YQМ имеет то свойство, что устанавливает "плохой" YQМ бит в любом состоянии решетки Витерби для продвижения вперед по дереву решений. Бит YQМ 234 является меткой, которая указывает, что разность между двумя метриками приближающихся состояний больше или равна выбранной QТ величине. Если эта разность больше, чем величина QТ, то бит YQМ принимает значение бита YQМ предыдущего состояния. Если эта разность меньше, чем выбранная величина бита YQM, то бит YQМ нового состояния устанавливается в состояние "плохой" или "1". Перед началом операции по декодированию с любой гипотезой скорости нулевое состояние решетки Витерби помечается "хорошими" YQM битами ("0"), а все другие состояния решетки помечаются "плохими" YQМ битами. В конце процедуры декодирования гипотезы скорости цикл помечается либо как "хороший", либо как "плохой" в зависимости от бита YQМ для конечного нулевого состояния, который хранится в регистре 93 и выдается ACS логикой 106 (фиг.9). Так как каждый цикл вокодера укомплектован строчкой из восьми нулей (00000000), то декодер знает, что правильное конечное состояние цикла - это нулевое состояние.

Логика обратного звена 120 содержит память путей 126, которая имеет 64 слова из 256 битов решения каждое. Память путей 126 считывается дважды и затем записывается один раз в течение каждых четырех циклов вычисления. Таким образом, логика обратного звена 120 может записывать 256 битов в одиночное слово памяти пути и может считывать бит из каждого из 64 слов памяти путей в течение каждого цикла обработки. Логика обратного звена 120 содержит мультиплексор 128, генератор адреса 130 и совокупность защелок данных 132. Генератор адреса 130 определяет адрес слова, которое должно быть записано и первое считывание обратным звеном цикла обработки начинается с предыдущего записанного слова.

Процесс обратного звена заканчивается после чтения записи в память нулей записи пути 126 в самоопределяющей последовательности. Восемь LSВ считанного адреса начинается с наилучшего состояния шины 122 для последнего слова решения шины 118. Этот адресный бит будет нулем для последнего слова (так как входы наилучших состояний устанавливаются в состояние ноль) и для первых восьми слов каждого цикла блока (так как здесь входы решения и наилучшего состояния устанавливаются в нулевое состояние). Это решение запоминаемое согласно адресному биту для каждого считанного слова передвигается по адресу чтения в качестве LSВ для адресного бита в следующем считанном слове. Восемь LSB считанного адреса, которые формируют адресный бит, в слове решения сдвигаются на один бит для передвижения МSВ (восьмибитный адрес) в LSB позицию. Этот сдвиг компенсирует заказ решений парой ACS 108. Генератор адреса 130 уменьшает адрес слова после каждого считывания в обратное звено от адреса самого нового до адреса наиболее старого слова решения в памяти путей 126. Бит решения при 63-м чтении передается по внутренней битовой линии 134 на выходные защелки данных 132. Каждый цикл содержит 432 цикла обработки, включая 192 цикла для полной скорости передачи данных, 96 цикла для половинной скорости передачи данных, 48 циклов для четвертичной скорости передачи данных и 24 цикла для одной восьмой скорости передачи данных.

Работа обратного звена осуществляет те же функции как в пакетном, так и непрерывном режиме за исключением управления наилучшего состояния, описанного выше. Выходные биты линии 134 синхронизируются логикой обратного звена 120 по линии r-данных 56... (как раньше).

Логика коэффициента ошибок по символам (SЕR) 94 осуществляет повторное кодирование выходного потока данных по линии r-данных 56 и сравнивает вновь созданные кодовые символы с кодовыми символами, принятыми SVD 20 по входной линии декодирования 34. Сигнал стробирования по линии SYMSTB 80 синхронизирует знаковый бит r3 каждой метрики символа по шине 92 с первым-пришел-первым-обслужен (FIFO) 136, что компенсирует запаздывание в магистральной линии и в обратном звене в VD 50. Кодер 138 и счетчик ошибок 140 сбрасывается перед началом подготовки каждого цикла к тактированию каждого бита по линии 56 в 9-битный регистр сдвига в кодере 138. Осуществляется подсчет количества символов кода, которые не сравниваются в 8-битном счетчике ошибок 140, который имеет предел 255. Выходная информация счетчика 140 передается посредством шины SERROR 96 на OВ 54, где она сдвигается и защелкивается в соответствующем регистре.

Логика управления тактированием 104 запускает VD 50 после приема сигнала по линии INBUFRDY 66 и затем согласует тактирование других элементов VD 50. Логика 104 запускает два стробирующих сигнала (или три для скорости 1/3) по линии SYMSTB 80 для тактирования данных по SMT 88 в логику метрики ветки 90 и SER логику 94. В течение каждого цикла расчета VD 50 обрабатывает символ текущего информационного бита для одной гипотезы по hyp шине 102 с ACS парой 108. Цикл обработки содержит 128 циклов вычислений для обработки каждого двоичного символа любого ACS состояния. Так как сверточный кодер имеет ограниченную длину девять для настоящего исполнения, то имеется 29-1=256 состояний для всех исходных символов информационных битов (в каждом столбце решетки). Счетчик последовательности состояний логики управления тактированием 104, осуществляет подсчет в течение 256 состояний (2 состояния за один цикл подсчета), передавая результаты подсчета по шине STATESEQ 142. Другие элементы логики управления тактированием 104 кодируют содержимое регистра состояния для создания гипотез по hyp шине 102. Другие сигналы управления передаются по шине ACSSТАТЕ 144 (а) для запуска освобождения ACS обработки и логики 106, (b) для обнуления входов метрики состояний, связанных с ACS парой 108 в течение первого цикла обработки, (с) для установки флага в конце каждого цикла обработки так, чтобы можно было сохранить наилучшее состояние и (d) для запуска защелки решения 116 для каждого цикла расчета.

Логика управления тактированием 104 определяет адреса чтения и записи для памяти путей 126 и передает эту информацию по адресным шинам 146 и 148 соответственно. 11-битный счетчик (не показан) логики 104 увеличивается во время каждого чтения для создания адреса чтения для каждого байта решения шины 118. Одно из 32 записей битов решений по шине 118 осуществляется в течение каждых четырех циклов вычислений во время цикла обработки. Создается 6 MSB адреса чтения по шине 146 той же самой логикой, которая создает стробирующие сигналы чтения и дважды уменьшает адрес между стробирующими сигналами записи. Сигналы управления, необходимые для загрузки, сдвига и обнуления LSB считываемых адресов по шине 146 подаются от тактирующего устройства в логике 104. То же самое устройство тактирования определяет также и сигнал стробирования RSTB по линии RSTB 150 для согласования работы логики обратного звена 120 и логики SER 94. Логика тактирования и управления 104 тоже создает сигналы тактирования для повторного сброса и запуска счетчика ошибок 140 в SER 94.

Выходной буфер (OВ) настоящего изобретения

На фиг. 10 показана функциональная блок-схема, показывающая работу выходного буфера (OВ) 54. Декодированные данные преобразуются по шине rdata 56 в байты логики конвертера 152 и запоминаются в буфере 154. Конвертер 152 проверяет также код СRС пакета обычным образом. Эти пакеты и байты состояний для пакетов доступны для микропроцессорного интерфейса 58 по шине DECDATA 60 в течение примерно 10 милисекунд, начиная с момента посылки прерывания на микропроцессорный интерфейс 58 по линии INTD 156. Результаты CRC проверки в пакетов запоминаются в регистре состояния (не показан). Полиномы CRC, используемые конвертером 152, зависят от размеров пакетов (см. табл.2).

Используемые CRC имеют форму g(х)=р(х)*(х+1) и используются известные простые полиномы 2118 (8916) и 53618 (AFl16) для р(х).

Используемая в конвертере 152 логика для проверки СКС хорошо известна в науке и состоит из регистра, который ответвляется в соответствии с полиномом CRC, причем выходная информация ответвления накапливается после прохождения вентиля ХОR.

После обработки цикла четыре раза в пакетном режиме или один раз в непрерывном режиме и после записи данных для всех четырех скоростей в OB 54 прерывание линии 156 устанавливается в состояние верно (1). SVD 20 осуществляет последовательную обработку посредством тех же 432 циклов обработки для каждого цикла пакетного режима независимо от действительной скорости передачи данных или размера пакета. Таким образом, прерывание по линии 156 посылается с фиксированным запаздыванием по отношению к стробирующим сигналам входного кодового символа по линии 64 (фиг.7). В непрерывном режиме фиксированная задержка зависит от действительного размера пакета. Прерывание INTD по линии 156 автоматически сбрасывается после семи циклов внутреннего тактового генератора CHIPX8. Микропроцессор (не показан) может использовать этот сигнал прерывания или сигнал синхронизации цикла для указания, когда необходимо осуществить считывание выходных данных. Буфер 154 содержит необходимое пространство для хранения полного набора пакетов, тем самым допуская меньшее время обработки цикла, примерно 10 милисекунд для считывания выходных данных микропроцессорным интерфейсом 58 (фиг.5). Последние восемь битов каждого пакета нулевые в пакетном режиме, так как SVD 20 работает в пакетном режиме, при условии, что передающий кодировщик был предварительно обработан и установлен в нулевое состояние. Регистр DECDATA (не показан) в буфере 154 автоматически обновляется следующим байтом из буфера 154 после каждого чтения. Данные предварительно выбираются для минимизации времени ожидания микропроцессором следующего байта, но предварительный выбор все еще требует четырех внутренних циклов тактового генератора CHIPX8. Если микропроцессор может считать OВ 54 быстрее, чем один раз за каждые четыре внутренних цикла тактового генератора CHIPX8, то микропроцессор должен тестировать сигнал BYTERDY по шине BYTERDY 158, чтобы гарантировать, что выходное слово считано дважды. Информация о качестве ("метрика ошибок"), включенная в выходные данные, может использоваться микропроцессором для выбора наилучшего пакета из четырех доступных в OВ 54 в соответствии со способом указанной выше заявки на патент авторов Вutler и др.

Конвертер 152 передает информационные биты на буфер 154 в каждые 8 циклов обработки. Данные передаются по внутренней шине 160 на буфер 154 перед началом следующего цикла обработки. По мере поступления каждого информационного бита по линии 56 он тактируется в СRС генераторе (не показан) конвертера 152. Этот СRС генератор сбрасывается для всех данных перед началом каждого пакета. В конце 96 и 192 пакетов битов оставшаяся в СRС информация проверяется и устанавливается СRС бит в регистре STATUS (не показан), если вся оставшаяся информация нулевая. Считанные данные проверяются до посылки прерывания по линии INTD 156 и после каждого считывания. После посылки прерывания INTD по линии 156 указатель адреса чтения устанавливается на нулевой адрес. Сигнал SYTERDY устанавливается в нулевое состояние по линии 158 после каждого чтения и удерживается там до защелкивания нового байта данных в регистре DECDATA (не показан) буфера 154. OВ 54 кроме этого содержит логику тестирования для самотестирования правильности функционирования.

Контроллер и элементы интерфейса процессора настоящего изобретения

Как показано на фиг.5, контроллер 62 передает тактирующие и управляющие стробы на SVD 20. SVD 20 запускается в соответствии с частотой внутреннего генератора тактового сигнала CHIРХ8 и контроллер 62 передает последовательность стробирующих сигналов и сигналов запуска в соответствии с частотой этого внутреннего генератора тактирующего сигнала. Эти сигналы управления могут запускаться путем сброса для тестирования, но во время нормальной работы они последовательно участвуют в фиксированном наборе операций, отвечающих за сигналы DECMODE шины 68, и затем возвращаются в исходное состояние. Последовательность сигнала управления запускается вновь после каждого строба декодера в линии 70 (фиг.7). Сигнал подтверждения правильности звена, указывающий на правильность данных обратного звена, выполняет работу по запуску стробирующего сигнала RSTB по линии 150, вследствие чего начинается передача данных на OВ 54. Интерфейс контроллера 62 и интерфейс микропроцессора 58 содержат регистры управления микропроцессором, необходимые для правильной работы, включая регистр управления и сброса линии. В этих двух элементах содержится также и логика специального самоконтроля.

Действительное исполнение внутренних модулей каждого из описанных выше элементов SVD 20 может быть выполнено подходящим способом, известным в технике, но их предпочтительно выполнить в виде монолитной интегральной микросхемы.

Хотя предложения, примеры и исполнения настоящего описания предполагают последовательную обработку для достижения необходимых целей, но знакомым с данной областью техники очевидно, что логика рассмотренного декодера может быть повторена в многократных параллельных декодерах, которые работают совместно, чтобы предоставить столько выходов, сколько имеется скоростей передачи данных в системе передачи.

Настоящее изобретение может быть изменено также, например, посредством использования кодирования избыточным циклическим кодом для стольких скоростей передачи данных, сколько потребуется для рассматриваемой системы.

Очевидно, что другие исполнения и модификации настоящего изобретения легко могут получить те, кто знаком с данной областью техники после рассмотрения приведенных предложений. Поэтому настоящее изобретение ограничено только следующей формулой изобретения, которая учитывает все такие исполнения и модификации, если ее рассматривать совместно с приведенными выше заявками и прилагаемыми чертежами.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ДЕКОДЕР ВИТЕРБИ | 2010 |

|

RU2421900C1 |

| СПОСОБ ПЕРЕДАЧИ ГОЛОСОВЫХ ДАННЫХ В ЦИФРОВОЙ СИСТЕМЕ РАДИОСВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2301492C2 |

| АРХИТЕКТУРА ДЕКОДИРОВАНИЯ ПО ВИТЕРБИ ДЛЯ ИСПОЛЬЗОВАНИЯ В ПРОГРАММНО-УПРАВЛЯЕМЫХ РАДИОСИСТЕМАХ | 2006 |

|

RU2363098C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ В ПРИЕМНИКЕ СИСТЕМЫ СВЯЗИ СКОРОСТИ ПЕРЕДАЧИ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ПЕРЕМЕННОЙ СКОРОСТЬЮ | 1994 |

|

RU2188509C2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ В ПРИЕМНИКЕ СИСТЕМЫ СВЯЗИ СКОРОСТИ ПЕРЕДАЧИ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ПЕРЕМЕННОЙ СКОРОСТЬЮ | 1994 |

|

RU2160966C2 |

| ДЕКОДЕР ВИТЕРБИ С КАНАЛОМ ОЦЕНКИ ТЕКУЩЕГО ОТНОШЕНИЯ СИГНАЛ-ШУМ | 2010 |

|

RU2434325C1 |

| ВЫСОКОСКОРОСТНОЙ МОДУЛЬ СЛОЖЕНИЯ (СРАВНЕНИЯ) ВЫБОРА ДЛЯ ДЕКОДЕРА ВИТЕРБИ | 2000 |

|

RU2246751C2 |

| КОМПОНЕНТНЫЙ ДЕКОДЕР И СПОСОБ ДЕКОДИРОВАНИЯ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2000 |

|

RU2247471C2 |

| ДЕКОДЕР СВЕРТОЧНЫХ КОДОВ ДЛЯ DVB-T ПРИЕМНИКА | 2008 |

|

RU2399157C2 |