Область техники

Изобретение относится к области систем передачи информации и предназначено для измерения значения отношения сигнал-шум на входе декодера и адаптивного декодирования сверточных кодов с учетом текущего отношения сигнал-шум.

Уровень техники

Сверточное кодирование-декодирование широко используется в спутниковых системах передачи информации, например в каналах передачи данных спутниковых радионавигационных систем (GPS L5, GPS L2C, Galileo), а также в системах передачи дифференциальных поправок с геостационарных спутников (WAAS, EGNOS).

Известны декодеры сверточных кодов, использующие алгоритм декодирования Витерби, например патенты США 4.802.174, 4.905.317, 5.432.803, 5.390.198.

Недостатком указанных устройств является невозможность формирования оценки текущего значения отношения сигнал-шум на входе декодера.

Наиболее близким к заявленному решению является устройство по патенту США 4.802.174 от 31.01.1989 (G06F 11/10, 371/46).

Его недостатком является невозможность формирования оценки текущего значения отношения сигнал-шум на входе декодера.

Целью заявляемого решения является устранение недостатков известных устройств.

Раскрытие изобретения

Цель заявляемого решения достигается тем, что дополнительно введен канал измерения текущего значения отношения сигнал-шум, которое может быть использовано для индикации качества канала связи, для формирования сигнала перезапроса пакета данных в каналах с перезапросом, для выбора канала с лучшими показателями качества в многоканальных системах, для синхронизации декодера, для расчета реберных метрик (метрик переходов) в случае, если при декодировании учитываются параметры плотности распределения условных вероятностей, и для прочих нужд.

Предлагаемое устройство основывается на оценивании глубины истории декодирования, на которой все пути декодирования сходятся.

Данное устройство отличается:

- от устройств, учитывающих разность путевых метрик, тем, что обеспечивает независимость показаний от амплитуды входного сигнала;

- от устройств с прямым оцениванием вероятности ошибки в канале (BER monitor) тем, что обеспечивает более широкий диапазон оцениваемых значений как в области больших, так и в области малых отношений сигнал-шум.

Известные декодеры Витерби с каналом оценки текущего отношения сигнал-шум включают в себя последовательно соединенные:

- блок вычисления метрик переходов,

- блок расчета метрик и памяти путей,

- блок формирования информационного символа,

а также подключенные к блоку расчета метрик и памяти путей

- память минимальных метрик путей,

- память метрик путей и

- память путей, причем входом устройства является вход блока вычисления метрик переходов, а выходом - выход блока формирования информационного символа.

Заявляемое устройство в отличие от известных декодеров содержит последовательно соединенные:

- блок оценки глубины истории декодирования, на которой все пути декодирования сходятся,

- блок оценки отношения сигнал-шум,

при этом вход блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, соединен с вторым выходом памяти путей, а первый выход блока оценки отношения сигнал-шум соединен с первым управляющим входом блока вычисления метрик переходов и управляющим входом блока расчета метрик и памяти путей, второй выход блока оценки отношения сигнал-шум соединен со вторым управляющим входом блока вычисления метрик переходов и является выходом устройства, на который при его работе выдается сигнал, соответствующий оценке текущего отношения сигнал-шум.

Описание чертежей

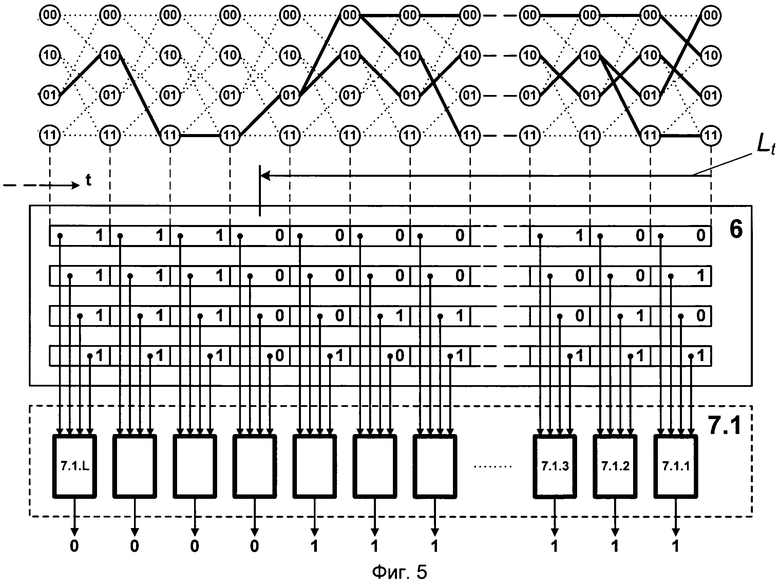

На Фиг.1 приведена структурная схема заявленного устройства.

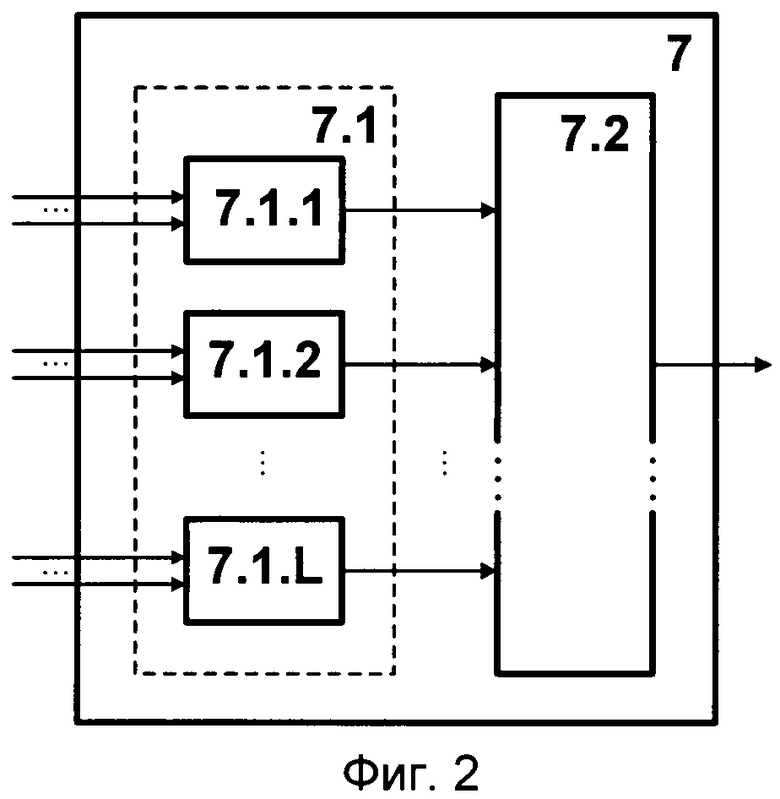

На Фиг.2 приведен вариант технической реализации блока оценки глубины истории декодирования, на которой все пути декодирования сходятся (7).

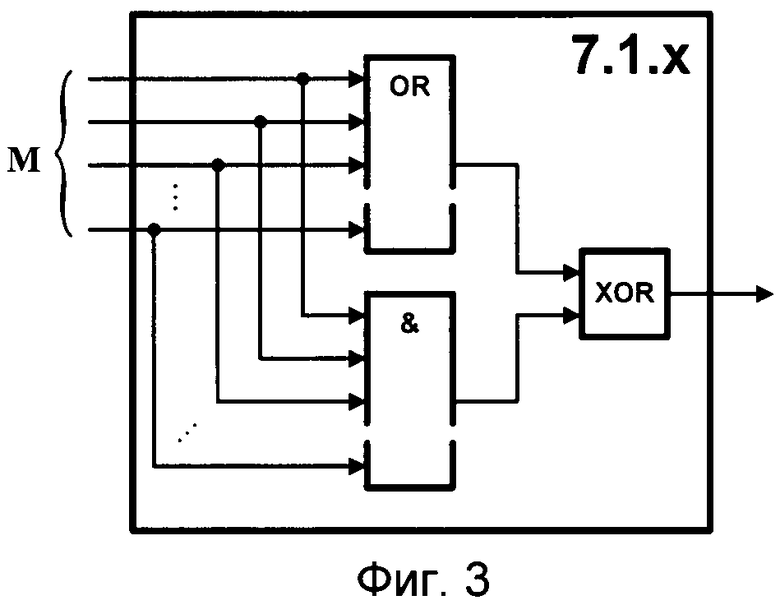

На Фиг.3 показана возможная техническая реализация блока комбинационной логики (7.1.х).

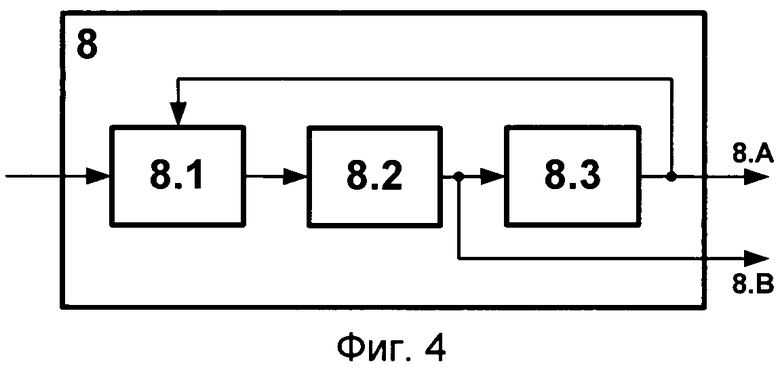

На Фиг.4 приведен вариант технической реализации блока оценки отношения сигнал-шум (8).

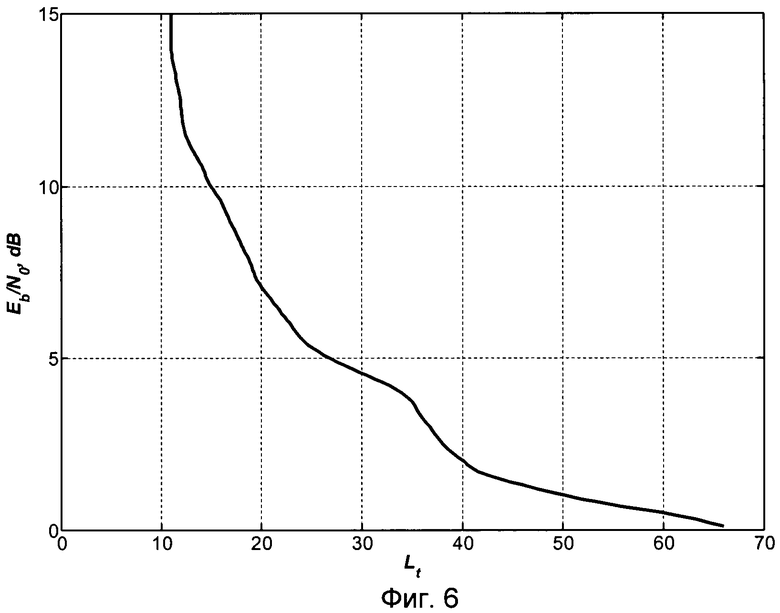

Фиг.5 поясняет логику использования данных из памяти путей для оценки глубины истории декодирования, на которой все пути декодирования сходятся, и порядок подключения входов блоков комбинационной логики (7.1.х) к ячейкам памяти путей (6).

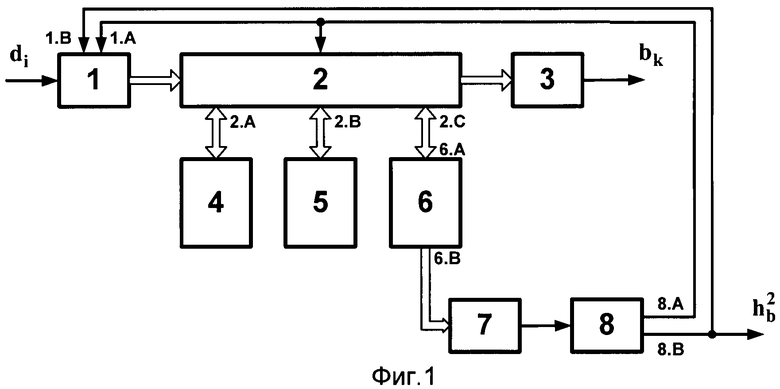

На Фиг.6 приведен график зависимости, связывающей битовое отношение сигнал-шум (Еb/N0) со средней текущей глубиной истории декодирования, на которой все пути декодирования сходятся, Lt.

Осуществление изобретения

Известные декодеры Витерби с каналом оценки текущего отношения сигнал-шум, шум могут быть реализованы (Фиг.1) в виде последовательно соединенных

- блока вычисления метрик переходов (1),

- блока расчета метрик и памяти путей (2),

- блока формирования информационного символа (3).

К блоку расчета метрик и памяти путей (2) подключены:

- память минимальных метрик путей (4),

- память метрик путей (5),

- память путей (6),

причем входом устройства является вход блока вычисления метрик переходов (1), а выходом - выход блока формирования информационного символа (3).

Заявляемое устройство содержит последовательно соединенные:

- блок оценки глубины истории декодирования, на которой все пути декодирования сходятся (7),

- блок оценки отношения сигнал-шум (8),

при этом вход блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, (7) соединен со вторым выходом (6.В) памяти путей (6), а первый выход (8.А) блока оценки отношения сигнал-шум (8) соединен с первым управляющим входом (1.А) блока вычисления метрик переходов (1) и управляющим входом блока расчета метрик и памяти путей (2), второй выход (8.В) блока оценки отношения сигнал-шум соединен со вторым управляющим входом (1.В) блока вычисления метрик переходов (1) и является выходом устройства, на который при его работе выдается сигнал, соответствующий оценке текущего отношения сигнал-шум  .

.

Вариантом реализации заявленного устройства является устройство, в котором блок оценки глубины истории декодирования, на которой все пути декодирования сходятся, (7) выполнен (Фиг.2) в виде:

- группы (7.1) блоков комбинационной логики (7.1.1-7.1.L), количество которых равно глубине декодирования, а количество входов каждого блока равно числу состояний сверточного кодера М, и

- приоритетного шифратора (7.2), количество входов которого равно количеству блоков комбинационной логики (7.1.1-7.1.L),

причем выход каждого блока комбинационной логики (7.1.х) соединен с соответствующим входом приоритетного шифратора (7.2), входом блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, (7) являются входы блоков комбинационной логики (7.1.х), а выходом - выход приоритетного шифратора (7.2).

Вариант реализации блока комбинационной логики (7.1.х) на основе типовых логических элементов приведен на Фиг.3.

Другим вариантом реализации заявленного устройства является устройство, в котором блок оценки отношения сигнал-шум (8) (Фиг.4) выполнен в виде последовательно соединенных:

- блока усреднения (8.1),

- блока нелинейного преобразования (8.2) и

- порогового устройства (8.3),

причем выход порогового устройства (8.3) соединен с управляющим входом блока усреднения (8.1) и является первым выходом (8.А) блока оценки отношения сигнал-шум (8), на который при его работе выдается бинарный сигнал, являющийся признаком аномальной работы декодера, а вторым его выходом (8.В) является выход блока нелинейного преобразования (8.2), на который при его работе выдается сигнал, соответствующий оценке текущего отношения сигнал-шум.

Заявленное устройство функционирует следующим образом (Фиг.1).

Набор отсчетов di, соответствующих принятому пакету канальных символов, поступает на вход блока вычисления метрик переходов (1), где на основе принятой реализации отсчетов производится расчет метрик переходов для всех возможных состояний на решетчатой диаграмме с учетом плотности распределения условных вероятностей, дисперсия которой определяется из оцененного значения отношения сигнал-шум на входе декодера, поступающего на вход 1.В.

Вычисленный набор метрик переходов поступает на вход блока расчета метрик и памяти путей (2), где происходит пересчет матрицы минимальных метрик путей, матрицы метрик переходов и матрицы памяти путей в соответствии с алгоритмом Витерби.

Результаты пересчета записываются в запоминающие устройства, представленные на Фиг.1 блоками: память минимальных метрик путей (4), память метрик путей (5), память путей (6).

Блок формирования информационного символа (3) на основе данных из блоков памяти путей (6) и памяти метрик путей (5) формирует решение bk о декодированном информационном символе, которое является информационным выходным сигналом декодера.

Кроме того, из блока памяти путей (6) на каждом шаге декодирования считываются данные о состоянии каждой ячейки матрицы путей, хранящейся в этом блоке, и передаются в блок оценки глубины истории декодирования, на которой все пути декодирования сходятся, (7), схема которого приведена на Фиг.2.

Блок оценки глубины истории декодирования, на которой все пути декодирования сходятся, (7) содержит группу блоков комбинационной логики (7.1) и приоритетный шифратор (7.2).

В блоке оценки глубины истории декодирования, на которой все пути декодирования сходятся, (7) бинарные данные, соответствующие содержанию ячеек каждого столбца матрицы путей, подаются на соответствующие входы блоков комбинационной логики (7.1.х), где х=1…L, a L - максимальная глубина истории декодирования (окно декодирования), которой соответствует количество столбцов в матрице путей.

Предполагается, что в матрице памяти путей в каждой ячейке хранится бинарный символ, соответствующий текущей оценке информационного символа, приводящего декодер в соответствующее состояние на решетчатой диаграмме.

Возможная реализация блоков комбинационной логики (7.1.х) на основе типовых логических устройств приведена на Фиг.3.

На вход каждого блока комбинационной логики поступают данные от соответствующего столбца матрицы памяти путей.

Количество входов каждого блока комбинационной логики совпадает с числом состояний на решетчатой диаграмме и равно M=2K-1, где K - длина кодового ограничения используемого кодового слова.

На выходе каждого блока комбинационной логики (7.1.х) формируется логический «0», если все бинарные символы в соответствующем столбце матрицы путей одинаковые, и логическая «1», если хотя бы один символ отличается от других.

Данная операция поясняется схемой, приведенной на Фиг.5.

Количество блоков комбинационной логики равно максимальной разрешенной глубине истории декодирования, (количеству столбцов матрицы памяти путей) L, при этом для определенности блок комбинационной логики 7.1.1 соответствует минимальной глубине истории декодирования 1, а блок комбинационной логики 7.1.L соответствует максимальной глубине истории декодирования L.

Как видно из данной фигуры, текущая глубина истории декодирования, на которой все пути декодирования сходятся, может быть определена путем определения максимального номера блока комбинационной логики (7.1.х) (крайнего левого), на выходе которого имеется логическая «1».

Эту операцию выполняет приоритетный шифратор (7.2), который выделяет логическую «1» в старшем разряде параллельного кода, сформированного выходами блоков комбинационной логики (7.1.х), и формирует бинарный код, соответствующий двоичному номеру данного разряда, который определяет текущую глубину истории декодирования, на которой все пути декодирования сходятся, Lt.

Приоритетный шифратор (7.2) может быть реализован, например, на основе интегральной микросхемы К555ИВ3 (зарубежный аналог 74147).

Сигнал с выхода приоритетного шифратора, являющийся выходным сигналом блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, поступает на вход блока оценки отношения сигнал-шум (8), который содержит последовательно соединенные блок усреднения (8.1), блок нелинейного преобразования (8.2) и пороговое устройство (8.3).

Причем выход порогового устройства (8.3) соединен с управляющим входом блока усреднения (8.1).

Схема реализации блока оценки отношения сигнал-шум (8) приведена на Фиг.4.

Блок усреднения (8.1) осуществляет усреднение на заданном интервале времени сформированной оценки глубины истории декодирования, на которой все пути декодирования сходятся.

Величина интервала усреднения обычно выбирается больше, чем максимальная глубина истории декодирования L.

Блок нелинейного преобразования (8.2) преобразует сигнал, сформированный на выходе блока усреднения (8.1), в сигнал, соответствующий текущему значению отношения сигнал-шум. Пример амплитудной характеристики блока нелинейного преобразования (8.2), полученной на основе моделирования на ЭВМ для сверточного кода со скоростью R=1/2 и кодовым ограничением К=7, приведен на Фиг.6.

Данная характеристика позволяет по измеренной глубине истории декодирования, на которой все пути декодирования сходятся, Lt определять соответствующее ей отношение сигнал-шум на входе декодера.

Эта зависимость может быть получена экспериментально или на основе моделирования для каждого типа декодера.

Пороговое устройство (8.3) формирует на своем выходе логический уровень «1», в случае, если значение оценки отношения сигнал-шум на его входе ниже заданного порога, если же значение отношения сигнал-шум выше порогового, то на выходе порогового устройства (8.3) будет сформирован логический уровень «0».

Таким образом, фиксируется факт критически большой глубины истории декодирования, на которой все пути декодирования сходятся, свидетельствующий либо о появлении ошибок, кратность которых превышает корректирующую способность кода, либо о неправильной синхронизации.

Сигнал с выхода порогового устройства (8.3) поступает на управляющий вход блока усреднения (8.1), где в случае логического уровня «1» на этом входе осуществляется сброс блока усреднения (8.1) и установка нулевого значения его выходного сигнала.

Одновременно сигнал с выхода порогового устройства (8.3) поступает на первый выход (8.А) блока оценки отношения сигнал-шум (8) и затем на первый управляющий вход (1.А) блока вычисления метрик переходов (1) и на управляющий вход блока расчета метрик и памяти путей (2).

Блок вычисления метрик переходов (1) по логическому уровню «1» на первом управляющем входе (1.А) для обеспечения синхронизации осуществляет пропуск одного отсчета во входном потоке.

Блок расчета метрик и памяти путей (2) по уровню «1» на своем управляющем входе производит инициализацию (установку в нулевое состояние) значений в памяти минимальных метрик путей (4), в памяти метрик путей (5) и в памяти путей декодирования (6).

После чего процедура декодирования начинается сначала.

Также возможно использование сигнала с первого выхода (8.А) блока оценки отношения сигнал-шум (8) внешними блоками, например, для фиксации того, что текущий и ряд последующих бит с выхода декодера некорректны.

Сигнал с выхода блока нелинейного преобразования (8.2) соответствует текущей оценке величины отношения сигнал-шум на входе декодера и подается на второй выход (8.В) блока оценки отношения сигнал-шум и затем на второй управляющий вход (1.В) блока вычисления метрик переходов (1).

При этом расчет метрик переходов осуществляется с учетом плотности распределения условных вероятностей, дисперсия которой определяется на основе оцененного значения отношения сигнал-шум на входе декодера.

Кроме того, оценка текущего отношения сигнал-шум может быть использована и другими внешними блоками приемного устройства для оптимизации процедуры приема.

Заявляемое решение позволяет формировать оценку текущего значения отношения сигнал-шум на входе декодера, что устраняет недостатки известных устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОЦЕНКИ ОТНОШЕНИЯ СИГНАЛ-ШУМ ПРИ ДЕКОДИРОВАНИИ СВЕРТОЧНЫХ КОДОВ | 2010 |

|

RU2446448C1 |

| МНОГОКАНАЛЬНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ДЕКОДЕР ВИТЕРБИ | 2010 |

|

RU2421900C1 |

| МНОГОСКОРОСТНОЙ ПОСЛЕДОВАТЕЛЬНЫЙ ДЕКОДЕР ВИТЕРБИ ДЛЯ ИСПОЛЬЗОВАНИЯ В СИСТЕМЕ МНОГОСТАНЦИОННОГО ДОСТУПА С КОДОВЫМ РАЗДЕЛЕНИЕМ | 1994 |

|

RU2222110C2 |

| АРХИТЕКТУРА ПАМЯТИ ДЛЯ ДЕКОДЕРА МАКСИМАЛЬНОЙ АПОСТЕРИОРНОЙ ВЕРОЯТНОСТИ | 1999 |

|

RU2236085C2 |

| АРХИТЕКТУРА ДЕКОДИРОВАНИЯ ПО ВИТЕРБИ ДЛЯ ИСПОЛЬЗОВАНИЯ В ПРОГРАММНО-УПРАВЛЯЕМЫХ РАДИОСИСТЕМАХ | 2006 |

|

RU2363098C1 |

| СПОСОБ УПРАВЛЕНИЯ УСТРОЙСТВАМИ ПРИЕМА И ПЕРЕДАЧИ ДАННЫХ В НАВИГАЦИОННОМ ПРИЕМНИКЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2476897C2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| СПОСОБ ИДЕНТИФИКАЦИИ СМЕННЫХ АНТЕННЫХ МОДУЛЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2439829C1 |

| КОМПОНЕНТНЫЙ ДЕКОДЕР И СПОСОБ ДЕКОДИРОВАНИЯ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2000 |

|

RU2247471C2 |

| ДЕКОДЕР СВЕРТОЧНЫХ КОДОВ ДЛЯ DVB-T ПРИЕМНИКА | 2008 |

|

RU2399157C2 |

Декодер Витерби с каналом оценки текущего отношения сигнал-шум, включающий в себя последовательно соединенные блок вычисления метрик переходов, блок расчета метрик и памяти путей, блок формирования информационного символа, а также подключенные к блоку расчета метрик и памяти путей: память минимальных метрик путей, память метрик путей и память путей, причем входом устройства является вход блока вычисления метрик переходов, а выходом - выход блока формирования информационного символа, причем содержит последовательно соединенные: блок оценки глубины истории декодирования, на которой все пути декодирования сходятся, блок оценки отношения сигнал-шум, при этом вход блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, соединен со вторым выходом памяти путей, а управляющий выход блока оценки отношения сигнал-шум соединен с управляющим входом синхронизации блока вычисления метрик переходов и управляющим входом блока расчета метрик и памяти путей, информационный выход блока оценки отношения сигнал-шум соединен со вторым управляющим входом блока вычисления метрик переходов и является выходом устройства, на который при его работе выдается сигнал, соответствующий оценке текущего отношения сигнал-шум. Технический результат - обеспечение формирования оценки текущего значения отношения сигнал-шум на входе декодера. 2 з.п. ф-лы, 6 ил.

1. Декодер Витерби с каналом оценки текущего отношения сигнал-шум, включающий в себя последовательно соединенные:

блок вычисления метрик переходов,

блок расчета метрик и памяти путей,

блок формирования информационного символа,

а также подключенные к блоку расчета метрик и памяти путей

память минимальных метрик путей,

память метрик путей и

память путей,

причем входом декодера является вход блока вычисления метрик переходов, а первым выходом - выход блока формирования информационного символа, отличающийся тем, что содержит последовательно соединенные:

блок оценки глубины истории декодирования, на которой все пути декодирования сходятся,

блок оценки отношения сигнал-шум, при этом вход блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, соединен со вторым выходом памяти путей, а управляющий выход блока оценки отношения сигнал-шум соединен с управляющим входом синхронизации блока вычисления метрик переходов и управляющим входом блока расчета метрик и памяти путей, информационный выход блока оценки отношения сигнал-шум соединен с соответствующим управляющим входом блока вычисления метрик переходов и является вторым выходом декодера, на который при его работе выдается сигнал, соответствующий оценке текущего отношения сигнал-шум.

2. Декодер по п.1, отличающийся тем, что блок оценки глубины истории декодирования, на которой все пути декодирования сходятся, выполнен в виде:

блоков комбинационной логики, количество которых равно глубине декодирования, а количество входов каждого блока равно числу состояний сверточного кодера, и

приоритетного шифратора, количество входов которого равно количеству блоков комбинационной логики,

при этом выход каждого блока комбинационной логики соединен с соответствующим входом приоритетного шифратора, входом блока оценки глубины истории декодирования, на которой все пути декодирования сходятся, являются входы блоков комбинационной логики, а выходом - выход приоритетного шифратора.

3. Декодер по п.1, отличающийся тем, что блок оценки отношения сигнал-шум выполнен в виде последовательно соединенных:

блока усреднения,

блока нелинейного преобразования и

порогового устройства,

причем выход порогового устройства соединен с управляющим входом блока усреднения и является первым выходом блока оценки отношения сигнал-шум, на который при его работе выдается бинарный сигнал, являющийся признаком аномальной работы декодера, а вторым его выходом является выход блока нелинейного преобразования, на который при его работе выдается сигнал, соответствующий оценке текущего отношения сигнал-шум.

| US 2009193321 A1, 2009.07.30 | |||

| US 4802174, 1989.01.31 | |||

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Декодер сверточного кода | 1988 |

|

SU1660178A1 |

Авторы

Даты

2011-11-20—Публикация

2010-06-09—Подача