Предпосылки изобретения

Чтобы увеличить производительность, многие коммуникационные системы применяют технологии упреждающего исправления ошибок. Это особенно верно для беспроводных коммуникационных систем, таких как сотовые сети. Одна из наиболее известных систем упреждающей коррекции ошибок известна как сверточное кодирование с декодированием по Витерби. Сверточное кодирование с декодированием по Витерби особенно полезно для каналов, в которых аддитивный белый гауссов шум искажает передаваемый сигнал.

Декодер Витерби - это наиболее подходящий последовательный декодер для сверточного кода. Декодеры Витерби были приняты к использованию на физическом уровне многих стандартов беспроводной связи, включая WCDMA, CDMA2000, IEEE-802.16e (т.е. WiBro) и другие. Эти стандарты работают на разных скоростях передачи данных и применяют сверточные кодеры в передатчиках и декодеры Витерби в приемниках, которые оптимизированы только под один-два конкретных стандарта. Также большинство обычных сверточных кодеров и декодеров Витерби работают на сравнительно малых скоростях передачи данных.

Устройство для программно-управляемой радиосвязи использует реконфигурируемое оборудование, которое может быть запрограммировано беспроводным способом с тем, чтобы работать в разных беспроводных стандартах. Например, передатчик для управляемой радиосвязи в беспроводном лэптопе или «карманном» компьютере может быть сконфигурирован с помощью различного программного обеспечения с тем, чтобы работать в IEEE-802.11x беспроводной сети, CDMA2000 беспроводной сети, OFDM/OFDMA беспроводной сети, GSM беспроводной сети или в другом типе сети. Многие из этих беспроводных сетей требуют использования декодеров Витерби.

Однако обычный декодер Витерби имеет существенные недостатки по отношению к устройствам программно-управляемой радиосвязи (SDR). Как отмечено выше, обычные декодеры Витерби оптимизированы для декодирования только по одному или двум специфическим (и сходным) стандартам. Если устройство программно-управляемой радиосвязи должно поддерживать большое количество стандартов, то в него должны быть внедрены более чем один декодер Витерби. Это ведет к усложненной конструкции приемопередатчика, который неэффективно занимает пространство чипа и потребляет избыточную величину энергии.

Кроме того, многие новые беспроводные стандарты работают с достаточно высокими скоростями передачи данных (например, WiBro, HDSPA и подобные). Декодер Витерби, оптимизированный по скорости и потреблению энергии для стандарта низкой скорости передачи данных, не подходит для оптимизации по скорости и потреблению энергии для стандарта высокой скорости передачи данных и наоборот. Таким образом, обычные декодеры Витерби не подходят для устройств программно-управляемой радиосвязи SDR.

Следовательно, существует необходимость в создании реконфигурируемого декодера Витерби для использования в системах программно-управляемой радиосвязи (SDR).

Сущность изобретения

В этом документе раскрывается устройство реконфигурируемого декодера Витерби. Описываемый декодер содержит реконфигурируемый канал данных, содержащий множество реконфигурируемых функциональных блоков, причем множество блоков включает с себя: 1) реконфигурируемый блок вычисления метрик ветвей и 2) реконфигурируемый блок сложения, сравнения, выбора и вычисления метрики маршрута, реконфигурируемый декодер Витерби далее содержит программируемый автомат конечных состояний (конечный автомат), предназначенный для управления реконфигурируемым маршрутом данных, при этом программируемый автомат конечных состояний обеспечивает выполнение множества контекстно-связанных инструкций, которые ассоциированы с реконфигурируемым декодером Витерби.

Также описывается система программно-управляемой радиосвязи (SDR), которая реализует реконфигурируемый декодер Витерби. Система SDR содержит: секцию радиочастотного (РЧ) приемопередатчика, выполненную с возможностью изменения конфигурации для работы в соответствии с множеством стандартов беспроводной связи; и реконфигурируемую секцию обработки базовой полосы, связанную с секцией РЧ-приемопередатчика, причем реконфигурируемая секция обработки базовой полосы включает в себя реконфигурируемый декодер Витерби.

Перед прочтением ДЕТАЛЬНОГО ОПИСАНИЯ ИЗОБРЕТЕНИЯ, приведенного ниже, может быть полезным привести определения некоторых слов и фраз, используемых в патентном документе: термины «включает» и «содержит», а также их производные обозначают включение без ограничений; термин «или» является включающим, обозначающим и/или; фразы «относящийся к» и «связанный с этим», а также их производные, могут обозначать "включать", "быть включенным", "соотносится с", "содержать", "содержаться в", "быть в связи с чем-либо", "соединяться с", "быть связанным", "взаимодействовать с", "чередоваться", "совмещать", "находиться вблизи", "связываться с", "иметь свойство" и т.п.; а термин «контроллер» обозначает любой прибор, систему или ее часть, управляющие, по меньшей мере, одной операцией, такой прибор может быть реализован в аппаратных средствах, встроенном программном обеспечении или программном обеспечении, или в любых комбинациях, по меньшей мере, двух указанных средств. Стоит отметить, что функциональные средства, относящиеся к каждому конкретному контроллеру, могут быть централизованными или распределенными, локальными или удаленными. Определения отдельных слов и фраз приводятся в тексте этого патентного документа; специалистам в данной области техники следует иметь в виду, что во многих, если не во всех, случаях, такие определения применяются к предыдущим, а также дальнейшим случаям использования определенных таким образом слов или фраз.

Краткое описание чертежей

Для более полного понимания настоящего раскрытия и его преимуществ, ссылки далее делаются на нижеследующее описание, рассматриваемое в связи с соответствующими чертежами, в которых одинаковыми ссылочными позициями обозначены сходные элементы:

Фиг.1 - высокоуровневая блок-схема устройства на основе реконфигурируемого процессора с набором команд для контекстно-связанных операций (CRISP), который может быть использован для применения в реконфигурируемом декодере Витерби;

Фиг.2 - высокоуровневая блок-схема реконфигурируемой системы;

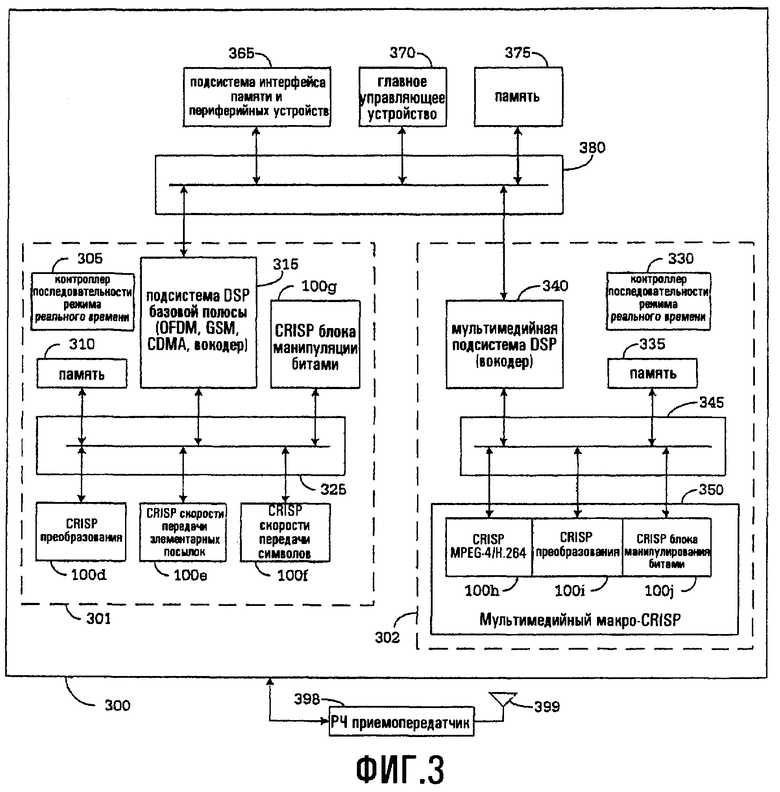

Фиг.3 - высокоуровневая блок-схема мультистандартной системы программно-управляемой радиосвязи, которая реализует реконфигурируемый декодер Витерби с использованием, по меньшей мере, одного устройства на основе реконфигурируемого процессора с набором команд для контекстно-связанных операций (CRISP);

Фиг.4 - блок-схема реконфигурируемого декодера Витерби, реализованного в процессоре CRISP, согласно принципам раскрытия;

Фиг.5 - временная диаграмма выбранных стадий конвейерной обработки в сверточном кодере;

Фиг.6 - временная диаграмма выбранных стадий конвейерной обработки в блоке вычисления метрик ветвей;

Фиг.7 - временная диаграмма выбранных стадий конвейерной обработки в блоке вычисления метрик каналов; и

Фиг.8 - временная диаграмма выбранных стадий конвейерной обработки в блоке вычисления решетки и трассировки.

Детальное описание изобретения

Фиг.1-8, рассмотренные ниже, и различные варианты осуществления, использованные для описания принципов настоящего раскрытия в этом патентном документе, приведены только для иллюстрации и не должны быть использованы никоим образом, чтобы ограничить область раскрытия. Специалистам в данной области техники должно быть понятно, что принципы настоящего изобретения могут быть использованы в любой подходящей системе обработки данных.

Раскрытый реконфигурируемый декодер Витерби позволяет в высокой степени использовать параллелизм для того, чтобы поддерживать стандарты высокой скорости передачи данных. Целевая скорость передачи данных прямой линии связи в WiBro составляет 12 Мбит/с, а максимальная скорость передачи данных в HSDPA составляет до 14,4 Мбит/с. Архитектура раскрытого реконфигурируемого декодера Витерби использует параллелизм, чтобы достичь необходимой пропускной способности при высоких скоростях передачи данных. Это достигается путем использования параллельных исполняющих элементов, а также методов конвейерной обработки, чтобы достичь высоких скоростей передачи данных.

Реконфигурируемый декодер Витерби поддерживает многорежимные операции по декодированию в разных коммуникационных стандартах, включая, в том числе, WCDMA, HSDPA, CDMA2000, IEEE-802.16e (т.е. WiBro) и GSM/EDGE. Раскрытый декодер Витерби также обеспечивает адаптивность, чтобы поддерживать разные скорости передачи данных. WiBro и WCDMA/HSDPA работают на многих различных скоростях передачи данных. Архитектура раскрытого декодера Витерби оптимизирована не только для максимальных скоростей передачи данных, но и для различных диапазонов скоростей передачи данных.

Реконфигурируемый декодер Витерби также минимизирует потребление энергии для различных стандартов и скоростей передачи данных, таким образом, декодер Витерби может применяться в переносных устройствах. Также реконфигурируемый декодер Витерби согласно принципам настоящего раскрытия дает возможности гибкого использования конечному пользователю. Хотя разработка ориентирована на декодирование по Витерби, архитектура не имеет жестких ограничений по параметрам. Таким образом, разработка обеспечивает обобщенную платформу декодера Витерби, которая позволяет конечному пользователю выбирать параметры и алгоритмы, основываясь на требованиях конечного пользователя.

Реконфигурируемый декодер Витерби, описанный здесь, реализован с использованием устройства на основе процессора CRISP. CRISP-приборы подробно описаны в патентной заявке США №11/123,313, которая включена в настоящий документ посредством вышеозначенной ссылки.

Фиг.1 - это высокоуровневая блок-схема процессора CRISP 100, который может использоваться для реализации декодера Витерби. CRISP 100 включает в себя память 110, программируемую схему 120 маршрута данных, программируемый конечный автомат 130 и опциональную память 140 программ. Контекст - это группа команд процессора данных, которые относятся к конкретной функции или приложению, таким как команды декодирования по Витерби. Как описано в патентной заявке США №11/123,313, CRISP 100 реализует только подмножество контекстно-связанных команд оптимальным образом.

Процессор CRISP 100 определяет основной блок аппаратных средств, обычно состоящий из более высокоуровневых блоков аппаратных средств. Принципиальное преимущество CRISP 100 состоит в том, что CRISP 100 разбивает требуемое приложение на две основные области: область управления и область канала данных и оптимизирует каждую область отдельно. Путем проведения декодирования по Витерби в CRISP 100 рассматриваемый декодер Витерби уменьшает проблемы, связанные с гибкостью и потреблением энергии, которые оказывают влияние на обычные декодеры Витерби.

Область управления поддерживается программируемым конечным автоматом 130, который может содержать цифровой процессор сигналов, контроллер или другое обычное устройство обработки. Программируемый конечный автомат 130 конфигурируется битами реконфигурирования, получаемыми из внешнего контроллера (не показан). Программируемый конечный автомат 130 может исполнять программу, сохраненную в ассоциированной опциональной памяти 140 программ. Программа может сохраняться в памяти 140 программ посредством линии данных от внешнего контроллера. Память 110 используется для хранения данных приложений, используемых в схеме 120 маршрута данных.

Программируемая схема 120 маршрута данных разделена на наборы блоков, выполняющих конкретные функции (например регистры, мультиплексоры, устройства умножения и подобные). Каждый из блоков является реконфигурируемым и программируемым, чтобы достичь максимальной гибкости. Разделение программируемой схемы 120 маршрута данных на функциональные блоки зависит от уровня реконфигурируемости и программируемости, необходимого для конкретного приложения. В контексте декодера Витерби эти функциональные блоки могут включать в себя блок вычисления метрик ветвей, блок сложения, сравнения, выбора и вычисления метрики маршрута, блок решетки и трассировки, буферы, оперативную память и другие блоки, как описано ниже в деталях.

Поскольку разные контексты реализованы отдельными устройствами CRISP, которые работают независимо от других устройств CRISP, реализация детектора Витерби с использованием одного или более устройств CRISP обеспечивает эффективную схему управления потреблением энергии, которая способна выключить устройство CRISP, если это устройство CRISP не требуется. Это обеспечивает активность только тех устройств CRISP, которые требуются в данный период, тогда как другие неиспользуемые устройства CRISP не потребляют значительной энергии.

Фиг.2 представляет собой высокоуровневую блок-схему реконфигурируемой системы 200 обработки согласно варианту осуществления данного раскрытия. Реконфигурируемая система 200 обработки содержит N процессоров CRISP, включающих в себя типичные CRISP 100a, 100b и 100c, которые произвольно обозначены как CRISP 1, CRISP 2 и CRISP N. Реконфигурируемая система 200 обработки далее содержит контроллер 210 последовательности режима реального времени, память 220 программ последовательности, программируемый коммутатор 230 межсоединений и буферы 240 и 245.

Биты реконфигурирования могут быть загружены в CRISP 100a, 100b и 100c через ЛИНИЮ УПРАВЛЕНИЯ посредством контроллера 210 последовательности режима реального времени и буфера 240. Программа управления может быть также загружена в память 220 программ последовательности через ЛИНИЮ УПРАВЛЕНИЯ посредством буфера 240. Контроллер 210 последовательности режима реального времени упорядочивает контексты, предназначенные к выполнению каждым из CRISP 100а-с, путем извлечения программных команд из памяти 220 программ и посылки битов реконфигурирования на CRISP 100а-с. В типовом исполнении контроллер 210 последовательности режима реального времени может содержать процессор стека, который применим в качестве диспетчера режима реального времени благодаря низкому времени ожидания и простоте.

Реконфигурируемый коммутатор 230 межсоединений обеспечивает связность между каждым из CRISP 100а-с и внешней ШИНОЙ ДАННЫХ посредством двунаправленного буфера 245. В типовом исполнении настоящего изобретения каждый из CRISP 100а-с может выступать в качестве ведущего по отношению к реконфигурируемому коммутатору 230 межсоединений и может инициировать процесс адресного доступа. Арбитр шины для реконфигурируемого коммутатора 230 межсоединений может быть внутренним по отношению к контроллеру 210 последовательности режима реального времени.

В типовом исполнении реконфигурируемая система 200 обработки может быть, например, мобильным телефоном или аналогичным беспроводным устройством или процессором данных, предназначенным для использования в ноутбуке. В варианте беспроводного устройства, основанном на архитектуре программно-управляемой радиосвязи (SDR), каждый из CRISP 100а-с отвечает за исполнение поднабора контекстно-связанных команд, которые ассоциированы с конкретной реконфигурируемой функцией. Например, CRISP 100а может быть конфигурирован для исполнения контекстно-связанных команд, которые обрабатывают сигналы полосы частот модулирующих сигналов (базовой полосы) CDMA или сигнала базовой полосы OFDMA. CRISP 100b может быть конфигурирован для исполнения контекстно-связанных команд, которые действуют как контроллер памяти. CRISP 100с может быть сконфигурирован для исполнения контекстно-связанных команд, которые выполняют турбодекодирование или декодирование по Витерби.

Так как устройства CRISP в значительной степени независимы и могут работать одновременно, декодер Витерби, реализованный с использованием одного или более CRISP, имеет преимущество параллелизма без вытекающих последствий потерь энергии, характерных для параллельных операций. Нежесткая связь и независимость устройств CRISP позволяет конфигурировать их для различных систем и функций, которые могут быть выключены раздельно.

Фиг.3 представляет собой высокоуровневую блок-схему мультистандартной системы 300 SDR, которая реализует реконфигурируемый декодер Витерби с использованием устройства CRISP. Система 300 SDR может содержать беспроводной терминал (либо мобильную станцию, абонентскую станцию и т.п.), который имеет доступ к беспроводной сети, как, например, сотовые телефоны стандарта GSM или CDMA, PDA устройства c характеристиками WCDMA, IEEE-802.11x, HSDPA, OFDM/OFDMA или подобные им.

Мультистандартная система 300 SDR содержит подсистему 301 базовой полосы, подсистему 302 приложений, подсистему 365 интерфейса памяти и периферийных устройств, главный управляющий модуль 370, память 375 и соединитель 380. Главный управляющий модуль 370 может включать в себя, например, обычный микроконтроллер или микропроцессор (например, x68, ARM, RISC, DSP, и т.д.). Подсистема 365 интерфейса памяти и периферийных устройств может соединять систему 300 SDR с внешней памятью (не изображена) и внешними периферийными устройствами (не изображены). Память 375 хранит данные от других компонентов в системе 300 SDR и внешних устройств (не изображены). Например, память 375 может хранить поток входящих выборок данных, связанных с сигналом, преобразованным с понижением частоты, генерируемым радиочастотным приемопередатчиком 398 и антенной 399, которые связаны с системой 300 SDR. Соединитель 380 выступает как системная шина, которая обеспечивает обмен данными между подсистемами 301 и 302, подсистемой 365 интерфейса памяти и периферийных устройств, главным управляющим модулем 370 и памятью 375.

Подсистема 301 базовой полосы содержит контроллер 305 последовательности режима реального времени, память 310, подсистему 315 базовой полосы DSP, соединитель 325 и множество специализированных процессоров с набором команд для контекстно-связанных операций, включающих CRISP 100d преобразования, CRISP 100e скорости передачи элементарных посылок, CRISP 100f скорости передачи символов и CRISP 100g блока манипулирования битами. Например, CRISP 100d преобразования может реализовать функцию быстрого преобразования Фурье, процессор 100e скорости передачи элементарных посылок может реализовать функцию корреляции для CDMA сигнала, CRISP 100f скорости передачи символов может реализовать функцию турбодекодирования или функцию декодирования по Витерби.

В приведенном для примера варианте осуществления CRISP 100d преобразования может получить выборки сигнала промежуточной частоты, сохраненные в памяти 375, и выполнить быстрое преобразование Фурье, которое формирует последовательность выборок элементарных посылок со скоростью передачи базовой полосы. Затем CRISP 100е скорости передачи элементарных посылок получает выборки элементарных посылок от CRISP 100d преобразования и реализует функцию корреляции, которая формирует последовательность символов данных. Далее, CRISP 100f скорости передачи символов получает символы данных от CRISP 100е скорости передачи элементарных посылок и выполняет турбодекодирование и декодирование по Витерби, чтобы восстановить пользовательские данные базовой полосы. Пользовательские данные базовой полосы могут быть потом использованы в подсистеме 302 приложений.

В приведенном для примера варианте осуществления настоящего изобретения CRISP 100f скорости передачи символов может состоять из двух и более процессоров, работающих параллельно. Также, например, CRISP 100g блока манипулирования битами может реализовать такие функции, как кодирование переменной длины, контроль циклическим избыточным кодом, сверточное кодирование и подобные. Соединитель 325 действует как системная шина, обеспечивающая передачу данных между контроллером 305 последовательности режима реального времени, памятью 310, подсистемой 315 цифрового процессора сигналов базовой полосы и CRISP 100d-100g.

Подсистема 302 приложений включает в себя контроллер 330 последовательности режима реального времени, память 335, мультимедийную подсистему 340 цифрового процессора сигналов, соединитель 345 и мультимедийный макроCRISP 350. Мультимедийный макроCRISP 350 включает в себя множество специализированных процессоров наборов команд для контекстно-ориентированных операций, включая CRISP 550h MPEG-4/H.264, CRISP 550i преобразования и CRISP 100j блока манипулирования битами. В приведенном для примера варианте осуществления изобретения CRISP 550h MPEG-4/H.264 выполняет функции оценки движения, а CRISP 100h преобразования выполняет функцию дискретного косинусного преобразования. Соединитель 380 обеспечивает перенос данных между контроллером 330 последовательности режима реального времени, памятью 335, мультимедийной подсистемой 340 цифрового процессора сигналов и мультимедийным макроCRISP 350.

В варианте осуществления по фиг.3 использование устройств CRISP позволяет изменять конфигурацию подсистемы 302 приложений мультистандартной системы 300 SDR, чтобы поддерживать множество видеостандартов с разными профилями и размерами. В дополнение, использование устройств CRISP позволяет изменять конфигурацию подсистемы 301 базовой полосы мультистандартной системы 300 SDR для того, чтобы поддерживать множество стандартов радиоинтерфейса. Таким образом, система 300 SDR может работать в разных типах беспроводных сетей (например, CDMA, GSM, 802.11x и т.д.) и может использовать разные типы аудио- и видеоформатов. Однако использование CRISP согласно принципам настоящего раскрытия позволяет системе 300 SDR выполнять эти функции с гораздо меньшим потреблением энергии, чем у других обычных беспроводных приборов со схожими характеристиками.

Фиг.4 представляет блок-схему реконфигурируемого декодера Витерби, реализованного в CRISP 100f согласно принципам настоящего раскрытия. Реконфигурируемый декодер Витерби включает в себя блок 405 вычисления метрик ветвей, блок 410 сложения, сравнения, выбора и вычисления метрики маршрута, блок 415 вычисления решетки и трассировки, буфер 420 памяти текущего этапа, буфер 425 памяти следующего этапа, блок 430 логики управления и регистров, блок 435 генерации адресов. Реконфигурируемый декодер Витерби связан с памятью 350, которая может являться устройством, отдельным от CRISP 100f, как показано на фиг.4, или же может быть интегрирована в CRISP 100f. Память 360 логически поделена на совместно используемый буфер 360 входных символов и совместно используемый буфер 370 архива решетки. В приведенном для примера варианте осуществления память 350 может содержать 32 килобайта оперативной памяти.

Блок 430 логики управления и регистров включает в себя программируемый конечный автомат и связанные управляющие регистры, которые контролируют всю работу CRISP 100f и реконфигурируют функциональные блоки маршрута данных, включая, например, блок 405 вычисления метрик ветвей, блок 410 сложения, сравнения, выбора и вычисления метрики маршрута, блок 415 вычисления решетки и трассировки, буфер 420 текущего этапа и буфер 425 следующего этапа.

Блок 435 генерации адресов контролирует операции чтения и записи в память 350, которые выполняются блоком 405 вычисления метрик ветвей и блоком 415 вычисления решетки и трассировки. CRISP 100e скорости передачи элементарных посылок или другой компонент в подсистеме 301 базовой полосы записывает выборки символьных данных в совместно используемый буфер 360 входных символов. Блок 405 вычисления метрик ветвей в дальнейшем считывает выборки символьных данных из совместно используемого буфера 360 входных символов. Блок 415 вычисления решетки и трассировки записывает фиксированные декодированные данные решетки в совместно используемый буфер 370 архива решетки и считывает сохраненные фиксированные данные решетки в более поздних циклах.

Хорошо известно, что алгоритм Витерби часто представляется как диаграмма решетки. Решетка - это индексированная по времени версия диаграммы состояний. В каждый момент времени в решетке могут содержаться два состояния, четыре состояния, шесть состояний, восемь состояний или более. Обнаружение методом максимума правдоподобия цифрового потока с межсимвольными помехами может быть описано как нахождение наиболее вероятного маршрута через решетку переходов состояний (ветвей). Каждое состояние соответствует возможному образцу недавно полученных битов данных, а каждая ветвь решетки соответствует приему следующего (зашумленного) входного сигнала. Метрики ветвей показывают затраты на прохождение по конкретным ветвям. Метрики маршрутов (или состояний) суммируют минимальные затраты для достижения конкретного состояния. Метрики маршрутов обновляются путем применения рекурсии сложения-сравнения и выбора. В каждый конкретный момент метрики ветвей добавляются к метрикам маршрутов (состояний) предыдущего момента времени. Затем выбирается наименьшая метрика маршрута в качестве новой метрики маршрута для каждого состояния. В конечном итоге, после того как все выборки входных символов обработаны, минимальное значение маршрута представляет оставшуюся выбранную последовательность. Трассировка назад по решетке дает наиболее вероятную последовательность переданных данных.

Блок 405 вычисления метрик ветвей представляет собой реконфигурируемое устройство, которое реконфигурируется посредством управляющих параметров и данных, записанных в блок 430 логики управления и регистров. Блок 405 вычисления метрик ветвей рассчитывает 4 возможных значения метрик ветвей путем расчета расстояний (меры различия) входных символов от целевых значений согласно общеизвестным принципам. Например, блок 405 вычисления метрик ветвей может считывать в 8-битных «мягких» выборках символов (например, двоичное дополнение 256-го уровня) из совместно используемого буфера 360 входных символов и может выводить четыре (4) значения метрик ветвей, каждая из которых содержит 16 бит. Значения метрик ветвей обычно являются расстояниями Хемминга (или другими значениями метрики), которые вычисляются в каждый момент времени для маршрутов между состояниями в предыдущий момент времени и состояниями в текущий момент времени.

Блок 410 сложения, сравнения, выбора и вычисления метрики маршрута является также реконфигурируемым устройством, которое реконфигурируется с помощью управляющих параметров и данных, записанных в блок 430 логики управления и регистров. Блок 410 вычисляет новое значение метрики маршрута (или состояний) на каждом этапе (то есть в момент времени) для решетки. Минимальная метрика маршрута потом выводится как Решение Этапа на блок 415 вычисления решетки и трассировки. Блок 410 сложения, сравнения, выбора и вычисления метрики маршрута считывает текущие метрики маршрутов (например, 4 метрики маршрутов) из буфера 420 памяти текущего этапа и добавляет текущие метрики маршрутов к метрикам ветвей из блока 405 вычисления метрик ветвей и сохраняет новые метрики маршрутов в буфере 425 памяти нового этапа. Буфер 425 памяти нового этапа и буфер 420 памяти текущего этапа меняют значения таким образом, что буфер 425 памяти следующего этапа становится буфером 420 памяти текущего этапа, а буфер 420 памяти текущего этапа становится буфером 425 памяти следующего этапа.

Блок 415 вычисления решетки и трассировки получает значение решения этапа из блока 410 сложения, сравнения, выбора и вычисления метрики маршрута и сохраняет жесткие декодированные значения в совместно используемом буфере архива решетки. Когда весь блок выборок символов обработан и решетка завершена в совместно используемом буфере архива решетки, блок 415 вычисления решетки и трассировки выполняет трассировку по кратчайшему пути в решетке, чтобы декодировать входную последовательность.

В предпочтительном варианте осуществления реконфигурируемый декодер Витерби в CRISP 100f обеспечивает полностью программируемые сессии декодирования канала по прямой связи и трассировки, которые поддерживают: i) декодирование канала с длинами кодовых ограничений, например, K=5, K=6, K=7 и K=9; ii) коды перфорирования и iii) скорости кодирования =1/2, 1/4, 1/6 для четырех полностью программируемых полиномов. Совместно используемый буфер 370 архива решетки может поддерживать до 512 этапов для K=9 или 8192 этапов для К=5. Реконфигурируемый декодер Витерби в CRISP 100f также поддерживает блочную длину символьных данных в памяти 350, которая полностью программируема и также поддерживает программируемые методы трассировки.

Внешний контролер, такой как подсистема 315 базовой полосы DSP или главный управляющий модуль 370, программирует реконфигурируемый декодер Витерби в CRISP 100f, пока он находится во включенном состоянии. Реконфигурируемый декодер Витерби в CRISP 100f может в дальнейшем независимо работать над целым блоком данных в памяти 350, основываясь на программируемых регистрах и специальных командах в блоке 430. Данные записываются и считываются из памяти 350 в CRISP 100f через шину в соединителе 325. Адреса совместно используемых буферов 360 входных символов и совместно используемого буфера 370 архива решетки являются полностью программируемыми.

Фиг.5-8 иллюстрируют архитектуру конвейерной обработки выбранных компонентов в CRISP 100f и сверточном кодере и передающем устройстве. Фиг.5 представляет собой временную диаграмму выбранных стадий конвейерной обработки в сверточном кодере, который кодирует данные, которые декодирует декодер Витерби. Сверточный кодер содержит каскад загрузки кодера, каскад перемещения кодера, каскад сохранения кодера. Показаны последовательные периоды времени T0, T1 и T2. Сверточный кодер получает пять последовательных блоков данных в следующем порядке (слева направо): (…, N-2, N-1, N, N+1, N+2). Во время T0 каскад загрузки кодера обрабатывает блок Данных N, каскад перемещения кодера обрабатывает блок Данных N-1 и каскад сохранения кодера обрабатывает блок Данных N-2. Во время Т1 каскад загрузки кодера обрабатывает блок Данных N+1, каскад перемещения кодера обрабатывает блок Данных N и каскад сохранения кодера обрабатывает блок Данных N-1. Во время Т2 каскад загрузки кодера обрабатывает блок Данных N+2, этап перемещения кодера обрабатывает блок Данных N+1 и каскад сохранения кодера обрабатывает блок Данных N.

Фиг.6 представляет временную диаграмму выбранных стадий конвейерной обработки в блоке 405 вычисления метрик ветвей. Блок 405 вычисления метрик ветвей содержит каскад загрузки метрик ветвей, каскад вычисления метрик ветвей и каскад сохранения метрик ветвей. Блок 405 вычисления метрик ветвей получает пять последовательных блоков данных в следующем порядке (слева направо): (…, N-2, N-1, N, N+1, N+2). Во время T0 каскад загрузки метрик ветвей обрабатывает блок Данных N, каскад вычисления метрик ветвей обрабатывает блок Данных N-1 и каскад сохранения метрик ветвей обрабатывает блок Данных N-2. Во время Т1 каскад загрузки метрик ветвей обрабатывает блок Данных N+1, каскад вычисления метрик ветвей обрабатывает блок Данных N и каскад сохранения метрик ветвей обрабатывает блок Данных N-1. Во время Т2 каскад загрузки метрик ветвей обрабатывает блок Данных N+2, каскад вычисления метрик ветвей обрабатывает блок Данных N+1 и каскад сохранения метрик ветвей обрабатывает блок Данных N.

Фиг.7 представляет временную диаграмму выбранных стадий конвейерной обработки в блоке вычисления метрики маршрута. Блок вычисления метрики маршрута содержит каскад предзагрузки метрики маршрута, каскад загрузки метрики маршрута, каскад сложения, сравнения, выбора и вычисления метрики маршрута, каскад сохранения метрики маршрута. Блок вычисления метрики маршрута получает шесть последовательных блоков данных в следующем порядке (слева направо): (…, N-2, N-1, N, N+1, N+2, N+3). Во время T0 каскад предзагрузки метрики маршрута обрабатывает блок Данных N+1, каскад загрузки метрики маршрута обрабатывает блок Данных N, каскад сложения, сравнения, выбора и вычисления метрики маршрута обрабатывает блок Данных N-1 и каскад сохранения метрики маршрута обрабатывает блок Данных N-2. Во время Т1 каскад предзагрузки метрики маршрута обрабатывает блок Данных N+2, каскад загрузки метрики маршрута обрабатывает блок Данных N+1, каскад сложения, сравнения, выбора и вычисления метрики маршрута обрабатывает блок Данных N и каскад сохранения метрики маршрута обрабатывает блок Данных N-1. Во время Т2 каскад предзагрузки метрики маршрута обрабатывает блок Данных N+3, каскад загрузки метрики маршрута обрабатывает блок Данных N+2, каскад сложения, сравнения, выбора и вычисления метрики маршрута обрабатывает блок Данных N+1 и каскад сохранения метрики маршрута обрабатывает блок Данных N.

Фиг.8 представляет временную диаграмму стадий конвейерной обработки в блоке 415 вычисления решетки и трассировки. Блок 415 вычисления решетки и трассировки содержит каскад сохранения решетки, каскад загрузки трассировки, каскад сдвига трассировки. Блок 415 вычисления решетки и трассировки получает пять последовательных блоков данных в следующем порядке (слева направо): (…, N-2, N-1, N, N+1, N+2). Во время T0 каскад сохранения решетки обрабатывает блок Данных N, каскад загрузки трассировки обрабатывает блок Данных N-1 и каскад сдвига трассировки обрабатывает блок Данных N-2. Во время Т1 каскад сохранения решетки обрабатывает блок Данных N+1, каскад загрузки трассировки обрабатывает блок Данных N, каскад сдвига трассировки обрабатывает блок Данных N-1. Во время Т2 каскад сохранения решетки обрабатывает блок Данных N+2, каскад загрузки трассировки обрабатывает блок Данных N+1 и каскад сдвига трассировки обрабатывает блок Данных N.

Хотя настоящее раскрытие было описано со ссылкой на пример варианта осуществления, различные изменения и модификация могут быть предложены специалистам в данной области техники. Предполагается, что настоящее изобретение включает в себя подобные изменения и модификации, как входящие в объем прилагаемой формулы изобретения.

Изобретение относится к радиосвязи и предназначено для упреждающей коррекции ошибок. Технический результат - повышение помехозащищенности в системах программно-управляемой радиосвязи. Декодер Витерби содержит реконфигурируемый маршрут данных и программируемый конечный автомат, который управляет реконфигурируемым маршрутом данных. Реконфигурируемый маршрут данных образован из множества реконфигурируемых функциональных блоков, включающих в себя реконфигурируемый блок вычисления метрик ветвей; и реконфигурируемый блок сложения, сравнения, выбора и вычисления метрики маршрута. Конечный автомат выполняет множество контекстно-связанных команд, ассоциированных с реконфигурируемым декодером Витерби. 2 н. и 18 з.п. ф-лы, 8 ил.

1. Реконфигурируемый декодер Витерби, содержащий реконфигурируемый маршрут данных, образованный из множества реконфигурируемых функциональных блоков, включающих в себя

i) реконфигурируемый блок вычисления метрик ветвей; и

ii) реконфигурируемый блок сложения, сравнения, выбора и вычисления метрики маршрута; и

программируемый конечный автомат, выполненный с возможностью управления реконфигурируемым маршрутом данных, причем конечный автомат обеспечивает выполнение множества контекстно-связанных команд, относящихся к реконфигурируемому декодеру Витерби.

2. Реконфигурируемый декодер Витерби по п.1, в котором реконфигурируемый маршрут данных конфигурируется битами реконфигурирования, получаемыми из внешнего устройства.

3. Реконфигурируемый декодер Витерби по п.2, в котором программируемый конечный автомат конфигурируется битами реконфигурирования, получаемыми из внешнего устройства.

4. Реконфигурируемый декодер Витерби по п.2, в котором декодер Витерби может быть переведен в режим малого потребления энергии внешним контроллером в период времени, когда реконфигурируемый декодер Витерби не требуется для декодирования входных данных.

5. Реконфигурируемый декодер Витерби по п.1, в котором реконфигурируемый блок вычисления метрик ветвей содержит множество каскадов конвейерной обработки, предназначенных для вычисления значений метрик ветвей на основе выборок входных символов.

6. Реконфигурируемый декодер Витерби по п.5, в котором реконфигурируемый блок сложения, сравнения, выбора и вычисления метрики маршрута содержит множество каскадов конвейерной обработки, предназначенных для вычисления значений метрики маршрута из значений метрик ветвей, полученных из реконфигурируемого блока вычисления метрики маршрута.

7. Реконфигурируемый декодер Витерби по п.6, в котором множество реконфигурируемых функциональных блоков дополнительно содержит реконфигурируемый блок вычисления решетки и трассировки.

8. Реконфигурируемый декодер Витерби по п.7, в котором реконфигурируемый блок вычисления решетки и трассировки содержит множество каскадов конвейерной обработки, предназначенных для генерации информации решетки состояний из значений метрики маршрута, получаемых из реконфигурируемого блока сложения, сравнения, выбора и вычисления метрики маршрута.

9. Реконфигурируемый декодер Витерби по п.8, в котором реконфигурируемый блок вычисления решетки и трассировки конфигурируется с помощью битов реконфигурирования, получаемых из внешнего устройства.

10. Реконфигурируемый декодер Витерби по п.9, в котором реконфигурируемый блок вычисления решетки и трассировки выводит один жестко декодированный бит во внешнюю шину для каждого каскада решетки.

11. Система программно-управляемой радиосвязи, содержащая

секцию радиочастотного (РЧ) приемопередатчика, выполненную с возможностью реконфигурации для работы в множестве различных стандартов беспроводной связи; и реконфигурируемую секцию обработки базовой полосы, связанную с секцией РЧ приемопередатчика, причем реконфигурируемая секция обработки базовой полосы содержит реконфигурируемый декодер Витерби, содержащий

реконфигурируемый маршрут данных, образованный из множества реконфигурируемых функциональных блоков, причем множество реконфигурируемых функциональных блоков включает в себя

i) реконфигурируемый блок вычисления метрик ветвей; и

ii) реконфигурируемый блок сложения, сравнения, выбора и вычисления метрики маршрута; и

программируемый конечный автомат, выполненный с возможностью управления реконфигурируемым маршрутом данных, причем программируемый конечный автомат обеспечивает выполнение множества контекстно-связанных команд, ассоциированных с реконфигурируемым декодером Витерби.

12. Система программно-управляемой радиосвязи по п.11, в которой реконфигурируемый маршрут данных конфигурируется битами реконфигурирования, получаемыми из внешнего устройства.

13. Система программно-управляемой радиосвязи по п.12, в которой программируемый конечный автомат конфигурируется битами реконфигурирования, получаемыми из внешнего устройства.

14. Система программно-управляемой радиосвязи по п.12, в которой реконфигурируемый декодер Витерби может быть переведен в режим малого потребления энергии внешним контроллером в период времени, когда реконфигурируемый декодер Витерби не требуется для декодирования входных данных.

15. Система программно-управляемой радиосвязи по п.11, в которой реконфигурируемый блок вычисления метрик ветвей содержит множество каскадов конвейерной обработки, предназначенных для вычисления значений метрик ветвей на основе выборок входных символов.

16. Система программно-управляемой радиосвязи по п.15, в которой реконфигурируемый блок сложения, сравнения, выбора и вычисления метрики маршрута содержит множество каскадов конвейерной обработки, предназначенных для вычисления значений метрики маршрута на основе значений метрик ветвей, получаемых из реконфигурируемого блока вычисления метрик ветвей.

17. Система программно-управляемой радиосвязи по п.16, в которой множество реконфигурируемых функциональных блоков включает в себя реконфигурируемый блок вычисления решетки и трассировки.

18. Система программно-управляемой радиосвязи по п.17, в которой реконфигурируемый блок вычисления решетки и трассировки содержит множество каскадов конвейерной обработки, предназначенных для генерации информации решетки состояний из значений метрики маршрута, полученной из реконфигурируемого блока сложения, сравнения, выбора и вычисления метрики маршрута.

19. Система программно-управляемой радиосвязи по п.18, в которой реконфигурируемый блок вычисления решетки и трассировки конфигурируется битами реконфигурирования, получаемыми из внешнего устройства.

20. Система программно-управляемой радиосвязи по п.19, в которой реконфигурируемый блок вычисления решетки и трассировки вводит один жестко декодированный бит во внешнюю шину для каждого каскада решетки.

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| ОПТИМАЛЬНЫЙ ДЕКОДЕР ПРОГРАММИРУЕМЫХ ВЫХОДНЫХ ДАННЫХ ДЛЯ РЕШЕТЧАТЫХ КОДОВ С КОНЕЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ БИТОВ | 1997 |

|

RU2179367C2 |

| ДЕКОДЕР ВИТЕРБИ | 1997 |

|

RU2127944C1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Насос | 1917 |

|

SU13A1 |

| US 6408420, D1, 18.06.2002 | |||

| US 5935270, A, 10.08.1999 | |||

| Зажимное устройство | 1981 |

|

SU973292A1 |

Авторы

Даты

2009-07-27—Публикация

2006-05-18—Подача