Область техники

Изобретение относится к цифровому устройству и способу воспроизведения сигнала для воспроизведения цифрового сигнала, который записан в виде множества значений, как например информация о положении границы углублений (питов).

Уровень техники

Практический способ такой системы для записи границ углублений как постепенных изменений положения со множеством значений раскрыт, например, в патенте США N 5557592. В обычной системе для записи и воспроизведения многозначной информации используется технология для удаления влияния шума в системах для записи и воспроизведения многозначной информации. Эта технология называется матричной кодирующей модуляцией. Например, основные принципы такой технологии описаны в "Journal of information processing society of Japan", vol. 72, N 3, стр. 306-316, март 1989. В матричной кодирующей модуляции при записи сигнала добавлен код свертки. Таким образом, так как комбинации воспроизведенных сигналов являются ограниченными, то правильная последовательность сигнала оценивается с помощью последовательности воспроизведенного сигнала так, чтобы удалить влияние шума или ему подобных. Такая система матричной кодирующей модуляции особенно эффективна для случайной помехи, например такой, как шум.

С другой стороны, в реальной системе, в то время как сигнал записывается или воспроизводится, сигнал может быть искажен. Значение воспроизведенного сигнала иногда отличается от идеального значения. Ошибка из-за искажения всегда постоянна до тех пор, пока записываемая информация является одной и той же, непохожей на ошибку шума. Матричная кодирующая модуляция эффективна против ошибки из-за искажения до некоторой степени. Однако, так как шум может быть случайным, то эффект удаления шума недостаточен.

Сущность изобретения

Таким образом, задачей настоящего изобретения является создание цифрового устройства и способа воспроизведения сигнала для корректного воспроизведения записанных данных, даже если присутствуют случайный шум и искажение сигнала.

Первым аспектом настоящего изобретения является цифровое устройство воспроизведения сигнала для воспроизведения многозначного цифрового сигнала, записанного на записывающую среду, содержащее множество средств приема записанного сигнала и определения виртуально записанного сигнала, средство оценки воспроизведенного сигнала для оценки амплитуды воспроизводимого сигнала, соответствующего виртуально записанному сигналу, средство вычисления расстояния между оценочным воспроизведенным сигналом и реальным воспроизведенным сигналом и средство декодирования для вычисления суммы множества выходных сигналов средства вычисления расстояния, множества выходных сигналов, хронологически изменяющихся, детектирования минимального выходного сигнала из суммы и выдачи воспроизведенных данных, соответствующих детектированному результату, при этом множество средств приема записанного сигнала выполнено с возможностью принимать только часть записанного сигнала, а средство декодирования - с возможностью определения бит старших разрядов записанного сигнала по указанному минимальному выходному сигналу из суммы, а бит младших разрядов с помощью выходных данных средства приема.

Согласно одному из наилучших вариантов осуществления изобретения средство оценки воспроизведенного сигнала выполнено с возможностью вычисления разности между выходным сигналом средства декодирования и воспроизведенным сигналом, декодированным средством декодирования и обновлять оценочное значение, соответствующее разности.

Вторым аспектом настоящего изобретения является способ воспроизведения цифрового сигнала для воспроизведения многозначного цифрового сигнала, записанного на записывающую среду, содержащий следующие этапы: принимают записанный сигнал и детектируют виртуально записанный сигнал, оценивают амплитуду воспроизведенного сигнала, соответствующего виртуально записанной информации, вычисляют разность между оценочным воспроизведенным сигналом и реальным воспроизведенным сигналом и вычисляют сумму расстояний, которые хронологически отличаются друг от друга, детектируя минимальное значение из суммы, и выдают воспроизведенные данные, соответствующие детектированному результату, при этом на стадии приема принимают только часть записанного сигнала, при выдаче воспроизведенных данных определяют биты старших разрядов записанного сигнала по указанному минимальному значению из суммы, а биты младших разрядов - с помощью выходных данных средства приема записанного сигнала.

Положение границ передней границы и задней границы каждого углубления, образованного на записывающей среде, например на оптическом диске, модулируется записанными данными и записанные данные записываются как множество значений. Когда записанные данные воспроизводятся с оптического диска, то воспроизведенный сигнал получается посредством дискретизации обеих границ сигнала, соответствующих каждому углублению. В этом случае оценивается амплитуда воспроизведенного сигнала, соответствующего виртуально записанным данным. Таким образом, вычисляется расстояние между оцененным воспроизведенным сигналом и реально воспроизведенным сигналом. Когда это расстояние декодируется с помощью способа декодирования максимальной вероятности, то записанные данные декодируются.

Эти и другие задачи, особенности и преимущества настоящего изобретения станут более понятными в свете последующего подробного описания наилучшего режима его воплощения, что иллюстрируется сопроводительными чертежами.

Краткое описание чертежей

В дальнейшем изобретение поясняется наилучшими вариантами его воплощения со ссылками на сопроводительные чертежи, на которых:

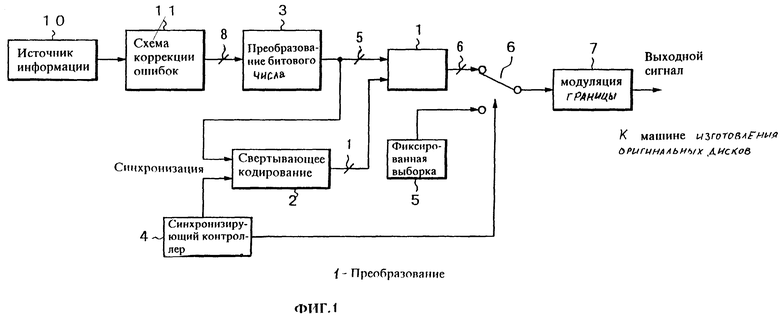

фиг.1 изображает блок-схему примера устройства записи,

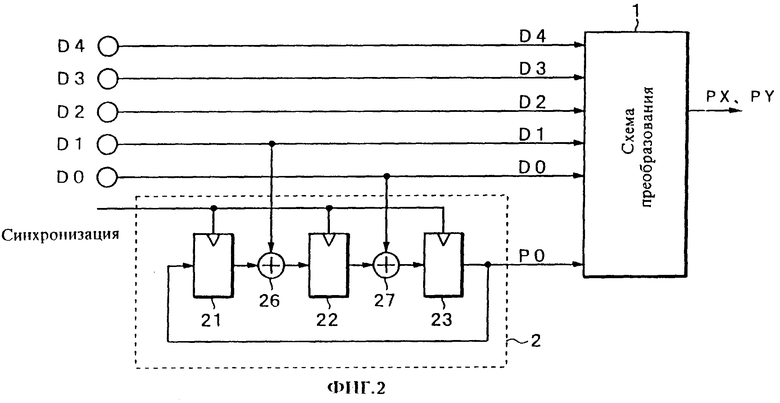

фиг.2 изображает блок-схему примера схемы вычисления кода свертки,

фиг.3 изображает пример преобразования записанных данных и данных положения границы углубления,

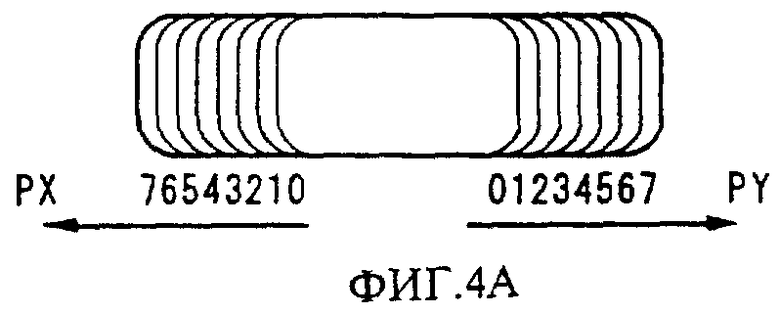

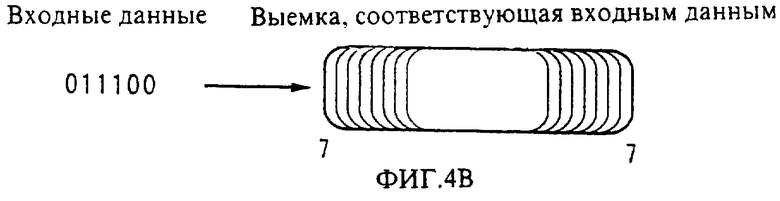

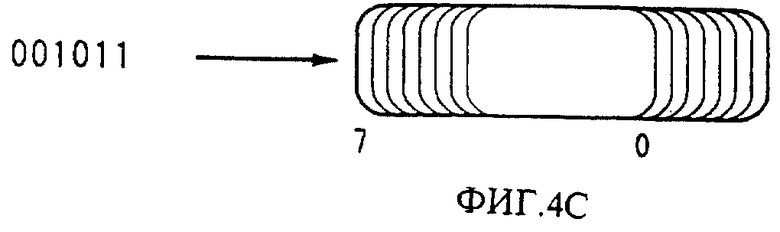

фиг.4А-4С изображают схему объяснения многозначного способа записи,

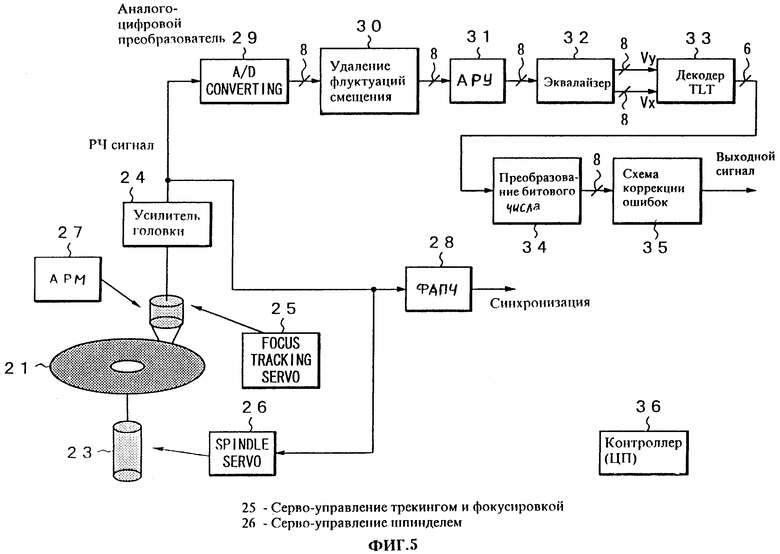

фиг.5 является общей схемой, изображающей устройство воспроизведения, согласно воплощению настоящего изобретения,

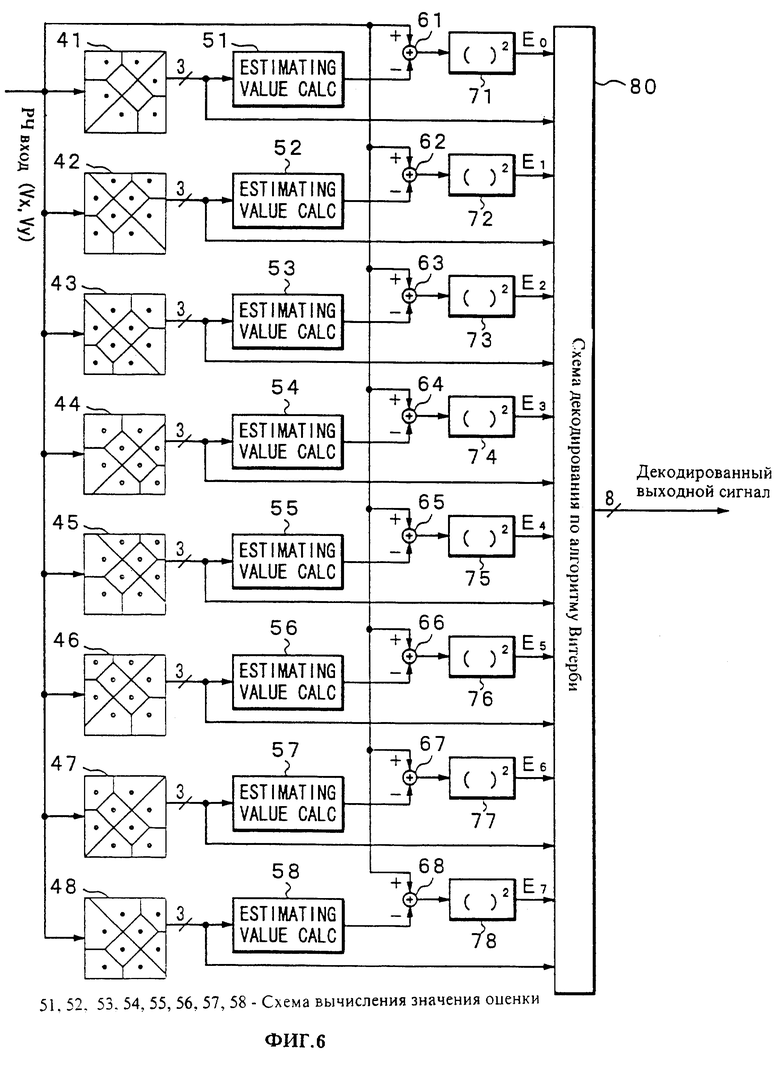

фиг.6 изображает схему TLT декодера согласно воплощению настоящего изобретения,

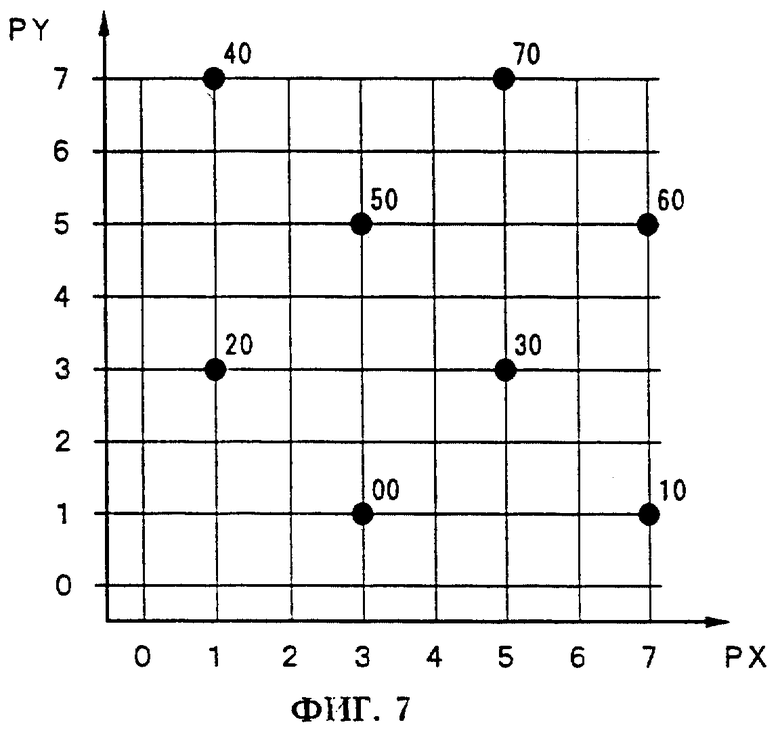

фиг.7 изображает схему преобразования записанной информации в случае, когда три бита младших разрядов равны 000,

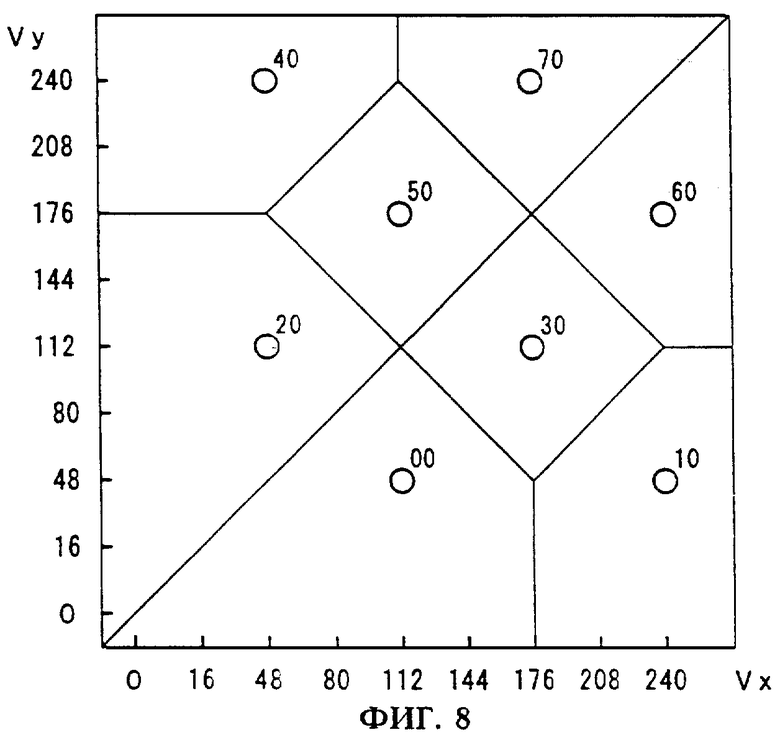

фиг.8 изображает схему двумерной области декодирования в случае, когда три бита младших разрядов равны 000,

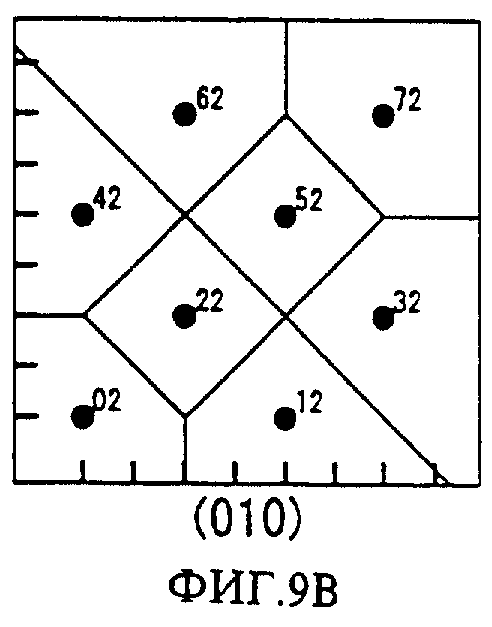

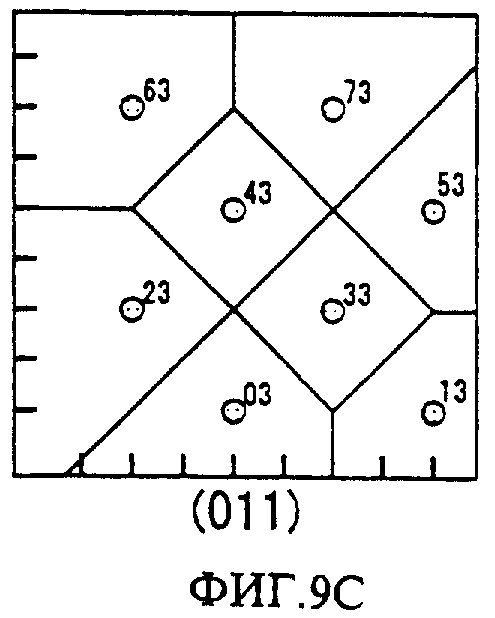

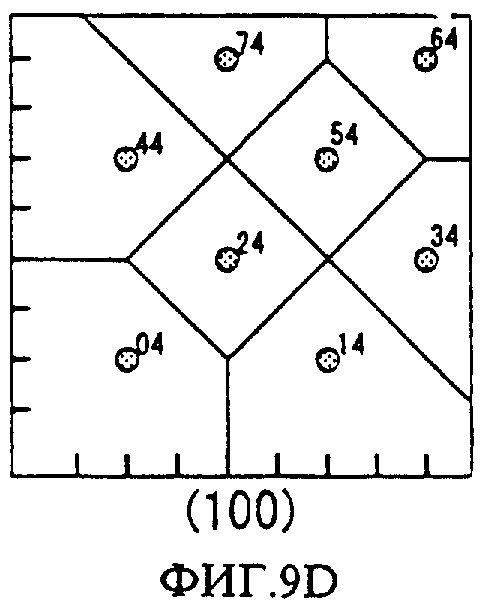

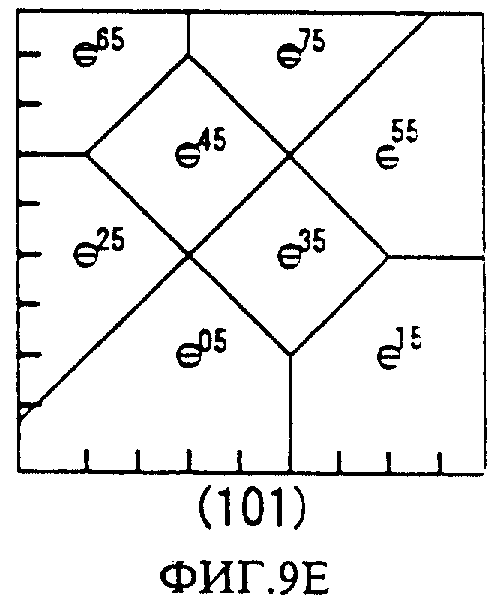

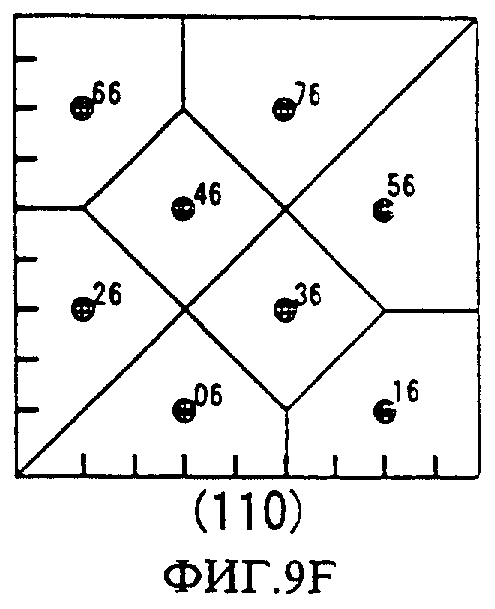

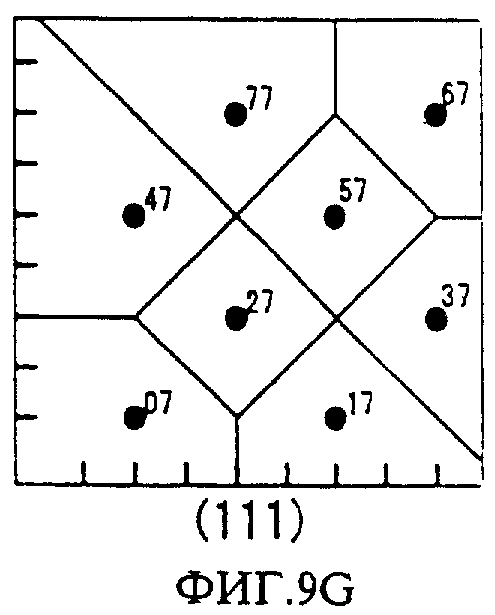

фиг.9А-9G изображают схему класса двумерного кодирования в случае, когда три бита младших разрядов находятся в диапазоне от 001 до 111,

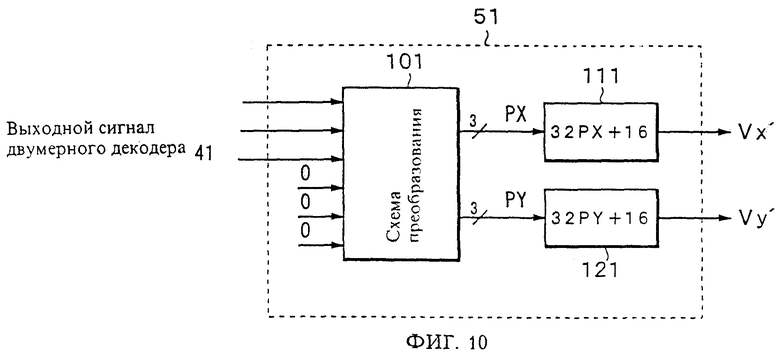

фиг.10 изображает пример схемы вычисления оцененных значений TLT декодера,

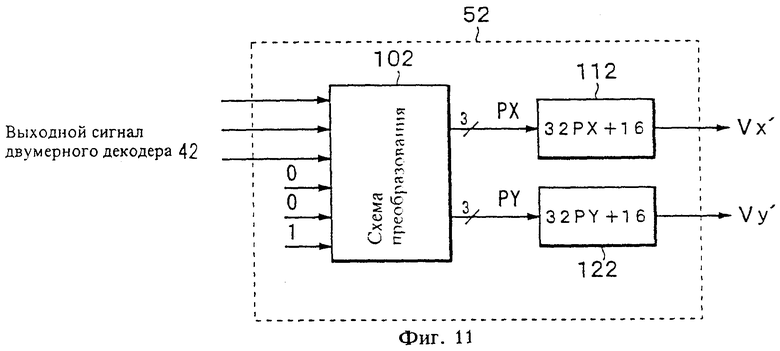

фиг.11 изображает пример схемы вычисления оцененных значений TLT декодера,

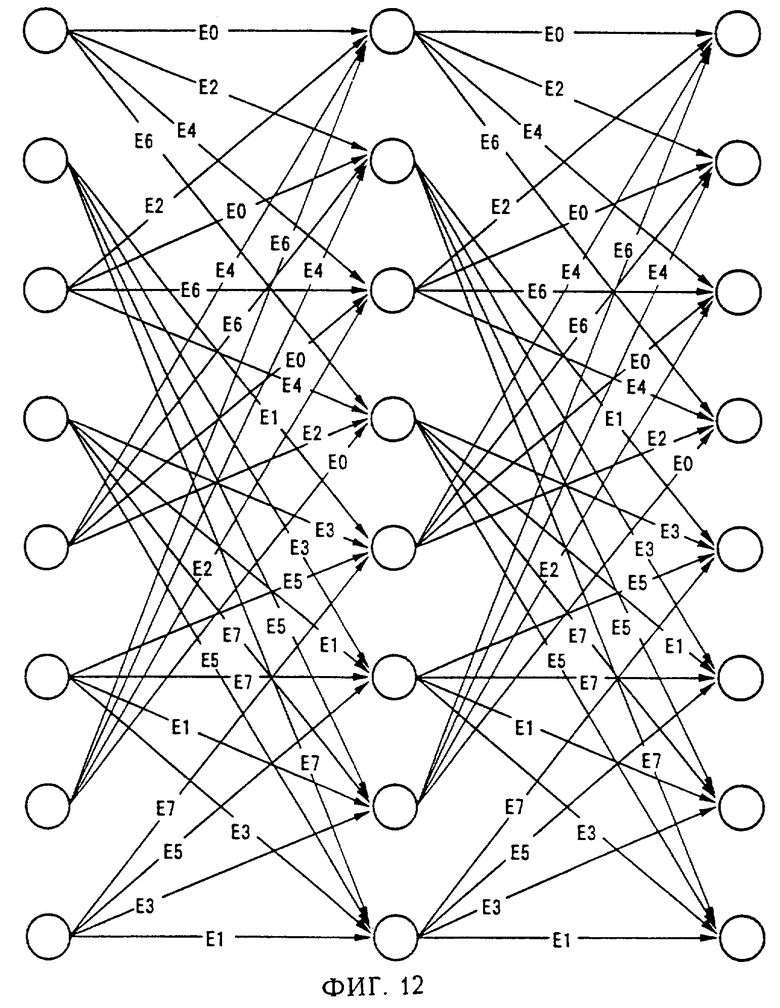

фиг.12 изображает схему матрицы для объяснения схемы декодирования Витерби TLT декодера,

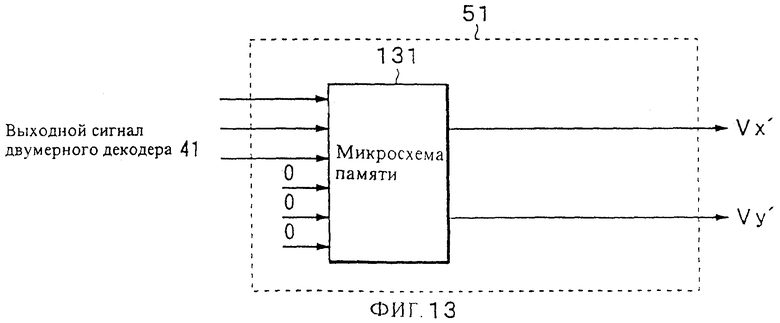

фиг.13 изображает другой пример схемы вычисления оцененных значений TLT декодера,

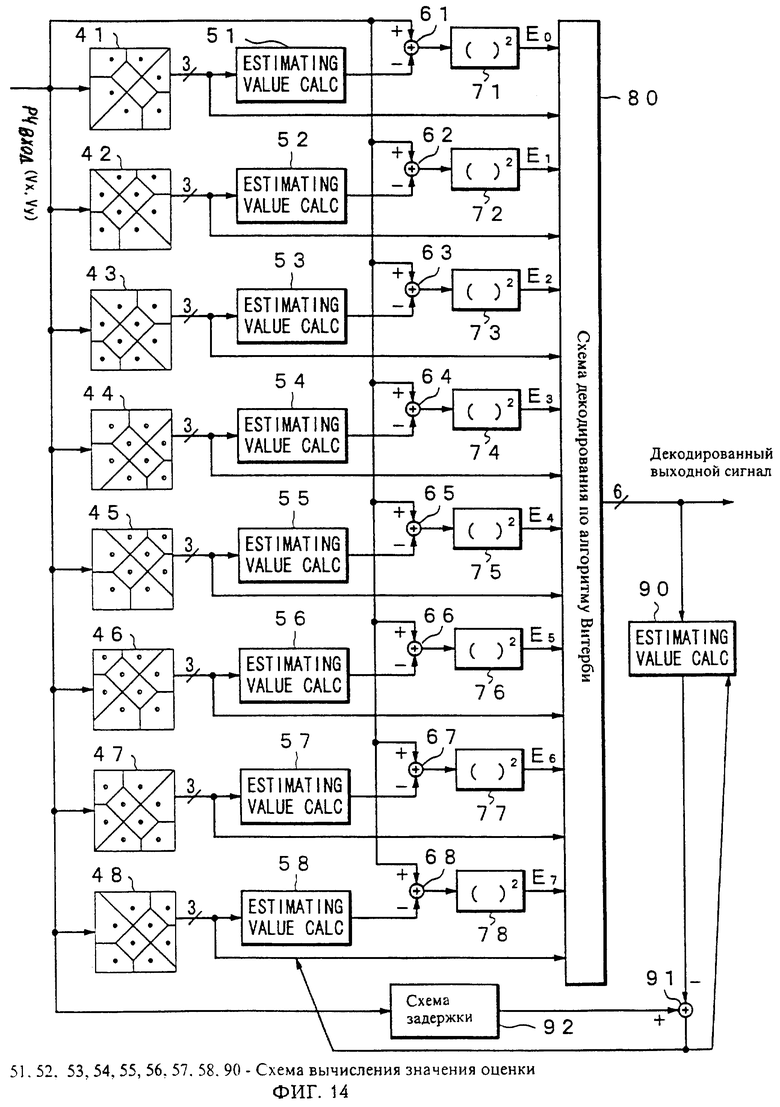

фиг.14 изображает схему TLT декодера согласно другому воплощению настоящего изобретения.

Подробное описание предпочтительных вариантов воплощения

Ниже описывается воплощение согласно настоящему изобретению со ссылками на сопроводительные чертежи. Фиг.1 изображает пример устройства записи, которое записывает цифровой сигнал на оптический диск. Цифровой сигнал (включая цифровой аудиосигнал, цифровой видеосигнал и т.д.), поданный от источника 10 информации, подается на схему 11 коррекции ошибки.

Как и с обычным оптическим диском, схема 11 коррекции ошибки добавляет код коррекции ошибки (CIRC), который является кодом Рида-Соломона, к цифровому сигналу, поданному от источника 10 информации. Этот код коррекции ошибки является тем же, что и тот, который применяется в обычном компакт-диске (CD). Этот код добавляется как избыточный так. что лаже если часть воспроизведенного сигнала содержит ошибку из-за дефекта диска, данные могут быть правильно считаны. Этот код коррекции ошибки вычисляется для каждых восьми бит (одного байта). Таким образом, данные выдаются с каждыми восемью битами. Однако, согласно воплощению, так как данные из пяти бит записываются для каждого углубления, восьмибитные данные преобразуются в пятибитные данные с помощью схемы 3 преобразования битового числа.

Схема 3 преобразования битового числа запоминает блоки данных из восьми битов (общее количество 40 бит) в регистре. Затем схема 3 преобразования битового числа выдает пятибитовые блоки данных из регистра. Выходные данные схемы 3 преобразования битового числа подаются на схему 1 преобразования и схему 2 вычисления кода свертки. Синхронизирующий контроллер 4 подает сигнал синхронизации на схему 2 вычисления кода свертки. Схема 2 вычисления кода свертки вычисляет код свертки и добавляет вычисленный код в качестве младшего значащего бита последовательности данных. Получившийся шестибитовый блок данных подается на схему 1 преобразования. Схема 1 преобразования преобразует шесть битов и положения границ передней границы и задней границы. Каждая из передней границы и задней границы независимо модулируется на восемь уровней. Положение границы передней границы и задней границы представляет собой три бита. Таким образом, данные из шести битов выдаются из схемы 1 преобразования для каждого углубления.

Шестибитовый сигнал подается от схемы 1 преобразования на один из двух входных выводов селектора 6 данных. Фиксированная выборка подается из схемы 5 генерирования фиксированной выборки на другой входной вывод селектора 6 данных. В соответствии с управляющим сигналом, подаваемым от синхронизирующего контроллера 4, селектор 6 данных переключается на заданные интервалы. Таким образом, фиксированная выборка вставляется в качестве опорного сигнала между последовательностями данных. Когда сигнал воспроизводится с диска, состояние углублений на диске может быть детектировано в соответствии с опорным сигналом. Сигнал синхронизации, который является опорным временным сигналом для данных воспроизведения с диска, воспроизводится из опорного сигнала.

Шестибитовый блочный сигнал подается из селектора 6 на схему 7 модулирования границы. Схема 7 модулирования границы модулирует положения границы каждого углубления, соответствующего шестибитовым блочным данным. Выходной сигнал схемы 7 модулирования границы подается на машину изготовления оригинала (не показана) и записывается на стеклянный оригинальный диск с помощью лазерного луча.

Оптический оригинальный диск, на который записываются данные, производится тем же способом, что и обычный оптический оригинальный диск. Затем оптический диск покрывается и окончательно создается штамп. С помощью штампа воспроизводятся диски так же, как оптические диски, например CD. Углубления производятся регулярно на фронтальной поверхности каждого воспроизведенного диска. Каждая из передней границы или задней границы каждого углубления модулируются на восемь уровней. Таким образом, одно углубление представляет собой данные из шести бит. Посредством записи данных со множеством значений увеличивается плотность записи.

Фиг.2 изображает пример схемы 2 вычисления кода свертки. На фиг.2 часть, окруженная точечной линией, представляет собой блок схемы 2 вычисления кода свертки. Схема 2 вычисления кода свертки состоит из трех триггеров 21-23 и двух схем 26 и 27 ИСКЛЮЧАЮЩЕЕ ИЛИ. На фиг.1 выходной сигнал данные блока из пяти битов подаются от схемы 3 преобразования битового числа и на схему 1 преобразования и на схему 2 вычисления кода свертки. Однако, в действительности, как изображено на фиг.2, данные, используемые в схеме 2 вычисления кода свертки, являются только двумя битами младших разрядов (D1 и D0) выходных данных схемы преобразования битового числа.

Схема 2 вычисления кода свертки вычисляет код Р6 свертки для каждого углубления (а именно, для каждых пятибитовых блочных данных) и выдает результат на схему 1 преобразования. Триггер 21 из трех триггеров изменяет состояние в соответствии с состоянием выхода триггера 23 для каждого углубления. Триггер 22 изменяет состояние в соответствии с состоянием сигнала выходного сигнала ИСКЛЮЧАЮЩЕЕ ИЛИ выходного сигнала триггера 21 и второго наименьшего значащего бита D1 схемы 2 преобразования битового числа для каждого углубления. Аналогично, триггер 23 изменяет состояние, соответствующее выходному сигналу ИСКЛЮЧАЮЩЕЕ ИЛИ выходного сигнала триггера 22 и наименьшего значащего бита D0 для схемы 2 преобразования битового числа.

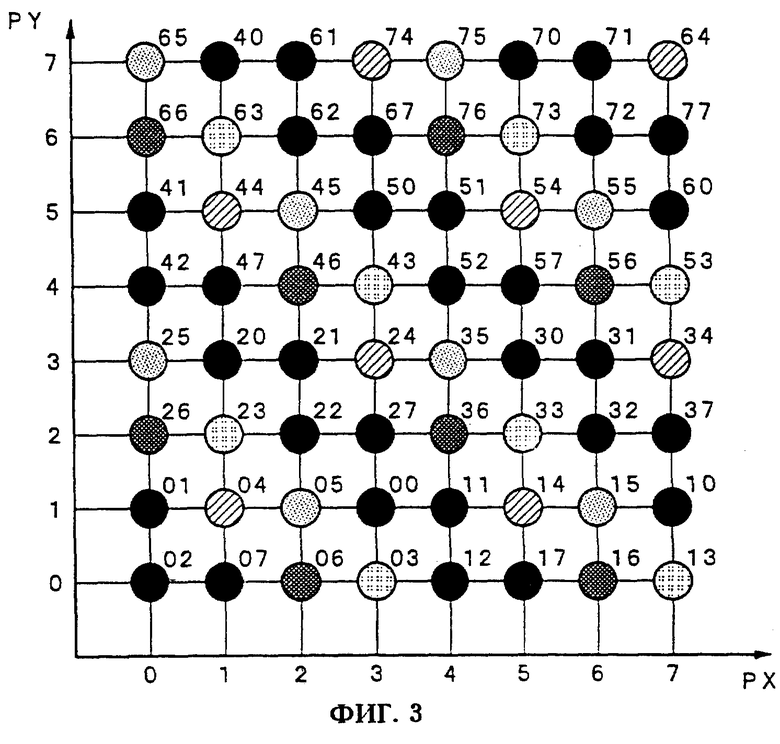

Далее описывается схема 1 преобразования. Схема 1 преобразования вводит пять битов D4-D0 схемы 3 преобразования битового числа и один бит Р0 схемы 2 вычисления кода свертки и выдает данные РХ и PY положения границы бита, каждые из которых состоят из трех битов. Фиг.3 изображает пример способа преобразования. На фиг.3 числа 00 до 77, размещенные в верхнем правом положении каждой точки решетки, представляют собой шестибитовые входные данные (D4, D3, D2, D1, D0 и Р0) в восьмеричной системе счисления (три бита данных положения границы бита представлены числами 0-7). Числа от 0 до 7, обозначенные на осях Х и Y, представляют собой трехбитовые данные РХ и PY.

Например, когда значения шести битов (D4, D3, D2, D1, D0 и Р0) входных данных равны (0, 0, 1, 0, 1 и 1), то входные данные в восьмеричной системе счисления равны 13. В этом случае определяется положение, точка решетки которого равна 13, и координаты Х и Y (РХ, PY) определенной точки решетки становятся (7, 0). Так как схема 1 преобразования выдает шестибитовые данные по сравнению с шестибитовыми входными данными, то схема 1 преобразования может быть выполнена с помощью микросхемы памяти, например памяти только для чтения (ROM).

После того как фиксированная выборка вставлена в качестве опорных данных, данные РХ и PY положения границы подаются на вход схемы 7 модуляции границы. Как изображено на фиг.4А, положение передней границы каждого углубления постепенно увеличивается в соответствии со значением РХ. К тому же, значение задней границы постепенно увеличивается в соответствии со значением PY.

Фиг.4В изображает пример соотношения между входными данными схемы 1 преобразования и формой углубления, которое записывается как ему соответствующее. На фиг.4В записанные данные в восьмеричной системе счисления равны 64. Схема 1 преобразования (фиг.3) получает РХ=7 и PY=7, соответствующие 64. Таким образом, и передний перепад и задний перепад углубления установлены на наибольшую длину углубления. В примере, изображенном на фиг.4С, записанные данные в восьмеричной нотации равны 13. В этом примере передний перепад углубления сдвинут к максимальной позиции, а задний перепад углубления установлен на самую короткую позицию.

Как описано выше, в настоящем изобретении множество значений записываются в качестве данных так, что положение передней границы и задней границы каждого углубления модулируются. Фиг.5 изображает оптический диск устройства воспроизведения согласно воплощению настоящего изобретения. На фиг.5 ссылочный номер 21 указывает оптический диск, который воспроизводится с оригинального диска, на котором данные записаны с помощью описанной выше системы изготовления оригинальных дисков. Номером 23 обозначен двигатель шпинделя, который врашает оптический диск 21 с постоянной линейной скоростью (CLV) или постоянной угловой скоростью (CAV). Оптическое устройство 22 считывания излучает лазерный луч на оптический диск 21. Фотодетектор в оптическом устройстве 22 считывания преобразует количество отраженного света в электрический сигнал и получает воспроизведенный РЧ сигнал через усилитель 24 головки.

Оптическое устройство 22 считывания управляется сервосхемой 25. Двигатель 23 шпинделя управляется схемой 26 сервоуправления шпинделем. На фиг.5 сервосхема 25 представлена как один блок. Однако сервосхема 25 включает в себя схемы сервоуправления фокусировкой (которая позволяет оптическому устройству 22 считывания правильно фокусироваться), сервоуправления трекингом (которая выравнивает оптическое пятно на нужную дорожку), сервоуправления сдвигом (которое перемещает оптическое устройство 22 считывания в правильное положение в радиальном направлении) и т.д. Сигнал ошибки фокусировки и сигнал ошибки трекинга образуются при вычислении выходного сигнала, например, четырехразделенного детектора. При необходимости вводится схема 27 АРС (автоматическая регулировка мощности) так, чтобы поддерживать правильную мощность лазера.

Воспроизведенный РЧ сигнал подается на схему 28 PLL (фазовой подстройки частоты - ФАПЧ). Схема 28 ФАПЧ генерирует сигнал синхронизации и подает его на всю систему. Аналого-цифровой преобразователь 29 преобразует воспроизведенный РЧ сигнал из аналогового сигнала в восьмибитовый цифровой сигнал при синхронизации с синхронизирующим сигналом. Затем схема 30 удаления флуктуации смешения и схема 31 AGC (автоматической регулировки усиления - АРУ) корректируют флуктуации смешения и усиления, которые имеют место из-за различных случайностей на этапах изготовления диска, с опорным сигналом, который периодически записан между каждыми данными. Схема 30 удаления флуктуации смещения удаляет вертикальные флуктуации входного воспроизведенного сигнала (а именно, флуктуации смещения) по отношению к уровню опорного сигнала, образованного между каждыми данными. Схема 31 AGC удаляет флуктуации усиления (а именно, флуктуации амплитуды воспроизведенного сигнала) по отношению к опорному сигналу.

Выходной сигнал схемы 31 AGC подается на эквалайзер 32. Эквалайзер 32 удаляет межкодовые помехи между записанными сигналами. Выходной сигнал эквалайзера 32 является парой сигналов Vx и Vy. Сигнал Vx получен дискретизацией передней границы каждого углубления. Сигнал Vy получен дискретизацией задней границы каждого углубления. Выходной сигнал эквалайзера 32 подается на TLT декодер 33. Как будет описано ниже, TLT декодер 33 декодирует выходной сигнал эквалайзера 32 так, что влияния искажения сигнала и случайный шум удаляются с информацией кода свертки, который добавляется к записанным данным. Как описано выше, так как код свертки является избыточной информацией, которая добавлена для удаления влияния шума и т.д., пятибитовая информация, для которой код свертки удаляется, получается для каждого углубления.

После того как TLT декодер 33 декодирует входные данные в пятибитовые блочные данные, схема 34 преобразования битового числа преобразует пятибитовые блочные данные в восьмибитовые блочные данные. Этот процесс выполняется с помощью сохранения восьми пятибитовых блоков в сдвиговом регистре и считывания из него пяти восьмибитовых блоков. Схема 34 преобразования битового числа подает восьмибитовые блочные данные на схему 35 коррекции ошибки. Схема 35 коррекции ошибки удаляет влияние дефекта на диске. Схема 35 коррекции ошибки выдает воспроизведенные данные. Для управления работой вышеописанного устройства воспроизведения с диска встраивается контроллер 36 (центральный процессор).

Далее описывается пример структуры TLT декодера 33. Сигналы Vx и Vy, обе границы каждого углубления которых дискретизированы, подаются на вход TLT декодера 33. Схема 30 удаления флуктуации смещения удаляет флуктуации смещения. Схема 31 AGC имеет нормализованную амплитуду сигнала. Таким образом, так как искажение из-за несовершенства системы записи и влияние шума, введенные в любом случае в процесс записи и процесс воспроизведения, удаляются из входных сигналов Vx и Vy, то они имеют значения, соответствующие положениям (РХ и PY). которые располагаются на записанных границах углубления.

Усиление схемы 31 AGC и значение смещения схемы 30 удаления флуктуации смещения могут быть установлены конструктором. Однако в настоящем изобретении схема 30 удаления флуктуации смещения и схема 31 AGC сконструированы так, что когда шум и искажение не имеют места, то сигналы Vx и Vy удовлетворяют следующим соотношениям:

Например, когда сигнал воспроизводится с углубления, позиции передней и задней границ (РХ и PY) которого записаны как (0 и 7), то входные сигналы (Vx и Vy) на TLT декодер 33 имеют значения (16 и 240). Так как входные сигналы (Vx и Vy) на TLT декодере 33 испытывают воздействие шума и искажения, то эти значения слабо изменяются. TLT декодер 33 правильно декодирует сигналы, которые слабо отклоняются от идеальных значений.

Фиг.6 изображает пример структуры TLT декодера 33. Восемь двумерных декодеров 41-48 дают восемь декодированных значений, соответствующих входным сигналам (Vx и Vy). Значения трех битов младшего разряда декодированных значений восьми двумерных декодеров 41-48 равны 000-111. Двумерные декодеры 41-48 являются средством приема записанной информации, которое принимает записанные данные и определяют виртуально записанную информацию. Например, самая верхняя схема 41 декодирования соответствует случаю, когда три бита младшего разряда входного сигнала равны 000. Двумерный декодер 41 декодирует данные с предположением, что три бита младшего разряда равны 000.

Существует восемь путей для данных, три бита младшего разряда которых равны 000. Фиг.7 изображает преобразование, в котором выделено только восемь сигналов. Как ясно из фиг.7, восемь путей записанных данных, три бита младшего разряда которых равны 000, установлены так, что каждые записанные данные являются максимально удаленными друг от друга на плоскости отображения (преобразования). В случае, когда известно, что три бита младшего разряда записанных данных равны 000, когда воспроизведенные сигналы Vx и Vy отделены пороговыми значениями на двумерной плоскости, каждый сигнал которой достаточно удален от других, три бита старшего разряда могут быть декодированы. Другими словами, область декодирования данных, три бита младшего разряда которых равны 000, образованы пороговыми значениями, представленными линиями. Как изображено на фиг.8, когда сигналы Vx и Vy декодированы в соответствии с определением пороговых значений на двумерной плоскости, так как расстояние между пороговыми значениями достаточно велико, даже если существует в некоторой степени искажение и шум, три бита старшего разряда могут быть декодированы.

Аналогично, второй верхний двумерный декодер 42 декодирует данные с предположением, что три бита младшего разряда равны 001. Когда три бита младшего разряда записанных данных равны 001, как и в случае, когда три бита младшего разряда равны 000, информационные точки, соответствующие трем битам старшего разряда, установлены так, что они максимально удалены друг от друга. Таким образом, с помощью двумерного декодера 42 пороговые значения которого установлены на двумерной плоскости так, как изображено на фиг.9А, могут быть получены значения трех битов старшего разряда.

Фиг.9В изображает область декодирования двумерного декодера 43, соответствующего случаю, когда три бита младшего разряда равны 010. Фиг.9С изображает область декодирования двумерного декодера 44, когда три бита младшего разряда равны 011. Фиг.9D изображает область декодирования двумерного декодера 45, когда три бита младшего разряда равны 100. Фиг.9Е изображает область декодирования двумерного декодера 46, когда три бита младшего разряда равны 101. Фиг.9F изображает область декодирования двумерного декодера 47, когда три бита младшего разряда равны 110. Фиг.9G изображает область декодирования двумерного декодера 48, когда три бита младшего разряда равны 111.

Таким образом, так как двумерные декодеры расположены соответствующими всем комбинациям трех битов младшего разряда, несмотря на влияние шума, и искажения являются слишком большими, один из этих восьми декодеров 41-48 может выдавать правильные данные. Однако точно не известно, какой из этих восьми декодеров 41-48 выдает правильные данные. Чтобы решить эту задачу, TLT декодер 33 предполагает, что все декодеры 41-48 выдают правильные данные и выполняет обработки для всех двумерных декодеров 41-48.

Схемы 51-58 вычисления оценочных значений подсоединены к выходам восьми двумерных декодеров 41-48. Схемы 51-58 вычисления оценочных значений являются средством оценки воспроизведенного сигнала, которое оценивает амплитуды воспроизведенных сигналов. соответствующих виртуально записанной информации. Декодированные данные трех битов старшего разряда подаются на восемь схем 51-58 вычисления оценочных значений. Схемы 51-58 вычисления оценочных значений расположены соответствующими всем комбинациям трех битов младшего разряда данных. Каждая схема вычисления оценочного значения получает все шестибитовые данные, записанные в одном углублении. С помощью шестибитовых данных каждая схема вычисления оценочного значения может вычислять значения воспроизведенного сигнала, которое полностью свободно от случайной ошибки из-за шума и т.п. Эти значения называются оценочными значениями (Vx' и Vy').

Фиг.10 изображает пример, посредством которого схема 51 вычисления оценочного значения может быть наиболее просто выполнена. На фиг.10 трехбитовые выходные данные двумерного декодера 51 подаются на схему 101 преобразования. Схема 101 преобразования выдает данные положения границы углубления (РХ и PY), три бита младшего разряда которого равны (0; 0 и 0). Схема 101 преобразования выполняет ту же функцию, что и схема 1 преобразования. Схема 101 преобразования может быть выполнена на микросхеме памяти или ей подобной. С помощью положений РХ и PY границы углубления схемы 111 и 121 выполняют вычисления, выраженные формулами (1) и (2) так, чтобы получить оценочные значения Vx' и Vy' воспроизведенных сигналов.

Другие схемы 52-58 вычисления оценочного значения имеют ту же структуру, что и схема 51 вычисления оценочного значения. Изменяя входные выборки трех битов младшего разряда на схему преобразования, эти схемы 52-58 вычисления оценочного значения могут быть реализованы. Фиг.11 изображает пример наиболее простой схемы 42 вычисления оценочного значения, три бита младшего разряда которого равны (0, 0 и 1). Как и со схемой 41 вычисления оценочного значения, каждая из схем 52-58 вычисления оценочного значения состоит из схемы 102 преобразования и схем 112 и 122 вычисления.

Схемы 61-68 вычитания вычисляют разности между восемью состояниями оценочных значений (Vx' и Vy') и реальными воспроизведенными значениями (Vx и Vy). Результаты вычитания поступают на вход устройств 71-78 вычисления квадрата. Устройства 71-78 вычисления квадрата выдают мощности ошибки Е0, Е1, Е2, Е3, Е4, Е5, Е6 и Е7. Схемы 61-68 вычитания и устройства 71-78 вычисления квадрата являются примером средства вычисления расстояния, которое вычисляет расстояние между оценочными воспроизведенными сигналами и реальными воспроизведенными сигналами. Другими словами, устройства 71-78 вычисления получают мощности ошибки, соответствующие следующей формуле:

Мощность ошибки=(Vx-Vx')2+(Vy-Vy')2

Сигналы, полученные в качестве мощностей ошибки, пропорциональны энергии "отклонения" между реальными воспроизведенными сигналами и оценочными значениями. Как описано выше, только один из восьми двумерных декодеров 41-48 принимает правильные три бита младшего разряда. Таким образом, только одна из схем вычисления оценочных значений выдает правильное оценочное значение (Vx' и Vy'). Когда влияние шума игнорируется, то считается, что правильные оценочные значения являются наиболее близкими к воспроизведенным сигналам. Таким образом, несмотря на влияние шума, выбирается одно из восьми устройств 71-78 вычисления квадрата, которое выдает минимальную мощность ошибки. Можно предположить, что когда определен выходной сигнал соответствующего двумерного декодера, то может быть получен выходной сигнал декодера с максимальной вероятностью. Однако в действительности всегда существует влияние шума. Когда декодирован воспроизведенный сигнал в какой-либо момент времени, если шум с большой амплитудой входит в сигнал в этот момент, то имеет место ошибка декодирования.

Для решения этой проблемы в воплощении настоящего изобретения наблюдаются восемь мощностей Е0-Е7 ошибки с несколькими выборками, которые хронологически отличаются друг от друга. Одна из этих мощностей Е0-Е7 ошибки, которая имеет максимальную вероятность, рассматривается как декодированный выходной сигнал. При декодированном выходном сигнале шум удаляется. В этом воплощении при записи данных к нему добавляется код свертки. Таким образом, мощность ошибки, вычисленная воспроизведенным сигналом, показана на матричной диаграмме на фиг.12.

Предполагая, что данные с мощностью Е0 ошибки в верхнем левом состоянии записаны на фиг.12, следующие данные имеют мощность ошибки Е0, Е2, Е4 или Е6. Таким образом, ясно, что другие значения не получены. Так как возможные пути ограничены так, как изображено на фиг.12, путь выбирается так, что сумма мощностей ошибки становится минимальной. Таким образом, даже если большой шум входит в конкретную выборку, то может быть определено устройство вычисления характеристики квадрата с максимальной вероятностью.

В схеме, изображенной на фиг.6, устройство 80 декодирования Витерби выбирает из возможных путей путь с минимальным совокупным значением мощностей ошибки. Когда такой путь выбран, то определяются три бита старшего разряда. Три бита младшего разряда записанных данных определяются с помощью выходных данных двумерного декодера соответствующего пути. С помощью такого способа схема 80 декодирования Витерби выдает окончательные декодированные значения шести битов.

В воплощении была описана наиболее простая структура схем 51-58 вычисления значений оценки. Другими словами, в этой структуре предполагалось, что воспроизведенные сигналы являются идеальными (а именно, полностью свободными от искажения сигнала). Однако в реальном оптическом диске форма каждого углубления может варьироваться в зависимости от его размера. Таким образом, записанные данные углубления вызывают искажения воспроизведенного сигнала. Когда воспроизведенный сигнал искажен, он отличается от идеального значения. Таким образом, как и в случае введения шума. когда данные декодированы, ошибка может иметь место.

Для декодирования сигнала таким способом, что влияние такого искажения сигнала удалено, будет описано другое воплощение настоящего изобретения. Для предотвращения искажения сигнала схемы 51-58 вычисления оценочных значений, изображенные на фиг.13, используются вместо схем, изображенных на фиг.6.

Фиг.13 изображает структуру только схемы 51 вычисления оценочного значения. Однако структуры других схем 52-58 вычисления оценочного значения являются такими же, что и структура схемы 51 вычисления оценочного значения. Три бита выходных данных двумерного декодера 41 подаются на микросхему 131 памяти. Микросхема 131 памяти выдает оценочные значения Vx' и Vy'. Так как микросхема 131 памяти может хранить любые оценочные значения, соответствующие всем комбинациям шести битов данных, записанных на каждом углублении, то микросхема 131 памяти может управлять различными искажениями сигнала, которые имеют место на реальных оптических дисках. К тому же, когда микросхема 131 памяти является перезаписываемой памятью, в то время как данные воспроизводятся с диска, значения данных могут быть изменены. В этом случае может быть достигнут более значительный эффект, чем вышеописанное воплощение.

Фиг.14 изображает другое воплощение, в котором значения, хранимые в микросхеме памяти схемы вычисления оценочных значений, изменяются, в то время как данные воспроизводятся. Схема 90 вычисления оценочных значений вычисляет оценочные значения с помощью декодированных выходных данных. Схема 91 вычитания вычисляет разности между оценочными значениями и воспроизведенными сигналами, задержанными схемой 92 задержки. Таким образом, содержимое микросхем памяти схем 51-58 вычисления оценочных значений и схемы 90 вычисления оценочных значений обновляется так, чтобы выходные данные схемы 91 вычитания постепенно уменьшались. В воплощении, изображенном на фиг.14, может быть эффективно предотвращено влияние искажения, которое хронологически изменяется.

В этом воплощении с помощью модуляции или передней границы или задней границы каждого углубления цифровой сигнал может быть записан как множество значений. В настоящем изобретении перезаписываемая записывающая среда, например оптический диск, может использоваться так же, как среда, только для чтения.

Хотя настоящее изобретение описано по отношению к наилучшим режимам его воплощения, специалистам должно быть понятно, что вышеописанные и различные другие изменения, опущения и добавления в общем и в деталях могут быть сделаны без отхода от сущности и формы настоящего изобретения, объем защиты которого определяется прилагаемой формулой изобретения.

Изобретение относится к цифровому устройству и способу воспроизведения цифрового сигнала, записанного в виде множества значений. Имеется множество средств приема записанного сигнала и определения виртуально записанного сигнала, средство оценки воспроизведенного сигнала для оценки амплитуды воспроизводимого сигнала, соответствующего виртуально записанному сигналу, средство вычисления расстояния между оценочным воспроизведенным сигналом и реальным воспроизведенным сигналом и средство декодирования для вычисления суммы множества выходных сигналов средства вычисления расстояния множества выходных сигналов, изменяющихся хронологически. Осуществляется детектирование минимального выходного сигнала из суммы и выдачи воспроизведенных данных, соответствующих результату детектирования. Множество средств приема записанного сигнала выполнено с возможностью принимать только часть записанного сигнала. Средство декодирования выполнено с возможностью определения бит старших разрядов записанного сигнала по указанному минимальному выходному сигналу из суммы, а бит младших разрядов - с помощью выходных данных средства приема. Технический результат - уменьшение искажений сигнала из-за шумов. 2 с. и 1 з.п. ф-лы, 22 ил.

| US 5095392 A 10.03.1992 | |||

| US 4713829 A 15.12.1987 | |||

| Устройство для укладки рыбы в банки | 1977 |

|

SU682415A1 |

| US 5010401 A 23.04.1991 | |||

| US 5124861 A 23.06.1992 | |||

| US 5017883 A 21.05.1991 | |||

| Устройство для восстановления информации | 1990 |

|

SU1707620A1 |

Авторы

Даты

2004-05-10—Публикация

1996-12-20—Подача