Изобретение относится к накоплению информации, а именно к восстановлению информации.

Известно устройство для восстановления информации, содержащее блок фазовой автоподстройки.частоты, декодер, делитель частоты и элемент задержки, причем вход блока фазовой автоподстройки частоты соединен с входной шиной, а выход - к выходу делителя частоты и к первому входу декодера, выход которого соединен с выходной шиной устройства.

Недостатками известного устройства являются высокая погрешность восстановления информации за счет влияния фазовых колебаний информационного сигнала, а также низкое быстродействие и невысокая точность восстановления информации.

Наиболее близким к предлагаемому по технической сущности является устройство для восстановления информации, содержащее блек фазовой автоподстройки частоты, подключенный входом к входной шине и выходом через делитель частоты к первому входу декодера, соединенного выходом с выходной шиной, элемент задержки, мультиплексор, триггер, реверсивный счетчик и блок последовательно соединенных элементов задержки, подключенный входом к входной шине и выходами элементов задержки к информационным входам мультиплексора, подсоединенного выходом к

VJ

О ,v| О

го о

синхронизирующему входу реверсивного счетчика и триггера, соединенного выходом с управляющим входом реверсивного счетчика и с вторым входом декодера, причем элемент задержки включен между выходом блока фазовой автоподстройки частоты и информационным входом триггера, а реверсивный счетчик подключен выходами к адресным входам мультиплексора.

Недостатком известного устройства является низкое быстродействие. При значительном фазовом колебании реверсивный счетчик осуществляет подстройку задержки информационного сигнала к центру временного окна, последовательно перебирая все значения задержки от текущего до оптимального. При этом возникает объективное противоречие (свойственное большинству подобных систем) - требование точности подстройки фазового сдвига под значение окна обусловливает большое количество элементов задержки в блоке, причем каждая задержка {отдельного элемента) должна быть малой, чтобы не допустить большей тогрешности.

Наличие большого количества элементов задержки при их последовательном переборе требует большого времени подстройки задержки информационного сигнала к временному окну, что снижает эффективность работы устройства, так как значительное время из общего времени работы формируемый им фазовый сдвиг может находиться вдали от временного окна, не успевая подстраиваться под него при отработке фазовых колебаний. При значительных фазовых колебаниях (в плохих каналах связи) устройство может даже потерять работоспособность, так как при фиксированной скорости отслеживания ф.г- зоеых колебаний будет не в состоянии отрабатывать их фазсвый сдвиг (имеются в виде информационные сигналы).

Если же время отдельных задержек выбрано достаточно большим для реализации подстройки при значительных фазовых колебаниях, это вызывает снижение точности подстройки, так как, например, находясь вблизи временного окна в области ранней временной задержки, информационный сигнал вызывает подстройку устройства в область поздних временных задержек, что при большом значении отдельной временной задержки в блоке элементов задержки означает отдаление от оптимального времени задержки.

С целью частичного устранения указанного недостатка целесообразно реализовать переменную величину подстройки: на основе оценки близости задержки информационного сигнала к значению окна шаг подстройки должен быть пропорциональным разности между текущей и оптимальной задержками.

Кроме того, целесообразно реализовать зону нечувствительности устройсвта при достижении задержками значения, близкого к оптимальному (около временного окна), с целью повышения точности подстройки. Бу0 дучи близко к временному окну (или даже - в нем. ) неправомерно осуществлять подстройку, которая заведомо ухудшит фазовое соотношение информационного сигнала и синхросерии.

5 Целью изобретения является повышение быстродействия и точности.

Поставленная цель достигается тем, что в устройство для восстановления информации, содержащшее блок элементов задерж0 ки и блок фазовой автоподстройки частоты, подключенные выходами к входной шине, мультиплексор, информационные входы которого соединены с выходами элементов задержки, а выход соединен с одним входом

5 декодера, другой выход которого соединен с входом делителя, вход которого подключен к выходу блока Фазовой автоподстройки частоты, выход декодера соединен с выходной шиной, реверсивный счетчик и элемент

0 задержки, вход которого соединен с выходом блока фазовой автоподстройки частоты, введены формирователь импульсов, генератор, регистр, счетчик, дешифратор, элемент ИЛИ и сумматор, причем выход генератора

5 соединен с син: рсвходом счетчика, выходы которого соединены с входами дешифратора, выходы которого подключены к входам элемента ИЛИ, выход которого подключен к синхронизирующему входу реверсивного

0 счетчика, выход старшего рзэрядэ счетчика соединен с управляющим входом реверсивного счетчика и со старички разрядом первой группы входом сумматора, к другому входу первой группы которого подключены

5 выходы реверсивного счетчика, входы второй группы сумматора соединены с выходами регистра и с адресными входами мультиплексора, а выходы - с информационными входами регистра, выход мультиплексора подключен к синхровходу

0 счетчика, выход элемента задержки через формирователь импульсов соединен с входами сброса счетчика и реверсивного счетчика.

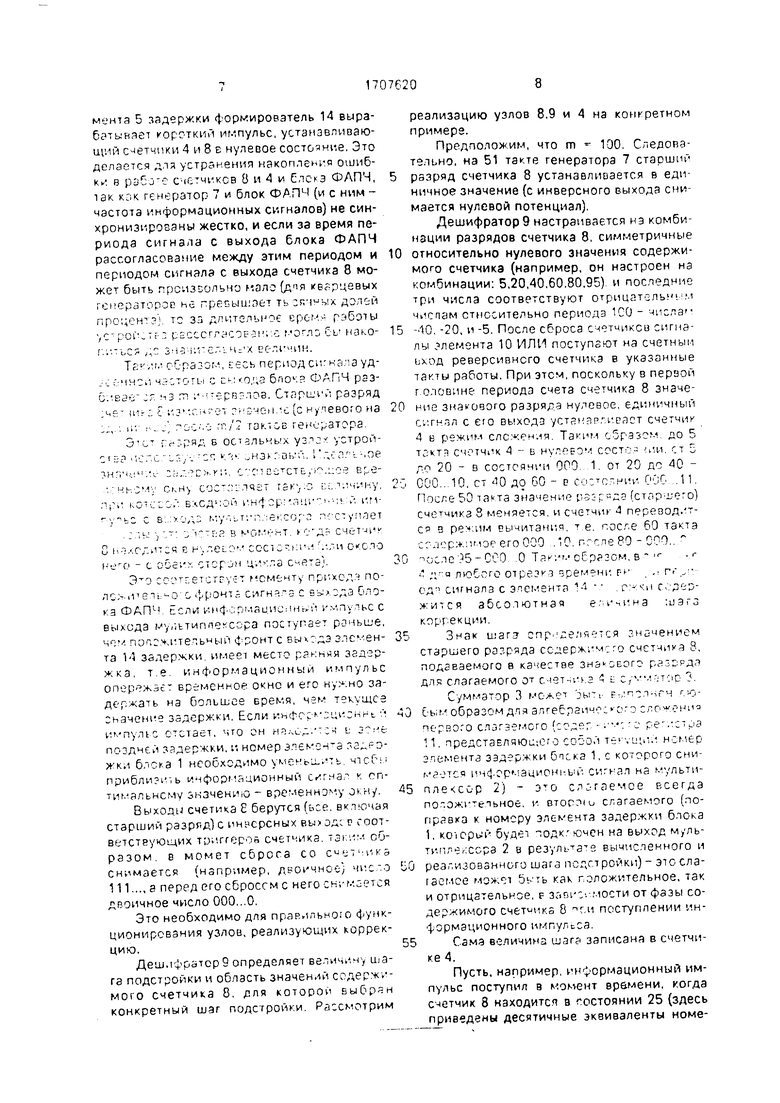

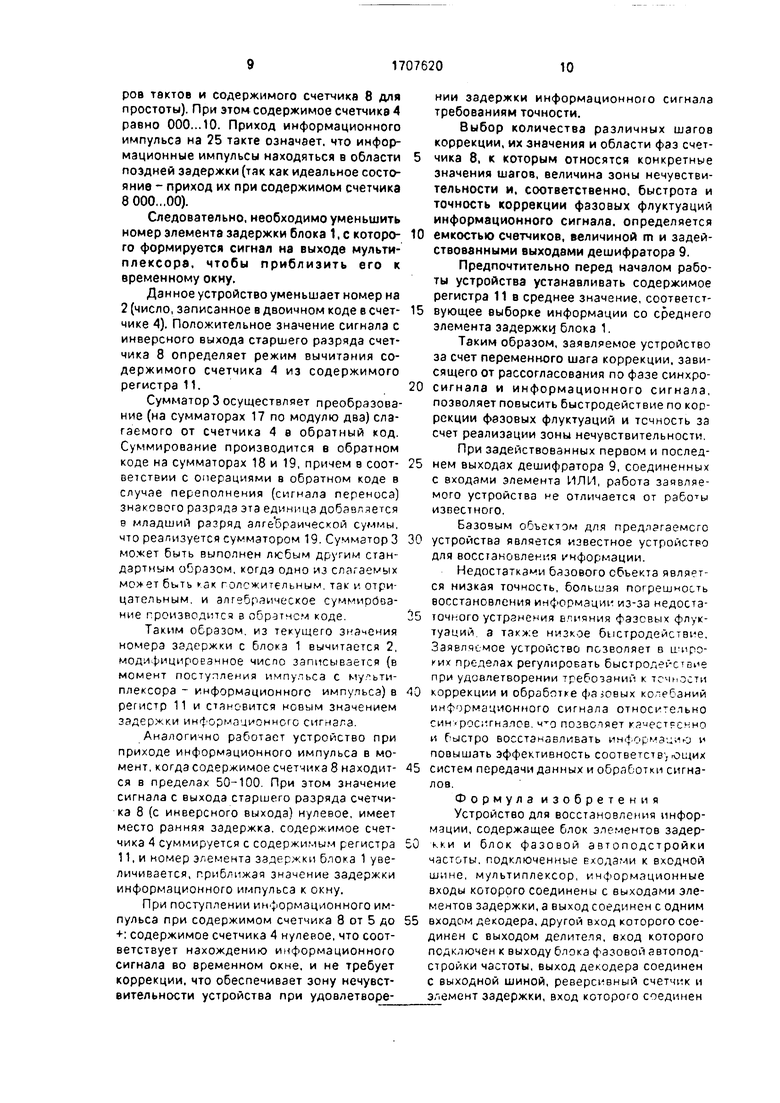

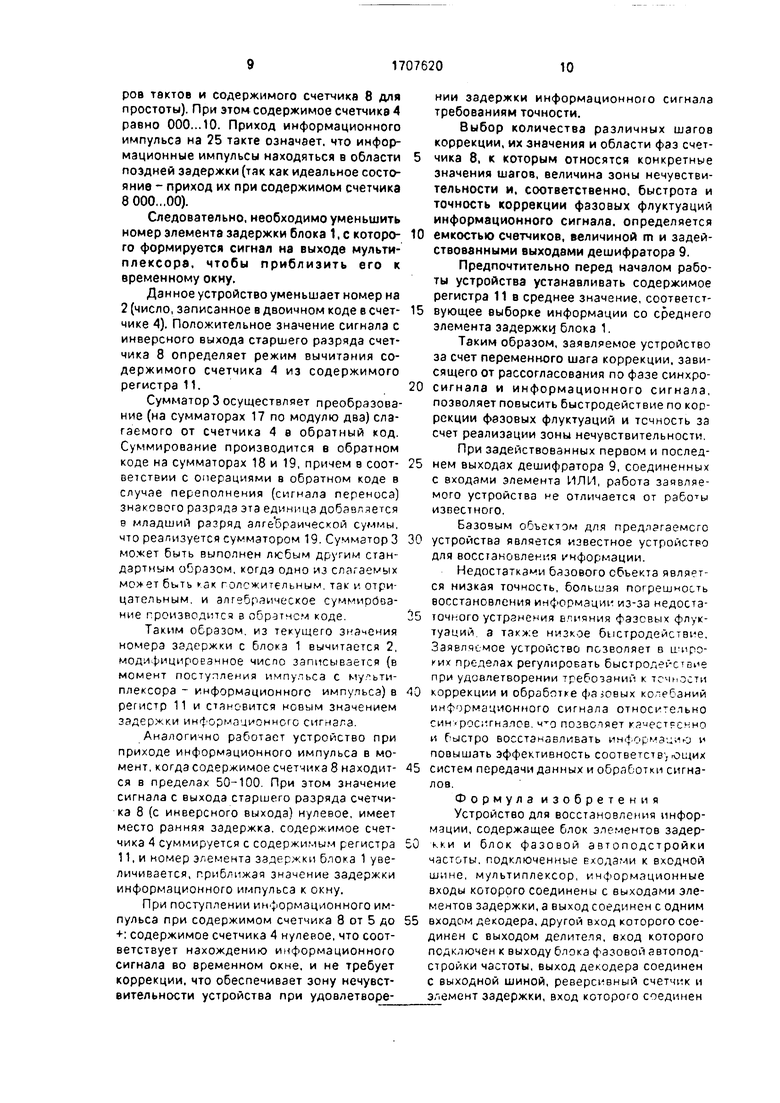

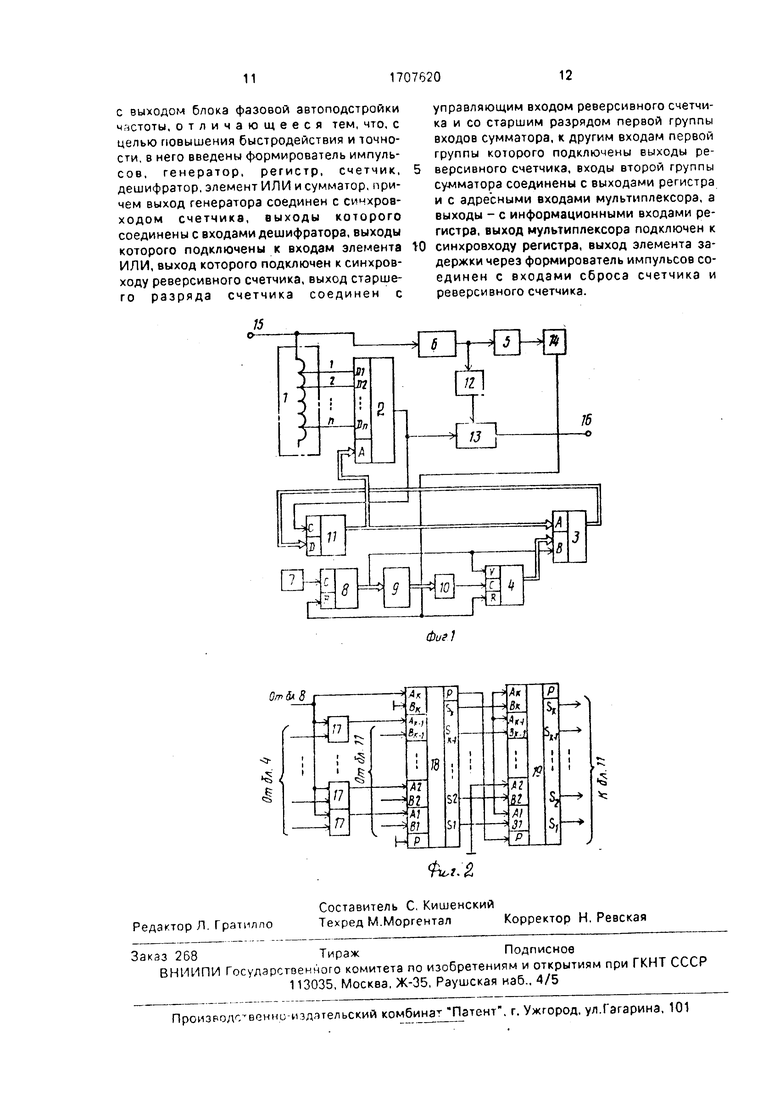

На фиг.1 приведена структурная схема

5 устройства для восстановления информации; на фиг.2 - структурная схема сумматора.

Устройство для восстановления информации содержит блок 1 элементов задержки, мультиплексор 2, сумматор 3, реверсивный счетчик 4, элемент 5 задержки, блок 6 фазовой автоподстройки частоты, генератор 7. счетчик 8. дешифратор 9. элемент ИЛИ 10, регистр 11, делитель 12, декодер 13 и формирователь 14. Входная шина 15 устройстве соединена с входами блоков 1 и 6. Выходная шина 16 устройства соединена с выходом блока 13. Выходы блока 1 соединены с информационными входами блока 2, выход которого подключен к синхронизирующему входу блока 11. Выходы блока 3 соединены с информационными входами блока 11. Выходы блока 4 соединены с одной группой в.-.одов блока 3. Выход блока 6 соединен с ьходом блока 13 и через блоки 5 и 14 соединен с входами сброса блоков 4 и 8. Выход блока 7 подключен к синхровходу блока 8, выходы которого соединены с входами блока 9, выходы которого соединены с входами блока 10, выход которого подключен ку синхровходу блока 4.

Выход блока 11 соединен с другой группой вхгдов блока 3 и с адресными входами блока 2. Выход блока 12 соединен с другим входом блока 13, выход блока 14 подключен к входам сброса блоков 4 и 8. Выход старшего разряда блока 8 соединен с дополнительным (старшим) входом второго слагаемого блока 3.

Сумматор 3 содержит группу сумматоров 17 по модулю два, одни входы которых соединены с выходами блока 4, а другие объединены и подключены к выходу старшего разряда блока 8, соединенному также с одним входом старшего разряда сумматора 18.

Другой вход (второго слагаемого) старшего разряда сумматора 18 заземлен. Входы первого слагаемого у сумматора 18 соединены с выходами сумматоров 17 по модулю два, входы второго слагаемого - с выходами регистра 11. Вход переноса сумматора 18 заземлен. Выходы сумматора 18 соединены с входами первого слагаемого сумматора 19. входы второго слагаемого которого заземлены, выход переноса сумматора 18 соединен с выходом переноса сумматора 19. Выходы сумматора 19 соединены с входами регистра 11 устройства.

Устройство работает следующим образом.

Блок 6 фазовой автоподстройки частоты служит для формирования импульсов из входной информации и привязки их по частоте и фазе. С его выхода синхросигналы через делитель 12 (делитель на два) частоты поступают на вход декодера 13. на другой вход которого поступает входная информация. Декодер 13 осуществляет декодирование (прием) информации. Блок 1 последовательно соединенных элементов задержки представляет собой согласованную линию задержки. Мультиплексор 2 производит выборку задержанных сигналов в соответст5 вии с адресом, содержащимся в регистре 11. Стершими разряд (его значение) счетчика 8 задает направление счета реверсивному счетчику 4. Элемент 5 задержки осуществляет задержку своего входного

0 сигнала на величину, равную половине максимальной величины задержки блока 1 последовательно соединенных элементов задержки, чтобы иметь возможность регулировать задержку входного сигнала с обеих

5 сторон временного окна (являющегося оптимальной задержкой временного сигнала для восстановления информации при фазовых флуктуациях). Счетчик 8 создает временную сетку импульсов для оценки

0 близости и знака рассогласования между информационным импульсом с текущей задержкой и временным окном. В счетчике 4 (реверсивном)хранится текущая (для каждого значения рассогласования) величина кор5 рекции задержки, выраженная в числе номеров элементов задержки блока 1. .на которое при определенном рассогласовании передвинется задержанный информа- ционый импульс.

0 Дешифратор 9 определяет для каждого значения рассогласования переход реверсивного счетчика с одного значения шага коррекции на другой. В сумматоре 3 вычисляется скорректированный номер элемента

5 задержки блока 1. с которого мультиплексор снимает информационный сигнал.

Принцип работы устройства основан на автоматической установке данных в центр временного окна для устрачения погрешно0 сти синхронизации, причем в отличие от известного устройства установка производится шагами, величина которых зависит от рассогласования информационного сигнала и синхросигнала по фазе

5 (фазовой флуктуации информационного сигнала), и имеет место зона нечувствительности устройства, за счет которой при нахождении информационного сигнала внутри временного окна коррекции не про0 изводится, чем дополнительно повышается точность устройства.

Генератор 7 вырабатывает импульсы, частота которых в целое число раз больше частоты сигналов с блока фазовой автопод5 стройки частоты (ФАПЧ): fr - m . Модуль счета счетчика 8 также равен т, так что счетчик 8 за период сигнала с выхода блока ФАПЧ пробегает все состояние от 0 до т-1. По положительному фронту сигнала с элемента 5 задержки формирователь 14 вырабатывает короткий импульс, устанавливающий сметчики 4 и 8 в нулевое состояние. Это делается для устранения накопления ошибки в рэбо-е счетчиков 8 и 4 и блскэ ФАПЧ, так кпк генератор 7 и блок ФАПЧ (и с ним - частота информационных сигналов) не синхронизированы жестко, и если за время периода сигнала с выхода блока ФАПЧ рассогласование между этим периодом и периодом сигнала с выхода счетчика 8 может быть произвольно кала (для кварцевых генераторов не превышает тьспчнух долей процент:, тс зз длительное еромя рэботы ус рой- ТЕ- pacccrracopa 1; . : могло бы накопит ьс ,;с знзч1гег.щ- х ЕС-ЛИЧИН..

Тек/.м образом, сесь период сигналауд- ,:с омнси чистоты с скко.ца блока ФАПЧ рзз- бпвз Г:г. нз m и--;терв:-лоз. Старший разряд ;че u-ir-;. i изменяет значен.ic (с нулевого на ;;,.-. uv с... j; поС .о гп/2 тактов генератора,

3 с.т разряд Б остальных узло устройС I 5 1СГ.С.Г: /-.; :СП . JH3X DIVU. I Г, С Л.г: t -.06

3nr, k i .v :;;.:. к и, с::смсптсть;г.иое вре- ..:: HH.CMV екну COCT; I; лчет Г8ку:о гл.лпчину. лри ко с с о.1, вхсдчой инфор аци-ь ч , им- с в ..:.од2 мультиплексоре; пест умает

..ЛЬ: ; - . ,1ЛТГ;й В N Or.. КО Д СЧйТ -И К. 8 И-.:СДПТС« С H,eLO . COCIC.HI vl .:,И

f- ero - с ооеих. сторон ц-. кла счета}.

Это соотг.етстгует цементу прихода по- лс -1пел1:1-о С Фронтf. сигнала с «ыодз блока ФАПЧ. Если информационней импульс с выхода муГ Ьтиппе«сора поступает роиыие, ч«т/. положительный Фронт с выхода элемента 14 задержки, имеет место ранняя задержка, т.е. информационный импульс опережает временное окно и его нужно задержать на большее время, чем текущее значение задержки. Если инФср - -цисннь импульс отстает, что он н я.с-;:.: с я L поздней задержки, и, номер элемента задро- жки блока 1 необходимо уменьи-ить. чтсГм- приблизить информационный сигнал к сп- тимальнсму значению - временному окну.

Выходы счетика S берутся (ьсе. включая старший разряд) с инверсных вы од; р соответствующих триггеров счетчика, таким образом, в момет сброса со сц ет ш к & снимается (например, двоичное) число 111..., а перед его сбросом с него снимается двоичное число 000...0.

Это необходимо для правильного функционирования узлов, реализующих коррекцию.

Дешифратор 9 определяет величину шага подстройки и область значений содержимого счетчика 8, для которой выбран конкретный шаг подстройки. Рассмотрим

реализацию узлов 8.9 и 4 на конкретном примерз.

Предположим, что m 100. Следовательно, на 51 такте генератора 7 старший

разряд счетчика 8 устанавливается в единичное значение (с инверсного выхода снимается нулевой потенциал).

Дешифратор 9 настраивается на комбинации разрядов счетчика 8, симметричные

0 относительно нулевого значения содержимого счетчика (например, он настроен на комбинации: 5,20,40,60,80.95). и последние три числа соответствуют отрицательным чиспам относительно периода 100 - числам

5 -40, -20, и -5. После сброса счетчиков сигналы элемента 10 ИЛИ поступают на счетный ьход реверсивного счетчика в указанные такты работы. При этом, поскольку в первой Головине периода счета счетчика 8 значе0 ние знакового разряда нулевое, единичный сигнал с его выхода устйнзр.гиеаст счетчик 4 в режим слежения. Таким образом, до 5 такта смотчик 4 - в нулевом состоя -ми, с т 5 до 20 - в состоянии 009. 1. от 20 до 40 5 000...10, ст 40 до GO - в сое-молнии 000...11. После 50 такта значение разряда (старшего) счетчика 8 меняется, и счетчик 4 переводится в режим вычитания, т.е. после 60 такта содержимое его 000 .10. пгсле 80 - 000..

0 - осле 5-СОО. .0 Так:-., сбргзом.в- . любого отрезка времени, г- .-. од 1 сигнала с элемента 14 . г:-чи содержится абсолютная е и ч и н а ;и а гз коррекции.

5Знак шаг. определяется значением

старшего разряда ссдержнмсго счетчика 8,

подаваемого в качестве знакового

для слагаемого от счетчика 4 z C/MM-JTOD 3.

Сумматор 3 может зьп- гю0 бь:м образом для алгебраичос о.-э сло.с-ни первого слагаемого (содег -:. -о регистра 11. представляющего собой текуи тн. номер элемента задержки бпска 1, с которого снимается информационный сигнал на мульти5 2) - это с л;-гаем ее всегда положительное, и етосгчи слагаемого (поправка к номеру элемента задержки блока 1, который будет подключен на выход мультиплексора 2 в результате вычисленного и

0 реализованного шага подстройки) - это слагаемое 5ь-ть как положительное, так и отрицательное, е злвиС .-мости от фазы содержимого счетчика 8 пг.и поступлении информационного импулсса.

5Сама величина шаг записана в счетчике 4.

Пусть, например, информационный импульс поступил в момент времени, когда счетчик 8 находится в состоянии 25 (здесь приведены десятичные эквиваленты номеров тактов и содержимого счетчика 8 для простоты). При этом содержимое счетчика 4 равно 000...10. Приход информационного импульса на 25 такте означает, что информационные импульсы находяться в области поздней задержки (так как идеальное состояние - приход их при содержимом счетчика 8 000...00).

Следовательно, необходимо уменьшить номер элемента задержки блока 1, с которого формируется сигнал на выходе мультиплексора, чтобы приблизить его к временному окну.

Данное устройство уменьшает номер на 2 (число, записанное в двоичном коде в счетчике 4). Положительное значение сигнала с инверсного выхода старшего разряда счетчика 8 определяет режим вычитания содержимого счетчика 4 из содержимого регистра 11.

Сумматор 3 осуществляет преобразование (на сумматорах 17 по модулю два) слагаемого от счетчика 4 в обратный код. Суммирование производится в обратном коде на сумматорах 18 и 19, причем в соответствии с операциями в обратном коде в случае переполнения (сигнала переноса) знакового разряда эта единица добавляется в младший разряд алгебраической суммы, что реализуется сумматором 19. Сумматор 3 может быть выполнен любым другим стандартным образом, когда одно из слагаемых быть как положительным, так и отрицательным, и алгебраическое суммирование производится в обратном коде.

Таким образом, из текущего значения номера задержки с блока 1 вычитается 2, модифицированное число записывается (в момент поступления импульса с мультиплексора - информационного импульса) в регистр 11 и становится новым значением задержки информационного сигнала.

Аналогично работает устройство при приходе информационного импульса в момент, когда содержимое счетчика 8 находится в пределах 50-100. При этом значение сигнала с выхода старшего разряда счетчика 8 (с инверсного выхода) нулевое, имеет место ранняя задержка, содержимое счетчика 4 суммируется с содержимым регистра 11, и номер элемента задержки блока 1 увеличивается, приближая значение задержки информационного импульса к окну.

При поступлении информационного импульса при содержимом счетчика 8 от 5 до +: содержимое счетчика 4 нулевое, что соответствует нахождению информационного сигнала во временном окне, и не требует коррекции, что обеспечивает зону нечувствительности устройства при удовлетворении задержки информационного сигнала требованиям точности.

Выбор количества различных шагов коррекции, их значения и области фаз счетчика 8, к которым относятся конкретные значения шагов, величина зоны нечувствительности и. соответственно, быстрота и точность коррекции фазовых флуктуации информационного сигнала, определяется

0 емкостью счетчиков, величиной m и задействованными выходами дешифратора 9.

Предпочтительно перед началом работы устройства устанавливать содержимое регистра 11 в среднее значение, соответст5 вующее выборке информации со среднего элемента задержки; блока 1.

Таким образом, заявляемое устройство за счет переменного шага коррекции, зависящего от рассогласования по фазе синхро0 сигнала и информационного сигнала, позволяет повысить быстродействие по коррекции фазовых флуктуации и точность за счет реализации зоны нечувствительности. При задействованных первом и послед5 нем выходах дешифратора 9, соединенных с входами элемента ИЛИ, работа заявляемого устройства не отличается от работы известного.

Базовым объектом для предлагаемого

0 устройства является известное устройство для восстановления информации.

Недостатками базового сбьекта является низкая точность, большая погрешность восстановления информации из-за недоста5 точного устранения влияния фазовых флуктуации, а также низкое быстродействие. Заявляемое устройство позволяет в широких пределах регулировать быстродействие при удовлетворении требований к темности

0 коррекции и обработке фазовых колебаний информационного сигнала относительно синхросигналов. что позволяет качественно и быстро восстанавливать информацию и повышать эффективность соответствующих

5 систем передачи данных и обработки сигналов.

Формула изобретения Устройство для восстановления информации, содержащее блок элементов задер0 кки и блок фазовой автоподстройки частоты, подключенные входами к входной шине, мультиплексор, информационные входы которого соединены с выходами элементов задержки, а выход соединен с одним

5 входом декодера, другой вход которого соединен с выходом делителя, вход которого подключен к выходу блока фазовой звтопод- стройки частоты, выход декодера соединен с выходной шиной, реверсивный счетчик и элемент задержки, вход которого соединен

с выходом блока фазовой автоподстройки частоты, отличающееся тем, что, с целью повышения быстродействия и точности, в него введены формирователь импуль- сов, генератор, регистр, счетчик, дешифратор, элемент ИЛИ и сумматор, причем выход генератора соединен с синхров- ходом счетчика, выходы которого соединены с входами дешифратора, выходы которого подключены к входам элемента ИЛИ, выход которого подключен к синхров- ходу реверсивного счетчика, выход старшего разряда счетчика соединен с

о

управляющим входом реверсивного счетчика и со старшим разрядом первой группы входов сумматора, к другим входам первой группы которого подключены выходы реверсивного счетчика, входы второй группы сумматора соединены с выходами регистра и с адресными входами мультиплексора, а выходы - с информационными входами регистра, выход мультиплексора подключен к синхровходу регистра, выход элемента задержки через формирователь импульсов соединен с входами сброса счетчика и реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2004 |

|

RU2260830C1 |

| Устройство для автоподстройки фазы тактовых импульсов | 1990 |

|

SU1811017A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Устройство для восстановления информации | 1988 |

|

SU1561098A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Устройство выделения данных при воспроизведении информации на подвижном магнитном носителе | 1986 |

|

SU1381589A1 |

| Устройство для восстановления воспроизводимой информации | 1988 |

|

SU1578761A1 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| Устройство демодуляции телевизионного сигнала системы Секам | 1989 |

|

SU1688458A1 |

Изобретение предназначено для накопления информации и может быть использовано для восстановления дискретной информации. Целью изобретения является повышение быстродействия и точности устройства. Устройство для восстановления информации содержит блок элементов задержки и блок фазовой автоподстройки частоты, подключенные входами к входной шине, мультиплексор, информационные входы которого соединены с выходами элементов задержки, а выход - с одним входом декодера, другой выход которого соединен с выходом делителя, выход которого подключен к выходу блока фазовой звтоподст- ройки частоты, выход декодера соединен с выходной шиной устройс еа, рес:ер;/ан й счетчик и элемент задержки, вход которого соединен с выходом блока Фазовой авто- подстройки частоты. В устройство ваед-эны формирователь импульсоь. екерат : регистр, счетчик, дешифратор, элемент ИЛИ и сумматор. 2 ил. Ј

| Патент США № 4191976, кл | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Патент США М° 3537082, кл | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Насос | 1917 |

|

SU13A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-23—Публикация

1990-03-05—Подача